Welcome to E-XFL.COM

Embedded - Microcontrollers - Application Specific: Tailored Solutions for Precision and Performance

### Embedded - Microcontrollers - Application Specific

represents a category of microcontrollers designed with unique features and capabilities tailored to specific application needs. Unlike general-purpose microcontrollers, application-specific microcontrollers are optimized for particular tasks, offering enhanced performance, efficiency, and functionality to meet the demands of specialized applications.

#### What Are <u>Embedded - Microcontrollers -</u> <u>Application Specific</u>?

Application charific microcontrollars are analyzared to

### Details

| Details                 |                                                                               |

|-------------------------|-------------------------------------------------------------------------------|

| Product Status          | Obsolete                                                                      |

| Applications            | Capacitive Sensing                                                            |

| Core Processor          | M8C                                                                           |

| Program Memory Type     | FLASH (8kB)                                                                   |

| Controller Series       | CY8C20xx6A                                                                    |

| RAM Size                | 1K x 8                                                                        |

| Interface               | I <sup>2</sup> C, SPI                                                         |

| Number of I/O           | 28                                                                            |

| Voltage - Supply        | 1.71V ~ 5.5V                                                                  |

| Operating Temperature   | -40°C ~ 85°C                                                                  |

| Mounting Type           | Surface Mount                                                                 |

| Package / Case          | 32-UFQFN Exposed Pad                                                          |

| Supplier Device Package | 32-QFN (5x5)                                                                  |

| Purchase URL            | https://www.e-xfl.com/product-detail/infineon-technologies/cy8c20436an-24lqxi |

|                         |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Analog Multiplexer System

The Analog Mux Bus can connect to every GPIO pin. Pins are connected to the bus individually or in any combination. The bus also connects to the analog system for analysis with the CapSense block comparator.

Switch control logic enables selected pins to precharge continuously under hardware control. This enables capacitive measurement for applications such as touch sensing. Other multiplexer applications include:

- Complex capacitive sensing interfaces, such as sliders and touchpads.

- Chip-wide mux that allows analog input from any I/O pin.

- Crosspoint connection between any I/O pin combinations.

## **Additional System Resources**

System resources provide additional capability, such as configurable USB and  $I^2C$  slave, SPI master/slave communication interface, three 16-bit programmable timers, and various system resets supported by the M8C.

These system resources provide additional capability useful to complete systems. Additional resources include low voltage detection and power on reset. The merits of each system resource are listed here:

- The I<sup>2</sup>C slave/SPI master-slave module provides 50/100/400 kHz communication over two wires. SPI communication over three or four wires runs at speeds of 46.9 kHz to 3 MHz (lower for a slower system clock).

- Low-voltage detection (LVD) interrupts can signal the application of falling voltage levels, while the advanced power-on-reset (POR) circuit eliminates the need for a system supervisor.

- An internal reference provides an absolute reference for capacitive sensing.

- A register-controlled bypass mode allows the user to disable the LDO regulator.

# **Getting Started**

The quickest way to understand PSoC silicon is to read this datasheet and then use the PSoC Designer Integrated Development Environment (IDE). This datasheet is an overview of the PSoC integrated circuit and presents specific pin, register, and electrical specifications.

For in depth information, along with detailed programming details, see the Technical Reference Manual for the CY8C20XX6A/S PSoC devices.

For up-to-date ordering, packaging, and electrical specification information, see the latest PSoC device datasheets on the web at www.cypress.com/psoc.

### CapSense Design Guides

Design Guides are an excellent introduction to the wide variety of possible CapSense designs. They are located at www.cypress.com/go/CapSenseDesignGuides.

Refer Getting Started with CapSense design guide for information on CapSense design and CY8C20XX6A/H/AS CapSense<sup>®</sup> Design Guide for specific information on CY8C20XX6A/AS CapSense controllers.

# Silicon Errata

Errata documents known issues with silicon including errata trigger conditions, scope of impact, available workarounds and silicon revision applicability. Refer to Silicon Errata for the PSoC<sup>®</sup> CY8C20x36A/46A/66A/96A/46AS/66AS/36H/46H families available at http://www.cypress.com/?rID=56239 for errata information on CY8C20xx6A/AS/H family of device. Compare errata document with datasheet for a complete functional description of device.

### **Development Kits**

PSoC Development Kits are available online from and through a growing number of regional and global distributors, which include Arrow, Avnet, Digi-Key, Farnell, Future Electronics, and Newark.

# Training

Free PSoC technical training (on demand, webinars, and workshops), which is available online via www.cypress.com, covers a wide variety of topics and skill levels to assist you in your designs.

# **CYPros Consultants**

Certified PSoC consultants offer everything from technical assistance to completed PSoC designs. To contact or become a PSoC consultant go to the CYPros Consultants web site.

### **Solutions Library**

Visit our growing library of solution focused designs. Here you can find various application designs that include firmware and hardware design files that enable you to complete your designs quickly.

### **Technical Support**

Technical support – including a searchable Knowledge Base articles and technical forums – is also available online. If you cannot find an answer to your question, call our Technical Support hotline at 1-800-541-4736.

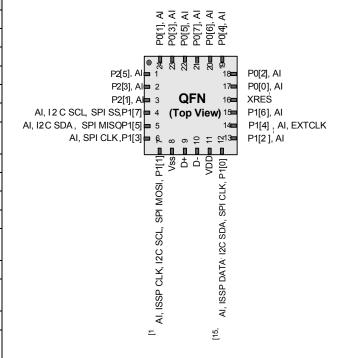

# 24-pin QFN (15 Sensing Inputs (With USB)) [13]

# Table 3. Pin Definitions – CY8C20396A <sup>[14]</sup>

| Pin | Ту      | ре     | Name            | Description                                                                  |

|-----|---------|--------|-----------------|------------------------------------------------------------------------------|

| No. | Digital | Analog | Name            | Description                                                                  |

| 1   | I/O     | I      | P2[5]           |                                                                              |

| 2   | I/O     | I      | P2[3]           |                                                                              |

| 3   | I/O     | I      | P2[1]           |                                                                              |

| 4   | IOHR    | I      | P1[7]           | I <sup>2</sup> C SCL, SPI SS                                                 |

| 5   | IOHR    | I      | P1[5]           | I <sup>2</sup> C SDA, SPI MISO                                               |

| 6   | IOHR    | I      | P1[3]           | SPI CLK                                                                      |

| 7   | IOHR    | I      | P1[1]           | ISSP CLK <sup>[15]</sup> , I <sup>2</sup> C SCL, SPI<br>MOSI                 |

| 8   | Pov     | wer    | V <sub>SS</sub> | Ground <sup>[17]</sup>                                                       |

| 9   | I/O     | I      | D+              | USB D+                                                                       |

| 10  | I/O     | I      | D-              | USB D-                                                                       |

| 11  | Pov     | wer    | V <sub>DD</sub> | Supply                                                                       |

| 12  | IOHR    | I      | P1[0]           | ISSP DATA <sup>[15]</sup> , I <sup>2</sup> C SDA, SPI<br>CLK <sup>[16]</sup> |

| 13  | IOHR    | I      | P1[2]           |                                                                              |

| 14  | IOHR    | I      | P1[4]           | Optional external clock input<br>(EXTCLK)                                    |

| 15  | IOHR    | I      | P1[6]           |                                                                              |

| 16  | RESET   | INPUT  | XRES            | Active high external reset with internal pull-down                           |

| 17  | IOH     | I      | P0[0]           |                                                                              |

| 18  | IOH     |        | P0[2]           |                                                                              |

| 19  | IOH     | I      | P0[4]           |                                                                              |

| 20  | IOH     | I      | P0[6]           |                                                                              |

| 21  | IOH     | I      | P0[7]           |                                                                              |

| 22  | IOH     | I      | P0[5]           |                                                                              |

| 23  | IOH     |        | P0[3]           | Integrating input                                                            |

| 24  | IOH     |        | P0[1]           | Integrating input                                                            |

| СР  | Pov     | wer    | $V_{SS}$        | Center pad must be connected to Ground                                       |

Figure 5. CY8C20396A

LEGEND I = Input, O = Output, OH = 5 mA High Output Drive, R = Regulated Output

#### Notes

- 13.20 GPIOs = 15 pins for capacitive sensing + 2 pins for I2C + 2 pins for USB + 1 pin for modulation capacitor.

- 14. The center pad (CP) on the QFN package must be connected to ground (V<sub>SS</sub>) for best mechanical, thermal, and electrical performance. If not connected to ground,

- The center part (c) you the cent package must be connected to ground (vgg) for best mechanical, thermal, and electrical performance. In hor connected to ground, it must be electrically floated and not connected to any other signal.

On power-up, the SDA(P1[0]) drives a strong high for 256 sleep clock cycles and drives resistive low for the next 256 sleep clock cycles. The SCL(P1[1]) line drives resistive low for 512 sleep clock cycles and both the pins transition to high impedance state. On reset, after XRES de-asserts, the SDA and the SCL lines drive resistive low for 8 sleep clock cycles and transition to high impedance state. Hence, during power-up or reset event, P1[1] and P1[0] may disturb the I2C bus. Use alternate pins if you encounter issues.

<sup>16.</sup> Alternate SPI clock

<sup>17.</sup> All VSS pins should be brought out to one common GND plane.

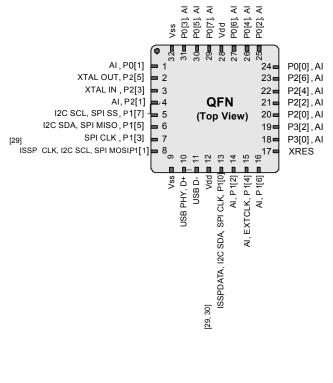

# 32-pin QFN (22 Sensing Inputs (With USB)) [27]

## Table 6. Pin Definitions – CY8C20496A<sup>[28]</sup>

| Pin | Ту      | ре     | Newse           | Description                                                                   |

|-----|---------|--------|-----------------|-------------------------------------------------------------------------------|

| No. | Digital | Analog | Name            | Description                                                                   |

| 1   | IOH     | I      | P0[1]           | Integrating Input                                                             |

| 2   | I/O     | I      | P2[5]           | XTAL Out                                                                      |

| 3   | I/O     | I      | P2[3]           | XTAL In                                                                       |

| 4   | I/O     | I      | P2[1]           |                                                                               |

| 5   | IOHR    | I      | P1[7]           | I <sup>2</sup> C SCL, SPI SS                                                  |

| 6   | IOHR    | I      | P1[5]           | I <sup>2</sup> C SDA, SPI MISO                                                |

| 7   | IOHR    | I      | P1[3]           | SPI CLK                                                                       |

| 8   | IOHR    | I      | P1[1]           | ISSP CLK <sup>[29]</sup> , I <sup>2</sup> C SCL, SPI MOSI                     |

| 9   | Po      | wer    | V <sub>SS</sub> | Ground Pin <sup>[31]</sup>                                                    |

| 10  |         | I      | D+              | USB D+                                                                        |

| 11  |         | l      | D-              | USB D-                                                                        |

| 12  | Po      | wer    | V <sub>DD</sub> | Power pin                                                                     |

| 13  | IOHR    | I      | P1[0]           | ISSP DATA <sup>[29]</sup> , I <sup>2</sup> C SDA, SPI<br>CLKI <sup>[30]</sup> |

| 14  | IOHR    | I      | P1[2]           |                                                                               |

| 15  | IOHR    | I      | P1[4]           | Optional external clock input<br>(EXTCLK)                                     |

| 16  | IOHR    | I      | P1[6]           |                                                                               |

| 17  | In      | out    | XRES            | Active high external reset with internal pull-down                            |

| 18  | I/O     | I      | P3[0]           |                                                                               |

| 19  | I/O     | I      | P3[2]           |                                                                               |

| 20  | I/O     | I      | P2[0]           |                                                                               |

| 21  | I/O     | I      | P2[2]           |                                                                               |

| 22  | I/O     | I      | P2[4]           |                                                                               |

| 23  | I/O     | I      | P2[6]           |                                                                               |

| 24  | IOH     | I      | P0[0]           |                                                                               |

| 25  | IOH     | I      | P0[2]           |                                                                               |

| 26  | IOH     | I      | P0[4]           |                                                                               |

| 27  | IOH     | I      | P0[6]           |                                                                               |

| 28  | Po      | wer    | V <sub>DD</sub> | Power Pin                                                                     |

| 29  | IOH     | I      | P0[7]           |                                                                               |

| 30  | IOH     | I      | P0[5]           |                                                                               |

| 31  | IOH     | I      | P0[3]           | Integrating Input                                                             |

| 32  | Po      | wer    | $V_{SS}$        | Ground Pin <sup>[31]</sup>                                                    |

Figure 8. CY8C20496A

LEGEND A = Analog, I = Input, O = Output, OH = 5 mA High Output Drive, R = Regulated Output.

#### Notes

- 27.27 GPIOs = 22 pins for capacitive sensing + 2 pins for I2C + 2 pins for USB + 1 pin for modulation capacitor.

- 28. The center pad (CP) on the QFN package must be connected to ground (V<sub>SS</sub>) for best mechanical, thermal, and electrical performance. If not connected to ground, it must be electrically floated and not connected to any other signal.

29. On power-up, the SDA(P1[0]) drives a strong high for 256 sleep clock cycles and drives resistive low for the next 256 sleep clock cycles. The SCL(P1[1]) line drives resistive low for 512 sleep clock cycles and both the pins transition to high impedance state. On reset, after XRES de-asserts, the SDA and the SCL lines drive resistive low for 8 sleep clock cycles and transition to high impedance state. Hence, during power-up or reset event, P1[1] and P1[0] may disturb the I2C bus. Use alternate pins if our operator is used. alternate pins if you encounter issues.

<sup>30.</sup> Alternate SPI clock

<sup>31.</sup> All VSS pins should be brought out to one common GND plane.

[33, 34]

# 48-pin SSOP (31 Sensing Inputs) <sup>[32]</sup> Table 7. Pin Definitions – CY8C20536A, CY8C20546A, and CY8C20566A<sup>[33]</sup>

| Pin<br>No. | Digital | Analog | Name            | Description                                                                  |            | Figure          | 9. CY8          | C20536/                                         | A, CY8C     | 2054 | 6A, and CY8C20566A                                                                                        |

|------------|---------|--------|-----------------|------------------------------------------------------------------------------|------------|-----------------|-----------------|-------------------------------------------------|-------------|------|-----------------------------------------------------------------------------------------------------------|

| 1          | IOH     | 1      | P0[7]           |                                                                              |            |                 |                 |                                                 | •           |      |                                                                                                           |

| 2          | IOH     | 1      | P0[5]           |                                                                              |            |                 |                 | AI, P0[7]<br>AI, P0[5]∎                         | 2           | 4    | 8 VDD<br>7 P0[6] , Al                                                                                     |

| 3          | IOH     | 1      | P0[3]           | Integrating Input                                                            |            |                 |                 | AI, P0[3]∎<br>AI P0[1]■                         | 3<br>4      | 46   | 6 P0[4] , Al<br>5 P0[2] , Al                                                                              |

| 4          | IOH     | 1      | P0[1]           | Integrating Input                                                            |            |                 |                 | AI, P2[7]                                       | 5           | 4    | 4 <b>=</b> P0[0], AI                                                                                      |

| 5          | I/O     | 1      | P2[7]           |                                                                              |            |                 | XT<br>X         | ALOUT, P2[5]=<br>TALIN, P2[3] =                 | 6<br>7      |      | 3 P2[6] , AI<br>2 P2[4] , AI                                                                              |

| 6          | I/O     | 1      | P2[5]           | XTAL Out                                                                     |            |                 |                 | AI, P2[1] ■<br>NC■                              | 8           | 4    | 1 P2[2], AI                                                                                               |

| 7          | I/O     | 1      | P2[3]           | XTAL In                                                                      |            |                 |                 | NC■                                             | 10          | 3    | 0 P2[0], Al<br>9 P3[6], Al                                                                                |

| 8          | I/O     | 1      | P2[1]           |                                                                              |            |                 |                 | AI, P4[3 <b>)⊒</b><br>AI, P4[1 <b>)⊒</b>        | 11<br>12 00 | 3    | 8 P3[4], Al<br>7 P3[2], Al<br>8 P3(0], Al                                                                 |

| 9          |         |        | NC              | No connection                                                                |            |                 |                 | NC=                                             |             | 3    |                                                                                                           |

| 10         |         |        | NC              | No connection                                                                |            |                 |                 | AI, P3[7] <b>_</b><br>AI, P3[5] <b>=</b>        | 15          | 3    | 5 XRES<br>4 NC                                                                                            |

| 11         | I/O     | 1      | P4[3]           |                                                                              |            |                 |                 | AI, P3[3]■<br>AI, P3[1]■                        |             | 33   | 3 NC<br>2 NC                                                                                              |

| 12         | I/O     | 1      | P4[1]           |                                                                              |            |                 |                 | NC <b></b>                                      | 18          | 2.   |                                                                                                           |

| 13         |         |        | NC              | No connection                                                                |            |                 | I2 C SCL,       | NC∎<br>SPI SS, P1[7]∎                           | 19<br>20    | 3    | 0 NC<br>NC                                                                                                |

| 14         | I/O     | 1      | P3[7]           |                                                                              |            | 1001            |                 | HMISO, P1[5] <b>⊟</b><br>SPICLK, P1[3] <b>⊟</b> |             | 28   | ■ NC<br>■ NC<br>■ P1(6),AI<br>■ P1(6),AI<br>■ P1(2),AI<br>■ P1(2),AI<br>■ P1(0),ISSP DATA,I2C SDA,SPI CLK |

| 15         | I/O     | 1      | P3[5]           |                                                                              |            | [33]<br>ISSP CL | K, I2 C SCL, SF | 91 MOSL P1[1 ]                                  | 23          | 2    | /■ P1[4], EXTCLK<br>6■ P1[2], AI                                                                          |

| 16         | I/O     | 1      | P3[3]           |                                                                              |            |                 |                 | VSS∎                                            | 24          | 2    | P1[0], ISSP DATA, I2C SDA, SPI CLK                                                                        |

| 17         | I/O     | 1      | P3[1]           |                                                                              |            |                 |                 |                                                 |             |      |                                                                                                           |

| 18         |         |        | NC              | No connection                                                                |            |                 |                 |                                                 |             |      |                                                                                                           |

| 19         |         |        | NC              | No connection                                                                |            |                 |                 |                                                 |             |      |                                                                                                           |

| 20         | IOHR    | 1      | P1[7]           | I <sup>2</sup> C SCL, SPI SS                                                 |            |                 |                 |                                                 |             |      |                                                                                                           |

| 21         | IOHR    | 1      | P1[5]           | I <sup>2</sup> C SDA, SPI MISO                                               |            |                 |                 |                                                 |             |      |                                                                                                           |

| 22         | IOHR    | 1      | P1[3]           | SPICLK                                                                       |            |                 |                 |                                                 |             |      |                                                                                                           |

| 23         | IOHR    | 1      | P1[1]           | ISSP CLK <sup>[33]</sup> , I <sup>2</sup> C SCL, SPI MOSI                    |            |                 |                 |                                                 |             |      |                                                                                                           |

| 24         |         |        | V <sub>SS</sub> | Ground Pin <sup>[35]</sup>                                                   |            |                 |                 |                                                 |             |      |                                                                                                           |

| 25         | IOHR    | I      | P1[0]           | ISSP DATA <sup>[33]</sup> , I <sup>2</sup> C SDA, SPI<br>CLK <sup>[34]</sup> |            |                 |                 |                                                 |             |      |                                                                                                           |

| 26         | IOHR    | 1      | P1[2]           |                                                                              |            |                 |                 |                                                 |             |      |                                                                                                           |

| 27         | IOHR    | I      | P1[4]           | Optional external clock input<br>(EXT CLK)                                   |            |                 |                 |                                                 |             |      |                                                                                                           |

| 28         | IOHR    | 1      | P1[6]           |                                                                              |            |                 |                 |                                                 |             |      |                                                                                                           |

| 29         |         |        | NC              | No connection                                                                |            |                 |                 |                                                 |             |      |                                                                                                           |

| 30         |         |        | NC              | No connection                                                                |            |                 |                 |                                                 |             |      |                                                                                                           |

| 31         |         |        | NC              | No connection                                                                |            |                 |                 |                                                 |             |      |                                                                                                           |

| 32         |         |        | NC              | No connection                                                                | Pin<br>No. | Digital         | Analog          | Name                                            |             |      | Description                                                                                               |

| 33         |         |        | NC              | No connection                                                                | 41         | I/O             | 1               | P2[2]                                           |             |      |                                                                                                           |

| 34         |         |        | NC              | No connection                                                                | 42         | I/O             | I               | P2[4]                                           |             |      |                                                                                                           |

| 35         |         |        | XRES            | Active high external reset with<br>internal pull-down                        | 43         | I/O             | I               | P2[6]                                           |             |      |                                                                                                           |

| 36         | I/O     | I      | P3[0]           |                                                                              | 44         | IOH             | I               | P0[0]                                           |             |      |                                                                                                           |

| 37         | I/O     | I      | P3[2]           |                                                                              | 45         | IOH             | I               | P0[2]                                           |             |      |                                                                                                           |

| 38         | I/O     | 1      | P3[4]           |                                                                              | 46         | IOH             | I               | P0[4]                                           | VREF        |      |                                                                                                           |

| 39         | I/O     | I      | P3[6]           |                                                                              | 47         | IOH             | 1               | P0[6]                                           |             |      |                                                                                                           |

| 40         | I/O     | 1      | P2[0]           |                                                                              | 48         | Power           |                 | V <sub>DD</sub>                                 | Power P     | in   |                                                                                                           |

LEGEND A = Analog, I = Input, O = Output, NC = No Connection, H = 5 mA High Output Drive, R = Regulated Output Option.

#### Notes

32.34 GPIOs = 31 pins for capacitive sensing + 2 pins for I2C + 1 pin for modulation capacitor.

33. On power-up, the SDA(P1[0]) drives a strong high for 256 sleep clock cycles and drives resistive low for the next 256 sleep clock cycles. The SCL(P1[1]) line drives resistive low for 512 sleep clock cycles and both the pins transition to high impedance state. On reset, after XRES de-asserts, the SDA and the SCL lines drive resistive low for 8 sleep clock cycles and transition to high impedance state. Hence, during power-up or reset event, P1[1] and P1[0] may disturb the I2C bus. Use alternate pins if you encounter issues.

34. Alternate SPI clock.

35. All VSS pins should be brought out to one common GND plane.

# 48-pin QFN (OCD) (33 Sensing Inputs) [46]

The 48-pin QFN part is for the CY8C20066A On-Chip Debug (OCD). Note that this part is only used for in-circuit debugging. Table 10. Pin Definitions – CY8C20066A <sup>[47, 48]</sup>

| Pin<br>No.         | Digital | Analog | Name            | Description                                                                  | ]                  |              | -                                            |                                                                        | /8C20066A                                                                                                                                   |

|--------------------|---------|--------|-----------------|------------------------------------------------------------------------------|--------------------|--------------|----------------------------------------------|------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| 1 <sup>[49]</sup>  |         | 1      | OCDOE           | OCD mode direction pin                                                       |                    |              |                                              | Po[1], AI<br>Vss<br>Po[3], AI<br>Po[5], AI                             | P0[7], AI<br>OCDE<br>OCDO<br>OCDO<br>OCDO<br>P0[6], AI<br>P0[0], AI<br>P0[0], AI                                                            |

| 2                  | I/O     | I      | P2[7]           |                                                                              |                    |              |                                              | Pol<br>Pol                                                             |                                                                                                                                             |

| 3                  | I/O     | I      | P2[5]           | Crystal output (XOut)                                                        |                    |              |                                              | 5<br>5<br>7<br>8                                                       |                                                                                                                                             |

| 4                  | I/O     |        | P2[3]           | Crystal input (XIn)                                                          |                    |              | A E 1<br>A P2[7] 2                           | 4444                                                                   |                                                                                                                                             |

| 5                  | I/O     |        | P2[1]           |                                                                              |                    |              | 0ut, P2[7] = 2<br>Out, P2[5] = 3             |                                                                        | 35 <b>■</b> P2[4] , Al<br>34 <b>■</b> P2[2] , Al                                                                                            |

| 6                  | I/O     | I      | P4[3]           |                                                                              |                    |              | Xln , P2[3] = 4                              |                                                                        | 34 <b>=</b> P2[2],AI<br>33 <b>=</b> P2[0],AI                                                                                                |

| 7                  | I/O     | I      | P4[1]           |                                                                              |                    | <i>7</i> u , | AI , P2[1] = 5                               |                                                                        | 32 <b>–</b> P4[2],AI                                                                                                                        |

| 8                  | I/O     | I      | P3[7]           |                                                                              |                    |              | AI , P4[3] = 6                               |                                                                        | QFN 31= P4[0],AI                                                                                                                            |

| 9                  | I/O     | 1      | P3[5]           |                                                                              |                    |              | AI , P4[1] 🗖 7                               |                                                                        | (Top View) 30= P3[6],AI                                                                                                                     |

| 10                 | I/O     | 1      | P3[3]           |                                                                              |                    |              | AI, P3[7] = 8                                |                                                                        | 29 <b>=</b> P3[4], Al                                                                                                                       |

| 11                 | I/O     | I      | P3[1]           |                                                                              |                    |              | AI, P3[5] <b>P</b> 9<br>AI, P3[3] <b>P</b> 1 |                                                                        | 28 <b>⊏</b> P3[2],AI<br>27 <b>⊏</b> P3[0],AI                                                                                                |

| 12                 | IOHR    | I      | P1[7]           | I <sup>2</sup> C SCL, SPI SS                                                 |                    |              | AI, P3[3] = 1<br>AI, P3[1] = 1               |                                                                        | 26 <b>=</b> XRES                                                                                                                            |

| 13                 | IOHR    | I      | P1[5]           | I <sup>2</sup> C SDA, SPI MISO                                               | AL, L              | 2 C SCL, SP  | I SS, P1[7] = 1                              | ∫~ 4 ∩ 0<br>∣                                                          | E @ @ Q ∑ X X X <sup>25</sup> ■ P1[6],Al                                                                                                    |

| 14 <sup>[49]</sup> |         |        | CCLK            | OCD CPU clock output                                                         |                    |              |                                              |                                                                        |                                                                                                                                             |

| 15 <sup>[49]</sup> |         |        | HCLK            | OCD high speed clock output                                                  |                    |              |                                              | I, P1[5]<br>CCLK<br>HCLK<br>, P1[3]                                    | 71[1]<br>D + D + D - D - D - 1[0]<br>D - 1[2]<br>D - 1[4]                                                                                   |

| 16                 | IOHR    | I      | P1[3]           | SPI CLK.                                                                     |                    |              |                                              | H O O H                                                                | 003, P1[1]<br>Vss<br>D - L<br>D - Vdd<br>Vdd<br>N, P1[2]<br>DLK, P1[2]<br>DLK, P1[2]                                                        |

| 17                 | IOHR    |        | P1[1]           | ISSP CLK <sup>[50],</sup> I <sup>2</sup> C SCL, SPI                          |                    |              |                                              | K, Ø,                                                                  | -, SPI MOSI, P1[1]<br>Vss<br>D +<br>D -<br>D -<br>D -<br>D -<br>D -<br>D -<br>D -<br>D -<br>D -<br>D -                                      |

| 17                 | IONK    |        | FILIJ           | MOSI                                                                         |                    |              |                                              | ICL M                                                                  | EX SPI                                                                                                                                      |

| 18                 | Po      | wer    | V <sub>SS</sub> | Ground connection <sup>[52]</sup>                                            |                    |              |                                              | 2C SDA, SPI MSO, AI, P1[5]<br>CCLK<br>HCLK<br>SPI CLK, AI, P1[3]       | AIA                                                                                                                                         |

| 19                 | I/O     |        | D+              | USB D+                                                                       |                    |              |                                              | SDA                                                                    | 12C S                                                                                                                                       |

| 20                 | I/O     |        | D-              | USB D-                                                                       |                    |              |                                              | 12C                                                                    | E É                                                                                                                                         |

| 21                 | Po      | wer    | V <sub>DD</sub> | Supply voltage                                                               |                    |              |                                              |                                                                        |                                                                                                                                             |

| 22                 | IOHR    | I      | P1[0]           | ISSP DATA <sup>[50]</sup> , I <sup>2</sup> C SDA, SPI<br>CLK <sup>[51]</sup> |                    |              |                                              | 12C SDA, SPI MSO, AI, P1[5]<br>CCLK<br>HCLK<br>F50] SPI CLK, AI, P1[3] | AI,JSSP CLM, IZC SCL, SPI MOSI, P1[1]<br>Vs<br>D-<br>B-<br>AI,ISSP DATA', IZC SDA, SPI CLK, P1[0]<br>AI, EXTCLK, P1[2]<br>AI, EXTCLK, P1[4] |

| 23                 | IOHR    | I      | P1[2]           |                                                                              | Pin<br>No.         | Digital      | Analog                                       | Name                                                                   | Description                                                                                                                                 |

| 24                 | IOHR    | I      | P1[4]           | Optional external clock input<br>(EXTCLK)                                    | 37                 | IOH          | I                                            | P0[0]                                                                  |                                                                                                                                             |

| 25                 | IOHR    |        | P1[6]           |                                                                              | 38                 | IOH          |                                              | P0[2]                                                                  |                                                                                                                                             |

| 26                 | In      | put    | XRES            | Active high external reset with<br>internal pull-down                        | 39                 | IOH          | Ι                                            | P0[4]                                                                  |                                                                                                                                             |

| 27                 | I/O     | I      | P3[0]           |                                                                              | 40                 | IOH          |                                              | P0[6]                                                                  |                                                                                                                                             |

| 28                 | I/O     | I      | P3[2]           |                                                                              | 41                 | P            | ower                                         | $V_{DD}$                                                               | Supply voltage                                                                                                                              |

| 29                 | I/O     |        | P3[4]           |                                                                              | 42 <sup>[49]</sup> |              |                                              | OCDO                                                                   | OCD even data I/O                                                                                                                           |

| 30                 | I/O     |        | P3[6]           |                                                                              | 43 <sup>[49]</sup> |              |                                              | OCDE                                                                   | OCD odd data output                                                                                                                         |

| 31                 | I/O     | I      | P4[0]           |                                                                              | 44                 | IOH          | Ι                                            | P0[7]                                                                  |                                                                                                                                             |

| 32                 | I/O     |        | P4[2]           |                                                                              | 45                 | IOH          |                                              | P0[5]                                                                  |                                                                                                                                             |

| 33                 | I/O     |        | P2[0]           |                                                                              | 46                 | IOH          |                                              | P0[3]                                                                  | Integrating input                                                                                                                           |

| 34                 | I/O     |        | P2[2]           |                                                                              | 47                 |              | ower                                         | V <sub>SS</sub>                                                        | Ground connection <sup>[52]</sup>                                                                                                           |

| 35                 | I/O     |        | P2[4]           |                                                                              | 48                 | IOH          |                                              | P0[1]                                                                  |                                                                                                                                             |

| 36                 | I/O     | Ι      | P2[6]           |                                                                              | СР                 | P            | ower                                         | V <sub>SS</sub>                                                        | Center pad must be connected to ground                                                                                                      |

LEGEND A = Analog, I = Input, O = Output, NC = No Connection H = 5 mA High Output Drive, R = Regulated Output.

#### Notes

Notes

46. 38 GPIOs = 33 pins for capacitive sensing + 2 pins for I2C + 2 pins for USB + 1 pin for modulation capacitor.

47. This part is available in limited quantities for In-Circuit Debugging during prototype development. It is not available in production volumes.

48. The center pad (CP) on the QFN package must be connected to ground (V<sub>SS</sub>) for best mechanical, thermal, and electrical performance. If not connected to ground, it must be electrically floated and not connected to any other signal.

49. This pin (associated with OCD part only) is required for connecting the device to ICE-Cube In-Circuit Emulator for firmware debugging purpose. To know more about the usage of ICE-Cube, refer to CY3215-DK PSoC<sup>®</sup> IN-CIRCUIT EMULATOR KIT GUIDE.

50. On Power-up, the SDA(P1[0]) drives a strong high for 256 sleep clock cycles and drives resistive low for 512 sleep clock cycles and both the pins transition to High impedance state. In both cases, a pull-up resistance on these lines combines with the pull-down resistance (5.6K ohm) and form a potential divider. Hence, during power-up or reset event, P1[1] and P1[0] may disturb the I2C bus. Use alternate pins if you encounter issues.

51. Alternate SPI clock.

51. Alternate SPI clock.

52. All VSS pins should be brought out to one common GND plane.

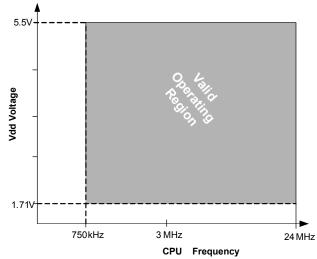

# **Electrical Specifications**

This section presents the DC and AC electrical specifications of the CY8C20XX6A/S PSoC devices. For the latest electrical specifications, confirm that you have the most recent datasheet by visiting the web at http://www.cypress.com/psoc.

# Figure 13. Voltage versus CPU Frequency

# Absolute Maximum Ratings

Exceeding maximum ratings may shorten the useful life of the device. User guidelines are not tested.

#### Table 11. Absolute Maximum Ratings

| Symbol                           | Description                         | Conditions                                                                                                                                                                                      | Min                | Тур | Max                   | Units |

|----------------------------------|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----|-----------------------|-------|

| T <sub>STG</sub>                 | Storage temperature                 | Higher storage temperatures reduce data<br>retention time. Recommended Storage<br>Temperature is +25 °C ± 25 °C. Extended<br>duration storage temperatures above 85 °C<br>degrades reliability. | -55                | +25 | +125                  | °C    |

| V <sub>DD</sub>                  | Supply voltage relative to $V_{SS}$ | _                                                                                                                                                                                               | -0.5               | _   | +6.0                  | V     |

| V <sub>IO</sub>                  | DC input voltage                    | _                                                                                                                                                                                               | $V_{\rm SS} - 0.5$ | _   | V <sub>DD</sub> + 0.5 | V     |

| V <sub>IOZ</sub> <sup>[53]</sup> | DC voltage applied to tristate      | _                                                                                                                                                                                               | $V_{\rm SS} - 0.5$ | _   | V <sub>DD</sub> + 0.5 | V     |

| I <sub>MIO</sub>                 | Maximum current into any port pin   | -                                                                                                                                                                                               | -25                | -   | +50                   | mA    |

| ESD                              | Electrostatic discharge voltage     | Human body model ESD                                                                                                                                                                            | 2000               | -   | -                     | V     |

| LU                               | Latch-up current                    | In accordance with JESD78 standard                                                                                                                                                              | -                  | -   | 200                   | mA    |

# **Operating Temperature**

## Table 12. Operating Temperature

| Symbol         | Description                  | Conditions                                                                                                                                                                             | Min | Тур | Мах  | Units |

|----------------|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|------|-------|

| T <sub>A</sub> | Ambient temperature          | _                                                                                                                                                                                      | -40 | -   | +85  | °C    |

| т <sub>с</sub> | Commercial temperature range | _                                                                                                                                                                                      | 0   | -   | 70   | °C    |

| TJ             |                              | The temperature rise from ambient to junction is package specific. Refer the Thermal Impedances on page 38. The user must limit the power consumption to comply with this requirement. | 40  | _   | +100 | °C    |

Note

53. Port1 pins are hot-swap capable with I/O configured in High-Z mode, and pin input voltage above V<sub>DD</sub>.

# **DC GPIO Specifications**

The following tables list guaranteed maximum and minimum specifications for the voltage and temperature ranges: 3.0 V to 5.5 V and -40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, 2.4 V to 3.0 V and -40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, or 1.71 V to 2.4 V and -40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, respectively. Typical parameters apply to 5 V and 3.3 V at 25 C and are for design guidance only.

| Table 14. | 3.0 V to 5. | 5 V DC GPIO | Specifications |

|-----------|-------------|-------------|----------------|

|-----------|-------------|-------------|----------------|

| Symbol                | Description                                                                       | Conditions                                                                                                                                                                                            | Min                    | Тур   | Max  | Units |

|-----------------------|-----------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|-------|------|-------|

| R <sub>PU</sub>       | Pull-up resistor                                                                  | _                                                                                                                                                                                                     | 4                      | 5.60  | 8    | kΩ    |

| V <sub>OH1</sub>      | High output voltage<br>Port 2 or 3 or 4 pins                                      | $I_{OH} \le 10 \ \mu$ A, maximum of 10 mA source current in all I/Os                                                                                                                                  | V <sub>DD</sub> – 0.20 | -     | -    | V     |

| V <sub>OH2</sub>      | High output voltage<br>Port 2 or 3 or 4 pins                                      | I <sub>OH</sub> = 1 mA, maximum of 20 mA source<br>current in all I/Os                                                                                                                                | V <sub>DD</sub> - 0.90 | -     | -    | V     |

| V <sub>OH3</sub>      | High output voltage<br>Port 0 or 1 pins with LDO regulator<br>Disabled for port 1 | I <sub>OH</sub> < 10 μA, maximum of 10 mA source<br>current in all I/Os                                                                                                                               | V <sub>DD</sub> – 0.20 | -     | -    | V     |

| V <sub>OH4</sub>      | High output voltage<br>Port 0 or 1 pins with LDO regulator<br>Disabled for port 1 | I <sub>OH</sub> = 5 mA, maximum of 20 mA source<br>current in all I/Os                                                                                                                                | V <sub>DD</sub> – 0.90 | -     | -    | V     |

| V <sub>OH5</sub>      | High output voltage<br>Port 1 Pins with LDO Regulator Enabled<br>for 3 V out      | $I_{OH}$ < 10 $\mu$ A, $V_{DD}$ > 3.1 V, maximum of 4 I/Os all sourcing 5 mA                                                                                                                          | 2.85                   | 3.00  | 3.30 | V     |

| V <sub>OH6</sub>      | High output voltage<br>Port 1 pins with LDO regulator enabled for<br>3 V out      | $I_{OH}$ = 5 mA, $V_{DD}$ > 3.1 V, maximum of 20 mA source current in all I/Os                                                                                                                        | 2.20                   | -     | -    | V     |

| V <sub>OH7</sub>      | High output voltage<br>Port 1 pins with LDO enabled for 2.5 V out                 | $I_{OH}$ < 10 $\mu$ A, V <sub>DD</sub> > 2.7 V, maximum of 20 mA source current in all I/Os                                                                                                           | 2.35                   | 2.50  | 2.75 | V     |

| V <sub>OH8</sub>      | High output voltage<br>Port 1 pins with LDO enabled for 2.5 V out                 | I <sub>OH</sub> = 2 mA, V <sub>DD</sub> > 2.7 V, maximum of 20 mA<br>source current in all I/Os                                                                                                       | 1.90                   | -     | -    | V     |

| V <sub>OH9</sub>      | High output voltage<br>Port 1 pins with LDO enabled for 1.8 V out                 | $I_{OH}$ < 10 $\mu$ A, V <sub>DD</sub> > 2.7 V, maximum of 20 mA source current in all I/Os                                                                                                           | 1.60                   | 1.80  | 2.10 | V     |

| V <sub>OH10</sub>     | High output voltage<br>Port 1 pins with LDO enabled for 1.8 V out                 | I <sub>OH</sub> = 1 mA, V <sub>DD</sub> > 2.7 V, maximum of 20 mA<br>source current in all I/Os                                                                                                       | 1.20                   | -     | -    | V     |

| V <sub>OL</sub>       | Low output voltage                                                                | $I_{OL}$ = 25 mA, $V_{DD}$ > 3.3 V, maximum of<br>60 mA sink current on even port pins (for<br>example, P0[2] and P1[4]) and 60 mA sink<br>current on odd port pins (for example, P0[3]<br>and P1[5]) | _                      | _     | 0.75 | v     |

| V <sub>IL</sub>       | Input low voltage                                                                 | -                                                                                                                                                                                                     | -                      | -     | 0.80 | V     |

| V <sub>IH</sub>       | Input high voltage                                                                | _                                                                                                                                                                                                     | 2.00                   | -     | -    | V     |

| V <sub>H</sub>        | Input hysteresis voltage                                                          | _                                                                                                                                                                                                     | -                      | 80    | -    | mV    |

| IIL                   | Input leakage (Absolute Value)                                                    | _                                                                                                                                                                                                     | -                      | 0.001 | 1    | μΑ    |

| C <sub>PIN</sub>      | Pin capacitance                                                                   | Package and pin dependent<br>Temp = 25 °C                                                                                                                                                             | 0.50                   | 1.70  | 7    | pF    |

| V <sub>ILLVT3.3</sub> | Input Low Voltage with low threshold<br>enable set, Enable for Port1              | Bit3 of IO_CFG1 set to enable low threshold voltage of Port1 input                                                                                                                                    | 0.8                    | V     | -    | -     |

| V <sub>IHLVT3.3</sub> | Input High Voltage with low threshold<br>enable set, Enable for Port1             | Bit3 of IO_CFG1 set to enable low threshold voltage of Port1 input                                                                                                                                    | 1.4                    | -     | -    | V     |

| V <sub>ILLVT5.5</sub> | Input Low Voltage with low threshold<br>enable set, Enable for Port1              | Bit3 of IO_CFG1 set to enable low threshold voltage of Port1 input                                                                                                                                    | 0.8                    | V     | -    | -     |

| V <sub>IHLVT5.5</sub> | Input High Voltage with low threshold<br>enable set, Enable for Port1             | Bit3 of IO_CFG1 set to enable low threshold voltage of Port1 input                                                                                                                                    | 1.7                    | -     | -    | V     |

# Table 16. 1.71 V to 2.4 V DC GPIO Specifications (continued)

| Symbol           | Description                    | Conditions                                | Min                  | Тур  | Max  | Units |

|------------------|--------------------------------|-------------------------------------------|----------------------|------|------|-------|

| V <sub>IH</sub>  | Input high voltage             | _                                         | $0.65 \times V_{DD}$ | -    | _    | V     |

| V <sub>H</sub>   | Input hysteresis voltage       | -                                         | -                    | 80   | _    | mV    |

| IIL              | Input leakage (absolute value) | -                                         | -                    | 1    | 1000 | nA    |

| C <sub>PIN</sub> | Capacitive load on pins        | Package and pin dependent<br>temp = 25 °C | 0.50                 | 1.70 | 7    | pF    |

# Table 17. DC Characteristics – USB Interface

| Symbol             | Description                          | Conditions                  | Min   | Тур  | Max   | Units |

|--------------------|--------------------------------------|-----------------------------|-------|------|-------|-------|

| R <sub>USBI</sub>  | USB D+ pull-up resistance            | With idle bus               | 900   | -    | 1575  | Ω     |

| R <sub>USBA</sub>  | USB D+ pull-up resistance            | While receiving traffic     | 1425  | -    | 3090  | Ω     |

| V <sub>OHUSB</sub> | Static output high                   | -                           | 2.8   | -    | 3.6   | V     |

| V <sub>OLUSB</sub> | Static output low                    | -                           | -     | -    | 0.3   | V     |

| V <sub>DI</sub>    | Differential input sensitivity       | -                           | 0.2   | -    |       | V     |

| V <sub>CM</sub>    | Differential input common mode range | -                           | 0.8   | -    | 2.5   | V     |

| V <sub>SE</sub>    | Single ended receiver threshold      | -                           | 0.8   | -    | 2.0   | V     |

| C <sub>IN</sub>    | Transceiver capacitance              | -                           | -     | -    | 50    | pF    |

| I <sub>IO</sub>    | High Z state data line leakage       | On D+ or D- line            | -10   | -    | +10   | μΑ    |

| R <sub>PS2</sub>   | PS/2 pull-up resistance              | -                           | 3000  | 5000 | 7000  | Ω     |

| R <sub>EXT</sub>   | External USB series resistor         | In series with each USB pin | 21.78 | 22.0 | 22.22 | Ω     |

# **DC Analog Mux Bus Specifications**

Table 18 lists guaranteed maximum and minimum specifications for the entire voltage and temperature ranges.

## Table 18. DC Analog Mux Bus Specifications

| Symbol           | Description                                                       | Conditions | Min | Тур | Max | Units |

|------------------|-------------------------------------------------------------------|------------|-----|-----|-----|-------|

| R <sub>SW</sub>  | Switch resistance to common analog bus                            | _          | -   | _   | 800 | Ω     |

| R <sub>GND</sub> | Resistance of initialization switch to $\mathrm{V}_{\mathrm{SS}}$ | _          | -   | _   | 800 | Ω     |

The maximum pin voltage for measuring  $\rm R_{SW}$  and  $\rm R_{GND}$  is 1.8 V

#### **DC Low Power Comparator Specifications**

Table 19 lists guaranteed maximum and minimum specifications for the entire voltage and temperature ranges.

# Table 19. DC Comparator Specifications

| Symbol             | Description                            | Conditions                          | Min | Тур | Max | Units |

|--------------------|----------------------------------------|-------------------------------------|-----|-----|-----|-------|

| V <sub>LPC</sub>   | Low power comparator (LPC) common mode | Maximum voltage limited to $V_{DD}$ | 0.0 | -   | 1.8 | V     |

| I <sub>LPC</sub>   | LPC supply current                     | _                                   | -   | 10  | 40  | μΑ    |

| V <sub>OSLPC</sub> | LPC voltage offset                     | -                                   | -   | 3   | 30  | mV    |

# **Comparator User Module Electrical Specifications**

Table 20 lists the guaranteed maximum and minimum specifications. Unless stated otherwise, the specifications are for the entire device voltage and temperature operating range: –40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, 1.71 V  $\leq$  V<sub>DD</sub>  $\leq$  5.5 V.

Table 20. Comparator User Module Electrical Specifications

| Symbol            | Description                            | Conditions                                  | Min | Тур | Max | Units |

|-------------------|----------------------------------------|---------------------------------------------|-----|-----|-----|-------|

| t <sub>COMP</sub> | Comparator response time               | 50 mV overdrive                             | -   | 70  | 100 | ns    |

| Offset            |                                        | Valid from 0.2 V to V <sub>DD</sub> – 0.2 V | -   | 2.5 | 30  | mV    |

| Current           | Average DC current, 50 mV<br>overdrive |                                             | -   | 20  | 80  | μA    |

| PSRR              | Supply voltage > 2 V                   | Power supply rejection ratio                | -   | 80  | -   | dB    |

| PORK              | Supply voltage < 2 V                   | Power supply rejection ratio                | -   | 40  | -   | dB    |

| Input range       |                                        | -                                           | 0   |     | 1.5 | V     |

# ADC Electrical Specifications

# Table 21. ADC User Module Electrical Specifications

| Symbol              | Description                  | Conditions                                                                                     | Min                       | Тур                       | Max                       | Units |

|---------------------|------------------------------|------------------------------------------------------------------------------------------------|---------------------------|---------------------------|---------------------------|-------|

| Input               | •                            |                                                                                                |                           |                           |                           |       |

| V <sub>IN</sub>     | Input voltage range          | -                                                                                              | 0                         | -                         | VREFADC                   | V     |

| C <sub>IIN</sub>    | Input capacitance            | _                                                                                              | _                         | _                         | 5                         | pF    |

| R <sub>IN</sub>     | Input resistance             | Equivalent switched cap input<br>resistance for 8-, 9-, or 10-bit<br>resolution                | 1/(500fF ×<br>data clock) | 1/(400fF ×<br>data clock) | 1/(300fF ×<br>data clock) | Ω     |

| Reference           |                              |                                                                                                |                           | •                         | •                         |       |

| V <sub>REFADC</sub> | ADC reference voltage        | -                                                                                              | 1.14                      | _                         | 1.26                      | V     |

| Conversion I        | Rate                         |                                                                                                | 1                         |                           |                           |       |

| F <sub>CLK</sub>    | Data clock                   | Source is chip's internal main<br>oscillator. See AC Chip-Level<br>Specifications for accuracy | 2.25                      | _                         | 6                         | MHz   |

| S8                  | 8-bit sample rate            | Data clock set to 6 MHz. sample rate<br>= 0.001/ (2^Resolution/Data Clock)                     |                           | 23.43                     | -                         | ksps  |

| S10                 | 10-bit sample rate           | Data clock set to 6 MHz. sample rate<br>= 0.001/ (2 <sup>resolution/data clock)</sup>          | -                         | 5.85                      | -                         | ksps  |

| DC Accuracy         | /                            |                                                                                                |                           | •                         | •                         |       |

| RES                 | Resolution                   | Can be set to 8-, 9-, or 10-bit                                                                | 8                         | -                         | 10                        | bits  |

| DNL                 | Differential nonlinearity    | -                                                                                              | -1                        | -                         | +2                        | LSB   |

| INL                 | Integral nonlinearity        | -                                                                                              | -2                        | -                         | +2                        | LSB   |

| F                   | Offset error                 | 8-bit resolution                                                                               | 0                         | 3.20                      | 19.20                     | LSB   |

| E <sub>OFFSET</sub> | Oliset error                 | 10-bit resolution                                                                              | 0                         | 12.80                     | 76.80                     | LSB   |

| E <sub>GAIN</sub>   | Gain error                   | For any resolution                                                                             | -5                        | -                         | +5                        | %FSR  |

| Power               |                              |                                                                                                | 1                         |                           |                           |       |

| I <sub>ADC</sub>    | Operating current            | _                                                                                              | _                         | 2.10                      | 2.60                      | mA    |

|                     |                              | PSRR (V <sub>DD</sub> > 3.0 V)                                                                 | _                         | 24                        | _                         | dB    |

| PSRR                | Power supply rejection ratio | PSRR (V <sub>DD</sub> < 3.0 V)                                                                 | _                         | 30                        | _                         | dB    |

#### Table 29. AC Characteristics – USB Data Timings

| Symbol             | Description                                             | Conditions         | Min        | Тур | Max        | Units |

|--------------------|---------------------------------------------------------|--------------------|------------|-----|------------|-------|

| t <sub>DRATE</sub> | Full speed data rate                                    | Average bit rate   | 12 – 0.25% | 12  | 12 + 0.25% | MHz   |

| t <sub>JR1</sub>   | Receiver jitter tolerance                               | To next transition | -18.5      | -   | 18.5       | ns    |