Welcome to **E-XFL.COM**

<u>Embedded - Microcontrollers - Application</u>

<u>Specific</u>: Tailored Solutions for Precision and Performance

Embedded - Microcontrollers - Application Specific represents a category of microcontrollers designed with unique features and capabilities tailored to specific application needs. Unlike general-purpose microcontrollers, application-specific microcontrollers are optimized for particular tasks, offering enhanced performance, efficiency, and functionality to meet the demands of specialized applications.

What Are <u>Embedded - Microcontrollers - Application Specific</u>?

Application enacific microcontrollars are anaineared to

| Details                 |                                                                              |

|-------------------------|------------------------------------------------------------------------------|

| Product Status          | Active                                                                       |

| Applications            | Capacitive Sensing                                                           |

| Core Processor          | M8C                                                                          |

| Program Memory Type     | FLASH (8kB)                                                                  |

| Controller Series       | CY8C20xx6A                                                                   |

| RAM Size                | 1K x 8                                                                       |

| Interface               | I <sup>2</sup> C, SPI                                                        |

| Number of I/O           | 36                                                                           |

| Voltage - Supply        | 1.71V ~ 5.5V                                                                 |

| Operating Temperature   | -40°C ~ 85°C                                                                 |

| Mounting Type           | Surface Mount                                                                |

| Package / Case          | 48-UFQFN Exposed Pad                                                         |

| Supplier Device Package | 48-QFN (6x6)                                                                 |

| Purchase URL            | https://www.e-xfl.com/product-detail/infineon-technologies/cy8c20636a-24lqxi |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## More Information

Cypress provides a wealth of data at www.cypress.com to help you to select the right PSoC device for your design, and to help you to quickly and effectively integrate the device into your design. For a comprehensive list of resources, see the knowledge base article KBA92181, Resources Available for CapSense® Controllers. Following is an abbreviated list for CapSense devices:

- Overview: CapSense Portfolio, CapSense Roadmap

- Product Selectors: CapSense, CapSense Plus, CapSense Express, PSoC3 with CapSense, PSoC5 with CapSense, PSoC4. In addition, PSoC Designer offers a device selection tool at the time of creating a new project.

- Application notes: Cypress offers CapSense application notes covering a broad range of topics, from basic to advanced level. Recommended application notes for getting started with CapSense are:

- □ AN64846: Getting Started With CapSense

- □ AN73034: CY8C20xx6A/H/AS CapSense® Design Guide

- □ AN2397: CapSense® Data Viewing Tools

- Technical Reference Manual (TRM):

- □ PSoC® CY8C20xx6A/AS/L Family Technical Reference Manual

## ■ Development Kits:

- □ CY3280-20x66 Universal CapSense Controller Kit features a predefined control circuitry and plug-in hardware to make prototyping and debugging easy. Programming and I2C-to-USB Bridge hardware are included for tuning and data acquisition.

- CY3280-BMM Matrix Button Module Kit consists of eight CapSense sensors organized in a 4x4 matrix format to form 16 physical buttons and eight LEDs. This module connects to any CY3280 Universal CapSense Controller Board, including CY3280-20x66 Universal CapSense Controller.

- □ CY3280-BSM Simple Button Module Kit consists of ten CapSense buttons and ten LEDs. This module connects to any CY3280 Universal CapSense Controller Board, including CY3280-20x66 Universal CapSense Controller.

The CY3217-MiniProg1 and CY8CKIT-002 PSoC® MiniProg3 device provides an interface for flash programming.

## **PSoC Designer**

PSoC Designer is a free Windows-based Integrated Design Environment (IDE). It enables concurrent hardware and firmware design of systems based on CapSense (see Figure 1). With PSoC Designer, you can:

- 1. Drag and drop User Modules to build your hardware system design in the main design workspace

- 2. Codesign your application firmware with the PSoC hardware, using the PSoC Designer IDE C compiler

- 3. Configure User Module

- 4. Explore the library of user modules

- 5. Review user module datasheets

Example\_CSD\_EzI2Cs\_Filters\_20xx6 - PSoC Designer 5.4 <u>File Edit View Project Interconnect Build Debug</u> Global Resources - example csd ezi2cs 20xx6

4 X IMO Setting CPU\_Clock 24MHz SysClk/2 Workspace 'Example\_CSD\_EzI2Cs\_Filters\_20xx6' (1 project)

Example\_CSD\_EzI2Cs\_Filters\_20xx6 [CY8C20666-24LTXI]

Example\_CSD\_EzI2Cs\_Filters\_20xx6 [Chip] 32K\_Select Internal ILO Setting 32kHz 512 Hz Loadable Configuration Interna 4.73V Disable Disable SysClk Source example\_csd\_ezi2cs\_20xx6 - 2 User Modules Example\_CSD\_EzI2Cs\_Filters\_20xx6 |

Example\_CSD\_EzI2Cs\_Filters\_20xx6 | Interrupt Mode P1[0] Data Output IMO Setting Selects the speed of the internal main oscillator (IMO) Registers Affected: CPU\_SCR1 IMO\_TR arameters - CSD Name User Module Part 2.0 cap Workspace Explorer Co FingerThreshold 100 Noise Threshold User Modules User Modules

ADCs

Amplifiers

Cap Sensors

Digital Comm ndicates the name used to identify this User Module instance Digital Com

Legacy

Misc Digital

MUXs

Protocols

RF CapSense® Sigma-Delta Datasheet ⊕ PO(0)

⊕ PO(1)

⊕ PO(2)

⊕ PO(3)

⊕ PO(4)

⊕ PO(6)

⊕ PO(6)

⊕ PO(7)

⊕ P1(0)

⊕ P1(1) Resources PSoC® Blocks Port 0 0, StdCPU, High Z Analog, I -Port 0 1. StdCPU. High Z Analog. I Port\_0\_2, StdCPU, High Z Analog, I Custom User Module CapSense® |2C/SP| Timer Comparator Flash RAM CSDCapacitor, Analog MUXINDUI, HI Port\_0\_4, StdCPU, High Z Analog, I Port\_0\_5, StdCPU, High Z Analog, I Port\_0\_6, StdCPU, High Z Analog, I Port\_0\_7, StdCPU, High Z Analog, I CY8C20x66A, CY8C20x36A, CY8C20x46A, CY8C20x96A, CY8C20xx6AS, User Module 1 1143 35 79 EzI2CsSDA, I2C SDA, Open Drain L EzI2CsSCL, I2C SCL, Open Drain Lo 10 Port\_1\_2, StdCPU, High Z Analog, I Port\_1\_3, StdCPU, High Z Analog, I

Figure 1. PSoC Designer Features

# PSoC® Functional Overview

The PSoC family consists of on-chip controller devices, which are designed to replace multiple traditional microcontroller unit (MCU)-based components with one, low cost single-chip programmable component. A PSoC device includes configurable analog and digital blocks, and programmable interconnect. This architecture allows the user to create customized peripheral configurations, to match the requirements of each individual application. Additionally, a fast CPU, Flash program memory, SRAM data memory, and configurable I/O are included in a range of convenient pinouts.

The architecture for this device family, as shown in the Logic Block Diagram on page 2, consists of three main areas:

- The Core

- CapSense Analog System

- System Resources (including a full-speed USB port).

A common, versatile bus allows connection between I/O and the analog system.

Each CY8C20XX6A/S PSoC device includes a dedicated CapSense block that provides sensing and scanning control circuitry for capacitive sensing applications. Depending on the PSoC package, up to 36 GPIO are also included. The GPIO provides access to the MCU and analog mux.

## **PSoC Core**

The PSoC Core is a powerful engine that supports a rich instruction set. It encompasses SRAM for data storage, an interrupt controller, sleep and watchdog timers, and IMO and ILO. The CPU core, called the M8C, is a powerful processor with speeds up to 24 MHz. The M8C is a 4-MIPS, 8-bit Harvard-architecture microprocessor.

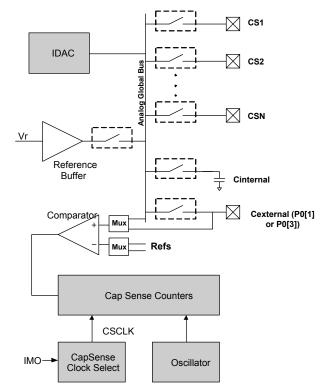

## CapSense System

The analog system contains the capacitive sensing hardware. Several hardware algorithms are supported. This hardware performs capacitive sensing and scanning without requiring external components. The analog system is composed of the CapSense PSoC block and an internal 1 V or 1.2 V analog reference, which together support capacitive sensing of up to 33 inputs <sup>[2]</sup>. Capacitive sensing is configurable on each GPIO pin. Scanning of enabled CapSense pins are completed quickly and easily across multiple ports.

## SmartSense

SmartSense is an innovative solution from Cypress that removes manual tuning of CapSense applications. This solution is easy to use and provides a robust noise immunity. It is the only auto-tuning solution that establishes, monitors, and maintains all

required tuning parameters. SmartSense allows engineers to go from prototyping to mass production without re-tuning for manufacturing variations in PCB and/or overlay material properties.

## SmartSense EMC

In addition to the SmartSense auto tuning algorithm to remove manual tuning of CapSense applications, SmartSense\_EMC user module incorporates a unique algorithm to improve robustness of capacitive sensing algorithm/circuit against high frequency conducted and radiated noise. Every electronic device must comply with specific limits for radiated and conducted external noise and these limits are specified by regulatory bodies (for example, FCC, CE, U/L and so on). A very good PCB layout design, power supply design and system design is a mandatory for a product to pass the conducted and radiated noise tests. An ideal PCB layout, power supply design or system design is not often possible because of cost and form factor limitations of the product. SmartSense\_EMC with superior noise immunity is well suited and handy for such applications to pass radiated and conducted noise test.

Figure 2. CapSense System Block Diagram

#### Note

<sup>2. 36</sup> GPIOs = 33 pins for capacitive sensing + 2 pins for  $I^2C$  + 1 pin for modulator capacitor.

# Getting Started

The quickest way to understand PSoC silicon is to read this datasheet and then use the PSoC Designer Integrated Development Environment (IDE). This datasheet is an overview of the PSoC integrated circuit and presents specific pin, register, and electrical specifications.

For in depth information, along with detailed programming details, see the Technical Reference Manual for the CY8C20XX6A/S PSoC devices.

For up-to-date ordering, packaging, and electrical specification information, see the latest PSoC device datasheets on the web at www.cypress.com/psoc.

# CapSense Design Guides

Design Guides are an excellent introduction to the wide variety of possible CapSense designs. They are located at www.cypress.com/go/CapSenseDesignGuides.

Refer Getting Started with CapSense design guide for information on CapSense design and CY8C20XX6A/H/AS CapSense<sup>®</sup> Design Guide for specific information on CY8C20XX6A/AS CapSense controllers.

#### Silicon Errata

Errata documents known issues with silicon including errata trigger conditions, scope of impact, available workarounds and silicon revision applicability. Refer to Silicon Errata for the PSoC® CY8C20x36A/46A/66A/96A/46AS/66AS/36H/46H families available at <a href="http://www.cypress.com/?rID=56239">http://www.cypress.com/?rID=56239</a> for errata information on CY8C20xx6A/AS/H family of device. Compare errata document with datasheet for a complete functional description of device.

## **Development Kits**

PSoC Development Kits are available online from and through a growing number of regional and global distributors, which include Arrow, Avnet, Digi-Key, Farnell, Future Electronics, and Newark.

## **Training**

Free PSoC technical training (on demand, webinars, and workshops), which is available online via www.cypress.com, covers a wide variety of topics and skill levels to assist you in your designs.

## **CYPros Consultants**

Certified PSoC consultants offer everything from technical assistance to completed PSoC designs. To contact or become a PSoC consultant go to the CYPros Consultants web site.

## **Solutions Library**

Visit our growing library of solution focused designs. Here you can find various application designs that include firmware and hardware design files that enable you to complete your designs quickly.

## **Technical Support**

Technical support – including a searchable Knowledge Base articles and technical forums – is also available online. If you cannot find an answer to your question, call our Technical Support hotline at 1-800-541-4736.

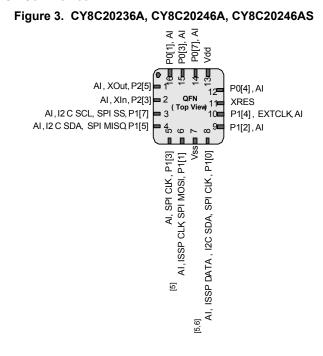

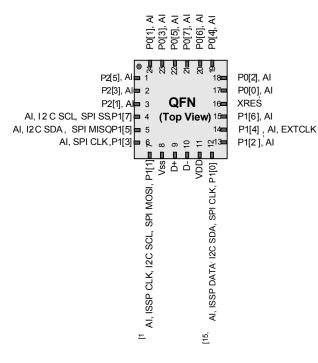

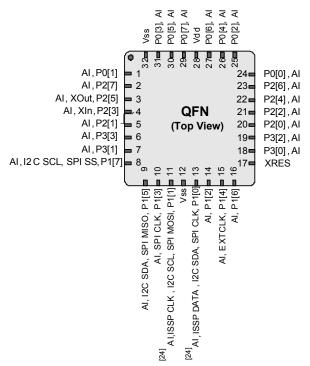

## **Pinouts**

The CY8C20XX6A/S PSoC device is available in a variety of packages, which are listed and illustrated in the following tables. Every port pin (labeled with a "P") is capable of Digital I/O and connection to the common analog bus. However,  $V_{SS}$ ,  $V_{DD}$ , and XRES are not capable of Digital I/O.

# 16-pin QFN (10 Sensing Inputs)[3, 4]

Table 1. Pin Definitions - CY8C20236A, CY8C20246A, CY8C20246AS PSoC Device

|     |         |        |          | •                                                                       |

|-----|---------|--------|----------|-------------------------------------------------------------------------|

| Pin | Ту      | pe     | Name     | Description                                                             |

| No. | Digital | Analog | Itallic  | Description                                                             |

| 1   | I/O     | I      | P2[5]    | Crystal output (XOut)                                                   |

| 2   | I/O     | Ĺ      | P2[3]    | Crystal input (XIn)                                                     |

| 3   | IOHR    | I      | P1[7]    | I <sup>2</sup> C SCL, SPI SS                                            |

| 4   | IOHR    | I      | P1[5]    | I <sup>2</sup> C SDA, SPI MISO                                          |

| 5   | IOHR    | I      | P1[3]    | SPI CLK                                                                 |

| 6   | IOHR    | I      | P1[1]    | ISSP CLK <sup>[5]</sup> , I <sup>2</sup> C SCL, SPI MOSI                |

| 7   | Po      | wer    | $V_{SS}$ | Ground connection <sup>[7]</sup>                                        |

| 8   | IOHR    | I      | P1[0]    | ISSP DATA <sup>[5]</sup> , I <sup>2</sup> C SDA, SPI CLK <sup>[6]</sup> |

| 9   | IOHR    | I      | P1[2]    |                                                                         |

| 10  | IOHR    | Ĺ      | P1[4]    | Optional external clock (EXTCLK)                                        |

| 11  | In      | put    | XRES     | Active high external reset with internal pull-down                      |

| 12  | IOH     | ĺ      | P0[4]    |                                                                         |

| 13  | Po      | wer    | $V_{DD}$ | Supply voltage                                                          |

| 14  | IOH     | I      | P0[7]    |                                                                         |

| 15  | IOH     | I      | P0[3]    | Integrating input                                                       |

| 16  | IOH     | I      | P0[1]    | Integrating input                                                       |

**LEGEND** A = Analog, I = Input, O = Output, OH = 5 mA High Output Drive, R = Regulated Output.

- 3. 13 GPIOs = 10 pins for capacitive sensing + 2 pins for I2C + 1 pin for modulation capacitor.

- 4. No Center Pad.

- On power-up, the SDA(P1[0]) drives a strong high for 256 sleep clock cycles and drives resistive low for the next 256 sleep clock cycles. The SCL(P1[1]) line drives resistive low for 512 sleep clock cycles and both the pins transition to high impedance state. On reset, after XRES de-asserts, the SDA and the SCL lines drive resistive low for 8 sleep clock cycles and transition to high impedance state. Hence, during power-up or reset event, P1[1] and P1[0] may disturb the I2C bus. Use alternate pins if you encounter issues.

- 6. Alternate SPI clock.

- 7. All VSS pins should be brought out to one common GND plane.

# 24-pin QFN (15 Sensing Inputs (With USB)) [13]

Table 3. Pin Definitions - CY8C20396A [14]

| Pin | Ту      | pe     | Name            | Description                                                                  |

|-----|---------|--------|-----------------|------------------------------------------------------------------------------|

| No. | Digital | Analog | Name            | Description                                                                  |

| 1   | I/O     | I      | P2[5]           |                                                                              |

| 2   | I/O     | I      | P2[3]           |                                                                              |

| 3   | I/O     | I      | P2[1]           |                                                                              |

| 4   | IOHR    | I      | P1[7]           | I <sup>2</sup> C SCL, SPI SS                                                 |

| 5   | IOHR    | I      | P1[5]           | I <sup>2</sup> C SDA, SPI MISO                                               |

| 6   | IOHR    | I      | P1[3]           | SPI CLK                                                                      |

| 7   | IOHR    | I      | P1[1]           | ISSP CLK <sup>[15]</sup> , I <sup>2</sup> C SCL, SPI<br>MOSI                 |

| 8   | Pov     | wer    | V <sub>SS</sub> | Ground <sup>[17]</sup>                                                       |

| 9   | I/O     | I      | D+              | USB D+                                                                       |

| 10  | I/O     | ı      | D-              | USB D-                                                                       |

| 11  | Pov     | wer    | $V_{DD}$        | Supply                                                                       |

| 12  | IOHR    | I      | P1[0]           | ISSP DATA <sup>[15]</sup> , I <sup>2</sup> C SDA, SPI<br>CLK <sup>[16]</sup> |

| 13  | IOHR    | I      | P1[2]           |                                                                              |

| 14  | IOHR    | I      | P1[4]           | Optional external clock input (EXTCLK)                                       |

| 15  | IOHR    | I      | P1[6]           |                                                                              |

| 16  | RESET   | INPUT  | XRES            | Active high external reset with internal pull-down                           |

| 17  | IOH     | I      | P0[0]           |                                                                              |

| 18  | IOH     | I      | P0[2]           |                                                                              |

| 19  | IOH     | I      | P0[4]           |                                                                              |

| 20  | IOH     | I      | P0[6]           |                                                                              |

| 21  | IOH     | I      | P0[7]           |                                                                              |

| 22  | IOH     | I      | P0[5]           |                                                                              |

| 23  | IOH     | I      | P0[3]           | Integrating input                                                            |

| 24  | IOH     | I      | P0[1]           | Integrating input                                                            |

| СР  | Pov     | wer    | V <sub>SS</sub> | Center pad must be connected to Ground                                       |

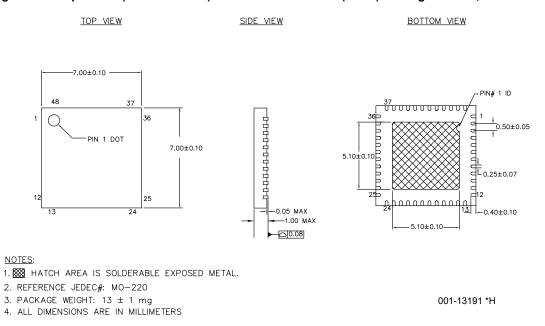

Figure 5. CY8C20396A

LEGEND I = Input, O = Output, OH = 5 mA High Output Drive, R = Regulated Output

- 13. 20 GPIOs = 15 pins for capacitive sensing + 2 pins for I2C + 2 pins for USB + 1 pin for modulation capacitor.

- 14. The center pad (CP) on the QFN package must be connected to ground (VSS) for best mechanical, thermal, and electrical performance. If not connected to ground,

- it must be electrically floated and not connected to any other signal.

15. On power-up, the SDA(P1[0]) drives a strong high for 256 sleep clock cycles and drives resistive low for 512 sleep clock cycles and both the pins transition to high impedance state. On reset, after XRES de-asserts, the SDA and the SCL lines drive resistive low for 8 sleep clock cycles and transition to high impedance state. Hence, during power-up or reset event, P1[1] and P1[0] may disturb the I2C bus. Use alternate pins if you encounter issues.

- 16. Alternate SPI clock.

- 17. All VSS pins should be brought out to one common GND plane.

# 32-pin QFN (25 Sensing Inputs) [22]

Table 5. Pin Definitions - CY8C20436A, CY8C20446A, CY8C20446AS, CY8C20466A, CY8C20466AS<sup>[23]</sup>

| Name                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Pin | Ty   | ре  |                 |                                                                              |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|-----|-----------------|------------------------------------------------------------------------------|--|

| 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     | _    |     | Name            | Description                                                                  |  |

| 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1   | IOH  | I   | P0[1]           | Integrating input                                                            |  |

| 1/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 2   | I/O  | I   | P2[7]           |                                                                              |  |

| 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 3   | I/O  | ı   | P2[5]           | Crystal output (XOut)                                                        |  |

| 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 4   | I/O  | ı   | P2[3]           | Crystal input (XIn)                                                          |  |

| 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 5   | I/O  | ı   | P2[1]           |                                                                              |  |

| 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 6   | I/O  | ı   | P3[3]           |                                                                              |  |

| 9 IOHR I P1[5] I <sup>2</sup> C SDA, SPI MISO  10 IOHR I P1[3] SPI CLK.  11 IOHR I P1[1] ISSP CLK <sup>[24]</sup> , I <sup>2</sup> C SCL, SPI MOSI  12 Power V <sub>SS</sub> Ground connection <sup>[26]</sup> 13 IOHR I P1[0] ISSP DATA <sup>[24]</sup> , I <sup>2</sup> C SDA, SPI CLK <sup>[25]</sup> 14 IOHR I P1[2]  15 IOHR I P1[6]  17 Input XRES Active high external clock input (EXTCLK)  18 I/O I P3[0]  19 I/O I P3[0]  20 I/O I P2[0]  21 I/O I P2[1]  22 I/O I P2[2]  23 I/O I P2[6]  24 IOH I P0[0]  25 IOH I P0[2]  26 IOH I P0[2]  27 IOH I P0[6]  28 Power V <sub>DD</sub> Supply voltage  29 IOH I P0[5]  31 IOH I P0[3] Integrating input  32 Power V <sub>SS</sub> Ground connection <sup>[26]</sup> CR Power V <sub>SS</sub> Ground connection <sup>[26]</sup> Center pad must be connected to | 7   | I/O  | ı   | P3[1]           |                                                                              |  |

| 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 8   | IOHR | I   | P1[7]           | I <sup>2</sup> C SCL, SPI SS                                                 |  |

| 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 9   | IOHR | I   | P1[5]           | I <sup>2</sup> C SDA, SPI MISO                                               |  |

| 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 10  | IOHR | ı   | P1[3]           |                                                                              |  |

| 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 11  | IOHR | I   | P1[1]           | ISSP CLK <sup>[24]</sup> , I <sup>2</sup> C SCL, SPI MOSI.                   |  |

| 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 12  | Po   | wer | $V_{SS}$        | Ground connection <sup>[26]</sup>                                            |  |

| 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 13  | IOHR | I   | P1[0]           | ISSP DATA <sup>[24]</sup> , I <sup>2</sup> C SDA,<br>SPI CLK <sup>[25]</sup> |  |

| 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 14  | IOHR | I   | P1[2]           |                                                                              |  |

| 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 15  | IOHR | I   | P1[4]           |                                                                              |  |

| 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 16  | IOHR | I   | P1[6]           |                                                                              |  |

| 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 17  | Inj  | out | XRES            |                                                                              |  |

| 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 18  | I/O  | I   | P3[0]           |                                                                              |  |

| 21         I/O         I         P2[2]           22         I/O         I         P2[4]           23         I/O         I         P2[6]           24         IOH         I         P0[0]           25         IOH         I         P0[2]           26         IOH         I         P0[4]           27         IOH         I         P0[6]           28         Power         V <sub>DD</sub> Supply voltage           29         IOH         I         P0[7]           30         IOH         I         P0[5]           31         IOH         I         P0[3]         Integrating input           32         Power         V <sub>SS</sub> Ground connection[26]           CP         Power         V <sub>C</sub> Center pad must be connected to                                                               | 19  | I/O  | I   | P3[2]           |                                                                              |  |

| 22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 20  | I/O  | I   | P2[0]           |                                                                              |  |

| 23    I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 21  | I/O  | I   | P2[2]           |                                                                              |  |

| 24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 22  | I/O  | I   | P2[4]           |                                                                              |  |

| 25         IOH         I         P0[2]           26         IOH         I         P0[4]           27         IOH         I         P0[6]           28         Power         V <sub>DD</sub> Supply voltage           29         IOH         I         P0[7]           30         IOH         I         P0[5]           31         IOH         I         P0[3]         Integrating input           32         Power         V <sub>SS</sub> Ground connection[26]           CP         Power         V <sub>C</sub> Center pad must be connected to                                                                                                                                                                                                                                                                   | 23  | I/O  | I   | P2[6]           |                                                                              |  |

| 26         IOH         I         P0[4]           27         IOH         I         P0[6]           28         Power         V <sub>DD</sub> Supply voltage           29         IOH         I         P0[7]           30         IOH         I         P0[5]           31         IOH         I         P0[3]         Integrating input           32         Power         V <sub>SS</sub> Ground connection[26]           CP         Power         V <sub>C</sub> Center pad must be connected to                                                                                                                                                                                                                                                                                                                    | 24  | IOH  | I   | P0[0]           |                                                                              |  |

| 27         IOH         I         P0[6]           28         Power         V <sub>DD</sub> Supply voltage           29         IOH         I         P0[7]           30         IOH         I         P0[5]           31         IOH         I         P0[3]         Integrating input           32         Power         V <sub>SS</sub> Ground connection[26]           CP         Power         V <sub>C</sub> Center pad must be connected to                                                                                                                                                                                                                                                                                                                                                                     | 25  | IOH  | I   | P0[2]           |                                                                              |  |

| 28         Power         V <sub>DD</sub> Supply voltage           29         IOH         I         P0[7]           30         IOH         I         P0[5]           31         IOH         I         P0[3]         Integrating input           32         Power         V <sub>SS</sub> Ground connection[26]           CR         Power         V <sub>C</sub> Center pad must be connected to                                                                                                                                                                                                                                                                                                                                                                                                                      | 26  | IOH  | I   | P0[4]           |                                                                              |  |

| 29         IOH         I         P0[7]           30         IOH         I         P0[5]           31         IOH         I         P0[3]         Integrating input           32         Power         V <sub>SS</sub> Ground connection <sup>[26]</sup> CP         Power         V <sub>C</sub> Center pad must be connected to                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 27  | IOH  | I   | P0[6]           |                                                                              |  |

| 30 IOH I P0[5] 31 IOH I P0[3] Integrating input 32 Power V <sub>SS</sub> Ground connection <sup>[26]</sup> CP Power V <sub>S</sub> Center pad must be connected to                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 28  | Po   | wer | $V_{DD}$        | Supply voltage                                                               |  |

| 31 IOH I P0[3] Integrating input 32 Power V <sub>SS</sub> Ground connection <sup>[26]</sup> CP Power V <sub>C</sub> Center pad must be connected to                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 29  | IOH  | I   | P0[7]           |                                                                              |  |

| 32 Power V <sub>SS</sub> Ground connection <sup>[26]</sup> CP Power V Center pad must be connected to                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 30  | IOH  | I   | P0[5]           |                                                                              |  |

| CP Power Vac Center pad must be connected to                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 31  | IOH  | I   | P0[3]           | Integrating input                                                            |  |

| CP Power V Center pad must be connected to                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 32  | Po   | wer | V <sub>SS</sub> | Ground connection <sup>[26]</sup>                                            |  |

| 9,04,14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | СР  | Po   | wer | V <sub>SS</sub> | Center pad must be connected to ground                                       |  |

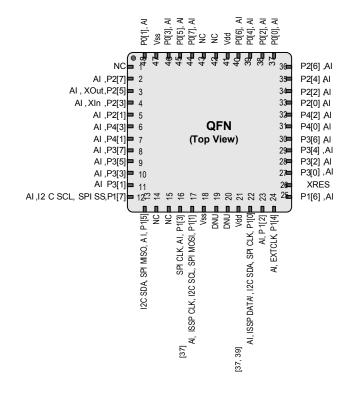

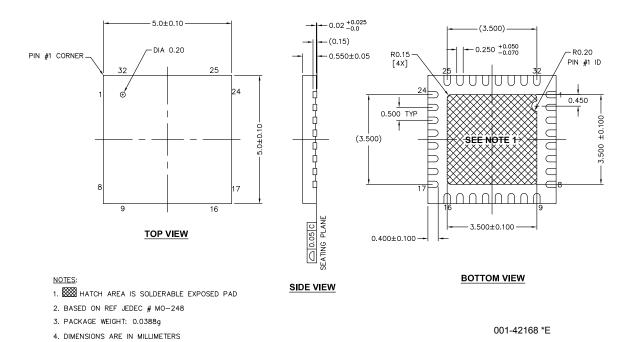

Figure 7. CY8C20436A, CY8C20446A, CY8C20446AS, CY8C20466A, CY8C20466AS

**LEGEND** A = Analog, I = Input, O = Output, OH = 5 mA High Output Drive, R = Regulated Output.

- 22. 28 GPIOs = 25 pins for capacitive sensing + 2 pins for I2C + 1 pin for modulation capacitor.

- 23. The center pad (CP) on the QFN package must be connected to ground (V<sub>SS</sub>) for best mechanical, thermal, and electrical performance. If not connected to ground, it must be electrically floated and not connected to any other signal.

- 24. On power-up, the SDA(P1[0]) drives a strong high for 256 sleep clock cycles and drives resistive low for the next 256 sleep clock cycles. The SCL(P1[1]) line drives resistive low for 512 sleep clock cycles and both the pins transition to high impedance state. On reset, after XRES de-asserts, the SDA and the SCL lines drive resistive low for 8 sleep clock cycles and transition to high impedance state. Hence, during power-up or reset event, P1[1] and P1[0] may disturb the I2C bus. Use alternate pins if you encounter issues.

- 25. Alternate SPI clock.

- 26. All VSS pins should be brought out to one common GND plane.

# 48-pin QFN (33 Sensing Inputs) [36]

# Table 8. Pin Definitions - CY8C20636A<sup>[37, 38]</sup>

| Pin<br>No. | Digital | Analog | Name     | Description                                                                  |

|------------|---------|--------|----------|------------------------------------------------------------------------------|

| 1          |         |        | NC       | No connection                                                                |

| 2          | I/O     | ı      | P2[7]    |                                                                              |

| 3          | I/O     |        | P2[5]    | Crystal output (XOut)                                                        |

| 4          | I/O     |        | P2[3]    | Crystal input (XIn)                                                          |

| 5          | I/O     |        | P2[1]    |                                                                              |

| 6          | I/O     |        | P4[3]    |                                                                              |

| 7          | I/O     |        | P4[1]    |                                                                              |

| 8          | I/O     |        | P3[7]    |                                                                              |

| 9          | I/O     |        | P3[5]    |                                                                              |

| 10         | I/O     |        | P3[3]    |                                                                              |

| 11         | I/O     |        | P3[1]    |                                                                              |

| 12         | IOHR    |        | P1[7]    | I <sup>2</sup> C SCL, SPI SS                                                 |

| 13         | IOHR    |        | P1[5]    | I <sup>2</sup> C SDA, SPI MISO                                               |

| 14         |         |        | NC       | No connection                                                                |

| 15         |         |        | NC       | No connection                                                                |

| 16         | IOHR    |        | P1[3]    | SPI CLK                                                                      |

| 17         | IOHR    | I      | P1[1]    | ISSP CLK <sup>[37]</sup> , I <sup>2</sup> C SCL, SPI<br>MOSI                 |

| 18         | Po      | wer    | $V_{SS}$ | Ground connection <sup>[40]</sup>                                            |

| 19         |         |        | DNU      |                                                                              |

| 20         |         |        | DNU      |                                                                              |

| 21         | Po      | wer    | $V_{DD}$ | Supply voltage                                                               |

| 22         | IOHR    | I      | P1[0]    | ISSP DATA <sup>[37]</sup> , I <sup>2</sup> C SDA, SPI<br>CLK <sup>[39]</sup> |

| 23         | IOHR    | ı      | P1[2]    |                                                                              |

| 24         | IOHR    | I      | P1[4]    | Optional external clock input (EXTCLK)                                       |

| 25         | IOHR    |        | P1[6]    |                                                                              |

| 26         | In      | put    | XRES     | Active high external reset with internal pull-down                           |

| 27         | I/O     | ı      | P3[0]    |                                                                              |

| 28         | I/O     | ı      | P3[2]    |                                                                              |

| 29         | I/O     | I      | P3[4]    |                                                                              |

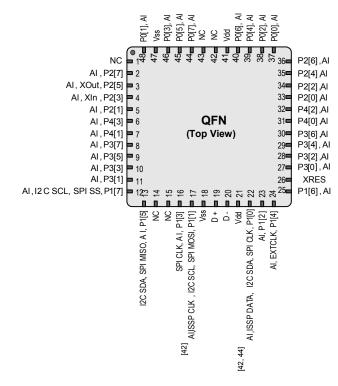

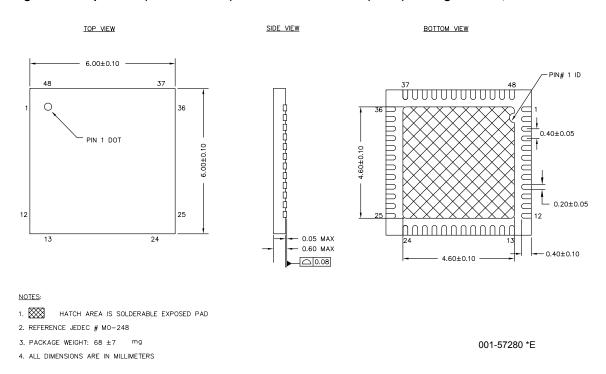

## Figure 10. CY8C20636A

| 28 | I/O | ı | P3[2] |   |            |                                 |               |             |                                        |

|----|-----|---|-------|---|------------|---------------------------------|---------------|-------------|----------------------------------------|

| 29 | I/O | I | P3[4] |   | Pin<br>No. | Digital Analog Name Description |               | Description |                                        |

| 30 | I/O | ı | P3[6] | 4 | 40         | IOH                             | 1             | P0[6]       |                                        |

| 31 | I/O | ı | P4[0] | 4 | 41         | Po                              | wer           | $V_{DD}$    | Supply voltage                         |

| 32 | I/O | I | P4[2] | 4 | 12         |                                 | No connection |             |                                        |

| 33 | I/O | ı | P2[0] | 4 | 43         |                                 |               | NC          | No connection                          |

| 34 | I/O | ı | P2[2] | 4 | 14         | IOH                             |               | P0[7]       |                                        |

| 35 | I/O | ı | P2[4] | 4 | 45         | IOH                             |               | P0[5]       |                                        |

| 36 | I/O | ı | P2[6] | 4 | 16         | IOH                             |               | P0[3]       | Integrating input                      |

| 37 | IOH | I | P0[0] | 4 | 17         | Power                           |               | $V_{SS}$    | Ground connection <sup>[40]</sup>      |

| 38 | IOH | ı | P0[2] | 4 | 48         | IOH I                           |               | P0[1]       |                                        |

| 39 | IOH |   | P0[4] |   | CP         | Po                              | wer           | $V_{SS}$    | Center pad must be connected to ground |

LEGEND A = Analog, I = Input, O = Output, NC = No Connection H = 5 mA High Output Drive, R = Regulated Output.

- 36. 36 GPIOs = 33 pins for capacitive sensing + 2 pins for I2C + 1 pin for modulation capacitor.

- 37. On power-up, the SDA(P1[0]) drives a strong high for 256 sleep clock cycles and drives resistive low for the next 256 sleep clock cycles. The SCL(P1[1]) line drives resistive low for 512 sleep clock cycles and both the pins transition to high impedance state. On reset, after XRES de-asserts, the SDA and the SCL lines drive resistive low for 8 sleep clock cycles and transition to high impedance state. Hence, during power-up or reset event, P1[1] and P1[0] may disturb the I2C bus. Use alternate pins if you encounter issues.

- 38. The center pad (CP) on the QFN package must be connected to ground (V<sub>SS</sub>) for best mechanical, thermal, and electrical performance. If not connected to ground, it must be electrically floated and not connected to any other signal

- 39. Alternate SPI clock

- 40. All VSS pins should be brought out to one common GND plane.

# 48-pin QFN (33 Sensing Inputs (With USB)) [41]

# Table 9. Pin Definitions - CY8C20646A, CY8C20646AS, CY8C20666A, CY8C20666AS [42, 43]

| Pin<br>No. | Digital | Analog | Name            | Description                                                                  |

|------------|---------|--------|-----------------|------------------------------------------------------------------------------|

| 1          |         | I      | NC              | No connection                                                                |

| 2          | I/O     | ı      | P2[7]           |                                                                              |

| 3          | I/O     | ı      | P2[5]           | Crystal output (XOut)                                                        |

| 4          | I/O     | ı      | P2[3]           | Crystal input (XIn)                                                          |

| 5          | I/O     | ı      | P2[1]           |                                                                              |

| 6          | I/O     | ı      | P4[3]           |                                                                              |

| 7          | I/O     | ı      | P4[1]           |                                                                              |

| 8          | I/O     | ı      | P3[7]           |                                                                              |

| 9          | I/O     | ı      | P3[5]           |                                                                              |

| 10         | I/O     | ı      | P3[3]           |                                                                              |

| 11         | I/O     | ı      | P3[1]           |                                                                              |

| 12         | IOHR    | ı      | P1[7]           | I <sup>2</sup> C SCL, SPI SS                                                 |

| 13         | IOHR    | ı      | P1[5]           | I <sup>2</sup> C SDA, SPI MISO                                               |

| 14         |         |        | NC              | No connection                                                                |

| 15         |         |        | NC              | No connection                                                                |

| 16         | IOHR    | ı      | P1[3]           | SPI CLK                                                                      |

| 17         | IOHR    | ı      | P1[1]           | ISSP CLK <sup>[42]</sup> , I <sup>2</sup> C SCL, SPI MOSI                    |

| 18         | Po      | wer    | V <sub>SS</sub> | Ground connection[45]                                                        |

| 19         | I/O     |        | D+              | USB D+                                                                       |

| 20         | I/O     |        | D-              | USB D-                                                                       |

| 21         | Po      | wer    | $V_{DD}$        | Supply voltage                                                               |

| 22         | IOHR    | I      | P1[0]           | ISSP DATA <sup>[42]</sup> , I <sup>2</sup> C SDA, SPI<br>CLK <sup>[44]</sup> |

| 23         | IOHR    | ı      | P1[2]           |                                                                              |

| 24         | IOHR    | I      | P1[4]           | Optional external clock input (EXTCLK)                                       |

| 25         | IOHR    | I      | P1[6]           |                                                                              |

| 26         | In      | put    | XRES            | Active high external reset with internal pull-down                           |

| 27         | I/O     | ı      | P3[0]           |                                                                              |

| 28         | I/O     | ı      | P3[2]           |                                                                              |

| 29         | I/O     | I      | P3[4]           |                                                                              |

| 30         | I/O     | ı      | P3[6]           |                                                                              |

| 21         | 1/0     | i .    | DAIOI           |                                                                              |

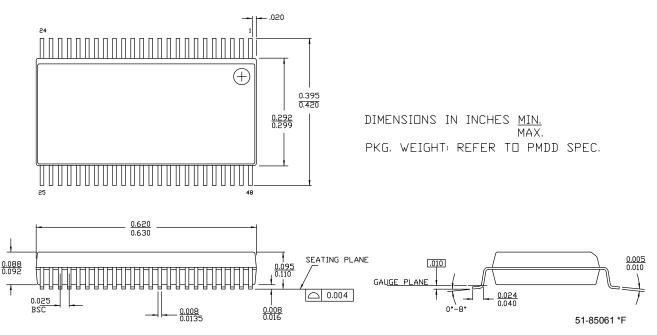

Figure 11. CY8C20646A, CY8C20646AS, CY8C20666A, CY8C20666AS

| 28 | I/O | ı | P3[2] |            |                                                         |                  |          |                   |  |

|----|-----|---|-------|------------|---------------------------------------------------------|------------------|----------|-------------------|--|

| 29 | I/O | I | P3[4] | Pin<br>No. |                                                         |                  |          | Description       |  |

| 30 | I/O | ı | P3[6] | 40         | IOH                                                     | I                | P0[6]    |                   |  |

| 31 | I/O | ı | P4[0] | 41         | P                                                       | ower             | $V_{DD}$ | Supply voltage    |  |

| 32 | I/O | ı | P4[2] | 42         |                                                         |                  | NC       | No connection     |  |

| 33 | I/O | ı | P2[0] | 43         |                                                         | NC No connection |          |                   |  |

| 34 | I/O | ı | P2[2] | 44         | IOH                                                     | I                | P0[7]    |                   |  |

| 35 | I/O | ı | P2[4] | 45         | IOH                                                     | IOH I P0[5]      |          |                   |  |

| 36 | I/O | ı | P2[6] | 46         | IOH                                                     | I                | P0[3]    | Integrating input |  |

| 37 | IOH | ı | P0[0] | 47         | Power V <sub>SS</sub> Ground connection <sup>[45]</sup> |                  |          |                   |  |

| 38 | IOH | ı | P0[2] | 48         |                                                         |                  |          |                   |  |

| 39 | IOH | ı | P0[4] | СР         |                                                         |                  |          |                   |  |

**LEGEND** A = Analog, I = Input, O = Output, NC = No Connection H = 5 mA High Output Drive, R = Regulated Output.

- 41.38 GPIOs = 33 pins for capacitive sensing + 2 pins for I2C + 2 pins for USB + 1 pin for modulation capacitor.

- 42. On Power-up, the SDA(P1[0]) drives a strong high for 256 sleep clock cycles and drives resistive low for the next 256 sleep clock cycles. The SCL(P1[1]) line drives resistive low for 512 sleep clock cycles and both the pins transition to High impedance state. On reset, after XRES de- asserts, the SDA and the SCL lines drive resistive low for 8 sleep clock cycles and transition to high impedance state. In both cases, a pull-up resistance on these lines combines with the pull-down resistance (5.6K ohm) and form a potential divider. Hence, during power-up or reset event, P1[1] and P1[0] may disturb the I2C bus. Use alternate pins if you encounter issues.

- 43. The center pad (CP) on the QFN package must be connected to ground (V<sub>SS</sub>) for best mechanical, thermal, and electrical performance. If not connected to ground, it must be electrically floated and not connected to any other signal.

- 44. Alternate SPI clock.

- 45. All VSS pins should be brought out to one common GND plane.

# **DC GPIO Specifications**

The following tables list guaranteed maximum and minimum specifications for the voltage and temperature ranges: 3.0 V to 5.5 V and  $-40~^{\circ}\text{C} \le T_{A} \le 85~^{\circ}\text{C}$ , 2.4 V to 3.0 V and  $-40~^{\circ}\text{C} \le T_{A} \le 85~^{\circ}\text{C}$ , or 1.71 V to 2.4 V and  $-40~^{\circ}\text{C} \le T_{A} \le 85~^{\circ}\text{C}$ , respectively. Typical parameters apply to 5 V and 3.3 V at 25 C and are for design guidance only.

Table 14. 3.0 V to 5.5 V DC GPIO Specifications

| Symbol                | Description                                                                       | Conditions                                                                                                                                                                                | Min                    | Тур   | Max  | Units |

|-----------------------|-----------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|-------|------|-------|

| R <sub>PU</sub>       | Pull-up resistor                                                                  | -                                                                                                                                                                                         | 4                      | 5.60  | 8    | kΩ    |

| V <sub>OH1</sub>      | High output voltage<br>Port 2 or 3 or 4 pins                                      | $I_{OH} \le 10~\mu A$ , maximum of 10 mA source current in all I/Os                                                                                                                       | V <sub>DD</sub> – 0.20 | -     | -    | V     |

| V <sub>OH2</sub>      | High output voltage<br>Port 2 or 3 or 4 pins                                      | I <sub>OH</sub> = 1 mA, maximum of 20 mA source current in all I/Os                                                                                                                       | V <sub>DD</sub> – 0.90 | -     | -    | V     |

| V <sub>OH3</sub>      | High output voltage<br>Port 0 or 1 pins with LDO regulator<br>Disabled for port 1 | $I_{OH}$ < 10 $\mu$ A, maximum of 10 mA source current in all I/Os                                                                                                                        | V <sub>DD</sub> – 0.20 | _     | -    | V     |

| V <sub>OH4</sub>      | High output voltage<br>Port 0 or 1 pins with LDO regulator<br>Disabled for port 1 | I <sub>OH</sub> = 5 mA, maximum of 20 mA source current in all I/Os                                                                                                                       | V <sub>DD</sub> – 0.90 | _     | -    | V     |

| V <sub>OH5</sub>      | High output voltage<br>Port 1 Pins with LDO Regulator Enabled<br>for 3 V out      | $I_{OH}$ < 10 $\mu$ A, $V_{DD}$ > 3.1 V, maximum of 4 I/Os all sourcing 5 mA                                                                                                              | 2.85                   | 3.00  | 3.30 | V     |

| V <sub>OH6</sub>      | High output voltage<br>Port 1 pins with LDO regulator enabled for<br>3 V out      | I <sub>OH</sub> = 5 mA, V <sub>DD</sub> > 3.1 V, maximum of 20 mA source current in all I/Os                                                                                              | 2.20                   | _     | -    | V     |

| V <sub>OH7</sub>      | High output voltage<br>Port 1 pins with LDO enabled for 2.5 V out                 | $I_{OH}\!<\!10\mu\text{A},V_{DD}\!>\!2.7\text{V},\text{maximum}\text{of}20\text{mA}$ source current in all I/Os                                                                           | 2.35                   | 2.50  | 2.75 | V     |

| V <sub>OH8</sub>      | High output voltage<br>Port 1 pins with LDO enabled for 2.5 V out                 | $I_{OH}$ = 2 mA, $V_{DD}$ > 2.7 V, maximum of 20 mA source current in all I/Os                                                                                                            | 1.90                   | -     | -    | V     |

| V <sub>OH9</sub>      | High output voltage<br>Port 1 pins with LDO enabled for 1.8 V out                 | $I_{OH}$ < 10 $\mu$ A, $V_{DD}$ > 2.7 V, maximum of 20 mA source current in all I/Os                                                                                                      | 1.60                   | 1.80  | 2.10 | V     |

| V <sub>OH10</sub>     | High output voltage<br>Port 1 pins with LDO enabled for 1.8 V out                 | $I_{OH}$ = 1 mA, $V_{DD}$ > 2.7 V, maximum of 20 mA source current in all I/Os                                                                                                            | 1.20                   | -     | -    | V     |

| V <sub>OL</sub>       | Low output voltage                                                                | $I_{OL}$ = 25 mA, $V_{DD}$ > 3.3 V, maximum of 60 mA sink current on even port pins (for example, P0[2] and P1[4]) and 60 mA sink current on odd port pins (for example, P0[3] and P1[5]) | _                      | -     | 0.75 | V     |

| V <sub>IL</sub>       | Input low voltage                                                                 | -                                                                                                                                                                                         | -                      | -     | 0.80 | V     |

| V <sub>IH</sub>       | Input high voltage                                                                | -                                                                                                                                                                                         | 2.00                   | _     | _    | V     |

| V <sub>H</sub>        | Input hysteresis voltage                                                          | -                                                                                                                                                                                         | -                      | 80    | _    | mV    |

| $I_{\rm IL}$          | Input leakage (Absolute Value)                                                    | _                                                                                                                                                                                         | -                      | 0.001 | 1    | μА    |

| C <sub>PIN</sub>      | Pin capacitance                                                                   | Package and pin dependent<br>Temp = 25 °C                                                                                                                                                 | 0.50                   | 1.70  | 7    | pF    |

| V <sub>ILLVT3.3</sub> | Input Low Voltage with low threshold enable set, Enable for Port1                 | Bit3 of IO_CFG1 set to enable low threshold voltage of Port1 input                                                                                                                        | 0.8                    | V     | ı    | _     |

| V <sub>IHLVT3.3</sub> | Input High Voltage with low threshold enable set, Enable for Port1                | Bit3 of IO_CFG1 set to enable low threshold voltage of Port1 input                                                                                                                        | 1.4                    | -     | _    | V     |

| V <sub>ILLVT5.5</sub> | Input Low Voltage with low threshold enable set, Enable for Port1                 | Bit3 of IO_CFG1 set to enable low threshold voltage of Port1 input                                                                                                                        | 0.8                    | V     | -    | -     |