# E·XFL

#### Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Product Status             | Obsolete                                                                |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | HC11                                                                    |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 3MHz                                                                    |

| Connectivity               | SCI, SPI                                                                |

| Peripherals                | POR, WDT                                                                |

| Number of I/O              | 38                                                                      |

| Program Memory Size        | -                                                                       |

| Program Memory Type        | ROMIess                                                                 |

| EEPROM Size                | 512 x 8                                                                 |

| RAM Size                   | 512 x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                             |

| Data Converters            | A/D 8x8b                                                                |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 52-LCC (J-Lead)                                                         |

| Supplier Device Package    | 52-PLCC (19.1x19.1)                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc68hc11e1cfne3 |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### General Description

- Computer operating properly (COP) watchdog system

- 38 general-purpose input/output (I/O) pins:

- 16 bidirectional I/O pins

- 11 input-only pins

- 11 output-only pins

- Several packaging options:

- 52-pin plastic-leaded chip carrier (PLCC)

- 52-pin windowed ceramic leaded chip carrier (CLCC)

- 52-pin plastic thin quad flat pack, 10 mm x 10 mm (TQFP)

- 64-pin quad flat pack (QFP)

- 48-pin plastic dual in-line package (DIP), MC68HC811E2 only

- 56-pin plastic shrink dual in-line package, .070-inch lead spacing (SDIP)

# 1.3 Structure

See Figure 1-1 for a functional diagram of the E-series MCUs. Differences among devices are noted in the table accompanying Figure 1-1.

# **1.4 Pin Descriptions**

M68HC11 E-series MCUs are available packaged in:

- 52-pin plastic-leaded chip carrier (PLCC)

- 52-pin windowed ceramic leaded chip carrier (CLCC)

- 52-pin plastic thin quad flat pack, 10 mm x 10 mm (TQFP)

- 64-pin quad flat pack (QFP)

- 48-pin plastic dual in-line package (DIP), MC68HC811E2 only

- 56-pin plastic shrink dual in-line package, .070-inch lead spacing (SDIP)

Most pins on these MCUs serve two or more functions, as described in the following paragraphs. Refer to Figure 1-2, Figure 1-3, Figure 1-4, Figure 1-5, and Figure 1-6 which show the M68HC11 E-series pin assignments for the PLCC/CLCC, QFP, TQFP, SDIP, and DIP packages.

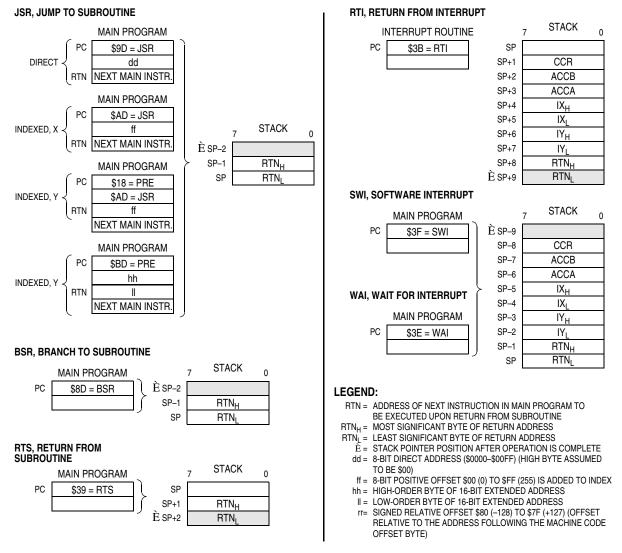

At the end of the interrupt service routine, an return-from interrupt (RTI) instruction is executed. The RTI instruction causes the saved registers to be pulled off the stack in reverse order. Program execution resumes at the return address.

Certain instructions push and pull the A and B accumulators and the X and Y index registers and are often used to preserve program context. For example, pushing accumulator A onto the stack when entering a subroutine that uses accumulator A and then pulling accumulator A off the stack just before leaving the subroutine ensures that the contents of a register will be the same after returning from the subroutine as it was before starting the subroutine.

Figure 4-2. Stacking Operations

| Mnemonic   | Operation                        | Description                                | A                     | ddressing                           |                            |                            | stru                       | ction    |                       |   |   | C | onditio | on Co |   |   |   |

|------------|----------------------------------|--------------------------------------------|-----------------------|-------------------------------------|----------------------------|----------------------------|----------------------------|----------|-----------------------|---|---|---|---------|-------|---|---|---|

|            | operation                        | -                                          |                       | Mode                                | 0                          | pcode                      | Ор                         | erand    | Cycles                | s | Х | Н | I       | Ν     | Z | V | С |

| INCB       | Increment<br>Accumulator<br>B    | B + 1 ⇒ B                                  | В                     | INH                                 |                            | 5C                         |                            | _        | 2                     | _ | _ | _ | _       | Δ     | Δ | Δ | _ |

| INS        | Increment<br>Stack Pointer       | $SP + 1 \Rightarrow SP$                    |                       | INH                                 |                            | 31                         |                            | _        | 3                     | — | — | _ |         | —     | _ | _ | _ |

| INX        | Increment<br>Index Register<br>X | $IX + 1 \Rightarrow IX$                    |                       | INH                                 |                            | 08                         |                            | _        | 3                     | _ | _ | _ | _       | _     | Δ | _ | _ |

| INY        | Increment<br>Index Register<br>Y | $IY + 1 \Rightarrow IY$                    |                       | INH                                 | 18                         | 08                         |                            | _        | 4                     | _ | _ | _ | _       | _     | Δ | _ |   |

| JMP (opr)  | Jump                             | See Figure 3–2                             |                       | EXT<br>IND,X<br>IND,Y               | 18                         | 7E<br>6E<br>6E             | hh<br>ff<br>ff             | 11       | 3<br>3<br>4           | _ | _ | _ | _       | _     | _ | _ |   |

| JSR (opr)  | Jump to<br>Subroutine            | See Figure 3–2                             |                       | DIR<br>EXT<br>IND,X<br>IND,Y        | 18                         | 9D<br>BD<br>AD<br>AD       | dd<br>hh<br>ff<br>ff       | 11       | 5<br>6<br>6<br>7      | _ | _ | _ | _       | -     | _ | _ | - |

| LDAA (opr) | Load<br>Accumulator<br>A         | $M \Rightarrow A$                          | A<br>A<br>A<br>A      | IMM<br>DIR<br>EXT<br>IND,X<br>IND,Y | 18                         | 86<br>96<br>B6<br>A6<br>A6 | ii<br>dd<br>hh<br>ff<br>ff | 11       | 2<br>3<br>4<br>4<br>5 | _ | _ | _ | _       | Δ     | Δ | 0 |   |

| LDAB (opr) | Load<br>Accumulator<br>B         | $M \Rightarrow B$                          | B<br>B<br>B<br>B<br>B | IMM<br>DIR<br>EXT<br>IND,X<br>IND,Y | 18                         | C6<br>D6<br>F6<br>E6<br>E6 | ii<br>dd<br>hh<br>ff<br>ff | 11       | 2<br>3<br>4<br>4<br>5 | _ | _ | _ | _       | Δ     | Δ | 0 |   |

| LDD (opr)  | Load Double<br>Accumulator<br>D  | $M \Rightarrow A, M + 1 \Rightarrow B$     |                       | IMM<br>DIR<br>EXT<br>IND,X<br>IND,Y | 18                         | CC<br>DC<br>FC<br>EC<br>EC | jj<br>dd<br>hh<br>ff<br>ff | kk<br>11 | 3<br>4<br>5<br>5<br>6 | _ | _ | _ | _       | Δ     | Δ | 0 | _ |

| LDS (opr)  | Load Stack<br>Pointer            | $M: M + 1 \Rightarrow SP$                  |                       | IMM<br>DIR<br>EXT<br>IND,X<br>IND,Y | 18                         | 8E<br>9E<br>AE<br>AE       | jj<br>dd<br>hh<br>ff<br>ff | kk<br>11 | 3<br>4<br>5<br>5<br>6 | _ | _ | - | _       | Δ     | Δ | 0 |   |

| LDX (opr)  | Load Index<br>Register<br>X      | $M:M+1\RightarrowIX$                       |                       | IMM<br>DIR<br>EXT<br>IND,X<br>IND,Y | CD                         | CE<br>DE<br>FE<br>EE<br>EE | jj<br>dd<br>hh<br>ff<br>ff | kk<br>11 | 3<br>4<br>5<br>5<br>6 | _ | _ | _ | _       | Δ     | Δ | 0 |   |

| LDY (opr)  | Load Index<br>Register<br>Y      | $M:M+1\RightarrowIY$                       |                       | IMM<br>DIR<br>EXT<br>IND,X<br>IND,Y | 18<br>18<br>18<br>1A<br>18 | CE<br>DE<br>FE<br>EE<br>EE | jj<br>dd<br>hh<br>ff<br>ff | kk<br>11 | 4<br>5<br>6<br>6<br>6 | _ | _ | _ | _       | Δ     | Δ | 0 |   |

| LSL (opr)  | Logical Shift<br>Left            |                                            |                       | EXT<br>IND,X<br>IND,Y               | 18                         | 78<br>68<br>68             | hh<br>ff<br>ff             | 11       | 6<br>6<br>7           | — | _ | _ | _       | Δ     | Δ | Δ | 2 |

| LSLA       | Logical Shift<br>Left A          |                                            | A                     | INH                                 |                            | 48                         |                            | _        | 2                     | — | _ | _ | _       | Δ     | Δ | Δ | 2 |

| LSLB       | Logical Shift<br>Left B          |                                            | В                     | INH                                 |                            | 58                         |                            | _        | 2                     | — | _ | _ | _       | Δ     | Δ | Δ | 4 |

| LSLD       | Logical Shift<br>Left Double     | ← ← ←<br>← ← ← ← ← ← ← ← ← ← ← ← ← ← ← ← ← |                       | INH                                 |                            | 05                         |                            | _        | 3                     | — | _ | _ | _       | Δ     | Δ | Δ | 2 |

| LSR (opr)  | Logical Shift<br>Right           | 0 <del>→□□□→</del> □<br>b7 b0 C            |                       | EXT<br>IND,X<br>IND,Y               | 18                         | 74<br>64<br>64             | hh<br>ff<br>ff             | 11       | 6<br>6<br>7           | _ | _ | _ | _       | 0     | Δ | Δ |   |

| LSRA       | Logical Shift<br>Right A         | 0                                          | A                     | INH                                 |                            | 44                         |                            | _        | 2                     | _ | _ | _ | _       | 0     | Δ | Δ |   |

| LSRB       | Logical Shift<br>Right B         | 0→□□□→□<br>b7 b0 C                         | В                     | INH                                 |                            | 54                         |                            | -        | 2                     | — | _ | _ | _       | 0     | Δ | Δ | 4 |

**Resets and Interrupts**

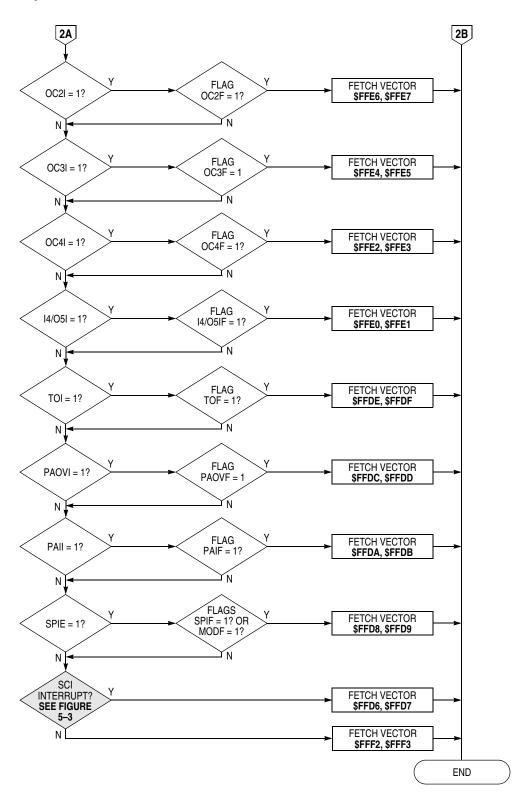

Figure 5-6. Interrupt Priority Resolution (Sheet 2 of 2)

M68HC11E Family Data Sheet, Rev. 5.1

### **Resets and Interrupts**

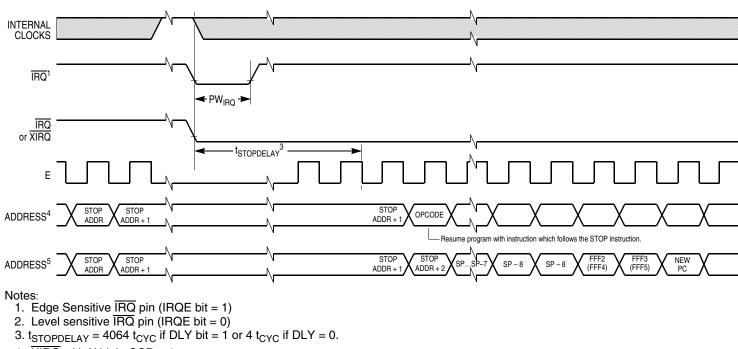

masked), the MCU starts up, beginning with the stacking sequence leading to normal service of the  $\overline{XIRQ}$  request. If X is set to 1 ( $\overline{XIRQ}$  masked or inhibited), then processing continues with the instruction that immediately follows the STOP instruction, and no  $\overline{XIRQ}$  interrupt service is requested or pending.

Because the oscillator is stopped in stop mode, a restart delay may be imposed to allow oscillator stabilization upon leaving stop. If the internal oscillator is being used, this delay is required; however, if a stable external oscillator is being used, the DLY control bit can be used to bypass this startup delay. The DLY control bit is set by reset and can be optionally cleared during initialization. If the DLY equal to 0 option is used to avoid startup delay on recovery from stop, then reset should not be used as the means of recovering from stop, as this causes DLY to be set again by reset, imposing the restart delay. This same delay also applies to power-on reset, regardless of the state of the DLY control bit, but does not apply to a reset while the clocks are running.

Parallel Input/Output (I/O) Ports

### **SPI Registers**

A write collision is normally a slave error because a slave has no control over when a master initiates a transfer. A master knows when a transfer is in progress, so there is no reason for a master to generate a write-collision error, although the SPI logic can detect write collisions in both master and slave devices.

The SPI configuration determines the characteristics of a transfer in progress. For a master, a transfer begins when data is written to SPDR and ends when SPIF is set. For a slave with CPHA equal to 0, a transfer starts when SS goes low and ends when SS returns high. In this case, SPIF is set at the middle of the eighth SCK cycle when data is transferred from the shifter to the parallel data register, but the transfer is still in progress until SS goes high. For a slave with CPHA equal to 1, transfer begins when the SCK line goes to its active level, which is the edge at the beginning of the first SCK cycle. The transfer ends in a slave in which CPHA equals 1 when SPIF is set.

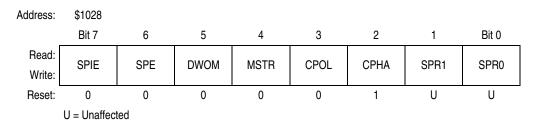

# 8.7 SPI Registers

The three SPI registers are:

- Serial peripheral control register (SPCR)

- Serial peripheral status register (SPSR)

- Serial peripheral data register (SPDR)

These registers provide control, status, and data storage functions.

# 8.7.1 Serial Peripheral Control Register

## Figure 8-3. Serial Peripheral Control Register (SPCR)

## SPIE — Serial Peripheral Interrupt Enable Bit

Set the SPE bit to 1 to request a hardware interrupt sequence each time the SPIF or MODF status flag is set. SPI interrupts are inhibited if this bit is clear or if the I bit in the condition code register is 1.

0 = SPI system interrupts disabled

1 = SPI system interrupts enabled

## SPE — Serial Peripheral System Enable Bit

When the SPE bit is set, the port D bit 2, 3, 4, and 5 pins are dedicated to the SPI function. If the SPI is in the master mode and DDRD bit 5 is set, then the port D bit 5 pin becomes a general-purpose output instead of the SS input.

- 0 = SPI system disabled

- 1 = SPI system enabled

# DWOM — Port D Wired-OR Mode Bit

DWOM affects all port D pins.

- 0 = Normal CMOS outputs

- 1 = Open-drain outputs

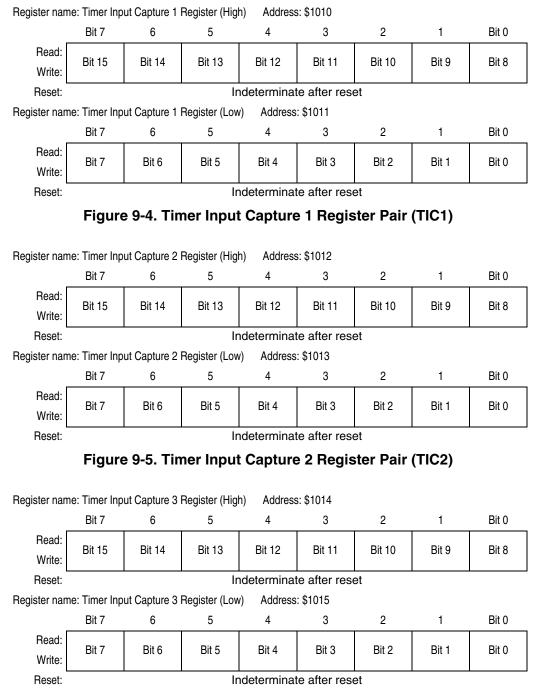

### Timing Systems

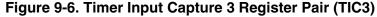

input capture register pair inhibits a new capture transfer for one bus cycle. If a double-byte read instruction, such as load double accumulator D (LDD), is used to read the captured value, coherency is assured. When a new input capture occurs immediately after a high-order byte read, transfer is delayed for an additional cycle but the value is not lost.

M68HC11E Family Data Sheet, Rev. 5.1

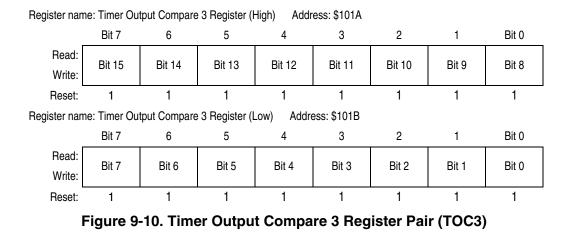

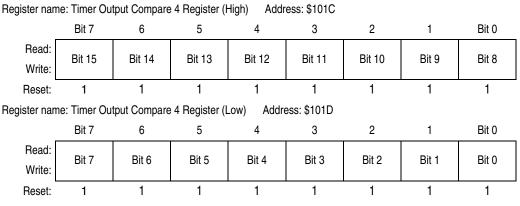

Figure 9-11. Timer Output Compare 4 Register Pair (TOC4)

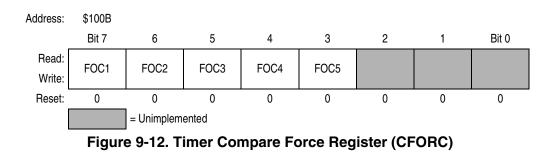

# 9.4.2 Timer Compare Force Register

The CFORC register allows forced early compares. FOC[1:5] correspond to the five output compares. These bits are set for each output compare that is to be forced. The action taken as a result of a forced compare is the same as if there were a match between the OCx register and the free-running counter, except that the corresponding interrupt status flag bits are not set. The forced channels trigger their programmed pin actions to occur at the next timer count transition after the write to CFORC.

The CFORC bits should not be used on an output compare function that is programmed to toggle its output on a successful compare because a normal compare that occurs immediately before or after the force can result in an undesirable operation.

M68HC11E Family Data Sheet, Rev. 5.1

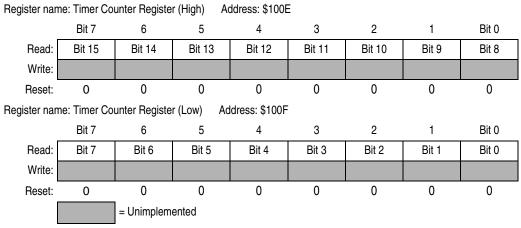

# 9.4.5 Timer Counter Register

The 16-bit read-only TCNT register contains the prescaled value of the 16-bit timer. A full counter read addresses the most significant byte (MSB) first. A read of this address causes the least significant byte (LSB) to be latched into a buffer for the next CPU cycle so that a double-byte read returns the full 16-bit state of the counter at the time of the MSB read cycle.

Figure 9-15. Timer Counter Register (TCNT)

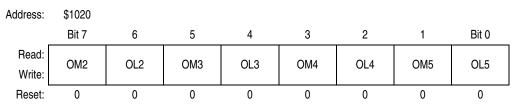

# 9.4.6 Timer Control Register 1

The bits of this register specify the action taken as a result of a successful OCx compare.

Figure 9-16. Timer Control Register 1 (TCTL1)

### OM[2:5] — Output Mode Bits OL[2:5] — Output Level Bits

These control bit pairs are encoded to specify the action taken after a successful OCx compare. OC5 functions only if the I4/O5 bit in the PACTL register is clear. Refer to Table 9-3 for the coding.

Table 9-3. Timer Output Compare Actions

| OMx | OLx | Action Taken on Successful Compare       |  |  |  |  |

|-----|-----|------------------------------------------|--|--|--|--|

| 0   | 0   | Timer disconnected from output pin logic |  |  |  |  |

| 0   | 1   | Toggle OCx output line                   |  |  |  |  |

| 1   | 0   | Clear OCx output line to 0               |  |  |  |  |

| 1   | 1   | Set OCx output line to 1                 |  |  |  |  |

4.  $\overline{XIRQ}$  with X bit in CCR = 1. 5. IRQ or (XIRQ with X bit in CCR = 0).

**Electrical Characteristics**

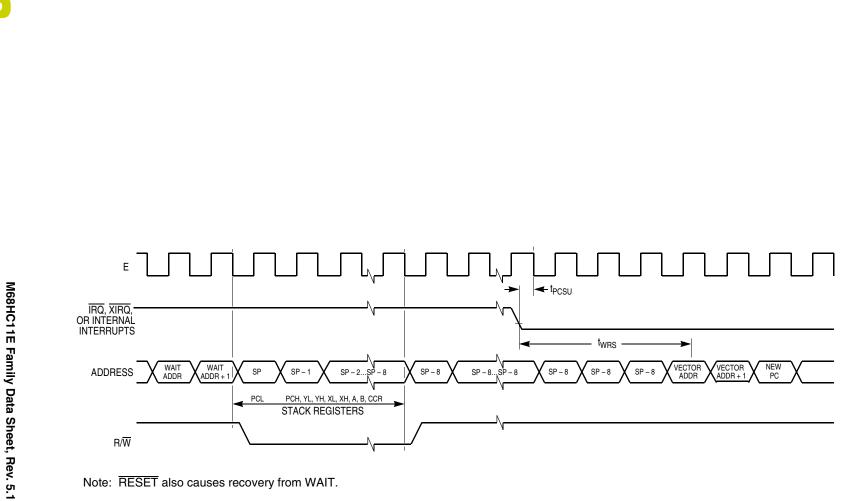

Note: RESET also causes recovery from WAIT.

Figure 10-5. WAIT Recovery from Interrupt Timing Diagram

160

### **Electrical Characteristics**

Note: Measurement points shown are 20% and 70% of  $V_{\text{DD}}.$

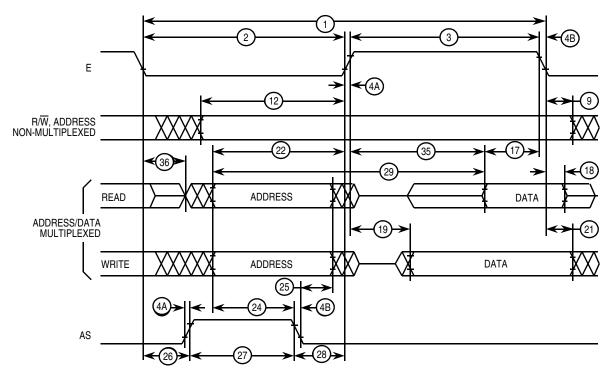

Figure 10-14. Multiplexed Expansion Bus Timing Diagram

# Appendix A Development Support

# A.1 Introduction

This section provides information on the development support offered for the E-series devices.

| <b>A.2</b> | M68HC11 | <b>E-Series</b> | Development | Tools |

|------------|---------|-----------------|-------------|-------|

|------------|---------|-----------------|-------------|-------|

| Device                      | Package | Emulation<br>Module <sup>(1) (2)</sup> | Flex<br>Cable <sup>(1) (2)</sup> | MMDS11<br>Target Head <sup>(1) (2)</sup> | SPGMR<br>Programming<br>Adapter <sup>(3)</sup> |

|-----------------------------|---------|----------------------------------------|----------------------------------|------------------------------------------|------------------------------------------------|

|                             | 52 FN   | M68EM11E20                             | M68CBL11C                        | M68TC11E20FN52                           | M68PA11E20FN52                                 |

| MC68HC11E9                  | 52 PB   | M68EM11E20                             | M68CBL11C                        | M68TC11E20PB52                           | M68PA11E20PB52                                 |

| MC68HC711E9                 | 56 B    | M68EM11E20                             | M68CBL11B                        | M68TC11E20B56                            | M68PA11E20B56                                  |

|                             | 64 FU   | M68EM11E20                             | M68CBL11C                        | M68TC11E20FU64                           | M68PA11E20FU64                                 |

| MC68HC11E20<br>MC68HC711E20 | 52 FN   | M68EM11E20                             | M68CBL11C                        | M68TC11E20FN52                           | M68PA11E20FN52                                 |

|                             | 64 FU   | M68EM11E20                             | M68CBL11C                        | M68TC11E20FU64                           | M68PA11E20FU64                                 |

| MC68HC811E2                 | 48 P    | M68EM11E20                             | M68CBL11B                        | M68TB11E20P48                            | M68PA11A8P48                                   |

|                             | 52 FN   | M68EM11E20                             | M68CBL11C                        | M68TC11E20FN52                           | M68PA11E20FN52                                 |

1. Each MMDS11 system consists of a system console (M68MMDS11), an emulation module, a flex cable, and a target head.

2. A complete EVS consists of a platform board (M68HC11PFB), an emulation module, a flex cable, and a target head.

3. Each SPGMR system consists of a universal serial programmer (M68SPGMR11) and a programming adapter. It can be used alone or in conjunction with the MMDS11.

# A.3 EVS — Evaluation System

The EVS is an economical tool for designing, debugging, and evaluating target systems based on the M68HC11. EVS features include:

- Monitor/debugger firmware

- One-line assembler/disassembler

- Host computer download capability

- Dual memory maps:

- 64-Kbyte monitor map that includes 16 Kbytes of monitor EPROM

- M68HC11 E-series user map that includes 64 Kbytes of emulation RAM

- MCU extension input/output (I/O) port for single-chip, expanded, and special-test operation modes

- RS-232C terminal and host I/O ports

- Logic analyzer connector

M68HC11E Family Data Sheet, Rev. 5.1

192

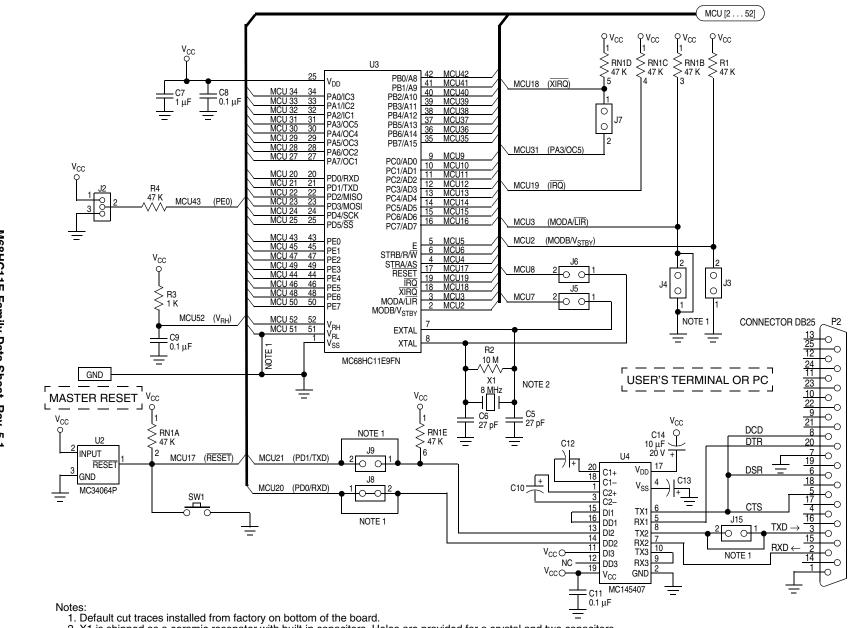

2. X1 is shipped as a ceramic resonator with built-in capacitors. Holes are provided for a crystal and two capacitors.

M68HC11E Family Data Sheet, Rev. 5.1

### Allowing for Bootstrap Mode

After the MCU sends \$FF [8], it enters the WAIT1 loop [9] and waits for the first data character from the host. When this character is received [10], the MCU programs it into the address pointed to by the Y index register. When the programming time delay is over, the MCU reads the programmed data, transmits it to the host for verification [11], and returns to the top of the WAIT1 loop to wait for the next data character [12]. Because the host previously sent the second data character, it is already waiting in the SCI receiver of the MCU. Steps [13], [14], and [15] correspond to the second pass through the WAIT1 loop.

Back in the host, the first verify character is received, and the third data character is sent [6]. The host then waits for the second verify character [7] to come back from the MCU. The sequence continues as long as the host continues to send data to the MCU. Since the WAIT1 loop in the PROGRAM utility is an indefinite loop, reset is used to end the process in the MCU after the host has finished sending data to be programmed.

## Allowing for Bootstrap Mode

Since bootstrap mode requires few connections to the MCU, it is easy to design systems that accommodate bootstrap mode.

Bootstrap mode is useful for diagnosing or repairing systems that have failed due to changes in the CONFIG register or failures of the expansion address/data buses, (rendering programs in external memory useless). Bootstrap mode can also be used to load information into the EPROM or EEPROM of an M68HC11 after final assembly of a module. Bootstrap mode is also useful for performing system checks and calibration routines. The following paragraphs explain system requirements for use of bootstrap mode in a product.

### Mode Select Pins

It must be possible to force the MODA and MODB pins to logic 0, which implies that these two pins should be pulled up to  $V_{DD}$  through resistors rather than being tied directly to  $V_{DD}$ . If mode pins are connected directly to  $V_{DD}$ , it is not possible to force a mode other than the one the MCU is hard wired for. It is also good practice to use pulldown resistors to  $V_{SS}$  rather than connecting mode pins directly to  $V_{SS}$  because it is sometimes a useful debug aid to attempt reset in modes other than the one the system was primarily designed for. Physically, this requirement sometimes calls for the addition of a test point or a wire connected to one or both mode pins. Mode selection only uses the mode pins while RESET is active.

### RESET

It must be possible to initiate a reset while the mode select pins are held low. In systems where there is no provision for manual reset, it is usually possible to generate a reset by turning power off and back on.

### **RxD** Pin

It must be possible to drive the PD0/RxD pin with serial data from a host computer (or another MCU). In many systems, this pin is already used for SCI communications; thus no changes are required.

### Driving Boot Mode from a Personal Computer

## Operation

Configure the EVBU for boot mode operation by putting a jumper at J3. Ensure that the trace command jumper at J7 is not installed because this would connect the 12-V programming voltage to the OC5 output of the MCU.

Connect the EVBU to its dc power supply. When it is time to program the MCU EPROM, turn on the 12-volt programming power supply to the new circuitry in the wire-wrap area.

Connect the EVBU serial port to the appropriate serial port on the host system. For the Macintosh, this is the modem port with a modem cable. For the MS-DOS<sup>®</sup> computer, it is connected to COM1 with a straight through or modem cable. Power up the host system and start the BASIC program. If the program has not been compiled, this is accomplished from within the appropriate BASIC compiler or interpreter. Power up the EVBU.

Answer the prompt for filename with either a [RETURN] to accept the default shown or by typing in a new filename and pressing [RETURN].

The program will inform the user that it is working on converting the file from S records to binary. This process will take from 30 seconds to a few minutes, depending on the computer.

A prompt reading, "Comm port open?" will appear at the end of the file conversion. This is the last chance to ensure that everything is properly configured on the EVBU. Pressing [RETURN] will send the bootcode to the target MC68HC711E9. The program then informs the user that the bootload code is being sent to the target, and the results of the echoing of this code are displayed on the screen.

Another prompt reading "Programming is ready to begin. Are you?" will appear. Turn on the 12-volt programming power supply and press [RETURN] to start the actual programming of the target EPROM.

A count of the byte being verified will be updated continually on the screen as the programming progresses. Any failures will be flagged as they occur.

When programming is complete, a message will be displayed as well as a prompt requesting the user to press [RETURN] to quit.

Turn off the 12-volt programming power supply before turning off 5 volts to the EVBU.

<sup>&</sup>lt;sup>®</sup> MS-DOS is a registered trademark of Microsoft Corporation in the United States and oth175190er countries.

1640 GOSUB 8000 'GET BYTE FOR VERIFICATION 1650 RCV = I - 11660 LOCATE 10,1:PRINT "Verifying byte #"; I; " 1664 IF CHR\$(CODE%(RCV)) = B\$ THEN 1670 1665 K=CODE%(RCV):GOSUB 8500 1666 LOCATE 1,1:PRINT "Byte #"; I; " ", " - Sent "; HX\$; 1668 K=ASC(B\$):GOSUB 8500 1669 PRINT " Received "; HX\$; 1670 NEXT I 1680 GOSUB 8000 'GET BYTE FOR VERIFICATION 1690 RCV = CODESIZE - 11700 LOCATE 10,1:PRINT "Verifying byte #"; CODESIZE%; " 1710 IF CHR\$(CODE%(RCV)) = B\$ THEN 1720 1713 K=CODE(RCV):GOSUB 8500 1714 LOCATE 1,1:PRINT "Byte #"; CODESIZE%; " ", " - Sent "; HX\$; 1715 K=ASC(B\$):GOSUB 8500 1716 PRINT " Received "; HX\$; 1720 LOCATE 8, 1: PRINT : PRINT "Done!!!!" 4900 CLOSE 4910 INPUT "Press [RETURN] to guit...", Q\$ 5000 END 5910 '\* SUBROUTINE TO READ IN ONE BYTE FROM A DISK FILE 5930 '\* RETURNS BYTE IN A\$ 6000 FLAG = 06010 IF EOF(1) THEN FLAG = 1: RETURN 6020 A\$ = INPUT\$(1, #1)6030 RETURN 6492 '\* SUBROUTINE TO SEND THE STRING IN AS OUT TO THE DEVICE 6494 '\* OPENED AS FILE #2. 6500 PRINT #2, A\$; 6510 RETURN 6594 '\* SUBROUTINE THAT CONVERTS THE HEX DIGIT IN A\$ TO AN INTEGER 7000 X = INSTR(H\$, A\$) 7010 IF X = 0 THEN FLAG = 1 7020 X = X - 17030 RETURN 7992 '\* SUBROUTINE TO READ IN ONE BYTE THROUGH THE COMM PORT OPENED 7994 '\* AS FILE #2. WAITS INDEFINITELY FOR THE BYTE TO BE 7996 '\* RECEIVED. SUBROUTINE WILL BE ABORTED BY ANY 7998 '\* KEYBOARD INPUT. RETURNS BYTE IN B\$. USES Q\$. 8000 WHILE LOC(2) = 0'WAIT FOR COMM PORT INPUT 8005 Q\$ = INKEY\$: IF Q\$ <> "" THEN 4900 'IF ANY KEY PRESSED, THEN ABORT 8010 WEND 8020 B = INPUT\$ (1, #2) 8030 RETURN

# To Execute the Program

Once you have obtained PCbug11, use this step-by-step procedure.

### Step 1

- Before applying power to the programming board, connect the M68HC711E9PGMR serial port P2 to one of your PC COM ports with a standard 25 pin RS-232 cable. Do not use a null modem cable or adapter which swaps the transmit and receive signals between the connectors at each end of the cable.

- Place your MC68HC811E2 part in the PLCC socket on your board.

- Insert the part upside down with the notched corner pointing toward the red power LED.

- Make sure both S1 and S2 switches are turned off.

- Apply +5 volts to +5 volts and ground to GND on the programmer board's power connector, P1. Applying voltage to the V<sub>PP</sub> pin is not necessary.

### Step 2

Apply power to the programmer board by moving the +5-volt switch to the ON position.

From a DOS command line prompt, start PCbug11 this way:

- C:\PCBUG11\> PCBUG11 –A PORT = 1 when the E9PGMR connected to COM1 or

- C:\PCBUG11\> PCBUG11 -A PORT = 2 when the E9PGMR connected to COM2

PCbug11only supports COM ports 1 and 2.

### Step 3

PCbug11 defaults to base ten for its input parameters.

Change this to hexadecimal by typing: CONTROL BASE HEX

### Step 4

Clear the block protect register (BPROT) to allow programming of the MC68HC811E2 EEPROM.

At the PCbug11 command prompt, type: MS 1035 00

### Step 5

PCbug11 defaults to a 512-byte EEPROM array located at \$B600. This must be changed since the EEPROM is, by default, located at \$F800 on the MC68HC811E2.

At the PCbug11 command prompt, type: EEPROM 0

Then type: EEPROM F800 FFFF EEPROM 103F 103F

This assumes you have not relocated the EEPROM by previously reprogramming the upper 4 bits of the CONFIG register. But if you have done this and your S records reside in an address range other than \$F800 to \$FFFF, you will need to first relocate the EEPROM.

Enabling the Security Feature on M68HC811E2 Devices with PCbug11 on the M68HC711E9PGMR, Rev. 0.1

### How to Reach Us:

Home Page: www.freescale.com

E-mail: support@freescale.com

#### USA/Europe or Locations Not Listed:

Freescale Semiconductor Technical Information Center, CH370 1300 N. Alma School Road Chandler, Arizona 85224 +1-800-521-6274 or +1-480-768-2130 support@freescale.com

#### Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) support@freescale.com

#### Japan:

Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku, Tokyo 153-0064 Japan 0120 191014 or +81 3 5437 9125 support.japan@freescale.com

#### Asia/Pacific:

Freescale Semiconductor Hong Kong Ltd. Technical Information Center 2 Dai King Street Tai Po Industrial Estate Tai Po, N.T., Hong Kong +800 2666 8080 support.asia@freescale.com

#### For Literature Requests Only:

Freescale Semiconductor Literature Distribution Center P.O. Box 5405 Denver, Colorado 80217 1-800-441-2447 or 303-675-2140 Fax: 303-675-2150 LDCForFreescaleSemiconductor@hibbertgroup.com Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals", must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

Freescale<sup>™</sup> and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. © Freescale Semiconductor, Inc. 2005. All rights reserved.

M68HC11E Rev. 5.1, 07/2005