Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                               |

|----------------------------|---------------------------------------------------------------|

| Product Status             | Active                                                        |

| Core Processor             | HC11                                                          |

| Core Size                  | 8-Bit                                                         |

| Speed                      | 3MHz                                                          |

| Connectivity               | SCI, SPI                                                      |

| Peripherals                | POR, WDT                                                      |

| Number of I/O              | 38                                                            |

| Program Memory Size        | -                                                             |

| Program Memory Type        | ROMIess                                                       |

| EEPROM Size                | 512 x 8                                                       |

| RAM Size                   | 512 x 8                                                       |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                   |

| Data Converters            | A/D 8x8b                                                      |

| Oscillator Type            | Internal                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                             |

| Mounting Type              | Surface Mount                                                 |

| Package / Case             | 52-LCC (J-Lead)                                               |

| Supplier Device Package    | 52-PLCC (19.1x19.1)                                           |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mc68hc11e1cfne3r |

|                            |                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

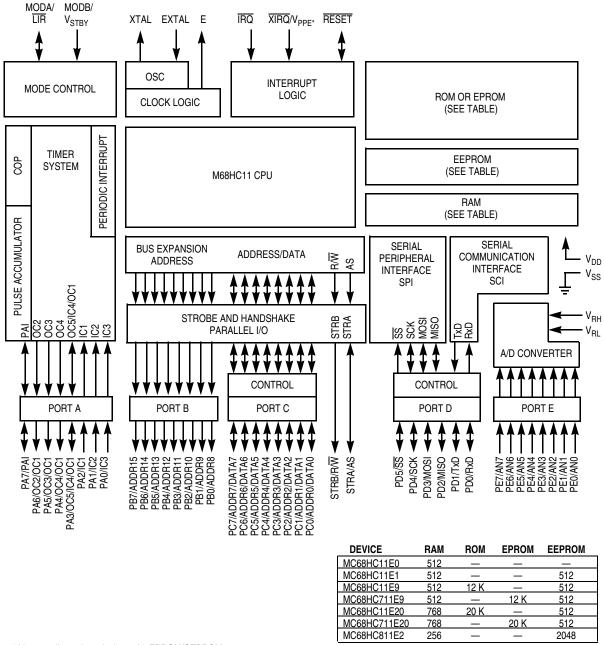

# Chapter 1 General Description

### 1.1 Introduction

This document contains a detailed description of the M68HC11 E series of 8-bit microcontroller units (MCUs). These MCUs all combine the M68HC11 central processor unit (CPU) with high-performance, on-chip peripherals.

The E series is comprised of many devices with various configurations of:

- Random-access memory (RAM)

- Read-only memory (ROM)

- Erasable programmable read-only memory (EPROM)

- Electrically erasable programmable read-only memory (EEPROM)

- Several low-voltage devices are also available.

With the exception of a few minor differences, the operation of all E-series MCUs is identical. A fully static design and high-density complementary metal-oxide semiconductor (HCMOS) fabrication process allow the E-series devices to operate at frequencies from 3 MHz to dc with very low power consumption.

# 1.2 Features

Features of the E-series devices include:

- M68HC11 CPU

- Power-saving stop and wait modes

- Low-voltage devices available (3.0–5.5 Vdc)

- 0, 256, 512, or 768 bytes of on-chip RAM, data retained during standby

- 0, 12, or 20 Kbytes of on-chip ROM or EPROM

- 0, 512, or 2048 bytes of on-chip EEPROM with block protect for security

- 2048 bytes of EEPROM with selectable base address in the MC68HC811E2

- Asynchronous non-return-to-zero (NRZ) serial communications interface (SCI)

- Additional baud rates available on MC68HC(7)11E20

- Synchronous serial peripheral interface (SPI)

- 8-channel, 8-bit analog-to-digital (A/D) converter

- 16-bit timer system:

- Three input capture (IC) channels

- Four output compare (OC) channels

- One additional channel, selectable as fourth IC or fifth OC

- 8-bit pulse accumulator

- Real-time interrupt circuit

$<sup>^{\</sup>star}$   $V_{\mbox{\footnotesize{PPE}}}$  applies only to devices with EPROM/OTPROM.

Figure 1-1. M68HC11 E-Series Block Diagram

#### **General Description**

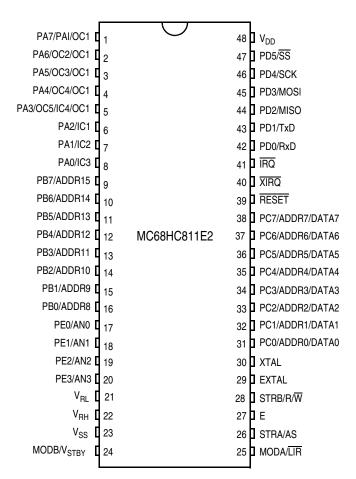

Figure 1-6. Pin Assignments for 48-Pin DIP (MC68HC811E2)

#### **Operating Modes and On-Chip Memory**

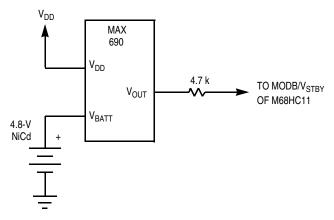

Figure 2-8. RAM Standby MODB/V<sub>STBY</sub> Connections

The bootloader program is contained in the internal bootstrap ROM. This ROM, which appears as internal memory space at locations \$BF00–\$BFFF, is enabled only if the MCU is reset in special bootstrap mode.

In expanded modes, the ROM/EPROM/OTPROM (if present) is enabled out of reset and located at the top of the memory map if the ROMON bit in the CONFIG register is set. ROM or EPROM is enabled out of reset in single-chip and bootstrap modes, regardless of the state of ROMON.

For devices with 512 bytes of EEPROM, the EEPROM is located at \$B600–\$B7FF and has the same read cycle time as the internal ROM. The 512 bytes of EEPROM cannot be remapped to other locations.

For the MC68HC811E2, EEPROM is located at \$F800–\$FFFF and can be remapped to any 4-Kbyte boundary. EEPROM mapping control bits (EE[3:0] in CONFIG) determine the location of the 2048 bytes of EEPROM and are present only on the MC68HC811E2. Refer to 2.3.3.1 System Configuration Register for a description of the MC68HC811E2 CONFIG register.

EEPROM can be programmed or erased by software and an on-chip charge pump, allowing EEPROM changes using the single V<sub>DD</sub> supply.

#### 2.3.2 Mode Selection

The four mode variations are selected by the logic states of the MODA and MODB pins during reset. The MODA and MODB logic levels determine the logic state of SMOD and the MDA control bits in the highest priority I-bit interrupt and miscellaneous (HPRIO) register.

After reset is released, the mode select pins no longer influence the MCU operating mode. In single-chip operating mode, the MODA pin is connected to a logic level 0. In expanded mode, MODA is normally connected to  $V_{DD}$  through a pullup resistor of 4.7 k $\Omega$ . The MODA pin also functions as the load instruction register  $\overline{LIR}$  pin when the MCU is not in reset. The open-drain active low  $\overline{LIR}$  output pin drives low during the first E cycle of each instruction. The MODB pin also functions as standby power input ( $V_{STBY}$ ), which allows RAM contents to be maintained in absence of  $V_{DD}$ .

Refer to Table 2-1, which is a summary of mode pin operation, the mode control bits, and the four operating modes.

#### **Operating Modes and On-Chip Memory**

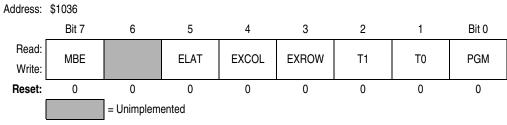

Figure 2-15. MC68HC711E20 EPROM Programming Control Register (EPROG)

## MBE — Multiple-Byte Programming Enable Bit

When multiple-byte programming is enabled, address bit 5 is considered a don't care so that bytes with address bit 5 = 0 and address bit 5 = 1 both get programmed. MBE can be read in any mode and always reads 0 in normal modes. MBE can be written only in special modes.

- 0 = EPROM array configured for normal programming

- 1 = Program two bytes with the same data

### Bit 6 — Unimplemented

Always reads 0

#### **ELAT — EPROM/OTPROM Latch Control Bit**

When ELAT = 1, writes to EPROM cause address and data to be latched and the EPROM/OTPROM cannot be read. ELAT can be read any time. ELAT can be written any time except when PGM = 1; then the write to ELAT is disabled.

- 0 = EPROM/OTPROM address and data bus configured for normal reads

- 1 = EPROM/OTPROM address and data bus configured for programming

#### **EXCOL** — Select Extra Columns Bit

- 0 = User array selected

- 1 = User array is disabled and extra columns are accessed at bits [7:0]. Addresses use bits [13:5] and bits [4:0] are don't care. EXCOL can be read and written only in special modes and always returns 0 in normal modes.

#### **EXROW** — Select Extra Rows Bit

- 0 = User array selected

- 1 = User array is disabled and two extra rows are available. Addresses use bits [7:0] and bits [13:8] are don't care. EXROW can be read and written only in special modes and always returns 0 in normal modes.

#### T[1:0] — EPROM Test Mode Select Bits

These bits allow selection of either gate stress or drain stress test modes. They can be read and written only in special modes and always read 0 in normal modes.

| T1 | ТО | Function Selected |

|----|----|-------------------|

| 0  | 0  | Normal mode       |

| 0  | 1  | Reserved          |

| 1  | 0  | Gate stress       |

| 1  | 1  | Drain stress      |

#### **Central Processor Unit (CPU)**

# 4.2.5 Program Counter (PC)

The program counter, a 16-bit register, contains the address of the next instruction to be executed. After reset, the program counter is initialized from one of six possible vectors, depending on operating mode and the cause of reset. See Table 4-1.

**Table 4-1. Reset Vector Comparison**

| Mode         | POR or RESET Pin | Clock Monitor | COP Watchdog |

|--------------|------------------|---------------|--------------|

| Normal       | \$FFFE, F        | \$FFFC, D     | \$FFFA, B    |

| Test or Boot | \$BFFE, F        | \$BFFC, D     | \$BFFA, B    |

# 4.2.6 Condition Code Register (CCR)

This 8-bit register contains:

- Five condition code indicators (C, V, Z, N, and H),

- Two interrupt masking bits (IRQ and XIRQ)

- A stop disable bit (S)

In the M68HC11 CPU, condition codes are updated automatically by most instructions. For example, load accumulator A (LDAA) and store accumulator A (STAA) instructions automatically set or clear the N, Z, and V condition code flags. Pushes, pulls, add B to X (ABX), add B to Y (ABY), and transfer/exchange instructions do not affect the condition codes. Refer to Table 4-2, which shows what condition codes are affected by a particular instruction.

# 4.2.6.1 Carry/Borrow (C)

The C bit is set if the arithmetic logic unit (ALU) performs a carry or borrow during an arithmetic operation. The C bit also acts as an error flag for multiply and divide operations. Shift and rotate instructions operate with and through the carry bit to facilitate multiple-word shift operations.

#### 4.2.6.2 Overflow (V)

The overflow bit is set if an operation causes an arithmetic overflow. Otherwise, the V bit is cleared.

#### 4.2.6.3 Zero (Z)

The Z bit is set if the result of an arithmetic, logic, or data manipulation operation is 0. Otherwise, the Z bit is cleared. Compare instructions do an internal implied subtraction and the condition codes, including Z, reflect the results of that subtraction. A few operations (INX, DEX, INY, and DEY) affect the Z bit and no other condition flags. For these operations, only = and  $\neq$  conditions can be determined.

#### 4.2.6.4 Negative (N)

The N bit is set if the result of an arithmetic, logic, or data manipulation operation is negative (MSB = 1). Otherwise, the N bit is cleared. A result is said to be negative if its most significant bit (MSB) is a 1. A quick way to test whether the contents of a memory location has the MSB set is to load it into an accumulator and then check the status of the N bit.

#### Parallel Input/Output (I/O) Ports

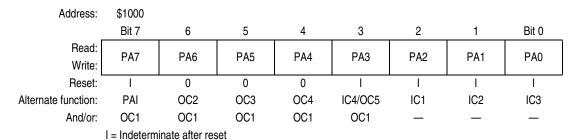

# 6.2 Port A

Port A shares functions with the timer system and has:

- Three input-only pins

- Three output-only pins

- Two bidirectional I/O pins

Figure 6-1. Port A Data Register (PORTA)

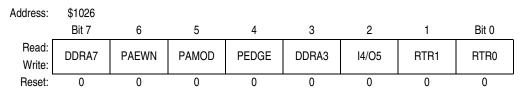

Figure 6-2. Pulse Accumulator Control Register (PACTL)

#### DDRA7 — Data Direction for Port A Bit 7

Overridden if an output compare function is configured to control the PA7 pin

0 = Input

1 = Output

The pulse accumulator uses port A bit 7 as the PAI input, but the pin can also be used as general-purpose I/O or as an output compare.

#### NOTE

Even when port A bit 7 is configured as an output, the pin still drives the input to the pulse accumulator.

#### PAEN — Pulse Accumulator System Enable Bit

Refer to Chapter 9 Timing Systems.

#### PAMOD — Pulse Accumulator Mode Bit

Refer to Chapter 9 Timing Systems.

### PEDGE — Pulse Accumulator Edge Control Bit

Refer to Chapter 9 Timing Systems.

#### DDRA3 — Data Direction for Port A Bit 3

This bit is overridden if an output compare function is configured to control the PA3 pin.

0 = Input

1 = Output

#### 14/O5 — Input Capture 4/Output Compare 5 Bit

Refer to Chapter 9 Timing Systems.

# RTR[1:0] — RTI Interrupt Rate Select Bits

Refer to Chapter 9 Timing Systems.

M68HC11E Family Data Sheet, Rev. 5.1

## **Serial Communications Interface (SCI)**

Note: Refer to Figure B-1. EVBU Schematic Diagram for an example of connecting RxD to a PC.

Figure 7-2. SCI Receiver Block Diagram

TDRE and TC flags are normally set when the transmitter is first enabled (TE set to 1). The TDRE flag indicates there is room in the transmit queue to store another data character in the TDR. The TIE bit is the local interrupt mask for TDRE. When TIE is 0, TDRE must be polled. When TIE and TDRE are 1, an interrupt is requested.

The TC flag indicates the transmitter has completed the queue. The TCIE bit is the local interrupt mask for TC. When TCIE is 0, TC must be polled. When TCIE is 1 and TC is 1, an interrupt is requested.

Writing a 0 to TE requests that the transmitter stop when it can. The transmitter completes any transmission in progress before actually shutting down. Only an MCU reset can cause the transmitter to stop and shut down immediately. If TE is written to 0 when the transmitter is already idle, the pin reverts to its general-purpose I/O function (synchronized to the bit-rate clock). If anything is being transmitted when TE is written to 0, that character is completed before the pin reverts to general-purpose I/O, but any other characters waiting in the transmit queue are lost. The TC and TDRE flags are set at the completion of this last character, even though TE has been disabled.

# 7.9 Receiver Flags

The SCI receiver has five status flags, three of which can generate interrupt requests. The status flags are set by the SCI logic in response to specific conditions in the receiver. These flags can be read (polled) at any time by software. Refer to Figure 7-10, which shows SCI interrupt arbitration.

When an overrun takes place, the new character is lost, and the character that was in its way in the parallel RDR is undisturbed. RDRF is set when a character has been received and transferred into the parallel RDR. The OR flag is set instead of RDRF if overrun occurs. A new character is ready to be transferred into RDR before a previous character is read from RDR.

The NF and FE flags provide additional information about the character in the RDR, but do not generate interrupt requests.

The last receiver status flag and interrupt source come from the IDLE flag. The RxD line is idle if it has constantly been at logic 1 for a full character time. The IDLE flag is set only after the RxD line has been busy and becomes idle, which prevents repeated interrupts for the whole time RxD remains idle.

#### **Electrical Characteristics**

# 10.3 Functional Operating Range

| Rating                                                                                                                                                              | Symbol         | Value                                                                                                                                           | Unit |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Operating temperature range MC68HC(7)11Ex MC68HC(7)11ExC MC68HC(7)11ExV MC68HC(7)11ExM MC68HC811E2 MC68HC811E2C MC68HC811E2V MC68HC811E2V MC68HC811E2M MC68HC811E2M | T <sub>A</sub> | T <sub>L</sub> to T <sub>H</sub> 0 to +70 -40 to +85 -40 to +105 -40 to +125 0 to +70 -40 to +85 -40 to +105 -40 to +125 -40 to +125 -20 to +70 | °C   |

| Operating voltage range                                                                                                                                             | $V_{DD}$       | 5.0 ± 10%                                                                                                                                       | V    |

# 10.4 Thermal Characteristics

| Characteristic                                                                                                                                                                                                | Symbol           | Value                                                                | Unit |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|----------------------------------------------------------------------|------|

| Average junction temperature                                                                                                                                                                                  | T <sub>J</sub>   | $T_A + (P_D \times \Theta_{JA})$                                     | °C   |

| Ambient temperature                                                                                                                                                                                           | T <sub>A</sub>   | User-determined                                                      | °C   |

| Package thermal resistance (junction-to-ambient) 48-pin plastic DIP (MC68HC811E2 only) 56-pin plastic SDIP 52-pin plastic leaded chip carrier 52-pin plastic thin quad flat pack (TQFP) 64-pin quad flat pack | $\Theta_{JA}$    | 50<br>50<br>50<br>85<br>85                                           | °C/W |

| Total power dissipation <sup>(1)</sup>                                                                                                                                                                        | P <sub>D</sub>   | P <sub>INT</sub> + P <sub>I/O</sub><br>K / T <sub>J</sub> + 273°C    | W    |

| Device internal power dissipation                                                                                                                                                                             | P <sub>INT</sub> | $I_{DD} \times V_{DD}$                                               | W    |

| I/O pin power dissipation <sup>(2)</sup>                                                                                                                                                                      | P <sub>I/O</sub> | User-determined                                                      | W    |

| A constant <sup>(3)</sup>                                                                                                                                                                                     | К                | $P_{D} \times (T_{A} + 273^{\circ}C) + \Theta_{JA} \times P_{D}^{2}$ | W/°C |

This is an approximate value, neglecting P<sub>I/O</sub>.

For most applications, P<sub>I/O</sub> ≤ P<sub>INT</sub> and can be neglected.

K is a constant pertaining to the device. Solve for K with a known T<sub>A</sub> and a measured P<sub>D</sub> (at equilibrium). Use this value of K to solve for P<sub>D</sub> and T<sub>J</sub> iteratively for any value of T<sub>A</sub>.

# **Electrical Characteristics**

# 10.6 Supply Currents and Power Dissipation

| Characteristics <sup>(1)</sup>                                                                                                                         | Symbol           | Min              | Max                        | Unit |

|--------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------------------|----------------------------|------|

| Run maximum total supply current <sup>(2)</sup> Single-chip mode2 MHz 3 MHz Expanded multiplexed mode2 MHz 3 MHz                                       | I <sub>DD</sub>  | _<br>_<br>_<br>_ | 15<br>27<br>27<br>27<br>35 | mA   |

| Wait maximum total supply current <sup>(2)</sup> (all peripheral functions shut down) Single-chip mode2 MHz 3 MHz Expanded multiplexed mode2 MHz 3 MHz | W <sub>IDD</sub> | _<br>_<br>_<br>_ | 6<br>15<br>10<br>20        | mA   |

| Stop maximum total supply current <sup>(2)</sup> Single-chip mode, no clocks–40°C to +85°C > +85°C to +105°C > +105°C to +125°C                        | S <sub>IDD</sub> | _<br>_<br>_      | 25<br>50<br>100            | μА   |

| Maximum power dissipation Single-chip mode2 MHz 3 MHz Expanded multiplexed mode2 MHz 3 MHz                                                             | P <sub>D</sub>   | _<br>_<br>_<br>_ | 85<br>150<br>150<br>195    | mW   |

<sup>1.</sup>  $V_{DD}$  = 5.0 Vdc  $\pm$  10%,  $V_{SS}$  = 0 Vdc,  $T_A$  =  $T_L$  to  $T_H$ , unless otherwise noted 2. EXTAL is driven with a square wave, and  $t_{CYC}$ = 500 ns for 2 MHz rating  $t_{CYC}$ = 333 ns for 3 MHz rating  $V_{IL}$  ≤ 0.2 V  $V_{IH}$   $\geq$   $V_{DD}$  - 0.2 V no dc loads

#### MC68L11E9/E20 Supply Currents and Power Dissipation

#### Notes:

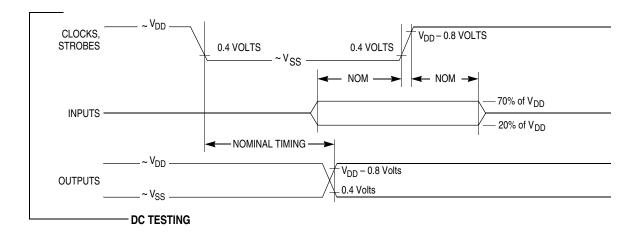

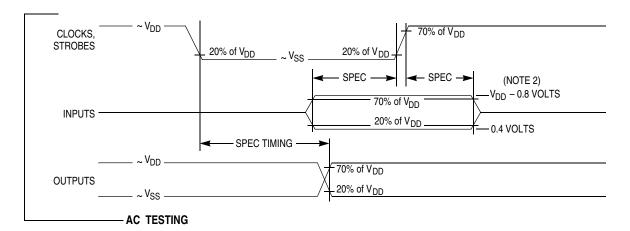

- 1. Full test loads are applied during all dc electrical tests and ac timing measurements.

- During ac timing measurements, inputs are driven to 0.4 volts and V<sub>DD</sub> 0.8 volts while timing measurements are taken at 20% and 70% of V<sub>DD</sub> points.

Figure 10-1. Test Methods

#### **Electrical Characteristics**

# 10.11 Peripheral Port Timing

| Characteristic <sup>(1)</sup> (2)                                                                                                          | Cumbal            | 1.0 MHz |            | 2.0 MHz |            | 3.0 MHz |            | Unit  |

|--------------------------------------------------------------------------------------------------------------------------------------------|-------------------|---------|------------|---------|------------|---------|------------|-------|

| Characteristic                                                                                                                             | Symbol            | Min     | Max        | Min     | Max        | Min     | Max        | Oilit |

| Frequency of operation E-clock frequency                                                                                                   | f <sub>o</sub>    | dc      | 1.0        | dc      | 2.0        | dc      | 3.0        | MHz   |

| E-clock period                                                                                                                             | t <sub>CYC</sub>  | 1000    |            | 500     |            | 333     | _          | ns    |

| Peripheral data setup time<br>MCU read of ports A, C, D, and E                                                                             | t <sub>PDSU</sub> | 100     | _          | 100     | _          | 100     | _          | ns    |

| Peripheral data hold time<br>MCU read of ports A, C, D, and E                                                                              | t <sub>PDH</sub>  | 50      |            | 50      |            | 50      | _          | ns    |

| Delay time, peripheral data write  t <sub>PWD</sub> = 1/4 t <sub>CYC</sub> + 100 ns  MCU writes to port A  MCU writes to ports B, C, and D | t <sub>PWD</sub>  |         | 200<br>350 |         | 200<br>225 |         | 200<br>183 | ns    |

| Port C input data setup time                                                                                                               | t <sub>IS</sub>   | 60      | _          | 60      | _          | 60      | _          | ns    |

| Port C input data hold time                                                                                                                | t <sub>IH</sub>   | 100     | _          | 100     | _          | 100     | _          | ns    |

| Delay time, E fall to STRB<br>t <sub>DEB</sub> = 1/4 t <sub>CYC</sub> + 100 ns                                                             | t <sub>DEB</sub>  | _       | 350        | _       | 225        | _       | 183        | ns    |

| Setup time, STRA asserted to E fall <sup>(3)</sup>                                                                                         | t <sub>AES</sub>  | 0       | _          | 0       | _          | 0       | _          | ns    |

| Delay time, STRA asserted to port C data output valid                                                                                      | t <sub>PCD</sub>  | _       | 100        | _       | 100        | _       | 100        | ns    |

| Hold time, STRA negated to port C data                                                                                                     | t <sub>PCH</sub>  | 10      | _          | 10      | _          | 10      | _          | ns    |

| 3-state hold time                                                                                                                          | t <sub>PCZ</sub>  |         | 150        |         | 150        |         | 150        | ns    |

<sup>1.</sup>  $V_{DD}$  = 5.0 Vdc  $\pm$  10%,  $V_{SS}$  = 0 Vdc,  $T_A$  =  $T_L$  to  $T_H$ , all timing is shown with respect to 20%  $V_{DD}$  and 70%  $V_{DD}$ , unless otherwise noted

<sup>2.</sup> Ports C and D timing is valid for active drive. (CWOM and DWOM bits are not set in PIOC and SPCR registers, respectively.)

<sup>3.</sup> If this setup time is met, STRB acknowledges in the next cycle. If it is not met, the response may be delayed one more cycle.

# 10.17 Serial Peripheral Interface Timing Characteristics

| Missee | O (1)                                                  | Combal                                           | Е                                                   | :9                                  | E                                                   | 20                                  | l locia          |

|--------|--------------------------------------------------------|--------------------------------------------------|-----------------------------------------------------|-------------------------------------|-----------------------------------------------------|-------------------------------------|------------------|

| Num    | Characteristic <sup>(1)</sup>                          | Symbol                                           | Min                                                 | Max                                 | Min                                                 | Max                                 | Unit             |

|        | Frequency of operation E clock                         | f <sub>o</sub>                                   | dc                                                  | 3.0                                 | dc                                                  | 3.0                                 | MHz              |

|        | E-clock period                                         | t <sub>CYC</sub>                                 | 333                                                 | _                                   | 333                                                 | _                                   | ns               |

|        | Operating frequency<br>Master<br>Slave                 | f <sub>op(m)</sub><br>f <sub>op(s)</sub>         | f <sub>o</sub> /32<br>dc                            | f <sub>o</sub> /2<br>f <sub>o</sub> | f <sub>o</sub> /128<br>dc                           | f <sub>o</sub> /2<br>f <sub>o</sub> | MHz              |

| 1      | Cycle time<br>Master<br>Slave                          | t <sub>CYC(m)</sub> t <sub>CYC(s)</sub>          | 2<br>1                                              | 32<br>—                             | 2<br>1                                              | 128<br>—                            | t <sub>CYC</sub> |

| 2      | Enable lead time <sup>(2)</sup><br>Slave               | t <sub>lead(s)</sub>                             | 1                                                   | _                                   | 1                                                   | _                                   | t <sub>CYC</sub> |

| 3      | Enable lag time <sup>(2)</sup><br>Slave                | t <sub>lag(s)</sub>                              | 1                                                   | _                                   | 1                                                   | _                                   | t <sub>CYC</sub> |

| 4      | Clock (SCK) high time<br>Master<br>Slave               | t <sub>w</sub> (SCKH)m<br>t <sub>w</sub> (SCKH)s | t <sub>CYC</sub> -25<br>1/2<br>t <sub>CYC</sub> -25 | 16 t <sub>CYC</sub>                 | t <sub>CYC</sub> -25<br>1/2<br>t <sub>CYC</sub> -25 | 64 t <sub>CYC</sub>                 | ns               |

| 5      | Clock (SCK) low time<br>Master<br>Slave                | t <sub>w(SCKL)m</sub>                            | t <sub>CYC</sub> -25<br>1/2<br>t <sub>CYC</sub> -25 | 16 t <sub>CYC</sub>                 | t <sub>CYC</sub> -25<br>1/2<br>t <sub>CYC</sub> -25 | 64 t <sub>CYC</sub>                 | ns               |

| 6      | Data setup time (inputs)  Master  Slave                | t <sub>su(m)</sub><br>t <sub>su(s)</sub>         | 30<br>30                                            | _<br>_                              | 30<br>30                                            | _<br>_                              | ns               |

| 7      | Data hold time (inputs)  Master Slave                  | t <sub>h(m)</sub> t <sub>h(s)</sub>              | 30<br>30                                            |                                     | 30<br>30                                            |                                     | ns               |

| 8      | Slave access time<br>CPHA = 0<br>CPHA = 1              | t <sub>a</sub>                                   | 0<br>0                                              | 40<br>40                            | 0<br>0                                              | 40<br>40                            | ns               |

| 9      | Disable time (hold time to high-impedance state) Slave | t <sub>dis</sub>                                 | _                                                   | 50                                  | _                                                   | 50                                  | ns               |

| 10     | Data valid <sup>(3)</sup> (after enable edge)          | t <sub>v</sub>                                   | _                                                   | 50                                  | _                                                   | 50                                  | ns               |

| 11     | Data hold time (outputs) (after enable edge)           | t <sub>ho</sub>                                  | 0                                                   | _                                   | 0                                                   | _                                   | ns               |

<sup>1.</sup>  $V_{DD}$  = 5.0 Vdc  $\pm 10\%$ ,  $V_{SS}$  = 0 Vdc,  $T_A$  =  $T_L$  to  $T_H$ , all timing is shown with respect to 20%  $V_{DD}$  and 70%  $V_{DD}$ , unless otherwise noted

<sup>2.</sup> Time to data active from high-impedance state

<sup>3.</sup> Assumes 200 pF load on SCK, MOSI, and MISO pins

# **Ordering Information and Mechanical Specifications**

| Description                       | CONFIG         | Temperature      | Frequency | MC Order Number  |

|-----------------------------------|----------------|------------------|-----------|------------------|

| 52-pin plastic leaded chip carrie | er (PLCC) (Con | tinued)          |           |                  |

|                                   |                | -40°C to +85°C - | 2 MHz     | MC68HC711E9CFN2  |

| OTDDOM                            | 4              |                  | 3 MHz     | MC68HC711E9CFN3  |

| OTPROM                            | \$0F           | -40°C to +105°C  | 2 MHz     | MC68HC711E9VFN2  |

|                                   |                | -40°C to +125°C  | 2 MHz     | MC68HC711E9MFN2  |

| OTPROM, enhanced security feature | \$0F           | -40°C to +85°C   | 2 MHz     | MC68S711E9CFN2   |

|                                   |                | 0°C to +70°C     | 3 MHz     | MC68HC711E20FN3  |

|                                   |                | 400C to . 050C   | 2 MHz     | MC68HC711E20CFN2 |

| 20 Kbytes OTPROM                  | \$0F           | -40°C to +85°C   | 3 MHz     | MC68HC711E20CFN3 |

|                                   |                | -40°C to +105°C  | 2 MHz     | MC68HC711E20VFN2 |

|                                   |                | -40°C to +125°C  | 2 MHz     | MC68HC711E20MFN2 |

|                                   | \$FF           | 0°C to +70°C     | 2 MHz     | MC68HC811E2FN2   |

| No DOM 2 Voytoo FEDDOM            |                | -40°C to +85°C   | 2 MHz     | MC68HC811E2CFN2  |

| No ROM, 2 Kbytes EEPROM           |                | -40°C to +105°C  | 2 MHz     | MC68HC811E2VFN2  |

|                                   |                | -40°C to +125°C  | 2 MHz     | MC68HC811E2MFN2  |

| 64-pin quad flat pack (QFP)       |                |                  |           |                  |

| BUFFALO ROM                       | \$0F           | -40°C to +85°C   | 2 MHz     | MC68HC11E9BCFU2  |

| BUFFALU RUW                       |                |                  | 3 MHz     | MC68HC11E9BCFU3  |

|                                   |                | -40°C to +85°C   | 2 MHz     | MC68HC11E1CFU2   |

| No ROM                            | \$0D           | -40 C to +65 C   | 3 MHz     | MC68HC11E1CFU3   |

|                                   |                | -40°C to +105°C  | 2 MHz     | MC68HC11E1VFU2   |

| No ROM, no EEPROM                 | \$0C           | -40°C to +85°C   | 2 MHz     | MC68HC11E0CFU2   |

| NO NOW, NO EEPHOW                 | <b>ФОС</b>     | -40°C to +105°C  | 2 MHz     | MC68HC11E0VFU2   |

|                                   |                | 0°C to +70°°C    | 3 MHz     | MC68HC711E20FU3  |

|                                   |                | -40°C to +85°C   | 2 MHz     | MC68HC711E20CFU2 |

| 20 Kbytes OTPROM                  | \$0F           | -40 C (0 +65°C   | 3 MHz     | MC68HC711E20CFU3 |

|                                   |                | -40°C to +105°C  | 2 MHz     | MC68HC711E20VFU2 |

|                                   |                | -40°C to +125°C  | 2 MHz     | MC68HC711E20MFU2 |

| 52-pin thin quad flat pack (TQF)  | P)             |                  |           |                  |

| BLIEFALO ROM                      | ¢∩⊏            | -40°C to +85°C   | 2 MHz     | MC68HC11E9BCPB2  |

| BUFFALO ROM                       | \$0F           | -40 C (0 +65°C   | 3 MHz     | MC68HC11E9BCPB3  |

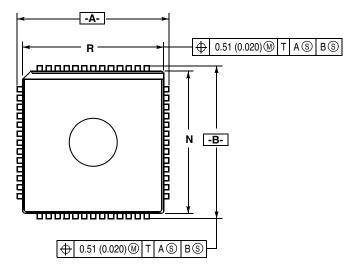

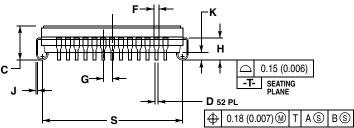

# 11.6 52-Pin Windowed Ceramic-Leaded Chip Carrier (Case 778B)

#### NOTES:

- DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.

- 2. CONTROLLING DIMENSION: INCH.

- DIMENSION R AND N DO NOT INCLUDE GLASS PROTRUSION. GLASS PROTRUSION TO BE 0.25 (0.010) MAXIMUM.

- 4. ALL DIMENSIONS AND TOLERANCES INCLUDE LEAD TRIM OFFSET AND LEAD

|        | INC   | HES   | MILLIN | IETERS |

|--------|-------|-------|--------|--------|

| DIM    | MIN   | MAX   | MIN    | MAX    |

| A      | 0.785 | 0.795 | 19.94  | 20.19  |

| В      | 0.785 | 0.795 | 19.94  | 20.19  |

| O      | 0.165 | 0.200 | 4.20   | 5.08   |

| ۵      | 0.017 | 0.021 | 0.44   | 0.53   |

| F      | 0.026 | 0.032 | 0.67   | 0.81   |

| G      | 0.050 | BSC   | 1.27   | BSC    |

| Ή      | 0.090 | 0.130 | 2.29   | 3.30   |

| 7      | 0.006 | 0.010 | 0.16   | 0.25   |

|        |       | 0.010 |        | 0.20   |

| K      | 0.035 | 0.045 | 0.89   | 1.14   |

| K<br>N |       |       |        |        |

|        | 0.035 | 0.045 | 0.89   | 1.14   |

199

illustrates the extreme measures used in the bootloader firmware to minimize memory usage. However, such measures are not usually considered good programming technique because they are misleading to someone trying to understand the program or use it as an example.

After initialization, a break character is transmitted [3] by the SCI. By connecting the TxD pin to the RxD pin (with a pullup because of port D wired-OR mode), this break will be received as a \$00 character and cause an immediate jump [4] to the start of the on-chip EEPROM (\$B600 in the MC68HC711E9). This feature is useful to pass control to a program in EEPROM essentially from reset. Refer to Common Bootstrap Mode Problems before using this feature.

If the first character is received as \$FF, the baud rate is assumed to be the default rate (7812 baud at a 2-MHz E-clock rate). If \$FF was sent at 1200 baud by the host, the SCI will receive the character as \$E0 or \$C0 because of the baud rate mismatch, and the bootloader will switch to 1200 baud [5] for the rest of the download operation. When the baud rate is switched to 1200 baud, the delay constant used to monitor the intercharacter delay also must be changed to reflect the new character time.

At [6], the Y index register is initialized to \$0000 to point to the start of on-chip RAM. The index register Y is used to keep track of where the next received data byte will be stored in RAM. The main loop for loading begins at [7].

The number of data bytes in the downloaded program can be any number between 0 and 512 bytes (the size of on-chip RAM). This procedure is called "variable-length download" and is accomplished by ending the download sequence when an idle time of at least four character times occurs after the last character to be downloaded. In M68HC11 Family members which have 256 bytes of RAM, the download length is fixed at exactly 256 bytes plus the leading \$FF character.

The intercharacter delay counter is started [8] by loading the delay constant from TOC1 into the X index register. The 19-E-cycle wait loop is executed repeatedly until either a character is received [9] or the allowed intercharacter delay time expires [10]. For 7812 baud, the delay constant is 10,241 E cycles (539 x 19 E cycles per loop). Four character times at 7812 baud is 10,240 E cycles (baud prescale of 4 x baud divider of 4 x 16 internal SCI clocks/bit time x 10 bit times/character x 4 character times). The delay from reset to the initial \$FF character is not critical since the delay counter is not started until after the first character (\$FF) is received.

To terminate the bootloading sequence and jump to the start of RAM without downloading any data to the on-chip RAM, simply send \$FF and nothing else. This feature is similar to the jump to EEPROM at [4] except the \$FF causes a jump to the start of RAM. This procedure requires that the RAM has been loaded with a valid program since it would make no sense to jump to a location in uninitialized memory.

After receiving a character, the downloaded byte is stored in RAM [11]. The data is transmitted back to the host [12] as an indication that the download is progressing normally. At [13], the RAM pointer is incremented to the next RAM address. If the RAM pointer has not passed the end of RAM, the main download loop (from [7] to [14]) is repeated.

When all data has been downloaded, the bootloader goes to [16] because of an intercharacter delay timeout [10] or because the entire 512-byte RAM has been filled [15]. At [16], the X and Y index registers are set up for calling the PROGRAM utility routine, which saves the user from having to do this in a downloaded program. The PROGRAM utility is fully explained in EPROM Programming Utility. The final step of the bootloader program is to jump to the start of RAM [17], which starts the user's downloaded program.

M68HC11 Bootstrap Mode, Rev. 1.1

#### **Driving Boot Mode from a Personal Computer**

## Operation

Configure the EVBU for boot mode operation by putting a jumper at J3. Ensure that the trace command jumper at J7 is not installed because this would connect the 12-V programming voltage to the OC5 output of the MCU.

Connect the EVBU to its dc power supply. When it is time to program the MCU EPROM, turn on the 12-volt programming power supply to the new circuitry in the wire-wrap area.

Connect the EVBU serial port to the appropriate serial port on the host system. For the Macintosh, this is the modem port with a modem cable. For the MS-DOS® computer, it is connected to COM1 with a straight through or modem cable. Power up the host system and start the BASIC program. If the program has not been compiled, this is accomplished from within the appropriate BASIC compiler or interpreter. Power up the EVBU.

Answer the prompt for filename with either a [RETURN] to accept the default shown or by typing in a new filename and pressing [RETURN].

The program will inform the user that it is working on converting the file from S records to binary. This process will take from 30 seconds to a few minutes, depending on the computer.

A prompt reading, "Comm port open?" will appear at the end of the file conversion. This is the last chance to ensure that everything is properly configured on the EVBU. Pressing [RETURN] will send the bootcode to the target MC68HC711E9. The program then informs the user that the bootload code is being sent to the target, and the results of the echoing of this code are displayed on the screen.

Another prompt reading "Programming is ready to begin. Are you?" will appear. Turn on the 12-volt programming power supply and press [RETURN] to start the actual programming of the target EPROM.

A count of the byte being verified will be updated continually on the screen as the programming progresses. Any failures will be flagged as they occur.

When programming is complete, a message will be displayed as well as a prompt requesting the user to press [RETURN] to quit.

Turn off the 12-volt programming power supply before turning off 5 volts to the EVBU.

<sup>&</sup>lt;sup>®</sup> MS-DOS is a registered trademark of Microsoft Corporation in the United States and oth175190er countries.

# **Listing 2. BASIC Program for Personal Computer**

```

3 1 *

E9BUF.BAS - A PROGRAM TO DEMONSTRATE THE USE OF THE BOOT MODE

ON THE HC11 BY PROGRAMMING AN HC711E9 WITH

5

BUFFALO 3.4

7 ' *

REQUIRES THAT THE S-RECORDS FOR BUFFALO (BUF34.S19)

8 ' *

BE AVAILABLE IN THE SAME DIRECTORY OR FOLDER

9 ' *

10 '*

THIS PROGRAM HAS BEEN RUN BOTH ON A MS-DOS COMPUTER

11 '*

USING QUICKBASIC 4.5 AND ON A MACINTOSH USING

12 '*

QUICKBASIC 1.0.

14 '*

25 H$ = "0123456789ABCDEF"

'STRING TO USE FOR HEX CONVERSIONS

30 DEFINT B, I: CODESIZE% = 8192: ADRSTART= 57344!

35 BOOTCOUNT = 25

'NUMBER OF BYTES IN BOOT CODE

'BUFFALO 3.4 IS 8K BYTES LONG

40 DIM CODE% (CODESIZE%)

45 BOOTCODE$ = ""

'INITIALIZE BOOTCODE$ TO NULL

49 REM **** READ IN AND SAVE THE CODE TO BE BOOT LOADED *****

'# OF BYTES IN BOOT CODE

50 FOR I = 1 TO BOOTCOUNT

55 READ Q$

60 A$ = MID$(Q$, 1, 1)

65 GOSUB 7000

'CONVERTS HEX DIGIT TO DECIMAL

70 \text{ TEMP} = 16 * X

'HANG ON TO UPPER DIGIT

75 A$ = MID$(Q$, 2, 1)

80 GOSUB 7000

85 \text{ TEMP} = \text{TEMP} + X

90 BOOTCODE$ = BOOTCODE$ + CHR$ (TEMP)

'BUILD BOOT CODE

95 NEXT I

96 REM **** S-RECORD CONVERSION STARTS HERE *****

97 FILNAMS="BUF34.S19"

'DEFAULT FILE NAME FOR S-RECORDS

100 CLS

105 PRINT "Filename.ext of S-record file to be downloaded (";FILNAM$;") ";

107 INPUT Q$

110 IF Q$<>"" THEN FILNAM$=Q$

120 OPEN FILNAM$ FOR INPUT AS #1

130 PRINT : PRINT "Converting "; FILNAM$; " to binary..."

999 REM ***** SCANS FOR 'S1' RECORDS *****

1000 GOSUB 6000

'GET 1 CHARACTER FROM INPUT FILE

1010 IF FLAG THEN 1250

'FLAG IS EOF FLAG FROM SUBROUTINE

1020 IF A$ <> "S" THEN 1000

1022 GOSUB 6000

1024 IF A$ <> "1" THEN 1000

1029 REM ***** S1 RECORD FOUND, NEXT 2 HEX DIGITS ARE THE BYTE COUNT *****

1030 GOSUB 6000

1040 GOSUB 7000

'RETURNS DECIMAL IN X

1050 BYTECOUNT = 16 * X

'ADJUST FOR HIGH NIBBLE

1060 GOSUB 6000

1070 GOSUB 7000

1080 BYTECOUNT = BYTECOUNT + X 'ADD LOW NIBBLE

```

#### M68HC11 Bootstrap Mode, Rev. 1.1

**Programming Procedure**

Programming MC68HC711E9 Devices with PCbug11 and the M68HC11EVBU, Rev. 0.1