Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                         |

|----------------------------|-------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                |

| Core Processor             | HC11                                                                    |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 3MHz                                                                    |

| Connectivity               | SCI, SPI                                                                |

| Peripherals                | POR, WDT                                                                |

| Number of I/O              | 38                                                                      |

| Program Memory Size        | 12KB (12K x 8)                                                          |

| Program Memory Type        | OTP                                                                     |

| EEPROM Size                | 512 x 8                                                                 |

| RAM Size                   | 512 x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                             |

| Data Converters            | A/D 8x8b                                                                |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 52-LCC (J-Lead)                                                         |

| Supplier Device Package    | 52-PLCC (19.1x19.1)                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc68hc711e9cfn3 |

# Chapter 1 General Description

#### 1.1 Introduction

This document contains a detailed description of the M68HC11 E series of 8-bit microcontroller units (MCUs). These MCUs all combine the M68HC11 central processor unit (CPU) with high-performance, on-chip peripherals.

The E series is comprised of many devices with various configurations of:

- Random-access memory (RAM)

- Read-only memory (ROM)

- Erasable programmable read-only memory (EPROM)

- Electrically erasable programmable read-only memory (EEPROM)

- Several low-voltage devices are also available.

With the exception of a few minor differences, the operation of all E-series MCUs is identical. A fully static design and high-density complementary metal-oxide semiconductor (HCMOS) fabrication process allow the E-series devices to operate at frequencies from 3 MHz to dc with very low power consumption.

## 1.2 Features

Features of the E-series devices include:

- M68HC11 CPU

- Power-saving stop and wait modes

- Low-voltage devices available (3.0–5.5 Vdc)

- 0, 256, 512, or 768 bytes of on-chip RAM, data retained during standby

- 0, 12, or 20 Kbytes of on-chip ROM or EPROM

- 0, 512, or 2048 bytes of on-chip EEPROM with block protect for security

- 2048 bytes of EEPROM with selectable base address in the MC68HC811E2

- Asynchronous non-return-to-zero (NRZ) serial communications interface (SCI)

- Additional baud rates available on MC68HC(7)11E20

- Synchronous serial peripheral interface (SPI)

- 8-channel, 8-bit analog-to-digital (A/D) converter

- 16-bit timer system:

- Three input capture (IC) channels

- Four output compare (OC) channels

- One additional channel, selectable as fourth IC or fifth OC

- 8-bit pulse accumulator

- Real-time interrupt circuit

#### **General Description**

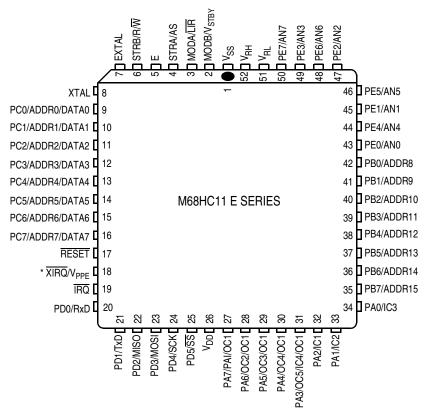

$<sup>^{\</sup>star}$   $V_{\mbox{\footnotesize{PPE}}}$  applies only to devices with EPROM/OTPROM.

Figure 1-2. Pin Assignments for 52-Pin PLCC and CLCC

# **Chapter 2 Operating Modes and On-Chip Memory**

### 2.1 Introduction

This section contains information about the operating modes and the on-chip memory for M68HC11 E-series MCUs. Except for a few minor differences, operation is identical for all devices in the E series. Differences are noted where necessary.

# 2.2 Operating Modes

The values of the mode select inputs MODB and MODA during reset determine the operating mode. Single-chip and expanded multiplexed are the normal modes.

- In single-chip mode only on-chip memory is available.

- Expanded mode, however, allows access to external memory.

Each of the two normal modes is paired with a special mode:

- Bootstrap, a variation of the single-chip mode, is a special mode that executes a bootloader program in an internal bootstrap ROM.

- Test is a special mode that allows privileged access to internal resources.

# 2.2.1 Single-Chip Mode

In single-chip mode, ports B and C and strobe pins A (STRA) and B (STRB) are available for general-purpose parallel input/output (I/O). In this mode, all software needed to control the MCU is contained in internal resources. If present, read-only memory (ROM) and/or erasable, programmable read-only memory (EPROM) will always be enabled out of reset, ensuring that the reset and interrupt vectors will be available at locations \$FFCO-\$FFFF.

#### NOTE

For the MC68HC811E2, the vector locations are the same; however, they are contained in the 2048-byte EEPROM array.

#### 2.2.2 Expanded Mode

In expanded operating mode, the MCU can access the full 64-Kbyte address space. The space includes:

- The same on-chip memory addresses used for single-chip mode

- Addresses for external peripherals and memory devices

The expansion bus is made up of ports B and C, and control signals AS (address strobe) and R/W (read/write). R/W and AS allow the low-order address and the 8-bit data bus to be multiplexed on the same pins. During the first half of each bus cycle address information is present. During the second half of each bus cycle the pins become the bidirectional data bus. AS is an active-high latch enable signal for an external address latch. Address information is allowed through the transparent latch while AS is high and is latched when AS drives low.

M68HC11E Family Data Sheet, Rev. 5.1

69

#### 4.2.6.5 Interrupt Mask (I)

The interrupt request (IRQ) mask (I bit) is a global mask that disables all maskable interrupt sources. While the I bit is set, interrupts can become pending, but the operation of the CPU continues uninterrupted until the I bit is cleared. After any reset, the I bit is set by default and can only be cleared by a software instruction. When an interrupt is recognized, the I bit is set after the registers are stacked, but before the interrupt vector is fetched. After the interrupt has been serviced, a return-from-interrupt instruction is normally executed, restoring the registers to the values that were present before the interrupt occurred. Normally, the I bit is 0 after a return from interrupt is executed. Although the I bit can be cleared within an interrupt service routine, "nesting" interrupts in this way should only be done when there is a clear understanding of latency and of the arbitration mechanism. Refer to Chapter 5 Resets and Interrupts.

#### 4.2.6.6 Half Carry (H)

The H bit is set when a carry occurs between bits 3 and 4 of the arithmetic logic unit during an ADD, ABA, or ADC instruction. Otherwise, the H bit is cleared. Half carry is used during BCD operations.

#### 4.2.6.7 X Interrupt Mask (X)

The XIRQ mask (X) bit disables interrupts from the XIRQ pin. After any reset, X is set by default and must be cleared by a software instruction. When an XIRQ interrupt is recognized, the X and I bits are set after the registers are stacked, but before the interrupt vector is fetched. After the interrupt has been serviced, an RTI instruction is normally executed, causing the registers to be restored to the values that were present before the interrupt occurred. The X interrupt mask bit is set only by hardware (RESET or XIRQ acknowledge). X is cleared only by program instruction (TAP, where the associated bit of A is 0; or RTI, where bit 6 of the value loaded into the CCR from the stack has been cleared). There is no hardware action for clearing X.

# 4.2.6.8 STOP Disable (S)

Setting the STOP disable (S) bit prevents the STOP instruction from putting the M68HC11 into a low-power stop condition. If the STOP instruction is encountered by the CPU while the S bit is set, it is treated as a no-operation (NOP) instruction, and processing continues to the next instruction. S is set by reset; STOP is disabled by default.

# 4.3 Data Types

The M68HC11 CPU supports four data types:

- 1. Bit data

- 2. 8-bit and 16-bit signed and unsigned integers

- 3. 16-bit unsigned fractions

- 4. 16-bit addresses

A byte is eight bits wide and can be accessed at any byte location. A word is composed of two consecutive bytes with the most significant byte at the lower value address. Because the M68HC11 is an 8-bit CPU, there are no special requirements for alignment of instructions or operands.

M68HC11E Family Data Sheet, Rev. 5.1

#### 4.5.3 Extended

In the extended addressing mode, the effective address of the argument is contained in two bytes following the opcode byte. These are 3-byte instructions (or 4-byte instructions if a prebyte is required). One or two bytes are needed for the opcode and two for the effective address.

#### 4.5.4 Indexed

In the indexed addressing mode, an 8-bit unsigned offset contained in the instruction is added to the value contained in an index register (IX or IY). The sum is the effective address. This addressing mode allows referencing any memory location in the 64-Kbyte address space. These are 2- to 5-byte instructions, depending on whether or not a prebyte is required.

#### 4.5.5 Inherent

In the inherent addressing mode, all the information necessary to execute the instruction is contained in the opcode. Operations that use only the index registers or accumulators, as well as control instructions with no arguments, are included in this addressing mode. These are 1- or 2-byte instructions.

#### 4.5.6 Relative

The relative addressing mode is used only for branch instructions. If the branch condition is true, an 8-bit signed offset included in the instruction is added to the contents of the program counter to form the effective branch address. Otherwise, control proceeds to the next instruction. These are usually 2-byte instructions.

#### 4.6 Instruction Set

Refer to Table 4-2, which shows all the M68HC11 instructions in all possible addressing modes. For each instruction, the table shows the operand construction, the number of machine code bytes, and execution time in CPU E-clock cycles.

# **Central Processor Unit (CPU)**

# Table 4-2. Instruction Set (Sheet 5 of 7)

| NA         | 0                                  | Description (                       | Addressing                        | Ir                            | nstruction              |                       |   |              | Co | onditio | n Co | des |   |   |

|------------|------------------------------------|-------------------------------------|-----------------------------------|-------------------------------|-------------------------|-----------------------|---|--------------|----|---------|------|-----|---|---|

| Mnemonic   | Operation                          | Description                         | Mode                              | Opcode                        | Operand                 | Cycles                | S | Х            | Н  | П       | N    | Z   | ٧ | С |

| LSRD       | Logical Shift<br>Right Double      | 0                                   | INH                               | 04                            | _                       | 3                     | _ | _            | _  | _       | 0    | Δ   | Δ | Δ |

| MUL        | Multiply 8 by 8                    | $A * B \Rightarrow D$               | INH                               | 3D                            | _                       | 10                    | _ | _            | _  | _       | _    | _   | _ | Δ |

| NEG (opr)  | Two's<br>Complement<br>Memory Byte | 0 − M ⇒ M                           | EXT<br>IND,X<br>IND,Y             | 70<br>60<br>18 60             | hh 11<br>ff<br>ff       | 6<br>6<br>7           | _ | _            | _  | _       | Δ    | Δ   | Δ | Δ |

| NEGA       | Two's<br>Complement<br>A           | 0 − A ⇒ A                           | A INH                             | 40                            | _                       | 2                     | _ | _            | _  | _       | Δ    | Δ   | Δ | Δ |

| NEGB       | Two's<br>Complement<br>B           | 0 − B ⇒ B                           | B INH                             | 50                            | _                       | 2                     | _ | -            | _  | _       | Δ    | Δ   | Δ | Δ |

| NOP        | No operation                       | No Operation                        | INH                               | 01                            | _                       | 2                     | _ | _            | _  | _       | _    | _   | _ | _ |

| ORAA (opr) | OR<br>Accumulator<br>A (Inclusive) | A + M ⇒ A                           | A IMM A DIR A EXT A IND,X A IND,Y | 8A<br>9A<br>BA<br>AA<br>18 AA | ii<br>dd<br>hh ll<br>ff | 2<br>3<br>4<br>4<br>5 | _ | _            | _  | _       | Δ    | Δ   | 0 | _ |

| ORAB (opr) | OR<br>Accumulator<br>B (Inclusive) | B + M ⇒ B                           | B IMM B DIR B EXT B IND,X B IND,Y | CA<br>DA<br>FA<br>EA<br>18 EA | ii<br>dd<br>hh ll<br>ff | 2<br>3<br>4<br>4<br>5 | _ | _            | _  | _       | Δ    | Δ   | 0 | _ |

| PSHA       | Push A onto<br>Stack               | ,                                   | A INH                             | 36                            | _                       | 3                     | _ | _            | _  | _       | _    | _   | _ | _ |

| PSHB       | Push B onto<br>Stack               | $B \Rightarrow Stk, SP = SP - 1$    |                                   | 37                            | _                       | 3                     | _ | _            | _  | _       | _    | _   | _ | _ |

| PSHX       | Push X onto<br>Stack (Lo<br>First) | $IX \Rightarrow Stk, SP = SP - 2$   | INH                               | 3C                            | _                       | 4                     | _ | _            | _  | _       | _    | _   | _ | _ |

| PSHY       | Push Y onto<br>Stack (Lo<br>First) | $IY \Rightarrow Stk, SP = SP - 2$   | INH                               | 18 3C                         | _                       | 5                     | _ | _            | _  | _       | _    | _   | _ | _ |

| PULA       | Pull A from<br>Stack               | $SP = SP + 1, A \leftarrow Stk$     | A INH                             | 32                            | _                       | 4                     | _ | _            | _  | _       | _    | _   | _ | _ |

| PULB       | Pull B from<br>Stack               | $SP = SP + 1, B \Leftarrow Stk$     | B INH                             | 33                            | _                       | 4                     | _ | -            | _  | _       | _    | _   | _ | _ |

| PULX       | Pull X From<br>Stack (Hi<br>First) | $SP = SP + 2$ , $IX \Leftarrow Stk$ | INH                               | 38                            | _                       | 5                     | _ | _            | _  | _       | _    | _   | _ | _ |

| PULY       | Pull Y from<br>Stack (Hi<br>First) | $SP = SP + 2$ , $IY \Leftarrow Stk$ | INH                               | 18 38                         | _                       | 6                     | _ | _            | _  | _       | _    | _   | _ | _ |

| ROL (opr)  | Rotate Left                        | C b7 b0                             | EXT<br>IND,X<br>IND,Y             | 79<br>69<br>18 69             | hh 11<br>ff<br>ff       | 6<br>6<br>7           | _ | _            | _  | _       | Δ    | Δ   | Δ | Δ |

| ROLA       | Rotate Left A                      | C b7 b0                             | A INH                             | 49                            | _                       | 2                     | _ | -            | _  | _       | Δ    | Δ   | Δ | Δ |

| ROLB       | Rotate Left B                      | C b7 b0                             | B INH                             | 59                            | _                       | 2                     | _ | _            | _  | _       | Δ    | Δ   | Δ | Δ |

| ROR (opr)  | Rotate Right                       | b7 b0 C                             | EXT<br>IND,X<br>IND,Y             | 76<br>66<br>18 66             | hh 11<br>ff<br>ff       | 6<br>6<br>7           | _ | _            | _  | _       | Δ    | Δ   | Δ | Δ |

| RORA       | Rotate Right A                     | b7 b0 C                             | A INH                             | 46                            | _                       | 2                     | _ | _            | _  | _       | Δ    | Δ   | Δ | Δ |

| RORB       | Rotate Right B                     | b7 b0 C                             | B INH                             | 56                            | _                       | 2                     | _ |              | _  | _       | Δ    | Δ   | Δ | Δ |

| RTI        | Return from<br>Interrupt           | See Figure 3–2                      | INH                               | 3B                            | _                       | 12                    | Δ | $\downarrow$ | Δ  | Δ       | Δ    | Δ   | Δ | Δ |

| RTS        | Return from<br>Subroutine          | See Figure 3–2                      | INH                               | 39                            | _                       | 5                     | _ |              | _  | _       | _    | _   |   |   |

| SBA        | Subtract B from<br>A               | $A - B \Rightarrow A$               | INH                               | 10                            | _                       | 2                     | _ | _            | _  | _       | Δ    | Δ   | Δ | Δ |

end of the interrupt service routine, the return-from-interrupt instruction is executed and the saved registers are pulled from the stack in reverse order so that normal program execution can resume. Refer to Chapter 4 Central Processor Unit (CPU).

**Memory Location CPU Registers** SP **PCL** SP-1 **PCH** SP-2 **IYL** SP-3 IYH SP-4 IXL SP-5 IXH SP-6 **ACCA** SP-7 **ACCB** CCR SP-8

Table 5-5. Stacking Order on Entry to Interrupts

# 5.5.2 Non-Maskable Interrupt Request (XIRQ)

Non-maskable interrupts are useful because they can always interrupt CPU operations. The most common use for such an interrupt is for serious system problems, such as program runaway or power failure. The XIRQ input is an updated version of the NMI (non-maskable interrupt) input of earlier MCUs.

Upon reset, both the X bit and I bit of the CCR are set to inhibit all maskable interrupts and  $\overline{\text{XIRQ}}$ . After minimum system initialization, software can clear the X bit by a TAP instruction, enabling  $\overline{\text{XIRQ}}$  interrupts. Thereafter, software cannot set the X bit. Thus, an  $\overline{\text{XIRQ}}$  interrupt is a non-maskable interrupt. Because the operation of the I-bit-related interrupt structure has no effect on the X bit, the internal  $\overline{\text{XIRQ}}$  pin remains unmasked. In the interrupt priority logic, the  $\overline{\text{XIRQ}}$  interrupt has a higher priority than any source that is maskable by the I bit. All I-bit-related interrupts operate normally with their own priority relationship.

When an I-bit-related interrupt occurs, the I bit is automatically set by hardware after stacking the CCR byte. The X bit is not affected. When an X-bit-related interrupt occurs, both the X and I bits are automatically set by hardware after stacking the CCR. A return-from-interrupt instruction restores the X and I bits to their pre-interrupt request state.

## 5.5.3 Illegal Opcode Trap

Because not all possible opcodes or opcode sequences are defined, the MCU includes an illegal opcode detection circuit, which generates an interrupt request. When an illegal opcode is detected and the interrupt is recognized, the current value of the program counter is stacked. After interrupt service is complete, reinitialize the stack pointer so repeated execution of illegal opcodes does not cause stack underflow. Left uninitialized, the illegal opcode vector can point to a memory location that contains an illegal opcode. This condition causes an infinite loop that causes stack underflow. The stack grows until the system crashes.

The illegal opcode trap mechanism works for all unimplemented opcodes on all four opcode map pages. The address stacked as the return address for the illegal opcode interrupt is the address of the first byte of the illegal opcode. Otherwise, it would be almost impossible to determine whether the illegal opcode had been one or two bytes. The stacked return address can be used as a pointer to the illegal opcode so the illegal opcode service routine can evaluate the offending opcode.

# **Serial Communications Interface (SCI)**

**Table 7-1. Baud Rate Values**

|                   |      |      |      |      |        |               |          | Crystal Frequency (MHz) |              |              |              |              |               |

|-------------------|------|------|------|------|--------|---------------|----------|-------------------------|--------------|--------------|--------------|--------------|---------------|

|                   |      |      |      |      |        | Prescale      | Baud     | 4.00                    | 4.9152       | 8.00         | 10.00        | 12.00        | 16.00         |

| Prescaler Selects |      |      |      |      | Divide | Set<br>Divide |          | Bus Frequency (MHz)     |              |              |              |              |               |

| SCP2              | SCP1 | SCP0 | SCR2 | SCR1 | SCR0   |               |          | 1.00                    | 1.23         | 2.00         | 2.50         | 3.00         | 4.00          |

| 0                 | 0    | 0    | 0    | 0    | 0      | 1             | 1        | 62500                   | 76800        | 125000       | 156250       | 187500       | 250000        |

| 0                 | 0    | 0    | 0    | 0    | 1      | 1             | 2        | 31250                   | 38400        | 62500        | 78125        | 93750        | 125000        |

| 0                 | 0    | 0    | 0    | 1    | 0      | 1             | 4        | 15625                   | 19200        | 31250        | 39063        | 46875        | 62500         |

| 0                 | 0    | 0    | 0    | 1    | 1      | 1             | 8        | 7813                    | 9600         | 15625        | 19531        | 23438        | 31250         |

| 0                 | 0    | 0    | 1    | 0    | 0      | 1             | 16       | 3906                    | 4800         | 7813         | 9766         | 11719        | 15625         |

| 0                 | 0    | 0    | 1    | 0    | 1      | 1<br>1        | 32<br>64 | 1953<br>977             | 2400         | 3906         | 4883         | 5859         | 7813          |

| 0                 | 0    | 0    |      | 1    | 0      | 1             | 128      | 977<br>488              | 1200<br>600  | 1953<br>977  | 2441<br>1221 | 2930<br>1465 | 3906<br>1953  |

|                   | _    | _    | · ·  |      |        |               |          |                         |              |              |              |              |               |

| 0                 | 0    | 1    | 0    | 0    | 0      | 3             | 1        | 20833                   | 25600        | 41667        | 52083        | 62500        | 83333         |

| 0                 | 0    | 1    | 0    | 0    | 1      | 3             | 2        | 10417                   | 12800        | 20833        | 26042        | 31250        | 41667         |

| 0                 | 0    | 1    | 0    | 1    | 0      | 3             | 4        | 5208                    | 6400         | 10417        | 13021        | 15625        | 20833         |

| 0                 | 0    | 1    | 0    | 1 0  | 1<br>0 | 3<br>3        | 8<br>16  | 2604<br>1302            | 3200<br>1600 | 5208<br>2604 | 6510<br>3255 | 7813<br>3906 | 10417<br>5208 |

| 0                 | 0    | 1 1  |      | 0    | 1      | 3             | 32       | 651                     | 800          | 1302         | 3255<br>1628 | 1953         | 2604          |

| 0                 | 0    |      |      | 1    | 0      | 3             | 64       | 326                     | 400          | 651          | 814          | 977          | 1302          |

| 0                 | 0    | 1    | 1    | 1    | 1      | 3             | 128      | 163                     | 200          | 326          | 407          | 488          | 651           |

| 0                 | 1    | 0    | 0    | 0    | 0      | 4             | 1        | 15625                   | 19200        | 31250        | 39063        | 46875        | 62500         |

| 0                 | 1    | 0    | 0    | 0    | 1      | 4             | 2        | 7813                    | 9600         | 15625        | 19531        | 23438        | 31250         |

| 0                 | 1    | 0    | 0    | 1    | 0      | 4             | 4        | 3906                    | 4800         | 7813         | 9766         | 11719        | 15625         |

| 0                 | 1    | 0    | 0    | 1    | 1      | 4             | 8        | 1953                    | 2400         | 3906         | 4883         | 5859         | 7813          |

| 0                 | 1    | 0    | 1    | 0    | 0      | 4             | 16       | 977                     | 1200         | 1953         | 2441         | 2930         | 3906          |

| 0                 | 1    | 0    | 1    | 0    | 1      | 4             | 32       | 488                     | 600          | 977          | 1221         | 1465         | 1953          |

| 0                 | 1    | 0    | 1    | 1    | 0      | 4             | 64       | 244                     | 300          | 488          | 610          | 732          | 977           |

| 0                 | 1    | 0    | 1    | 1    | 1      | 4             | 128      | 122                     | 150          | 244          | 305          | 366          | 488           |

| 0                 | 1    | 1    | 0    | 0    | 0      | 13            | 1        | 4808                    | 5908         | 9615         | 12019        | 14423        | 19231         |

| 0                 | 1    | 1    | 0    | 0    | 1      | 13            | 2        | 2404                    | 2954         | 4808         | 6010         | 7212         | 9615          |

| 0                 | 1    | 1    | 0    | 1    | 0      | 13            | 4        | 1202                    | 1477         | 2404         | 3005         | 3606         | 4808          |

| 0                 | 1    | 1    | 0    | 1    | 1      | 13            | 8        | 601                     | 738          | 1202         | 1502         | 1803         | 2404          |

| 0                 | 1    | 1    | 1    | 0    | 0      | 13            | 16       | 300                     | 369          | 601          | 751          | 901          | 1202          |

| 0                 | 1    | 1    | 1    | 0    | 1      | 13            | 32<br>64 | 150                     | 185          | 300          | 376          | 451          | 601           |

| 0                 | 1    | 1    | 1    | 1    | 0      | 13<br>13      | 128      | 75<br>38                | 92<br>46     | 150<br>75    | 188<br>94    | 225<br>113   | 300<br>150    |

|                   | · ·  |      | · ·  | -    |        |               |          |                         |              |              |              |              |               |

| 1                 | 0    | 0    | 0    | 0    | 0      | 39            | 1        | 1603                    | 1969         | 3205         | 4006         | 4808         | 6410          |

| 1                 | 0    | 0    | 0    | 0    | 1      | 39            | 2        | 801<br>401              | 985<br>492   | 1603<br>801  | 2003         | 2404<br>1202 | 3205<br>1603  |

| 1 1               | 0    | 0    | 0    | 1 1  | 0      | 39<br>39      | 4<br>Ω   | 200                     | 492<br>246   | 401          | 1002<br>501  | 601          | 801           |

| 1                 | 0    | 0    | 1    | 0    | 1<br>0 | 39<br>39      | 8<br>16  | 100                     | 123          | 200          | 250          | 300          | 401           |

|                   | 0    | 0    |      | 0    | 1      | 39            | 32       | 50                      | 62           | 100          | 125          | 150          | 200           |

| li                | 0    | 0    | 1    | 1    | 0      | 39            | 64       | 25                      | 31           | 50           | 63           | 75           | 100           |

| li                | 0    | Ö    |      | li   | 1      | 39            | 128      | 13                      | 15           | 25           | 31           | 38           | 50            |

| <u>'</u>          |      |      | '    | '    | '      | - 55          | 120      | .0                      | ٠٠           | 20           | 01           | - 50         | - 50          |

Shaded areas reflect standard baud rates. On MC68HC(7)11E20 do not set SCP1 or SCP0 when SCP2 is 1.

Serial Peripheral Interface (SPI)

# 8.5.3 Serial Clock

SCK, an input to a slave device, is generated by the master device and synchronizes data movement in and out of the device through the MOSI and MISO lines. Master and slave devices are capable of exchanging a byte of information during a sequence of eight clock cycles.

Four possible timing relationships can be chosen by using control bits CPOL and CPHA in the serial peripheral control register (SPCR). Both master and slave devices must operate with the same timing. The SPI clock rate select bits, SPR[1:0], in the SPCR of the master device, select the clock rate. In a slave device, SPR[1:0] have no effect on the operation of the SPI.

#### 8.5.4 Slave Select

The slave select  $(\overline{SS})$  input of a slave device must be externally asserted before a master device can exchange data with the slave device.  $\overline{SS}$  must be low before data transactions and must stay low for the duration of the transaction.

The  $\overline{SS}$  line of the master must be held high. If it goes low, a mode fault error flag (MODF) is set in the serial peripheral status register (SPSR). To disable the mode fault circuit, write a 1 in bit 5 of the port D data direction register. This sets the  $\overline{SS}$  pin to act as a general-purpose output rather than the dedicated input to the slave select circuit, thus inhibiting the mode fault flag. The other three lines are dedicated to the SPI whenever the serial peripheral interface is on.

The state of the master and slave CPHA bits affects the operation of  $\overline{SS}$ . CPHA settings should be identical for master and slave. When CPHA = 0, the shift clock is the OR of  $\overline{SS}$  with SCK. In this clock phase mode,  $\overline{SS}$  must go high between successive characters in an SPI message. When CPHA = 1,  $\overline{SS}$  can be left low between successive SPI characters. In cases where there is only one SPI slave MCU, its  $\overline{SS}$  line can be tied to  $V_{SS}$  as long as only CPHA = 1 clock mode is used.

# 8.6 SPI System Errors

Two system errors can be detected by the SPI system. The first type of error arises in a multiple-master system when more than one SPI device simultaneously tries to be a master. This error is called a mode fault. The second type of error, write collision, indicates that an attempt was made to write data to the SPDR while a transfer was in progress.

When the SPI system is configured as a master and the  $\overline{SS}$  input line goes to active low, a mode fault error has occurred — usually because two devices have attempted to act as master at the same time. In cases where more than one device is concurrently configured as a master, there is a chance of contention between two pin drivers. For push-pull CMOS drivers, this contention can cause permanent damage. The mode fault mechanism attempts to protect the device by disabling the drivers. The MSTR control bit in the SPCR and all four DDRD control bits associated with the SPI are cleared and an interrupt is generated subject to masking by the SPIE control bit and the I bit in the CCR.

Other precautions may need to be taken to prevent driver damage. If two devices are made masters at the same time, mode fault does not help protect either one unless one of them selects the other as slave. The amount of damage possible depends on the length of time both devices attempt to act as master.

A write collision error occurs if the SPDR is written while a transfer is in progress. Because the SPDR is not double buffered in the transmit direction, writes to SPDR cause data to be written directly into the SPI shift register. Because this write corrupts any transfer in progress, a write collision error is generated. The transfer continues undisturbed, and the write data that caused the error is not written to the shifter.

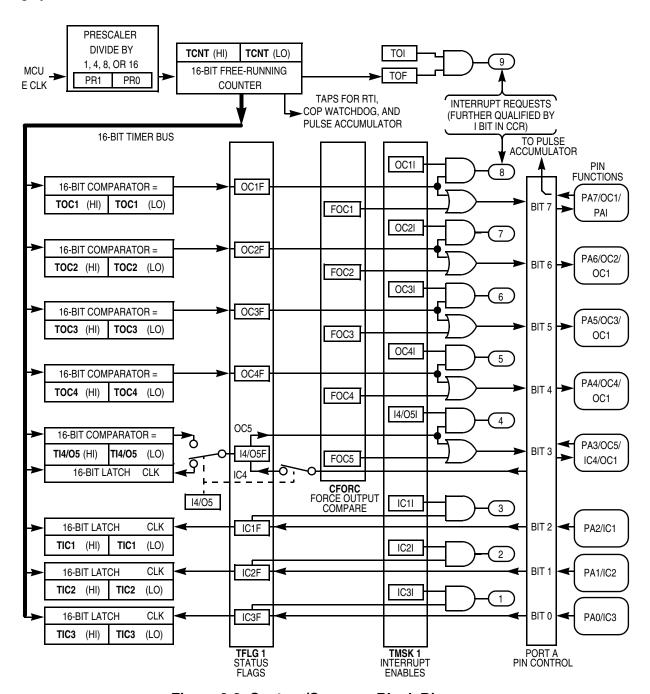

#### **Timing Systems**

Figure 9-2. Capture/Compare Block Diagram

#### **Timing Systems**

# FOC[1:5] — Force Output Comparison Bit

When the FOC bit associated with an output compare circuit is set, the output compare circuit immediately performs the action it is programmed to do when an output match occurs.

0 = Not affected

1 = Output x action occurs

#### Bits [2:0] — Unimplemented

Always read 0

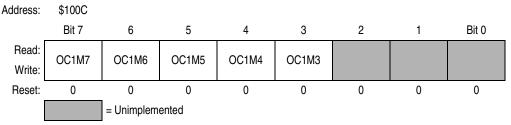

# 9.4.3 Output Compare Mask Register

Use OC1M with OC1 to specify the bits of port A that are affected by a successful OC1 compare. The bits of the OC1M register correspond to PA[7:3].

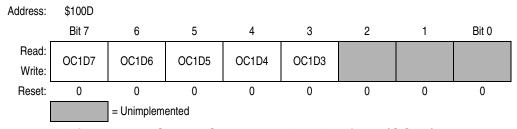

Figure 9-13. Output Compare 1 Mask Register (OC1M)

#### OC1M[7:3] — Output Compare Masks

0 = OC1 disabled

1 = OC1 enabled to control the corresponding pin of port A

#### Bits [2:0] — Unimplemented

Always read 0

# 9.4.4 Output Compare Data Register

Use this register with OC1 to specify the data that is to be stored on the affected pin of port A after a successful OC1 compare. When a successful OC1 compare occurs, a data bit in OC1D is stored in the corresponding bit of port A for each bit that is set in OC1M.

Figure 9-14. Output Compare 1 Data Register (OC1D)

If OC1Mx is set, data in OC1Dx is output to port A bit x on successful OC1 compares.

#### Bits [2:0] — Unimplemented

Always read 0

#### **Timing Systems**

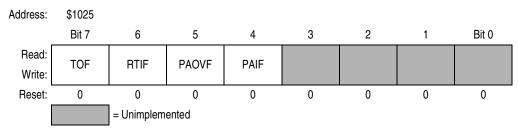

## 9.4.10 Timer Interrupt Flag Register 2

Bits in this register indicate when certain timer system events have occurred. Coupled with the four high-order bits of TMSK2, the bits of TFLG2 allow the timer subsystem to operate in either a polled or interrupt driven system. Each bit of TFLG2 corresponds to a bit in TMSK2 in the same position.

Figure 9-20. Timer Interrupt Flag 2 Register (TFLG2)

Clear flags by writing a 1 to the corresponding bit position(s).

#### TOF — Timer Overflow Interrupt Flag

Set when TCNT changes from \$FFFF to \$0000

#### RTIF — Real-Time (Periodic) Interrupt Flag

Refer to 9.5 Real-Time Interrupt (RTI).

#### PAOVF — Pulse Accumulator Overflow Interrupt Flag

Refer to 9.7 Pulse Accumulator.

#### PAIF — Pulse Accumulator Input Edge Interrupt Flag

Refer to 9.7 Pulse Accumulator.

#### Bits [3:0] — Unimplemented

Always read 0

# 9.5 Real-Time Interrupt (RTI)

The real-time interrupt (RTI) feature, used to generate hardware interrupts at a fixed periodic rate, is controlled and configured by two bits (RTR1 and RTR0) in the pulse accumulator control (PACTL) register. The RTII bit in the TMSK2 register enables the interrupt capability. The four different rates available are a product of the MCU oscillator frequency and the value of bits RTR[1:0]. Refer to Table 9-5, which shows the periodic real-time interrupt rates.

Table 9-5. RTI Rates

| RTR[1:0] | E = 3 MHz | E = 2 MHz | E = 1 MHz | E = X MHz            |

|----------|-----------|-----------|-----------|----------------------|

| 0 0      | 2.731 ms  | 4.096 ms  | 8.192 ms  | (E/2 <sup>13</sup> ) |

| 0 1      | 5.461 ms  | 8.192 ms  | 16.384 ms | (E/2 <sup>14</sup> ) |

| 1 0      | 10.923 ms | 16.384 ms | 32.768 ms | (E/2 <sup>15</sup> ) |

| 1 1      | 21.845 ms | 32.768 ms | 65.536 ms | (E/2 <sup>16</sup> ) |

The clock source for the RTI function is a free-running clock that cannot be stopped or interrupted except by reset. This clock causes the time between successive RTI timeouts to be a constant that is

## PEDGE — Pulse Accumulator Edge Control Bit

Refer to 9.7 Pulse Accumulator.

#### DDRA3 — Data Direction for Port A Bit 3

Refer to Chapter 6 Parallel Input/Output (I/O) Ports.

## 14/O5 — Input Capture 4/Output Compare Bit

Refer to 9.7 Pulse Accumulator.

#### RTR[1:0] — RTI Interrupt Rate Select Bits

These two bits determine the rate at which the RTI system requests interrupts. The RTI system is driven by an E divided by 2<sup>13</sup> rate clock that is compensated so it is independent of the timer prescaler. These two control bits select an additional division factor. Refer to Table 9-5.

# 9.6 Computer Operating Properly (COP) Watchdog Function

The clocking chain for the COP function, tapped off of the main timer divider chain, is only superficially related to the main timer system. The CR[1:0] bits in the OPTION register and the NOCOP bit in the CONFIG register determine the status of the COP function. One additional register, COPRST, is used to arm and clear the COP watchdog reset system. Refer to Chapter 5 Resets and Interrupts for a more detailed discussion of the COP function.

### 9.7 Pulse Accumulator

The M68HC11 Family of MCUs has an 8-bit counter that can be configured to operate either as a simple event counter or for gated time accumulation, depending on the state of the PAMOD bit in the PACTL register. Refer to the pulse accumulator block diagram, Figure 9-24. In the event counting mode, the 8-bit counter is clocked to increasing values by an external pin. The maximum clocking rate for the external event counting mode is the E clock divided by two. In gated time accumulation mode, a free-running E-clock divide-by-64 signal drives the 8-bit counter, but only while the external PAI pin is activated. Refer to Table 9-6. The pulse accumulator counter can be read or written at any time.

| Crystal<br>Frequency | E Clock | Cycle Time | E ÷ 64   | PACNT<br>Overflow |

|----------------------|---------|------------|----------|-------------------|

| 4.0 MHz              | 1 MHz   | 1000 ns    | 64 μs    | 16.384 ms         |

| 8.0 MHz              | 2 MHz   | 500 ns     | 32 μs    | 8.192 ms          |

| 12.0 MHz             | 3 MHz   | 333 ns     | 21.33 μs | 5.461 ms          |

Table 9-6. Pulse Accumulator Timing

Pulse accumulator control bits are also located within two timer registers, TMSK2 and TFLG2, as described in the following paragraphs.

M68HC11E Family Data Sheet, Rev. 5.1 Freescale Semiconductor 143

# **Chapter 10 Electrical Characteristics**

## 10.1 Introduction

This section contains electrical specifications for the M68HC11 E-series devices.

# 10.2 Maximum Ratings for Standard and Extended Voltage Devices

Maximum ratings are the extreme limits to which the microcontroller unit (MCU) can be exposed without permanently damaging it.

#### NOTE

This device is not guaranteed to operate properly at the maximum ratings. Refer to 10.5 DC Electrical Characteristics, 10.6 Supply Currents and Power Dissipation, 10.7 MC68L11E9/E20 DC Electrical Characteristics, and 10.8 MC68L11E9/E20 Supply Currents and Power Dissipation for guaranteed operating conditions.

| Rating                                                                                                                        | Symbol           | Value        | Unit |

|-------------------------------------------------------------------------------------------------------------------------------|------------------|--------------|------|

| Supply voltage                                                                                                                | V <sub>DD</sub>  | -0.3 to +7.0 | V    |

| Input voltage                                                                                                                 | V <sub>In</sub>  | -0.3 to +7.0 | V    |

| Current drain per pin $^{(1)}$ excluding $\rm V_{DD},  V_{SS},  AV_{DD},  V_{RH},  V_{RL},  and  \overline{\rm XIRQ/V_{PPE}}$ | I <sub>D</sub>   | 25           | mA   |

| Storage temperature                                                                                                           | T <sub>STG</sub> | -55 to +150  | °C   |

<sup>1.</sup> One pin at a time, observing maximum power dissipation limits

#### **NOTE**

This device contains circuitry to protect the inputs against damage due to high static voltages or electric fields; however, it is advised that normal precautions be taken to avoid application of any voltage higher than maximum-rated voltages to this high-impedance circuit. For proper operation, it is recommended that  $V_{In}$  and  $V_{Out}$  be constrained to the range  $V_{SS} \leq (V_{In} \text{ or } V_{Out}) \leq V_{DD}$ . Reliability of operation is enhanced if unused inputs are connected to an appropriate logic voltage level (for example, either  $V_{SS}$  or  $V_{DD}$ ).

#### **Electrical Characteristics**

# 10.8 MC68L11E9/E20 Supply Currents and Power Dissipation

| Characteristic <sup>(1)</sup>                                                                                                                                                                                                        | Symbol           | 1 MHz                | 2 MHz                 | Unit |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|----------------------|-----------------------|------|

| Run maximum total supply current <sup>(2)</sup> Single-chip mode $V_{DD} = 5.5 \text{ V}$ $V_{DD} = 3.0 \text{ V}$ Expanded multiplexed mode $V_{DD} = 5.5 \text{ V}$ $V_{DD} = 5.5 \text{ V}$                                       | I <sub>DD</sub>  | 8<br>4<br>14<br>7    | 15<br>8<br>27<br>14   | mA   |

| Wait maximum total supply current <sup>(2)</sup> (all peripheral functions shut down) Single-chip mode $V_{DD} = 5.5 \text{ V}$ $V_{DD} = 3.0 \text{ V}$ Expanded multiplexed mode $V_{DD} = 5.5 \text{ V}$ $V_{DD} = 3.0 \text{ V}$ | W <sub>IDD</sub> | 3<br>1.5<br>5<br>2.5 | 6<br>3<br>10<br>5     | mA   |

| Stop maximum total supply current <sup>(2)</sup> Single-chip mode, no clocks $V_{DD} = 5.5 \text{ V}$ $V_{DD} = 3.0 \text{ V}$                                                                                                       | S <sub>IDD</sub> | 50<br>25             | 50<br>25              | μΑ   |

| Maximum power dissipation Single-chip mode 2 MHz 3 MHz Expanded multiplexed mode 2 MHz 3 MHz                                                                                                                                         | P <sub>D</sub>   | 44<br>12<br>77<br>21 | 85<br>24<br>150<br>42 | mW   |

<sup>1.</sup>  $V_{DD}$  = 3.0 Vdc to 5.5 Vdc,  $V_{SS}$  = 0 Vdc,  $T_A$  =  $T_L$  to  $T_H$ , unless otherwise noted 2. EXTAL is driven with a square wave, and  $t_{CYC}$  = 500 ns for 2 MHz rating  $t_{CYC}$  = 333 ns for 3 MHz rating  $V_{IL} \le 0.2 \text{ V}$   $V_{IH} \ge V_{DD} - 0.2 \text{ V}$  no dc loads

#### **Electrical Characteristics**

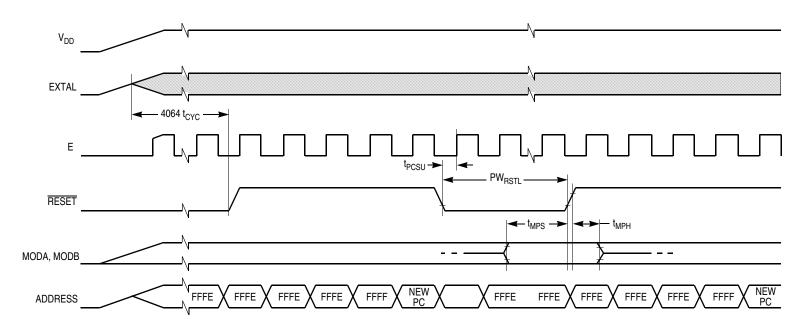

# 10.9 Control Timing

| Oh (1) (2)                                                                                                          | Symbol             | 1.0 MHz  |     | 2.0 MHz |     | 3.0 MHz |      | Unit             |  |

|---------------------------------------------------------------------------------------------------------------------|--------------------|----------|-----|---------|-----|---------|------|------------------|--|

| Characteristic <sup>(1)</sup> (2)                                                                                   |                    | Min      | Max | Min     | Max | Min     | Max  | Oiiit            |  |

| Frequency of operation                                                                                              | f <sub>o</sub>     | dc       | 1.0 | dc      | 2.0 | dc      | 3.0  | MHz              |  |

| E-clock period                                                                                                      | t <sub>CYC</sub>   | 100<br>0 | _   | 500     | _   | 333     | _    | ns               |  |

| Crystal frequency                                                                                                   | f <sub>XTAL</sub>  | _        | 4.0 | _       | 8.0 | _       | 12.0 | MHz              |  |

| External oscillator frequency                                                                                       | 4 f <sub>o</sub>   | dc       | 4.0 | dc      | 8.0 | dc      | 12.0 | MHz              |  |

| Processor control setup time  t <sub>PCSU</sub> = 1/4 t <sub>CYC</sub> + 50 ns                                      | t <sub>PCSU</sub>  | 300      | _   | 175     | _   | 133     | _    | ns               |  |

| Reset input pulse width To guarantee external reset vector Minimum input time (can be pre-empted by internal reset) | PW <sub>RSTL</sub> | 8<br>1   | _   | 8<br>1  | _   | 8<br>1  |      | t <sub>CYC</sub> |  |

| Mode programming setup time                                                                                         | t <sub>MPS</sub>   | 2        | _   | 2       | _   | 2       | _    | t <sub>CYC</sub> |  |

| Mode programming hold time                                                                                          | t <sub>MPH</sub>   | 10       | _   | 10      | _   | 10      | _    | ns               |  |

| Interrupt pulse width, $\overline{IRQ}$ edge-sensitive mode $PW_{IRQ} = t_{CYC} + 20 \text{ ns}$                    | PW <sub>IRQ</sub>  | 102<br>0 | _   | 520     | _   | 353     | _    | ns               |  |

| Wait recovery startup time                                                                                          | t <sub>WRS</sub>   | _        | 4   | _       | 4   | _       | 4    | t <sub>CYC</sub> |  |

| Timer pulse width input capture pulse accumulator input PW <sub>TIM</sub> = t <sub>CYC</sub> + 20 ns                | PW <sub>TIM</sub>  | 102<br>0 | _   | 520     | _   | 353     | _    | ns               |  |

V<sub>DD</sub> = 5.0 Vdc ±10%, V<sub>SS</sub> = 0 Vdc, T<sub>A</sub> = T<sub>L</sub> to T<sub>H</sub>, all timing is shown with respect to 20% V<sub>DD</sub> and 70% V<sub>DD</sub>, unless otherwise noted

RESET is recognized during the first clock cycle it is held low. Internal circuitry then drives the pin low for four clock cycles, releases the pin, and samples the pin level two cycles later to determine the source of the interrupt. Refer to Chapter 5 Resets and Interrupts for further detail.

Figure 10-3. POR External Reset Timing Diagram

# **Ordering Information and Mechanical Specifications**

| Description                       | CONFIG         | Temperature     | Frequency | MC Order Number  |

|-----------------------------------|----------------|-----------------|-----------|------------------|

| 52-pin plastic leaded chip carrie | er (PLCC) (Con | tinued)         |           |                  |

|                                   |                | -40°C to +85°C  | 2 MHz     | MC68HC711E9CFN2  |

| OTDDOM                            | фо <u>г</u>    | -40°C (0 +65°C  | 3 MHz     | MC68HC711E9CFN3  |

| OTPROM                            | \$0F           | -40°C to +105°C | 2 MHz     | MC68HC711E9VFN2  |

|                                   |                | -40°C to +125°C | 2 MHz     | MC68HC711E9MFN2  |

| OTPROM, enhanced security feature | \$0F           | -40°C to +85°C  | 2 MHz     | MC68S711E9CFN2   |

|                                   |                | 0°C to +70°C    | 3 MHz     | MC68HC711E20FN3  |

|                                   |                | 400C to . 050C  | 2 MHz     | MC68HC711E20CFN2 |

| 20 Kbytes OTPROM                  | \$0F           | -40°C to +85°C  | 3 MHz     | MC68HC711E20CFN3 |

|                                   |                | -40°C to +105°C | 2 MHz     | MC68HC711E20VFN2 |

|                                   |                | -40°C to +125°C | 2 MHz     | MC68HC711E20MFN2 |

|                                   |                | 0°C to +70°C    | 2 MHz     | MC68HC811E2FN2   |

| No DOM 2 Voytoo FEDDOM            | <b>4</b>       | -40°C to +85°C  | 2 MHz     | MC68HC811E2CFN2  |

| No ROM, 2 Kbytes EEPROM           | \$FF           | -40°C to +105°C | 2 MHz     | MC68HC811E2VFN2  |

|                                   |                | -40°C to +125°C | 2 MHz     | MC68HC811E2MFN2  |

| 64-pin quad flat pack (QFP)       |                |                 |           |                  |

| BUFFALO ROM                       | ¢or            | 40°C to . 95°C  | 2 MHz     | MC68HC11E9BCFU2  |

| BUFFALU RUW                       | \$0F           | −40°C to +85°C  | 3 MHz     | MC68HC11E9BCFU3  |

|                                   |                | -40°C to +85°C  | 2 MHz     | MC68HC11E1CFU2   |

| No ROM                            | \$0D           | -40 C to +65 C  | 3 MHz     | MC68HC11E1CFU3   |

|                                   |                | -40°C to +105°C | 2 MHz     | MC68HC11E1VFU2   |

| No ROM, no EEPROM                 | \$0C           | -40°C to +85°C  | 2 MHz     | MC68HC11E0CFU2   |

| NO NOW, NO EEPHOW                 | <b>ФОС</b>     | -40°C to +105°C | 2 MHz     | MC68HC11E0VFU2   |

|                                   |                | 0°C to +70°°C   | 3 MHz     | MC68HC711E20FU3  |

|                                   |                | -40°C to +85°C  | 2 MHz     | MC68HC711E20CFU2 |

| 20 Kbytes OTPROM                  | \$0F           | -40 C (0 +65°C  | 3 MHz     | MC68HC711E20CFU3 |

|                                   |                | -40°C to +105°C | 2 MHz     | MC68HC711E20VFU2 |

|                                   |                | -40°C to +125°C | 2 MHz     | MC68HC711E20MFU2 |

| 52-pin thin quad flat pack (TQF)  | P)             |                 |           |                  |

| BUFFALO ROM                       | 4              |                 | 2 MHz     | MC68HC11E9BCPB2  |

| DUFFALU NUM                       | \$0F           | -40°C to +85°C  | 3 MHz     | MC68HC11E9BCPB3  |

201

# **UPLOAD Utility**

The UPLOAD utility subroutine transfers data from the MCU to a host computer system over the SCI serial data link.

#### NOTE

Only EPROM versions of the M68HC11 include this utility.

Verification of EPROM contents is one example of how the UPLOAD utility could be used. Before calling this program, the Y index register is loaded (by user firmware) with the address of the first data byte to be uploaded. If a baud rate other than the current SCI baud rate is to be used for the upload process, the user's firmware must also write to the baud register. The UPLOAD program sends successive bytes of data out the SCI transmitter until a reset is issued (the upload loop is infinite).

For a complete commented listing example of the UPLOAD utility, refer to Listing 3. MC68HC711E9 Bootloader ROM.

## **EPROM Programming Utility**

The EPROM programming utility is one way of programming data into the internal EPROM of the MC68HC711E9 MCU. An external 12-V programming power supply is required to program on-chip EPROM. The simplest way to use this utility program is to bootload a 3-byte program consisting of a single jump instruction to the start of the PROGRAM utility program (\$BF00). The bootloader program sets the X and Y index registers to default values before jumping to the downloaded program (see [16] at the bottom of Figure 3). When the host computer sees the \$FF character, data to be programmed into the EPROM is sent, starting with the character for location \$D000. After the last byte to be programmed is sent to the MC68HC711E9 and the corresponding verification data is returned to the host, the programming operation is terminated by resetting the MCU.

The number of bytes to be programmed, the first address to be programmed, and the programming time can be controlled by the user if values other than the default values are desired.

To understand the detailed operation of the EPROM programming utility, refer to Figure 4 during the following discussion. Figure 4 is composed of three interrelated parts. The upper-left portion shows the flowchart of the PROGRAM utility running in the boot ROM of the MCU. The upper-right portion shows the flowchart for the user-supplied driver program running in the host computer. The lower portion of Figure 4 is a timing sequence showing the relationship of operations between the MCU and the host computer. Reference numbers in the flowcharts in the upper half of Figure 4 have matching numbers in the lower half to help the reader relate the three parts of the figure.

The shaded area [1] refers to the software and hardware latency in the MCU leading to the transmission of a character (in this case, the \$FF). The shaded area [2] refers to a similar latency in the host computer (in this case, leading to the transmission of the first data character to the MCU).

The overall operation begins when the MCU sends the first character (\$FF) to the host computer, indicating that it is ready for the first data character. The host computer sends the first data byte [3] and enters its main loop. The second data character is sent [4], and the host then waits [5] for the first verify byte to come back from the MCU.

M68HC11 Bootstrap Mode, Rev. 1.1

#### **Common Bootstrap Mode Problems**

```

8491 '*

DECIMAL TO HEX CONVERSION

8492 '*

INPUT: K - INTEGER TO BE CONVERTED

8493 '*

OUTPUT: HX$ - TWO CHARACTER STRING WITH HEX CONVERSION

8494 '***********************

8500 IF K > 255 THEN HX$="Too big":GOTO 8530

'UPPER NIBBLE

8510 HX$=MID$(H$,K\16+1,1)

8520 HX$=HX$+MID$(H$,(K MOD 16)+1,1) 'LOWER NIBBLE

8530 RETURN

9500 DATA 86, 23

'LDAA

#$23

9510 DATA B7, 10, 02

'STAA

OPT2

make port C wire or

#$FE

9520 DATA 86, FE

'LDAA

9530 DATA B7, 10, 03

PORTC

light 1 LED on port C bit 0

'STAA

9540 DATA C6, FF

'LDAB

#$FF

9550 DATA F7, 10, 07

make port C outputs

'STAB

DDRC

9560 DATA CE, OF, A0

'LDX

#4000

2msec at 2MHz

9570 DATA 18, CE, E0, 00

'LDY

#$E000 Start of BUFFALO 3.4

9580 DATA 7E, BF, 00

'JMP

$BF00

EPROM routine start address

```

# **Common Bootstrap Mode Problems**

It is not unusual for a user to encounter problems with bootstrap mode because it is new to many users. By knowing some of the common difficulties, the user can avoid them or at least recognize and quickly correct them.

#### Reset Conditions vs. Conditions as Bootloaded Program Starts

It is common to confuse the reset state of systems and control bits with the state of these systems and control bits when a bootloaded program in RAM starts.

Between these times, the bootloader program is executed, which changes the states of some systems and control bits:

- The SCI system is initialized and turned on (Rx and Tx).

- The SCI system has control of the PD0 and PD1 pins.

- Port D outputs are configured for wire-OR operation.

- The stack pointer is initialized to the top of RAM.

- Time has passed (two or more SCI character times).

- Timer has advanced from its reset count value.

Users also forget that bootstrap mode is a special mode. Thus, privileged control bits are accessible, and write protection for some registers is not in effect. The bootstrap ROM is in the memory map. The DISR bit in the TEST1 control register is set, which disables resets from the COP and clock monitor systems.

Since bootstrap is a special mode, these conditions can be changed by software. The bus can even be switched from single-chip mode to expanded mode to gain access to external memories and peripherals.

M68HC11 Bootstrap Mode, Rev. 1.1 218 Freescale Semiconductor