### NXP USA Inc. - MC68HC711E9CFNE3 Datasheet

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                 |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | HC11                                                                     |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 3MHz                                                                     |

| Connectivity               | SCI, SPI                                                                 |

| Peripherals                | POR, WDT                                                                 |

| Number of I/O              | 38                                                                       |

| Program Memory Size        | 12KB (12K x 8)                                                           |

| Program Memory Type        | OTP                                                                      |

| EEPROM Size                | 512 x 8                                                                  |

| RAM Size                   | 512 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                              |

| Data Converters            | A/D 8x8b                                                                 |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 52-LCC (J-Lead)                                                          |

| Supplier Device Package    | 52-PLCC (19.1x19.1)                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc68hc711e9cfne3 |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

**Revision History**

# **Revision History**

| Date              | Revision<br>Level | Description                                                                                                                   | Page<br>Number(s) |

|-------------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------|-------------------|

| May, 2001 3.1     |                   | 2.3.3.1 System Configuration Register — Addition to NOCOP bit description                                                     | 44                |

| Way, 2001         | 3.1               | Added 10.21 EPROM Characteristics                                                                                             | 175               |

| June, 2001        | 3.2               | 10.21 EPROM Characteristics — For clarity, addition to note 2 following the table                                             | 175               |

| December,<br>2001 | 3.3               | 7.7.2 Serial Communications Control Register 1 — SCCR1 bit 4 (M) description corrected                                        | 110               |

|                   |                   | 10.7 MC68L11E9/E20 DC Electrical Characteristics — Title changed to include the MC68L11E20                                    | 153               |

|                   |                   | 10.8 MC68L11E9/E20 Supply Currents and Power Dissipation — Title changed to include the MC68L11E20                            | 154               |

|                   |                   | 10.10 MC68L11E9/E20 Control Timing — Title changed to include the MC68L11E20                                                  | 157               |

|                   |                   | 10.12 MC68L11E9/E20 Peripheral Port Timing — Title changed to include the MC68L11E20                                          | 163               |

| July, 2002        | 4                 | 10.14 MC68L11E9/E20 Analog-to-Digital Converter Characteristics — Title changed to include the MC68L11E20                     | 167               |

|                   |                   | 10.16 MC68L11E9/E20 Expansion Bus Timing Characteristics — Title changed to include the MC68L11E20                            | 169               |

|                   |                   | 10.18 MC68L11E9/E20 Serial Peirpheral Interface Characteristics — Title changed to include the MC68L11E20                     | 172               |

|                   |                   | — Title changed to include the MC68L11E20                                                                                     | 175               |

|                   |                   | 11.4 Extended Voltage Device Ordering Information (3.0 Vdc to 5.5 Vdc) — Updated table to include MC68L1120                   | 181               |

|                   |                   | Format updated to current publications standards                                                                              | Throughout        |

| hun - 0000        | F                 | 1.4.6 Non-Maskable Interrupt (XIRQ/VPPE) — Added Caution note pertaining to EPROM programming of the MC68HC711E9 device only. | 23                |

| June, 2003        | 5                 | 6.4 Port C — Clarified description of DDRC[7:0] bits                                                                          | 100               |

|                   |                   | 10.21 EPROM Characteristics — Added note pertaining to EPROM programming of the MC68HC711E9 device only.                      | 175               |

| July, 2005        | 5.1               | Updated to meet Freescale identity guidelines.                                                                                | Throughout        |

### General Description

- Computer operating properly (COP) watchdog system

- 38 general-purpose input/output (I/O) pins:

- 16 bidirectional I/O pins

- 11 input-only pins

- 11 output-only pins

- Several packaging options:

- 52-pin plastic-leaded chip carrier (PLCC)

- 52-pin windowed ceramic leaded chip carrier (CLCC)

- 52-pin plastic thin quad flat pack, 10 mm x 10 mm (TQFP)

- 64-pin quad flat pack (QFP)

- 48-pin plastic dual in-line package (DIP), MC68HC811E2 only

- 56-pin plastic shrink dual in-line package, .070-inch lead spacing (SDIP)

## 1.3 Structure

See Figure 1-1 for a functional diagram of the E-series MCUs. Differences among devices are noted in the table accompanying Figure 1-1.

# **1.4 Pin Descriptions**

M68HC11 E-series MCUs are available packaged in:

- 52-pin plastic-leaded chip carrier (PLCC)

- 52-pin windowed ceramic leaded chip carrier (CLCC)

- 52-pin plastic thin quad flat pack, 10 mm x 10 mm (TQFP)

- 64-pin quad flat pack (QFP)

- 48-pin plastic dual in-line package (DIP), MC68HC811E2 only

- 56-pin plastic shrink dual in-line package, .070-inch lead spacing (SDIP)

Most pins on these MCUs serve two or more functions, as described in the following paragraphs. Refer to Figure 1-2, Figure 1-3, Figure 1-4, Figure 1-5, and Figure 1-6 which show the M68HC11 E-series pin assignments for the PLCC/CLCC, QFP, TQFP, SDIP, and DIP packages.

### 2.3.3.1 System Configuration Register

The system configuration register (CONFIG) consists of an EEPROM byte and static latches that control the startup configuration of the MCU. The contents of the EEPROM byte are transferred into static working latches during reset sequences. The operation of the MCU is controlled directly by these latches and not by CONFIG itself. In normal modes, changes to CONFIG do not affect operation of the MCU until after the next reset sequence. When programming, the CONFIG register itself is accessed. When the CONFIG register is read, the static latches are accessed. See 2.5.1 EEPROM and CONFIG Programming and Erasure for information on modifying CONFIG.

To take full advantage of the MCU's functionality, customers can program the CONFIG register in bootstrap mode. This can be accomplished by setting the mode pins to logic 0 and downloading a small program to internal RAM. For more information, Freescale application note AN1060 entitled M68HC11 Bootstrap Mode has been included at the back of this document. The downloadable talker will consist of:

- Bulk erase

- Byte programming

- Communication server

All of this functionality is provided by PCbug11 which can be found on the Freescale Web site at http://www.freescale.com. For more information on using PCbug11 to program an E-series device, Freescale engineering bulletin EB296 entitled Programming MC68HC711E9 Devices with PCbug11 and the M68HC11EVBU has been included at the back of this document.

### **NOTE** The CONFIG register on the 68HC11 is an EEPROM cell and must be programmed accordingly.

Operation of the CONFIG register in the MC68HC811E2 differs from other devices in the M68HC11 E series. See Figure 2-10 and Figure 2-11.

| Address:        | \$103F |            |       |   |       |       |       |       |

|-----------------|--------|------------|-------|---|-------|-------|-------|-------|

|                 | Bit 7  | 6          | 5     | 4 | 3     | 2     | 1     | Bit 0 |

| Read:<br>Write: |        |            |       |   | NOSEC | NOCOP | ROMON | EEON  |

| Resets:         |        |            |       |   |       |       |       |       |

| Single chip:    | 0      | 0          | 0     | 0 | U     | U     | 1     | U     |

| Bootstrap:      | 0      | 0          | 0     | 0 | U     | U(L)  | U     | U     |

| Expanded:       | 0      | 0          | 0     | 0 | 1     | U     | U     | U     |

| Test:           | 0      | 0          | 0     | 0 | 1     | U(L)  | U     | U     |

|                 |        | = Unimplem | ented |   |       |       |       |       |

U indicates a previously programmed bit. U(L) indicates that the bit resets to the logic level held in the latch prior to reset, but the function of COP is controlled by the DISR bit in TEST1 register.

### Figure 2-10. System Configuration Register (CONFIG)

| Table 2 | 2-4. RAM Mapping | Table 2-5. R | egister Mapping |

|---------|------------------|--------------|-----------------|

| RAM[3:0 | ] Address        | REG[3:0]     | Address         |

| 0000    | \$0000-\$0xFF    | 0000         | \$0000-\$003F   |

| 0001    | \$1000–\$1xFF    | 0001         | \$1000-\$103F   |

| 0010    | \$2000–\$2xFF    | 0010         | \$2000-\$203F   |

| 0011    | \$3000–\$3xFF    | 0011         | \$3000-\$303F   |

| 0100    | \$4000–\$4xFF    | 0100         | \$4000-\$403F   |

| 0101    | \$5000–\$5xFF    | 0101         | \$5000-\$503F   |

| 0110    | \$6000-\$6xFF    | 0110         | \$6000-\$603F   |

| 0111    | \$7000–\$7xFF    | 0111         | \$7000–\$703F   |

| 1000    | \$8000-\$8xFF    | 1000         | \$8000-\$803F   |

| 1001    | \$9000-\$9xFF    | 1001         | \$9000-\$903F   |

| 1010    | \$A000-\$AxFF    | 1010         | \$A000-\$A03F   |

| 1011    | \$B000-\$BxFF    | 1011         | \$B000-\$B03F   |

| 1100    | \$C000-\$CxFF    | 1100         | \$C000-\$C03F   |

| 1101    | \$D000-\$DxFF    | 1101         | \$D000-\$D03F   |

| 1110    | \$E000-\$ExFF    | 1110         | \$E000-\$E03F   |

| 1111    | \$F000-\$FxFF    | 1111         | \$F000-\$F03F   |

|         |                  |              |                 |

### Table 2-4. RAM Mapping

## 2.3.3.3 System Configuration Options Register

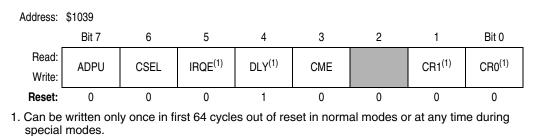

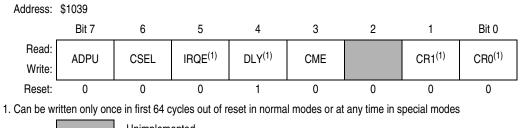

The 8-bit, special-purpose system configuration options register (OPTION) sets internal system configuration options during initialization. The time protected control bits, IRQE, DLY, and CR[1:0], can be written only once after a reset and then they become read-only. This minimizes the possibility of any accidental changes to the system configuration.

= Unimplemented

### Figure 2-13. System Configuration Options Register (OPTION)

### ADPU — Analog-to-Digital Converter Power-Up Bit

Refer to Chapter 3 Analog-to-Digital (A/D) Converter.

### CSEL — Clock Select Bit

Selects alternate clock source for on-chip EEPROM charge pump. Refer to 2.5.1 EEPROM and CONFIG Programming and Erasure for more information on EEPROM use.

CSEL also selects the clock source for the A/D converter, a function discussed in Chapter 3 Analog-to-Digital (A/D) Converter.

### **Operating Modes and On-Chip Memory**

## 2.4.1 Programming an Individual EPROM Address

- In this method, the MCU programs its own EPROM by controlling the PPROG register (EPROG in MC68HC711E20). Use these procedures to program the EPROM through the MCU with:

- The ROMON bit set in the CONFIG register

- The 12-volt nominal programming voltage present on the XIRQ/V<sub>PPE</sub> pin

- The IRQ pin must be pulled high.

## NOTE

Any operating mode can be used.

This example applies to all devices with EPROM/OTPROM except for the MC68HC711E20.

| LDAB<br>STAB | #\$20<br>\$103B                     | Set ELAT bit in (EPGM = 0) to enable                                |

|--------------|-------------------------------------|---------------------------------------------------------------------|

|              |                                     | EPROM latches.                                                      |

| STAA         | \$0,X                               | Store data to EPROM address                                         |

| LDAB         | #\$21                               |                                                                     |

| STAB         | \$103B                              | Set EPGM bit with ELAT = 1 to enable                                |

|              |                                     | EPROM programming voltage                                           |

| JSR          | DLYEP                               | Delay 2-4 ms                                                        |

| CLR          | \$103B                              | Turn off programming voltage and set<br>to READ mode                |

|              | STAB<br>STAA<br>LDAB<br>STAB<br>JSR | STAB \$103B<br>STAA \$0,X<br>LDAB #\$21<br>STAB \$103B<br>JSR DLYEP |

This example applies only to MC68HC711E20.

| EPROG | LDAB<br>STAB | #\$20<br>\$1036 | Set ELAT bit (EPGM = 0) to enable<br>EPROM latches.               |

|-------|--------------|-----------------|-------------------------------------------------------------------|

|       | STAA<br>LDAB | \$0,X<br>#\$21  | Store data to EPROM address                                       |

|       | STAB         | \$1036          | Set EPGM bit with ELAT = 1 to enable<br>EPROM programming voltage |

|       | JSR          | DLYEP           | Delay 2-4 ms                                                      |

|       | CLR          | \$1036          | Turn off programming voltage and set<br>to READ mode              |

## 2.4.2 Programming the EPROM with Downloaded Data

When using this method, the EPROM is programmed by software while in the special test or bootstrap modes. User-developed software can be uploaded through the SCI or a ROM-resident EPROM programming utility can be used. The 12-volt nominal programming voltage must be present on the XIRQ/V<sub>PPE</sub> pin. To use the resident utility, bootload a 3-byte program consisting of a single jump instruction to \$BF00. \$BF00 is the starting address of a resident EPROM programming utility. The utility program sets the X and Y index registers to default values, then receives programming data from an external host, and puts it in EPROM. The value in IX determines programming delay time. The value in IY is a pointer to the first address in EPROM to be programmed (default = \$D000).

When the utility program is ready to receive programming data, it sends the host the \$FF character. Then it waits. When the host sees the \$FF character, the EPROM programming data is sent, starting with the first location in the EPROM array. After the last byte to be programmed is sent and the corresponding verification data is returned, the programming operation is terminated by resetting the MCU.

For more information, Freescale application note AN1060 entitled M68HC11 Bootstrap Mode has been included at the back of this document.

Analog-to-Digital (A/D) Converter

# 3.3 A/D Converter Power-Up and Clock Select

Bit 7 of the OPTION register controls A/D converter power-up. Clearing ADPU removes power from and disables the A/D converter system. Setting ADPU enables the A/D converter system. Stabilization of the analog bias voltages requires a delay of as much as 100 µs after turning on the A/D converter. When the A/D converter system is operating with the MCU E clock, all switching and comparator operations are inherently synchronized to the main MCU clocks. This allows the comparator output to be sampled at relatively quiet times during MCU clock cycles. Since the internal RC oscillator is asynchronous to the MCU clock, there is more error attributable to internal system clock noise. A/D converter accuracy is reduced slightly while the internal RC oscillator is being used (CSEL = 1).

= Unimplemented

## Figure 3-4. System Configuration Options Register (OPTION)

### ADPU — A/D Power-Up Bit

- 0 = A/D powered down

- 1 = A/D powered up

## CSEL — Clock Select Bit

- 0 = A/D and EEPROM use system E clock.

- 1 = A/D and EEPROM use internal RC clock.

### IRQE — Configure IRQ for Edge-Sensitive Only Operation

Refer to Chapter 5 Resets and Interrupts.

### DLY — Enable Oscillator Startup Delay Bit

- 0 = The oscillator startup delay coming out of stop is bypassed and the MCU resumes processing within about four bus cycles.

- 1 = A delay of approximately 4000 E-clock cycles is imposed as the MCU is started up from the stop power-saving mode. This delay allows the crystal oscillator to stabilize.

### CME — Clock Monitor Enable Bit

Refer to Chapter 5 Resets and Interrupts.

### Bit 2 — Not implemented

Always reads 0

### CR[1:0] — COP Timer Rate Select Bits

Refer to Chapter 5 Resets and Interrupts and Chapter 9 Timing Systems.

When this control bit is clear, the four requested conversions are performed once to fill the four result registers. When this control bit is set, conversions are performed continuously with the result registers updated as data becomes available.

## MULT — Multiple Channel/Single Channel Control Bit

When this bit is clear, the A/D converter system is configured to perform four consecutive conversions on the single channel specified by the four channel select bits CD:CA (bits [3:0] of the ADCTL register). When this bit is set, the A/D system is configured to perform a conversion on each of four channels where each result register corresponds to one channel.

### NOTE

When the multiple-channel continuous scan mode is used, extra care is needed in the design of circuitry driving the A/D inputs. The charge on the capacitive DAC array before the sample time is related to the voltage on the previously converted channel. A charge share situation exists between the internal DAC capacitance and the external circuit capacitance. Although the amount of charge involved is small, the rate at which it is repeated is every 64  $\mu$ s for an E clock of 2 MHz. The RC charging rate of the external circuit must be balanced against this charge sharing effect to avoid errors in accuracy. Refer to M68HC11 Reference Manual, Freescale document order number M68HC11RM/AD, for further information.

### CD:CA — Channel Selects D:A Bits

Refer to Table 3-2. When a multiple channel mode is selected (MULT = 1), the two least significant channel select bits (CB and CA) have no meaning and the CD and CC bits specify which group of four channels is to be converted.

| Channel Select<br>Control Bits | Channel Signal                      | Result in ADRx<br>if MULT = 1 |

|--------------------------------|-------------------------------------|-------------------------------|

| CD:CC:CB:CA                    |                                     |                               |

| 0000                           | AN0                                 | ADR1                          |

| 0001                           | AN1                                 | ADR2                          |

| 0010                           | AN2                                 | ADR3                          |

| 0011                           | AN3                                 | ADR4                          |

| 0100                           | AN4                                 | ADR1                          |

| 0101                           | AN5                                 | ADR2                          |

| 0110                           | AN6                                 | ADR3                          |

| 0111                           | AN7                                 | ADR4                          |

| 10XX                           | Reserved                            | —                             |

| 1100                           | V <sub>RH</sub> <sup>(1)</sup>      | ADR1                          |

| 1101                           | V <sub>RL</sub> <sup>(1)</sup>      | ADR2                          |

| 1110                           | (V <sub>RH</sub> )/2 <sup>(1)</sup> | ADR3                          |

| 1111                           | Reserved <sup>(1)</sup>             | ADR4                          |

Table 3-2. A/D Converter Channel Selection

1. Used for factory testing

Analog-to-Digital (A/D) Converter

# 3.10 A/D Converter Result Registers

These read-only registers hold an 8-bit conversion result. Writes to these registers have no effect. Data in the A/D converter result registers is valid when the CCF flag in the ADCTL register is set, indicating a conversion sequence is complete. If conversion results are needed sooner, refer to Figure 3-3, which shows the A/D conversion sequence diagram.

| Register name: Analog-to-Digital Converter Result Register 1 Address: \$1031 |               |               |                |            |                |       |       |       |

|------------------------------------------------------------------------------|---------------|---------------|----------------|------------|----------------|-------|-------|-------|

|                                                                              | Bit 7         | 6             | 5              | 4          | 3              | 2     | 1     | Bit 0 |

| Read:                                                                        | Bit 7         | Bit 6         | Bit 5          | Bit 4      | Bit 3          | Bit 2 | Bit 1 | Bit 0 |

| Write:                                                                       |               |               |                |            |                |       |       |       |

| Reset:                                                                       |               |               | Ir             | ndetermina | te after rese  | et    |       |       |

| Register nan                                                                 | ne: Analog-to | -Digital Conv | erter Result F | Register 2 | Address: \$103 | 32    |       |       |

|                                                                              | Bit 7         | 6             | 5              | 4          | 3              | 2     | 1     | Bit 0 |

| Read:                                                                        | Bit 7         | Bit 6         | Bit 5          | Bit 4      | Bit 3          | Bit 2 | Bit 1 | Bit 0 |

| Write:                                                                       |               |               |                |            |                |       |       |       |

| Reset:                                                                       |               |               | Ir             | ndetermina | te after rese  | et    |       |       |

| Register nan                                                                 | ne: Analog-to | -Digital Conv | erter Result F | Register 3 | Address: \$103 | 33    |       |       |

|                                                                              | Bit 7         | 6             | 5              | 4          | 3              | 2     | 1     | Bit 0 |

| Read:                                                                        | Bit 7         | Bit 6         | Bit 5          | Bit 4      | Bit 3          | Bit 2 | Bit 1 | Bit 0 |

| Write:                                                                       |               |               |                |            |                |       |       |       |

| Reset:                                                                       |               |               | Ir             | ndetermina | te after rese  | et    |       |       |

| Register nan                                                                 | ne: Analog-to | -Digital Conv | erter Result F | Register 4 | Address: \$103 | 34    |       |       |

|                                                                              | Bit 7         | 6             | 5              | 4          | 3              | 2     | 1     | Bit 0 |

| Read:                                                                        | Bit 7         | Bit 6         | Bit 5          | Bit 4      | Bit 3          | Bit 2 | Bit 1 | Bit 0 |

| Write:                                                                       |               |               |                |            |                |       |       |       |

| Reset:                                                                       |               |               | Ir             | ndetermina | te after rese  | et    |       |       |

|                                                                              |               | = Unimplem    | ented          |            |                |       |       |       |

### Figure 3-6. Analog-to-Digital Converter Result Registers (ADR1–ADR4)

**Central Processor Unit (CPU)**

# 4.4 Opcodes and Operands

The M68HC11 Family of microcontrollers uses 8-bit opcodes. Each opcode identifies a particular instruction and associated addressing mode to the CPU. Several opcodes are required to provide each instruction with a range of addressing capabilities. Only 256 opcodes would be available if the range of values were restricted to the number able to be expressed in 8-bit binary numbers.

A 4-page opcode map has been implemented to expand the number of instructions. An additional byte, called a prebyte, directs the processor from page 0 of the opcode map to one of the other three pages. As its name implies, the additional byte precedes the opcode.

A complete instruction consists of a prebyte, if any, an opcode, and zero, one, two, or three operands. The operands contain information the CPU needs for executing the instruction. Complete instructions can be from one to five bytes long.

# 4.5 Addressing Modes

Six addressing modes can be used to access memory:

- Immediate

- Direct

- Extended

- Indexed

- Inherent

- Relative

These modes are detailed in the following paragraphs. All modes except inherent mode use an effective address. The effective address is the memory address from which the argument is fetched or stored or the address from which execution is to proceed. The effective address can be specified within an instruction, or it can be calculated.

## 4.5.1 Immediate

In the immediate addressing mode, an argument is contained in the byte(s) immediately following the opcode. The number of bytes following the opcode matches the size of the register or memory location being operated on. There are 2-, 3-, and 4- (if prebyte is required) byte immediate instructions. The effective address is the address of the byte following the instruction.

## 4.5.2 Direct

In the direct addressing mode, the low-order byte of the operand address is contained in a single byte following the opcode, and the high-order byte of the address is assumed to be \$00. Addresses \$00–\$FF are thus accessed directly, using 2-byte instructions. Execution time is reduced by eliminating the additional memory access required for the high-order address byte. In most applications, this 256-byte area is reserved for frequently referenced data. In M68HC11 MCUs, the memory map can be configured for combinations of internal registers, RAM, or external memory to occupy these addresses.

### **Central Processor Unit (CPU)**

| Table 4-2. Instruction Set | (Sheet 7 of 7) |

|----------------------------|----------------|

|----------------------------|----------------|

| Macanio  | Oneration                      | Description                                              | Addressing |      | ssing Instruction |       |         | Condition Codes |   |   |   |   |   |   |   |   |

|----------|--------------------------------|----------------------------------------------------------|------------|------|-------------------|-------|---------|-----------------|---|---|---|---|---|---|---|---|

| Mnemonic | Operation                      | Description                                              |            | Mode | Op                | ocode | Operand | Cycles          | S | Х | Н | I | Ν | Z | V | С |

| TSTA     | Test A for Zero<br>or Minus    | A – 0                                                    | A          | INH  |                   | 4D    | _       | 2               |   | _ | _ | _ | Δ | Δ | 0 | 0 |

| TSTB     | Test B for Zero<br>or Minus    | B – 0                                                    | В          | INH  |                   | 5D    | —       | 2               |   | — | _ | _ | Δ | Δ | 0 | 0 |

| TSX      | Transfer Stack<br>Pointer to X | $SP + 1 \Rightarrow IX$                                  |            | INH  |                   | 30    | —       | 3               | _ | — | — | — | — | — | — | _ |

| TSY      | Transfer Stack<br>Pointer to Y | $SP + 1 \Rightarrow IY$                                  |            | INH  | 18                | 30    | _       | 4               |   | _ | _ | _ | — | _ | _ | _ |

| TXS      | Transfer X to<br>Stack Pointer | $IX - 1 \Rightarrow SP$                                  |            | INH  |                   | 35    | —       | 3               |   | — | _ | _ | — | — | _ | _ |

| TYS      | Transfer Y to<br>Stack Pointer | $IY - 1 \Rightarrow SP$                                  |            | INH  | 18                | 35    | —       | 4               | _ | — | — | — | — | — | — | _ |

| WAI      | Wait for<br>Interrupt          | Stack Regs & WAIT                                        |            | INH  |                   | 3E    | _       | **              |   | _ | _ | _ | — | _ | _ | _ |

| XGDX     | Exchange D<br>with X           | $IX \mathbin{\Rightarrow} D, D \mathbin{\Rightarrow} IX$ |            | INH  |                   | 8F    | —       | 3               |   | _ | _ | — | — | _ | _ | _ |

| XGDY     | Exchange D<br>with Y           | $IY \Rightarrow D,  D \Rightarrow IY$                    |            | INH  | 18                | 8F    | _       | 4               |   | _ | _ | _ | — | _ | _ | _ |

#### Cycle

\* Infinity or until reset occurs

\*\* 12 cycles are used beginning with the opcode fetch. A wait state is entered which remains in effect for an integer number of MPU E-clock cycles (n) until an interrupt is recognized. Finally, two additional cycles are used to fetch the appropriate interrupt vector (14 + n total).

#### Operands

- dd = 8-bit direct address (\$0000-\$00FF) (high byte assumed to be \$00)

- ff = 8-bit positive offset \$00 (0) to \$FF (255) (is added to index)

- hh = High-order byte of 16-bit extended address

- ii = One byte of immediate data

- jj = High-order byte of 16-bit immediate data

- kk = Low-order byte of 16-bit immediate data

- 11 = Low-order byte of 16-bit extended address

- mm = 8-bit mask (set bits to be affected)

- rr = Signed relative offset \$80 (-128) to \$7F (+127)

(offset relative to address following machine code offset byte))

#### Operators

- () Contents of register shown inside parentheses

- ⇐ Is transferred to

- 1 Is pulled from stack

- $\Downarrow$  Is pushed onto stack

- Boolean AND

- + Arithmetic addition symbol except where used as inclusive-OR symbol in Boolean formula

- Exclusive-OR

Exclusive-OR

- \* Multiply

- : Concatenation

- Arithmetic subtraction symbol or negation symbol (two's complement)

#### **Condition Codes**

- Bit not changed

- 0 Bit always cleared

- 1 Bit always set

- $\Delta \qquad \qquad \text{Bit cleared or set, depending on operation}$

- $\downarrow$  Bit can be cleared, cannot become set

Parallel Input/Output (I/O) Ports

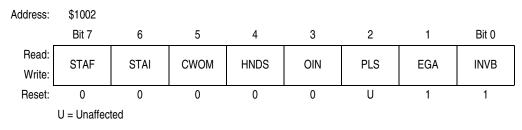

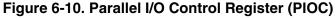

# 6.8 Parallel I/O Control Register

The parallel handshake functions are available only in the single-chip operating mode. PIOC is a read/write register except for bit 7, which is read only. Table 6-2 shows a summary of handshake operations.

|                                           | STAF<br>Clearing<br>Sequence                          | HNDS | OIN | PLS                                                  | EGA                                                                 | Port B                                                                                             | Port C                                                     |

|-------------------------------------------|-------------------------------------------------------|------|-----|------------------------------------------------------|---------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|------------------------------------------------------------|

| Simple<br>strobed<br>mode                 | Read<br>PIOC with<br>STAF = 1<br>then read<br>PORTCL  | 0    | х   | Х                                                    |                                                                     | Inputs latched into<br>PORTCL on any<br>active edge on<br>STRA                                     | STRB pulses<br>on writes<br>to PORTB                       |

| Full-input<br>hand-<br>shake<br>mode      | Read<br>PIOC with<br>STAF = 1<br>then read<br>PORTCL  | 1    | 0   | 0 = STRB<br>active level<br>1 = STRB<br>active pulse | 1<br>0                                                              | Inputs latched into<br>PORTCL on any<br>active edge on<br>STRA                                     | Normal output<br>port, unaffected<br>in handshake<br>modes |

| Full-<br>output<br>hand-<br>shake<br>mode | Read<br>PIOC with<br>STAF = 1<br>then write<br>PORTCL | 1    | 1   | 0 = STRB<br>active level<br>1 = STRB<br>active pulse | 0<br>Port C<br>Driven<br>STRA<br>Follow: Active Edge Follow<br>DDRC | Driven as outputs if<br>STRA at active<br>level; follows<br>DDRC<br>if STRA not at<br>active level | Normal output<br>port, unaffected<br>in handshake<br>modes |

| Table 6-2 | 2. Parallel | I/O Control |

|-----------|-------------|-------------|

|-----------|-------------|-------------|

## STAF — Strobe A Interrupt Status Flag

STAF is set when the selected edge occurs on strobe A. This bit can be cleared by a read of PIOC with STAF set followed by a read of PORTCL (simple strobed or full input handshake mode) or a write to PORTCL (output handshake mode).

- 0 = No edge on strobe A

- 1 = Selected edge on strobe A

### STAI — Strobe A Interrupt Enable Mask Bit

- 0 = STAF does not request interrupt

- 1 = STAF requests interrupt

# **10.5 DC Electrical Characteristics**

| Characteristics <sup>(1)</sup>                                                                                                                             | Symbol                            | Min                                                                   | Max                                            | Unit |

|------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|-----------------------------------------------------------------------|------------------------------------------------|------|

| Output voltage <sup>(2)</sup><br>$I_{Load} = \pm \pm 10.0 \mu A$<br>All outputs except XTAL<br>All outputs except XTAL, RESET, and MODA                    | V <sub>OL</sub> , V <sub>OH</sub> | <br>V <sub>DD</sub> -0.1                                              | 0.1                                            | V    |

| Output high voltage <sup>(2)</sup><br>$I_{Load} = -0.8 \text{ mA}, V_{DD} = 4.5 \text{ V}$<br>All outputs except XTAL, RESET, and MODA                     | V <sub>OH</sub>                   | V <sub>DD</sub> –0.8                                                  | _                                              | V    |

| Output low voltage<br>I <sub>Load</sub> = 1.6 mA<br>All outputs except XTAL                                                                                | V <sub>OL</sub>                   | _                                                                     | 0.4                                            | V    |

| Input high voltage<br>All inputs except RESET<br>RESET                                                                                                     | V <sub>IH</sub>                   | $\begin{array}{c} 0.7 \times V_{DD} \\ 0.8 \times V_{DD} \end{array}$ | V <sub>DD</sub> + 0.3<br>V <sub>DD</sub> + 0.3 | V    |

| Input low voltage, all inputs                                                                                                                              | V <sub>IL</sub>                   | V <sub>SS</sub> -0.3                                                  | $0.2 \times V_{DD}$                            | V    |

| I/O ports, 3-state leakage<br>V <sub>In</sub> = V <sub>IH</sub> or V <sub>IL</sub><br>PA7, PA3, PC[7:0], PD[5:0], AS/STRA,<br>MODA/LIR, RESET              | I <sub>OZ</sub>                   | _                                                                     | ±10                                            | μΑ   |

| Input leakage current <sup>(3)</sup><br>$V_{In} = V_{DD} \text{ or } V_{SS}$<br>PA[2:0], IRQ, XIRQ<br>MODB/V <sub>STBY</sub> (XIRQ on EPROM-based devices) | I <sub>In</sub>                   |                                                                       | ±1<br>±10                                      | μΑ   |

| RAM standby voltage, power down                                                                                                                            | V <sub>SB</sub>                   | 4.0                                                                   | V <sub>DD</sub>                                | V    |

| RAM standby current, power down                                                                                                                            | I <sub>SB</sub>                   | —                                                                     | 10                                             | μΑ   |

| Input capacitance<br>PA[2:0], PE[7:0], IRQ, XIRQ, EXTAL<br>PA7, PA3, PC[7:0], PD[5:0], AS/STRA, MODA/LIR, RESET                                            | C <sub>In</sub>                   |                                                                       | 8<br>12                                        | pF   |

| Output load capacitance<br>All outputs except PD[4:1]<br>PD[4:1]                                                                                           | CL                                |                                                                       | 90<br>100                                      | pF   |

V<sub>DD</sub> = 5.0 Vdc ± 10%, V<sub>SS</sub> = 0 Vdc, T<sub>A</sub> = T<sub>L</sub> to T<sub>H</sub>, unless otherwise noted

V<sub>OH</sub> specification for RESET and MODA is not applicable because they are open-drain pins. V<sub>OH</sub> specification not applicable to ports C and D in wired-OR mode.

Refer to 10.13 Analog-to-Digital Converter Characteristics and 10.14 MC68L11E9/E20 Analog-to-Digital Converter Characteristics for leakage current for port E.

MC68L11E9/E20 Supply Currents and Power Dissipation

Notes:

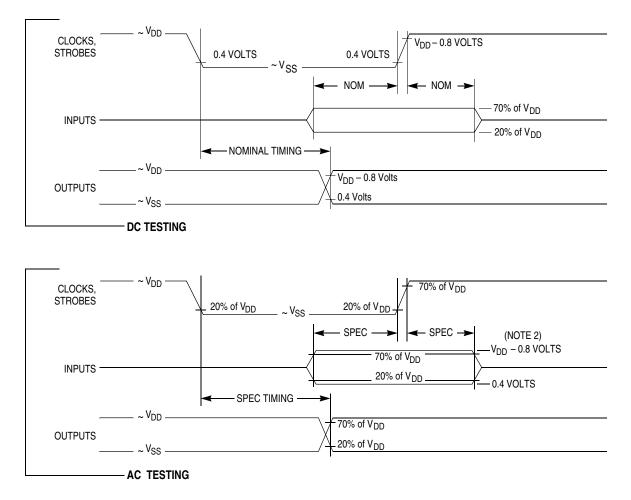

- 1. Full test loads are applied during all dc electrical tests and ac timing measurements.

- 2. During ac timing measurements, inputs are driven to 0.4 volts and  $V_{DD} 0.8$  volts while timing measurements are taken at 20% and 70% of  $V_{DD}$  points.

### Figure 10-1. Test Methods

# 10.14 MC68L11E9/E20 Analog-to-Digital Converter Characteristics

| Characteristic <sup>(1)</sup> | Parameter <sup>(2)</sup>                                                                                                                       | Min                  | Absolute   | Max                   | Unit                   |

|-------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|------------|-----------------------|------------------------|

| Resolution                    | Number of bits resolved by A/D converter                                                                                                       | _                    | 8          |                       | Bits                   |

| Non-linearity                 | Maximum deviation from the ideal A/D transfer characteristics                                                                                  | _                    | —          | ±1                    | LSB                    |

| Zero error                    | Difference between the output of an ideal and an actual for 0 input voltage                                                                    | _                    | —          | ±1                    | LSB                    |

| Full scale error              | Difference between the output of an ideal and an actual A/D for full-scale input voltage                                                       | _                    | —          | ±1                    | LSB                    |

| Total unadjusted<br>error     | Maximum sum of non-linearity, zero error, and full-scale error                                                                                 | _                    | —          | ±1/2                  | LSB                    |

| Quantization error            | Uncertainty because of converter resolution                                                                                                    | —                    | —          | ±1/2                  | LSB                    |

| Absolute accuracy             | Difference between the actual input voltage and<br>the full-scale weighted equivalent of the binary<br>output code, all error sources included | _                    | _          | ±2                    | LSB                    |

| Conversion range              | Analog input voltage range                                                                                                                     | V <sub>RL</sub>      | —          | V <sub>RH</sub>       | V                      |

| V <sub>RH</sub>               | Maximum analog reference voltage                                                                                                               | V <sub>RL</sub>      | —          | V <sub>DD</sub> + 0.1 | V                      |

| V <sub>RL</sub>               | Minimum analog reference voltage                                                                                                               | V <sub>SS</sub> –0.1 | —          | V <sub>RH</sub>       | V                      |

| $\Delta V_R$                  | Minimum difference between $V_{RH}$ and $V_{RL}$                                                                                               | 3.0                  | —          |                       | V                      |

| Conversion time               | Total time to perform a single<br>analog-to-digital conversion:<br>E clock<br>Internal RC oscillator                                           | _                    | 32<br>—    |                       | t <sub>CYC</sub><br>μs |

| Monotonicity                  | Conversion result never decreases with an<br>increase in input voltage and has no missing<br>codes                                             | _                    | Guaranteed |                       | _                      |

| Zero input reading            | Conversion result when $V_{In} = V_{RL}$                                                                                                       | 00                   | —          |                       | Hex                    |

| Full scale reading            | Conversion result when $V_{In} = V_{RH}$                                                                                                       | —                    | —          | FF                    | Hex                    |

| Sample acquisition time       | Analog input acquisition sampling time:<br>E clock<br>Internal RC oscillator                                                                   |                      | 12         |                       | t <sub>CYC</sub><br>μs |

| Sample/hold capacitance       | Input capacitance during sample<br>PE[7:0]                                                                                                     | _                    | 20 typical | —                     | pF                     |

| Input leakage                 | Input leakage on A/D pins<br>PE[7:0]<br>V <sub>RL</sub> , V <sub>RH</sub>                                                                      |                      |            | 400<br>1.0            | nA<br>μA               |

1.  $V_{DD}$  = 3.0 Vdc to 5.5 Vdc,  $V_{SS}$  = 0 Vdc,  $T_A$  =  $T_L$  to  $T_H$ , 750 kHz  $\leq$  E  $\leq$  2.0 MHz, unless otherwise noted 2. Source impedances greater than 10 k $\Omega$  affect accuracy adversely because of input leakage.

### **Custom ROM Device Ordering Information**

| Description                      | CONFIG              | Temperature     | Frequency | MC Order Number  |

|----------------------------------|---------------------|-----------------|-----------|------------------|

| 52-pin windowed ceramic leade    | ed chip carrier (   | CLCC)           |           |                  |

| EPROM                            | <b>*</b> 0 <b>F</b> | -40°C to +85°C  | 2 MHz     | MC68HC711E9CFS2  |

|                                  |                     |                 | 3 MHz     | MC68HC711E9CFS3  |

|                                  | \$0F                | -40°C to +105°C | 2 MHz     | MC68HC711E9VFS2  |

|                                  |                     | -40°C to +125°C | 2 MHz     | MC68HC711E9VFS2  |

| 20 Kbytes EPROM                  |                     | 0°C o +70°°C    | 3 MHz     | MC68HC711E20FS3  |

|                                  |                     | -40°C to +85°C  | 2 MHz     | MC68HC711E20CFS2 |

|                                  | \$0F                |                 | 3 MHz     | MC68HC711E20CFS3 |

|                                  |                     | -40°C to +105°C | 2 MHz     | MC68HC711E20VFS2 |

|                                  |                     | -40°C to +125°C | 2 MHz     | MC68HC711E20MFS2 |

| 48-pin dual in-line package (DIF | P) — MC68HC81       | 11E2 only       |           |                  |

| No ROM, 2 Kbytes EEPROM          | \$FF                | 0°C to +70°°C   | 2 MHz     | MC68HC811E2P2    |

|                                  |                     | -40°C to +85°C  | 2 MHz     | MC68HC811E2CP2   |

|                                  |                     | -40°C to +105°C | 2 MHz     | MC68HC811E2VP2   |

|                                  |                     | -40°C to +125°C | 2 MHz     | MC68HC811E2MP2   |

| 56-pin dual in-line package with | 0.70-inch lead      | spacing (SDIP)  |           |                  |

| BUFFALO ROM                      | \$0F                | -40°C to +85°C  | 2 MHz     | MC68HC11E9BCB2   |

| BUFFALO ROM                      |                     |                 | 3 MHz     | MC68HC11E9BCB3   |

| BUFFALO ROM       | \$0F -40°C to +85°C | 2 1011 12       | MC00HCTTE9DCD2 |                |

|-------------------|---------------------|-----------------|----------------|----------------|

|                   |                     | -40 0 10 403 0  | 3 MHz          | MC68HC11E9BCB3 |

| No ROM            | \$0D                | –40°C to +85°C  | 2 MHz          | MC68HC11E1CB2  |

|                   |                     |                 | 3 MHz          | MC68HC11E1CB3  |

|                   |                     | –40°C to +105°C | 2 MHz          | MC68HC11E1VB2  |

|                   |                     | –40°C to +125°C | 2 MHz          | MC68HC11E1MB2  |

| No ROM, no EEPROM | \$0C                | –40°C to +85°C  | 2 MHz          | MC68HC11E0CB2  |

|                   |                     |                 | 3 MHz          | MC68HC11E0CB3  |

|                   |                     | –40°C to +105°C | 2 MHz          | MC68HC11E0VB2  |

|                   |                     | –40°C to +125°C | 2 MHz          | MC68HC11E0MB2  |

# **11.3 Custom ROM Device Ordering Information**

| Description                               | Temperature Frequency |       | MC Order Number |  |  |  |

|-------------------------------------------|-----------------------|-------|-----------------|--|--|--|

| 52-pin plastic leaded chip carrier (PLCC) |                       |       |                 |  |  |  |

| Custom ROM                                | 0°C to +70°°C 3 MHz   |       | MC68HC11E9FN3   |  |  |  |

|                                           | -40°C to +85°C        | 2 MHz | MC68HC11E9CFN2  |  |  |  |

|                                           | -40 C 10 +65 C        | 3 MHz | MC68HC11E9CFN3  |  |  |  |

|                                           | –40°C to +105°C       | 2 MHz | MC68HC11E9VFN2  |  |  |  |

|                                           | –40°C to +125°C       | 2 MHz | MC68HC11E9MFN2  |  |  |  |

### **Boot ROM Firmware**

The alternate vector locations are achieved by simply driving address bit A14 low during all vector fetches if SMOD = 1. For special test mode, the alternate vector locations assure that the reset vector can be fetched from external memory space so the test system can control MCU operation. In special bootstrap mode, the small boot ROM is enabled in the memory map by RBOOT = 1 so the reset vector will be fetched from this ROM and the bootloader firmware will control MCU operation.

RBOOT is reset to 1 in bootstrap mode to enable the small boot ROM. In the other three modes, RBOOT is reset to 0 to keep the boot ROM out of the memory map. While in special test mode, SMOD = 1, which allows the RBOOT control bit to be written to 1 by software to enable the boot ROM for testing purposes.

## **Boot ROM Firmware**

The main program in the boot ROM is the bootloader, which is automatically executed as a result of resetting the MCU in bootstrap mode. Some newer versions of the M68HC11 Family have additional utility programs that can be called from a downloaded program. One utility is available to program EPROM or OTP versions of the M68HC11. A second utility allows the contents of memory locations to be uploaded to a host computer. In the MC68HC711K4 boot ROM, a section of code is used by Freescale for stress testing the on-chip EEPROM. These test and utility programs are similar to self-test ROM programs in other MCUs except that the boot ROM does not use valuable space in the normal memory map.

Bootstrap firmware is also involved in an optional EEPROM security function on some versions of the M68HC11. This EEPROM security feature prevents a software pirate from seeing what is in the on-chip EEPROM. The secured state is invoked by programming the no security (NOSEC) EEPROM bit in the CONFIG register. Once this NOSEC bit is programmed to 0, the MCU will ignore the mode A pin and always come out of reset in normal single-chip mode or special bootstrap mode, depending on the state of the mode B pin. Normal single-chip mode is the usual way a secured part would be used. Special bootstrap mode is used to disengage the security function (only after the contents of EEPROM and RAM have been erased). Refer to the *M68HC11 Reference Manual*, Freescale document order number M68HC11RM/AD, for additional information on the security mode and complete listings of the boot ROMs that support the EEPROM security functions.

## Automatic Selection of Baud Rate

The bootloader program in the MC68HC711E9 accommodates either of two baud rates.

- The higher of these baud rates (7812 baud at a 2-MHz E-clock rate) is used in systems that operate from a binary frequency crystal such as 2<sup>23</sup> Hz (8.389 MHz). At this crystal frequency, the baud rate is 8192 baud, which was used extensively in automotive applications.

- The second baud rate available to the M68HC11 bootloader is 1200 baud at a 2-MHz E-clock rate. Some of the newest versions of the M68HC11, including the MC68HC11F1 and MC68HC117K4, accommodate other baud rates using the same differentiation technique explained here. Refer to the reference numbers in square brackets in Figure 2 during the following explanation.

## NOTE

Software can change some aspects of the memory map after reset.

M68HC11 Bootstrap Mode, Rev. 1.1

```

Listing 3. MC68HC711E9 Bootloader ROM

```

52 D000 EPRMSTR EQU \$D000 Start of EPROM 53 FFFF EPRMEND EQU \$FFFF End of EPROM 54 \* 55 0000 RAMSTR EQU \$0000 56 01FF EQU \$01FF RAMEND 57 58 \* DELAY CONSTANTS 59 \* 60 0DB0 DELAYS EQU 3504 Delay at slow baud 61 021B DELAYF EOU 539 Delay at fast baud 62 2 ms programming delay 63 1068 PROGDEL EQU 4200 64 At 2.1 MHz 65 66 67 BF00 ORG \$BF00 68 69 \* Next two instructions provide a predictable place 70 \* to call PROGRAM and UPLOAD even if the routines 71 72 \* change size in future versions. 73 74 BF00 7EBF13 EPROM programming utility PROGRAM JMP PRGROUT 75 BF03 UPLOAD EQU Upload utility \* 76 77 \* UPLOAD - Utility subroutine to send data from 78 79 \* inside the MCU to the host via the SCI interface. \* Prior to calling UPLOAD set baud rate, turn on SCI 80 81 \* and set Y=first address to upload. 82 \* Bootloader leaves baud set, SCI enabled, and 83 \* Y pointing at EPROM start (\$D000) so these default 84 \* values do not have to be changed typically. 85 \* Consecutive locations are sent via SCI in an \* infinite loop. Reset stops the upload process. 86 87 Point to internal registers 88 BF03 CE1000 #\$1000 LDX 89 BF06 18A600 UPLOOP LDAA Ο,Υ Read byte Wait for TDRE 90 BF09 1F2E80FC BRCLR SCSR,X \$80 \* 91 BF0D A72F Send it STAA SCDAT,X 92 BF0F 1808 INY 93 BF11 20F3 BRA UPLOOP Next... 94 95 96 \* PROGRAM - Utility subroutine to program EPROM. \* Prior to calling PROGRAM set baud rate, turn on SCI 97 98 \* set X=2ms prog delay constant, and set Y=first 99 \* address to program. SP must point to RAM. \* Bootloader leaves baud set, SCI enabled, X=4200 100 \* and Y pointing at EPROM start (\$D000) so these 101 \* default values don't have to be changed typically. 102 103 \* Delay constant in X should be equivalent to 2 ms at 2.1 MHz X=4200; at 1 MHz X=2000. 104 \* \* An external voltage source is required for EPROM 105 106 \* programming.

M68HC11 Bootstrap Mode, Rev. 1.1

### Step 6

Erase the CONFIG to allow programming of NOSEC bit (bit 3). It is also recommended to program the EEPROM at this point before programming the CONFIG register. Refer to the engineering bulletin *Programming MC68HC811E2 Devices with PCbug11 and the M68HC711E9PGMR*, Freescale document number EB184.

At the PCbug11command prompt, type: EEPROM ERASE BULK 103F

### Step 7

You are now ready to enable the security feature on the MCHC811E2.

At the PCbug11 command prompt, type: MS 103F 05

The value \$05 assumes the EEPROM is to be mapped from \$0800 to \$0FFF.

### Step 8

After the programming operation is complete, verifying the CONFIG on the MCHC811E2 is not possible because in bootstrap mode the default value is always forced.

### Step 9

The part is now in secure mode and whatever code you loaded into EEPROM will be erased if you tried to bring the microcontroller up in either expanded mode or bootstrap mode. The microcontroller will work properly in the secure mode only in single chip mode.

### NOTE

If the part is placed in bootstrap mode or expanded mode, the code in EEPROM and RAM will be erased the microcontroller can be reused.

Enabling the Security Feature on M68HC811E2 Devices with PCbug11 on the M68HC711E9PGMR, Rev. 0.1

#### How to Reach Us:

Home Page: www.freescale.com

E-mail: support@freescale.com

#### **USA/Europe or Locations Not Listed:**

Freescale Semiconductor Technical Information Center, CH370 1300 N. Alma School Road Chandler, Arizona 85224 +1-800-521-6274 or +1-480-768-2130 support@freescale.com

#### Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) support@freescale.com

#### Japan:

Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku, Tokyo 153-0064 Japan 0120 191014 or +81 3 5437 9125 support.japan@freescale.com

#### Asia/Pacific:

Freescale Semiconductor Hong Kong Ltd. Technical Information Center 2 Dai King Street Tai Po Industrial Estate Tai Po, N.T., Hong Kong +800 2666 8080 support.asia@freescale.com

#### For Literature Requests Only:

Freescale Semiconductor Literature Distribution Center P.O. Box 5405 Denver, Colorado 80217 1-800-441-2447 or 303-675-2140 Fax: 303-675-2150 LDCForFreescaleSemiconductor@hibbertgroup.com Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals", must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

Freescale<sup>™</sup> and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. © Freescale Semiconductor, Inc. 2005. All rights reserved.