Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                      |

|----------------------------|-------------------------------------------------------------|

| Core Processor             | HC11                                                        |

| Core Size                  | 8-Bit                                                       |

| Speed                      | 3MHz                                                        |

| Connectivity               | SCI, SPI                                                    |

| Peripherals                | POR, WDT                                                    |

| Number of I/O              | 38                                                          |

| Program Memory Size        | -                                                           |

| Program Memory Type        | ROMIess                                                     |

| EEPROM Size                | -                                                           |

| RAM Size                   | 512 x 8                                                     |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                 |

| Data Converters            | A/D 8x8b                                                    |

| Oscillator Type            | Internal                                                    |

| Operating Temperature      | 0°C ~ 70°C (TA)                                             |

| Mounting Type              | Surface Mount                                               |

| Package / Case             | 52-LCC (J-Lead)                                             |

| Supplier Device Package    | 52-PLCC (19.1x19.1)                                         |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mc68hcp11e0fne |

|                            |                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **Operating Modes and On-Chip Memory**

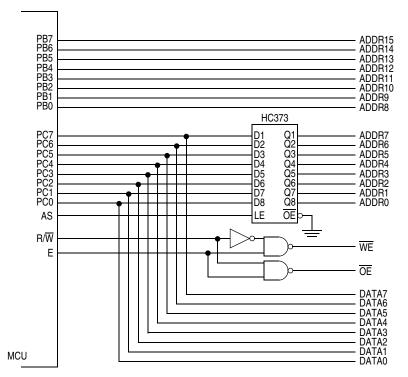

The address, R/W, and AS signals are active and valid for all bus cycles, including accesses to internal memory locations. The E clock is used to enable external devices to drive data onto the internal data bus during the second half of a read bus cycle (E clock high). R/W controls the direction of data transfers. R/W drives low when data is being written to the internal data bus. R/W will remain low during consecutive data bus write cycles, such as when a double-byte store occurs.

Refer to Figure 2-1.

NOTE

The write enable signal for an external memory is the NAND of the E clock and the inverted R/W signal.

Figure 2-1. Address/Data Demultiplexing

# 2.2.3 Test Mode

Test mode, a variation of the expanded mode, is primarily used during Freescale's internal production testing; however, it is accessible for programming the configuration (CONFIG) register, programming calibration data into electrically erasable, programmable read-only memory (EEPROM), and supporting emulation and debugging during development.

# 2.2.4 Bootstrap Mode

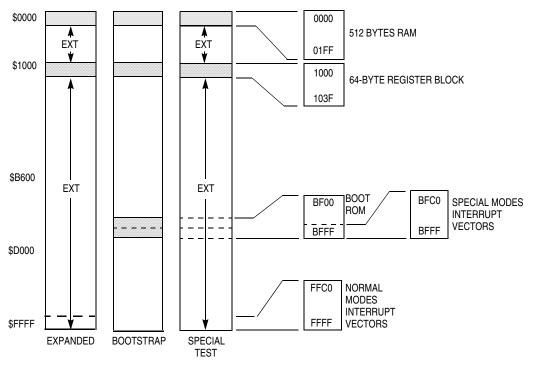

When the MCU is reset in special bootstrap mode, a small on-chip read-only memory (ROM) is enabled at address \$BF00-\$BFFF. The ROM contains a bootloader program and a special set of interrupt and reset vectors. The MCU fetches the reset vector, then executes the bootloader.

Bootstrap mode is a special variation of the single-chip mode. Bootstrap mode allows special-purpose programs to be entered into internal random-access memory (RAM). When bootstrap mode is selected at reset, a small bootstrap ROM becomes present in the memory map. Reset and interrupt vectors are

located in this ROM at \$BFC0-\$BFFF. The bootstrap ROM contains a small program which initializes the serial communications interface (SCI) and allows the user to download a program into on-chip RAM. The size of the downloaded program can be as large as the size of the on-chip RAM. After a 4-character delay, or after receiving the character for the highest address in RAM, control passes to the loaded program at \$0000. Refer to Figure 2-2, Figure 2-3, Figure 2-4, Figure 2-5, and Figure 2-6.

Use of an external pullup resistor is required when using the SCI transmitter pin because port D pins are configured for wired-OR operation by the bootloader. In bootstrap mode, the interrupt vectors are directed to RAM. This allows the use of interrupts through a jump table. Refer to the application note AN1060 entitled *M68HC11 Bootstrap Mode, that is included in this data book*.

# 2.3 Memory Map

The operating mode determines memory mapping and whether external addresses can be accessed. Refer to Figure 2-2, Figure 2-3, Figure 2-4, Figure 2-5, and Figure 2-6, which illustrate the memory maps for each of the three families comprising the M68HC11 E series of MCUs.

Memory locations for on-chip resources are the same for both expanded and single-chip modes. Control bits in the configuration (CONFIG) register allow EPROM and EEPROM (if present) to be disabled from the memory map. The RAM is mapped to \$0000 after reset. It can be placed at any 4-Kbyte boundary (\$x000) by writing an appropriate value to the RAM and I/O map register (INIT). The 64-byte register block is mapped to \$1000 after reset and also can be placed at any 4-Kbyte boundary (\$x000) by writing an appropriate value to the RAM and registers are mapped to the same boundary, the first 64 bytes of RAM will be inaccessible.

Refer to Figure 2-7, which details the MCU register and control bit assignments. Reset states shown are for single-chip mode only.

Figure 2-2. Memory Map for MC68HC11E0

M68HC11E Family Data Sheet, Rev. 5.1

#### **Operating Modes and On-Chip Memory**

| Addr.   | Register Name                                                                |                 | Bit 7       | 6                         | 5                   | 4                  | 3               | 2         | 1                  | Bit 0              |  |

|---------|------------------------------------------------------------------------------|-----------------|-------------|---------------------------|---------------------|--------------------|-----------------|-----------|--------------------|--------------------|--|

|         | Analog-to-Digital Results                                                    | Read:           | Bit 7       | Bit 6                     | Bit 5               | Bit 4              | Bit 3           | Bit 2     | Bit 1              | Bit 0              |  |

| \$1031  | Register 1 (ADR1)                                                            | Write:          |             |                           |                     |                    |                 |           |                    |                    |  |

|         | See page 64.                                                                 | Reset:          |             | Indeterminate after reset |                     |                    |                 |           |                    |                    |  |

|         | Analog-to-Digital Results                                                    | Read:           | Bit 7       | Bit 6                     | Bit 5               | Bit 4              | Bit 3           | Bit 2     | Bit 1              | Bit 0              |  |

| \$1032  | Register 2 (ADR2)<br>See page 64.                                            | Write:          |             |                           |                     |                    |                 |           |                    |                    |  |

|         |                                                                              | Reset:          |             |                           | r                   | 1                  | ate after reset |           |                    |                    |  |

|         | Analog-to-Digital Results                                                    | Read:           | Bit 7       | Bit 6                     | Bit 5               | Bit 4              | Bit 3           | Bit 2     | Bit 1              | Bit 0              |  |

| \$1033  | Register 3 (ADR3)                                                            | Write:          |             |                           |                     |                    |                 |           |                    |                    |  |

|         | See page 64.                                                                 | Reset:          |             |                           |                     |                    | ate after reset |           |                    |                    |  |

|         | Analog-to-Digital Results                                                    | Read:           | Bit 7       | Bit 6                     | Bit 5               | Bit 4              | Bit 3           | Bit 2     | Bit 1              | Bit 0              |  |

| \$1034  | Register 4 (ADR4)<br>See page 64.                                            | Write:          |             |                           |                     |                    |                 |           |                    |                    |  |

|         | 0000 page 04.                                                                | Reset:          |             |                           |                     | Indetermina        | ate after reset |           | [                  |                    |  |

|         | Block Protect Register                                                       | Read:           |             |                           |                     | PTCON              | BPRT3           | BPRT2     | BPRT1              | BPRT0              |  |

| \$1035  | (BPROT)<br>See page 52.                                                      | Write:          |             |                           |                     |                    |                 |           |                    |                    |  |

|         | 000 page 02.                                                                 | Reset:          | 0           | 0                         | 0                   | 1                  | 1               | 1         | 1                  | 1                  |  |

| \$1036  | EPROM Programming Control<br>Register (EPROG) <sup>(1)</sup><br>See page 53. | Read:<br>Write: | MBE         |                           | ELAT                | EXCOL              | EXROW           | T1        | T0                 | PGM                |  |

|         |                                                                              | Reset:          | 0           | 0                         | 0                   | 0                  | 0               | 0         | 0                  | 0                  |  |

| \$1037  | Reserved                                                                     | 1               | R           | R                         | R                   | R                  | R               | R         | R                  | R                  |  |

| 1. MC68 | HC711E20 only                                                                | ·               |             |                           |                     |                    |                 |           |                    |                    |  |

| \$1038  | Reserved                                                                     | 1               | R           | R                         | R                   | R                  | R               | R         | R                  | R                  |  |

|         |                                                                              | ļ               |             |                           |                     |                    |                 |           |                    |                    |  |

| \$1039  | System Configuration Options<br>Register (OPTION)<br>See page 46.            | Read:<br>Write: | ADPU        | CSEL                      | IRQE <sup>(1)</sup> | DLY <sup>(1)</sup> | CME             |           | CR1 <sup>(1)</sup> | CR0 <sup>(1)</sup> |  |

|         |                                                                              | Reset:          | 0           | 0                         | 0                   | 1                  | 0               | 0         | 0                  | 0                  |  |

|         | Arm/Reset COP Timer Circuitry                                                | Read:           |             |                           |                     |                    | -               |           | -                  |                    |  |

| \$103A  | Arm/Reset COP Timer Circuitry<br>Register (COPRST)<br>See page 81.           | Write:          | Bit 7       | Bit 6                     | Bit 5               | Bit 4              | Bit 3           | Bit 2     | Bit 1              | Bit 0              |  |

|         |                                                                              | Reset:          | 0           | 0                         | 0                   | 0                  | 0               | 0         | 0                  | 0                  |  |

| \$103B  | EPROM and EEPROM Program-<br>ming Control Register (PPROG)                   | Read:<br>Write: | ODD         | EVEN                      | ELAT <sup>(2)</sup> | BYTE               | ROW             | ERASE     | EELAT              | EPGM               |  |

|         | See page 49.                                                                 | Reset:          | 0           | 0                         | 0                   | 0                  | 0               | 0         | 0                  | 0                  |  |

| \$103C  | Highest Priority I Bit Interrupt and<br>Miscellaneous Register (HPRIO)       | Read:<br>Write: | RBOOT       | SMOD                      | MDA                 | IRV(NE)            | PSEL3           | PSEL2     | PSEL1              | PSEL0              |  |

|         | See page 41.                                                                 | Reset:          | 0           | 0                         | 0                   | 0                  | 0               | 1         | 1                  | 0                  |  |

| \$103D  | RAM and I/O Mapping Register<br>(INIT)                                       | Read:<br>Write: | RAM3        | RAM2                      | RAM1                | RAM0               | REG3            | REG2      | REG1               | REG0               |  |

|         | See page 45.                                                                 | Reset:          | 0           | 0                         | 0                   | 0                  | 0               | 0         | 0                  | 1                  |  |

|         |                                                                              | [               |             | = Unimplen                | nented              | R                  | = Reserved      | U = Unaff | ected              |                    |  |

|         |                                                                              | ,               | I = Indeter | minate after              | reset               | L                  | <b>-</b>        |           |                    |                    |  |

Figure 2-7. Register and Control Bit Assignments (Sheet 5 of 6)

M68HC11E Family Data Sheet, Rev. 5.1

**Central Processor Unit (CPU)**

# 4.4 Opcodes and Operands

The M68HC11 Family of microcontrollers uses 8-bit opcodes. Each opcode identifies a particular instruction and associated addressing mode to the CPU. Several opcodes are required to provide each instruction with a range of addressing capabilities. Only 256 opcodes would be available if the range of values were restricted to the number able to be expressed in 8-bit binary numbers.

A 4-page opcode map has been implemented to expand the number of instructions. An additional byte, called a prebyte, directs the processor from page 0 of the opcode map to one of the other three pages. As its name implies, the additional byte precedes the opcode.

A complete instruction consists of a prebyte, if any, an opcode, and zero, one, two, or three operands. The operands contain information the CPU needs for executing the instruction. Complete instructions can be from one to five bytes long.

# 4.5 Addressing Modes

Six addressing modes can be used to access memory:

- Immediate

- Direct

- Extended

- Indexed

- Inherent

- Relative

These modes are detailed in the following paragraphs. All modes except inherent mode use an effective address. The effective address is the memory address from which the argument is fetched or stored or the address from which execution is to proceed. The effective address can be specified within an instruction, or it can be calculated.

# 4.5.1 Immediate

In the immediate addressing mode, an argument is contained in the byte(s) immediately following the opcode. The number of bytes following the opcode matches the size of the register or memory location being operated on. There are 2-, 3-, and 4- (if prebyte is required) byte immediate instructions. The effective address is the address of the byte following the instruction.

# 4.5.2 Direct

In the direct addressing mode, the low-order byte of the operand address is contained in a single byte following the opcode, and the high-order byte of the address is assumed to be \$00. Addresses \$00–\$FF are thus accessed directly, using 2-byte instructions. Execution time is reduced by eliminating the additional memory access required for the high-order address byte. In most applications, this 256-byte area is reserved for frequently referenced data. In M68HC11 MCUs, the memory map can be configured for combinations of internal registers, RAM, or external memory to occupy these addresses.

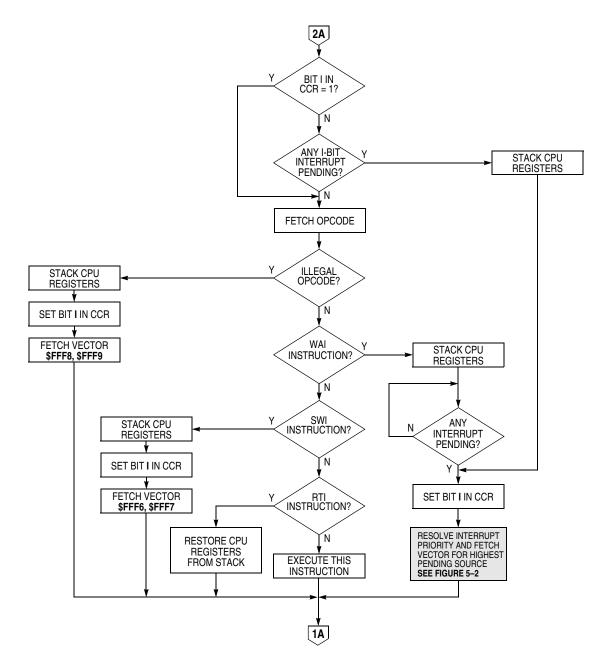

#### Resets and Interrupts

## 5.3.2 Memory Map

After reset, the INIT register is initialized to \$01, mapping the RAM at \$00 and the control registers at \$1000.

For the MC68HC811E2, the CONFIG register resets to \$FF. EEPROM mapping bits (EE[3:0]) place the EEPROM at \$F800. Refer to the memory map diagram for MC68HC811E2 in Chapter 2 Operating Modes and On-Chip Memory.

## 5.3.3 Timer

During reset, the timer system is initialized to a count of \$0000. The prescaler bits are cleared, and all output compare registers are initialized to \$FFFF. All input capture registers are indeterminate after reset. The output compare 1 mask (OC1M) register is cleared so that successful OC1 compares do not affect any I/O pins. The other four output compares are configured so that they do not affect any I/O pins on successful compares. All input capture edge-detector circuits are configured for capture disabled operation. The timer overflow interrupt flag and all eight timer function interrupt flags are cleared. All nine timer interrupts are disabled because their mask bits have been cleared.

The I4/O5 bit in the PACTL register is cleared to configure the I4/O5 function as OC5; however, the OM5:OL5 control bits in the TCTL1 register are clear so OC5 does not control the PA3 pin.

# 5.3.4 Real-Time Interrupt (RTI)

The real-time interrupt flag (RTIF) is cleared and automatic hardware interrupts are masked. The rate control bits are cleared after reset and can be initialized by software before the real-time interrupt (RTI) system is used.

## 5.3.5 Pulse Accumulator

The pulse accumulator system is disabled at reset so that the pulse accumulator input (PAI) pin defaults to being a general-purpose input pin.

# 5.3.6 Computer Operating Properly (COP)

The COP watchdog system is enabled if the NOCOP control bit in the CONFIG register is cleared and disabled if NOCOP is set. The COP rate is set for the shortest duration timeout.

## 5.3.7 Serial Communications Interface (SCI)

The reset condition of the SCI system is independent of the operating mode. At reset, the SCI baud rate control register (BAUD) is initialized to \$04. All transmit and receive interrupts are masked and both the transmitter and receiver are disabled so the port pins default to being general-purpose I/O lines. The SCI frame format is initialized to an 8-bit character size. The send break and receiver wakeup functions are disabled. The TDRE and TC status bits in the SCI status register (SCSR) are both 1s, indicating that there is no transmit data in either the transmit data register or the transmit serial shift register. The RDRF, IDLE, OR, NF, FE, PF, and RAF receive-related status bits in the SCI control register 2 (SCCR2) are cleared.

## 5.3.8 Serial Peripheral Interface (SPI)

The SPI system is disabled by reset. The port pins associated with this function default to being general-purpose I/O lines.

# 5.3.9 Analog-to-Digital (A/D) Converter

The analog-to-digital (A/D) converter configuration is indeterminate after reset. The ADPU bit is cleared by reset, which disables the A/D system. The conversion complete flag is indeterminate.

# 5.3.10 System

The EEPROM programming controls are disabled, so the memory system is configured for normal read operation. PSEL[3:0] are initialized with the value %0110, causing the external IRQ pin to have the highest I-bit interrupt priority. The IRQ pin is configured for level-sensitive operation (for wired-OR systems). The RBOOT, SMOD, and MDA bits in the HPRIO register reflect the status of the MODB and MODA inputs at the rising edge of reset. MODA and MODB inputs select one of the four operating modes. After reset, writing SMOD and MDA in special modes causes the MCU to change operating modes. Refer to the description of HPRIO register in Chapter 2 Operating Modes and On-Chip Memory for a detailed description of SMOD and MDA. The DLY control bit is set to specify that an oscillator startup delay is imposed upon recovery from stop mode. The clock monitor system is disabled because CME is cleared.

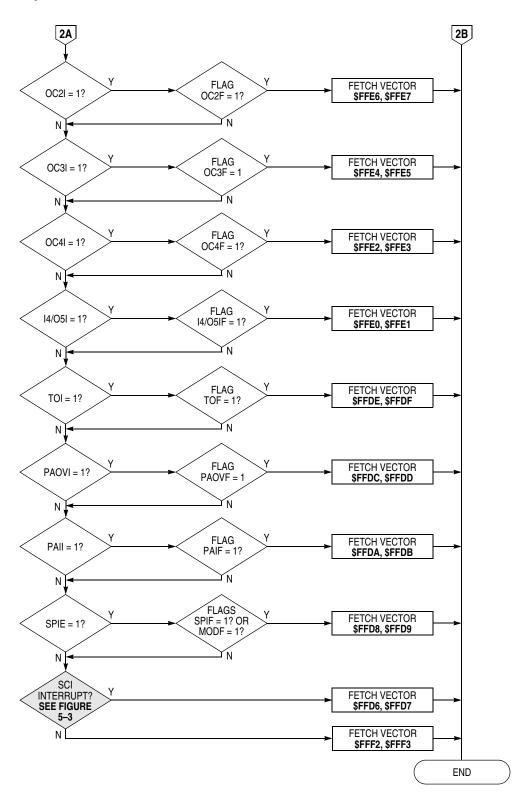

# 5.4 Reset and Interrupt Priority

Resets and interrupts have a hardware priority that determines which reset or interrupt is serviced first when simultaneous requests occur. Any maskable interrupt can be given priority over other maskable interrupts.

The first six interrupt sources are not maskable. The priority arrangement for these sources is:

- 1. POR or RESET pin

- 2. Clock monitor reset

- 3. COP watchdog reset

- 4. XIRQ interrupt

- 5. Illegal opcode interrupt

- 6. Software interrupt (SWI)

The maskable interrupt sources have this priority arrangement:

- 1. IRQ

- 2. Real-time interrupt

- 3. Timer input capture 1

- 4. Timer input capture 2

- 5. Timer input capture 3

- 6. Timer output compare 1

- 7. Timer output compare 2

- 8. Timer output compare 3

- 9. Timer output compare 4

- 10. Timer input capture 4/output compare 5

- 11. Timer overflow

- 12. Pulse accumulator overflow

- 13. Pulse accumulator input edge

- 14. SPI transfer complete

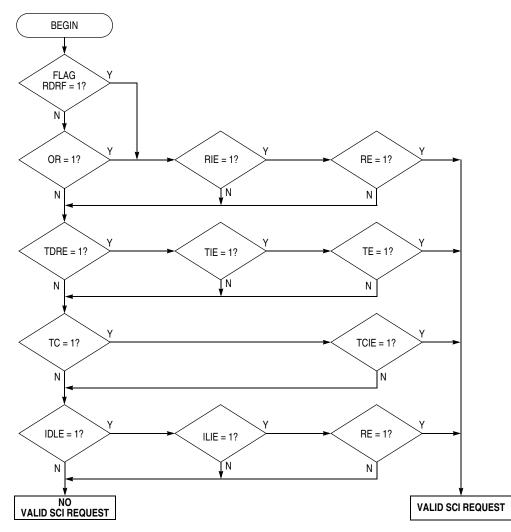

- 15. SCI system (refer to Figure 5-7)

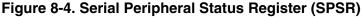

end of the interrupt service routine, the return-from-interrupt instruction is executed and the saved registers are pulled from the stack in reverse order so that normal program execution can resume. Refer to Chapter 4 Central Processor Unit (CPU).

| Memory Location | CPU Registers |

|-----------------|---------------|

| SP              | PCL           |

| SP-1            | PCH           |

| SP–2            | IYL           |

| SP–3            | IYH           |

| SP-4            | IXL           |

| SP–5            | IXH           |

| SP–6            | ACCA          |

| SP-7            | ACCB          |

| SP–8            | CCR           |

| Table 5-5. | Stacking | Order on | Entry to | Interrupts |

|------------|----------|----------|----------|------------|

|            | otuoning |          |          | michapio   |

# 5.5.2 Non-Maskable Interrupt Request (XIRQ)

Non-maskable interrupts are useful because they can always interrupt CPU operations. The most common use for such an interrupt is for serious system problems, such as program runaway or power failure. The XIRQ input is an updated version of the NMI (non-maskable interrupt) input of earlier MCUs.

Upon reset, both the X bit and I bit of the CCR are set to inhibit all maskable interrupts and  $\overline{XIRQ}$ . After minimum system initialization, software can clear the X bit by a TAP instruction, enabling  $\overline{XIRQ}$  interrupts. Thereafter, software cannot set the X bit. Thus, an  $\overline{XIRQ}$  interrupt is a non-maskable interrupt. Because the operation of the I-bit-related interrupt structure has no effect on the X bit, the internal  $\overline{XIRQ}$  pin remains unmasked. In the interrupt priority logic, the  $\overline{XIRQ}$  interrupt has a higher priority than any source that is maskable by the I bit. All I-bit-related interrupts operate normally with their own priority relationship.

When an I-bit-related interrupt occurs, the I bit is automatically set by hardware after stacking the CCR byte. The X bit is not affected. When an X-bit-related interrupt occurs, both the X and I bits are automatically set by hardware after stacking the CCR. A return-from-interrupt instruction restores the X and I bits to their pre-interrupt request state.

# 5.5.3 Illegal Opcode Trap

Because not all possible opcodes or opcode sequences are defined, the MCU includes an illegal opcode detection circuit, which generates an interrupt request. When an illegal opcode is detected and the interrupt is recognized, the current value of the program counter is stacked. After interrupt service is complete, reinitialize the stack pointer so repeated execution of illegal opcodes does not cause stack underflow. Left uninitialized, the illegal opcode vector can point to a memory location that contains an illegal opcode. This condition causes an infinite loop that causes stack underflow. The stack grows until the system crashes.

The illegal opcode trap mechanism works for all unimplemented opcodes on all four opcode map pages. The address stacked as the return address for the illegal opcode interrupt is the address of the first byte of the illegal opcode. Otherwise, it would be almost impossible to determine whether the illegal opcode had been one or two bytes. The stacked return address can be used as a pointer to the illegal opcode so the illegal opcode service routine can evaluate the offending opcode.

**Resets and Interrupts**

Figure 5-5. Processing Flow Out of Reset (Sheet 2 of 2)

**Resets and Interrupts**

Figure 5-6. Interrupt Priority Resolution (Sheet 2 of 2)

M68HC11E Family Data Sheet, Rev. 5.1

**Low-Power Operation**

Figure 5-7. Interrupt Source Resolution Within SCI

# 5.6.2 Stop Mode

Executing the STOP instruction while the S bit in the CCR is equal to 0 places the MCU in stop mode. If the S bit is not 0, the stop opcode is treated as a no-op (NOP). Stop mode offers minimum power consumption because all clocks, including the crystal oscillator, are stopped while in this mode. To exit stop and resume normal processing, a logic low level must be applied to one of the external interrupts (IRQ or XIRQ) or to the RESET pin. A pending edge-triggered IRQ can also bring the CPU out of stop.

Because all clocks are stopped in this mode, all internal peripheral functions also stop. The data in the internal RAM is retained as long as  $V_{DD}$  power is maintained. The CPU state and I/O pin levels are static and are unchanged by stop. Therefore, when an interrupt comes to restart the system, the MCU resumes processing as if there were no interruption. If reset is used to restart the system, a normal reset sequence results in which all I/O pins and functions are also restored to their initial states.

To use the  $\overline{IRQ}$  pin as a means of recovering from stop, the I bit in the CCR must be clear ( $\overline{IRQ}$  not masked). The  $\overline{XIRQ}$  pin can be used to wake up the MCU from stop regardless of the state of the X bit in the CCR, although the recovery sequence depends on the state of the X bit. If X is set to 0 ( $\overline{XIRQ}$  not

TDRE and TC flags are normally set when the transmitter is first enabled (TE set to 1). The TDRE flag indicates there is room in the transmit queue to store another data character in the TDR. The TIE bit is the local interrupt mask for TDRE. When TIE is 0, TDRE must be polled. When TIE and TDRE are 1, an interrupt is requested.

The TC flag indicates the transmitter has completed the queue. The TCIE bit is the local interrupt mask for TC. When TCIE is 0, TC must be polled. When TCIE is 1 and TC is 1, an interrupt is requested.

Writing a 0 to TE requests that the transmitter stop when it can. The transmitter completes any transmission in progress before actually shutting down. Only an MCU reset can cause the transmitter to stop and shut down immediately. If TE is written to 0 when the transmitter is already idle, the pin reverts to its general-purpose I/O function (synchronized to the bit-rate clock). If anything is being transmitted when TE is written to 0, that character is completed before the pin reverts to general-purpose I/O, but any other characters waiting in the transmit queue are lost. The TC and TDRE flags are set at the completion of this last character, even though TE has been disabled.

# 7.9 Receiver Flags

The SCI receiver has five status flags, three of which can generate interrupt requests. The status flags are set by the SCI logic in response to specific conditions in the receiver. These flags can be read (polled) at any time by software. Refer to Figure 7-10, which shows SCI interrupt arbitration.

When an overrun takes place, the new character is lost, and the character that was in its way in the parallel RDR is undisturbed. RDRF is set when a character has been received and transferred into the parallel RDR. The OR flag is set instead of RDRF if overrun occurs. A new character is ready to be transferred into RDR before a previous character is read from RDR.

The NF and FE flags provide additional information about the character in the RDR, but do not generate interrupt requests.

The last receiver status flag and interrupt source come from the IDLE flag. The RxD line is idle if it has constantly been at logic 1 for a full character time. The IDLE flag is set only after the RxD line has been busy and becomes idle, which prevents repeated interrupts for the whole time RxD remains idle.

#### Serial Peripheral Interface (SPI)

## MSTR — Master Mode Select Bit

It is customary to have an external pullup resistor on lines that are driven by open-drain devices.

- 0 = Slave mode

- 1 = Master mode

## **CPOL** — Clock Polarity Bit

When the clock polarity bit is cleared and data is not being transferred, the SCK pin of the master device has a steady state low value. When CPOL is set, SCK idles high. Refer to Figure 8-2 and 8.4 Clock Phase and Polarity Controls.

## CPHA — Clock Phase Bit

The clock phase bit, in conjunction with the CPOL bit, controls the clock-data relationship between master and slave. The CPHA bit selects one of two different clocking protocols. Refer to Figure 8-2 and 8.4 Clock Phase and Polarity Controls.

## SPR[1:0] — SPI Clock Rate Select Bits

These two bits select the SPI clock (SCK) rate when the device is configured as master. When the device is configured as slave, these bits have no effect. Refer to Table 8-1.

| SPR[1:0] | Divide<br>E Clock By | Frequency at<br>E = 1 MHz<br>(Baud) | Frequency at<br>E = 2 MHz<br>(Baud) | Frequency at<br>E = 3 MHz (<br>Baud) | Frequency at<br>E = 4 MHz<br>(Baud) |

|----------|----------------------|-------------------------------------|-------------------------------------|--------------------------------------|-------------------------------------|

| 0 0      | 2                    | 500 kHz                             | 1.0 MHz                             | 1.5 MHz                              | 2 MHz                               |

| 0 1      | 4                    | 250 kHz                             | 500 kHz                             | 750 kHz                              | 1 MHz                               |

| 10       | 16                   | 62.5 kHz                            | 125 kHz                             | 187.5 kHz                            | 250 kHz                             |

| 11       | 32                   | 31.3 kHz                            | 62.5 kHz                            | 93.8 kHz                             | 125 kHz                             |

#### Table 8-1. SPI Clock Rates

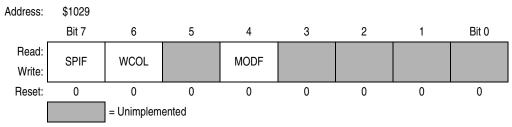

## 8.7.2 Serial Peripheral Status Register

## SPIF — SPI Interrupt Complete Flag

SPIF is set upon completion of data transfer between the processor and the external device. If SPIF goes high, and if SPIE is set, a serial peripheral interrupt is generated. To clear the SPIF bit, read the SPSR with SPIF set, then access the SPDR. Unless SPSR is read (with SPIF set) first, attempts to write SPDR are inhibited.

## WCOL — Write Collision Bit

Clearing the WCOL bit is accomplished by reading the SPSR (with WCOL set) followed by an access of SPDR. Refer to 8.5.4 Slave Select and 8.6 SPI System Errors.

- 0 = No write collision

- 1 = Write collision

**Electrical Characteristics**

Note: RESET also causes recovery from WAIT.

Figure 10-5. WAIT Recovery from Interrupt Timing Diagram

160

**Electrical Characteristics**

# **10.15 Expansion Bus Timing Characteristics**

| Num | Characteristic <sup>(1)</sup>                                                                                 | Symbol            | 1.0   | MHz   | 2.0 MHz |     | 3.0 MHz |     | Unit |

|-----|---------------------------------------------------------------------------------------------------------------|-------------------|-------|-------|---------|-----|---------|-----|------|

| Num | Characteristic                                                                                                | Symbol            | Min   | Max   | Min     | Max | Min     | Max | Unit |

|     | Frequency of operation (E-clock frequency)                                                                    | f <sub>o</sub>    | dc    | 1.0   | dc      | 2.0 | dc      | 3.0 | MHz  |

| 1   | Cycle time                                                                                                    | t <sub>CYC</sub>  | 1000  | _     | 500     | —   | 333     | —   | ns   |

| 2   | Pulse width, E low <sup>(2)</sup> , PW <sub>EL</sub> = 1/2 $t_{CYC}$ -23 ns                                   | $PW_{EL}$         | 477   | _     | 227     | _   | 146     | _   | ns   |

| 3   | Pulse width, E high <sup>(2)</sup> , PW <sub>EH</sub> = 1/2 t <sub>CYC</sub> -28 ns                           | PW <sub>EH</sub>  | 472   | —     | 222     | _   | 141     | _   | ns   |

| 4a  | E and AS rise time                                                                                            | t <sub>r</sub>    | —     | 20    | —       | 20  |         | 20  | ns   |

| 4b  | E and AS fall time                                                                                            | t <sub>f</sub>    | —     | 20    | —       | 20  | —       | 15  | ns   |

| 9   | Address hold time <sup>(2) (3)a</sup> , $t_{AH} = 1/8 t_{CYC}$ –29.5 ns                                       | t <sub>AH</sub>   | 95.5  | —     | 33      | —   | 26      | —   | ns   |

| 12  | Non-multiplexed address valid time to E rise<br>$t_{AV} = PW_{EL} - (t_{ASD} + 80 \text{ ns})^{(2)} (^{3)a}$  | t <sub>AV</sub>   | 281.5 | _     | 94      | _   | 54      | _   | ns   |

| 17  | Read data setup time                                                                                          | t <sub>DSR</sub>  | 30    | —     | 30      | —   | 30      | —   | ns   |

| 18  | Read data hold time, max = $t_{MAD}$                                                                          | t <sub>DHR</sub>  | 0     | 145.5 | 0       | 83  | 0       | 51  | ns   |

| 19  | Write data delay time, $t_{DDW} = 1/8 t_{CYC} + 65.5 ns^{(2)} (3)a$                                           | t <sub>DDW</sub>  | _     | 190.5 | _       | 128 |         | 71  | ns   |

| 21  | Write data hold time, $t_{DHW} = 1/8 t_{CYC} - 29.5 ns^{(2)} (3)a$                                            | t <sub>DHW</sub>  | 95.5  | _     | 33      | _   | 26      |     | ns   |

| 22  | Multiplexed address valid time to E rise<br>$t_{AVM} = PW_{EL} - (t_{ASD} + 90 \text{ ns})^{(2)} {}^{(3)a}$   | t <sub>AVM</sub>  | 271.5 | _     | 84      |     | 54      | _   | ns   |

| 24  | Multiplexed address valid time to AS fall $t_{ASL} = PW_{ASH} -70 \text{ ns}^{(2)}$                           | t <sub>ASL</sub>  | 151   | _     | 26      | _   | 13      | _   | ns   |

| 25  | Multiplexed address hold time<br>$t_{AHL} = 1/8 t_{CYC}$ -29.5 ns <sup>(2) (3)b</sup>                         |                   | 95.5  | _     | 33      | _   | 31      | _   | ns   |

| 26  | Delay time, E to AS rise, $t_{ASD} = 1/8 t_{CYC} - 9.5 ns^{(2)} (3)a$                                         | t <sub>ASD</sub>  | 115.5 | —     | 53      | _   | 31      | _   | ns   |

| 27  | Pulse width, AS high, $PW_{ASH} = 1/4 t_{CYC} - 29 ns^{(2)}$                                                  | PW <sub>ASH</sub> | 221   | _     | 96      | _   | 63      | —   | ns   |

| 28  | Delay time, AS to E rise, $t_{ASED} = 1/8 t_{CYC}$ –9.5 ns <sup>(2) (3)b</sup>                                | t <sub>ASED</sub> | 115.5 | _     | 53      | _   | 31      | —   | ns   |

| 29  | MPU address access time <sup>(3)a</sup><br>$t_{ACCA} = t_{CYC} - (PW_{EL} - t_{AVM}) - t_{DSR} - t_{f}$       | t <sub>ACCA</sub> | 744.5 | _     | 307     | _   | 196     | _   | ns   |

| 35  | MPU access time, $t_{ACCE} = PW_{EH} - t_{DSR}$                                                               | t <sub>ACCE</sub> | —     | 442   | —       | 192 |         | 111 | ns   |

| 36  | Multiplexed address delay (Previous cycle MPU read)<br>$t_{MAD} = t_{ASD} + 30 \text{ ns}^{(2)} \text{ (3)a}$ | t <sub>MAD</sub>  | 145.5 | —     | 83      | _   | 51      | _   | ns   |

1.  $V_{DD}$  = 5.0 Vdc ±10%,  $V_{SS}$  = 0 Vdc,  $T_A$  =  $T_L$  to  $T_H$ , all timing is shown with respect to 20%  $V_{DD}$  and 70%  $V_{DD}$ , unless otherwise noted

2. Formula only for dc to 2 MHz

3. Input clocks with duty cycles other than 50% affect bus performance. Timing parameters affected by input clock duty cycle are identified by (a) and (b). To recalculate the approximate bus timing values, substitute the following expressions in place of 1/8  $t_{CYC}$  in the above formulas, where applicable: (a) (1–dc)  $\times$  1/4  $t_{CYC}$

(b) dc  $\times$  1/4 t<sub>CYC</sub>

Where:

dc is the decimal value of duty cycle percentage (high time)

# 11.5 52-Pin Plastic-Leaded Chip Carrier (Case 778)

0.020 2 °

10

0.730

Z

G1 0.710

K1 0.040

2 °

1.02

18.04 18.54

- Extensive on-line MCU information via the CHIPINFO command. View memory map, vectors, register, and pinout information pertaining to the device being emulated

- Host software supports:

- An editor

- An assembler and user interface

- Source-level debug

- Bus state analysis

- IBM<sup>®</sup> mouse

# A.5 SPGMR11 — Serial Programmer for M68HC11 MCUs

The SPGMR11 is a modular EPROM/EEPROM programming tool for all M68HC11 devices. The programmer features interchangeable adapters that allow programming of various M68HC11 package types.

Programmer features include:

- Programs M68HC11 Family devices that contain an EPROM or EEPROM array.

- Can be operated as a stand-alone programmer connected to a host computer or connected between a host computer and the M68HC11 modular development system (MMDS11) station module

- Uses plug-in programming adapters to accommodate a variety of MCU devices and packages

- On-board programming voltage circuit eliminates the need for an external 12-volt supply.

- Includes programming software and a user's manual

- Includes a +5-volt power cable and a DB9 to DB25 connector adapter

<sup>&</sup>lt;sup>®</sup> IBM is a registered trademark145 of International Business Machines Corporation.

Freescale Semiconductor

**Application Note**

AN1060 Rev. 1.1, 07/2005

# M68HC11 Bootstrap Mode

By Jim Sibigtroth Mike Rhoades John Langan Austin, Texas

## Introduction

The M68HC11 Family of MCUs (microcontroller units) has a bootstrap mode that allows a user-defined program to be loaded into the internal random-access memory (RAM) by way of the serial communications interface (SCI); the M68HC11 then executes this loaded program. The loaded program can do anything a normal user program can do as well as anything a factory test program can do because protected control bits are accessible in bootstrap mode. Although the bootstrap mode is a single-chip mode of operation, expanded mode resources are accessible because the mode control bits can be changed while operating in the bootstrap mode.

This application note explains the operation and application of the M68HC11 bootstrap mode. Although basic concepts associated with this mode are quite simple, the more subtle implications of these functions require careful consideration. Useful applications of this mode are overlooked due to an incomplete understanding of bootstrap mode. Also, common problems associated with bootstrap mode could be avoided by a more complete understanding of its operation and implications.

Topics discussed in this application note include:

- Basic operation of the M68HC11 bootstrap mode

- General discussion of bootstrap mode uses

- Detailed explanation of on-chip bootstrap logic

- Detailed explanation of bootstrap firmware

- Bootstrap firmware vs. EEPROM security

- Incorporating the bootstrap mode into a system

- Driving bootstrap mode from another M68HC11

- Driving bootstrap mode from a personal computer

- Common bootstrap mode problems

- Variations for specific versions of M68HC11

- Commented listings for selected M68HC11 bootstrap ROMs

© Freescale Semiconductor, Inc., 2005. All rights reserved.

## **Basic Bootstrap Mode**

This section describes only basic functions of the bootstrap mode. Other functions of the bootstrap mode are described in detail in the remainder of this application note.

When an M68HC11 is reset in bootstrap mode, the reset vector is fetched from a small internal read-only memory (ROM) called the bootstrap ROM or boot ROM. The firmware program in this boot ROM then controls the bootloading process, in this manner:

- First, the on-chip SCI (serial communications interface) is initialized. The first character received (\$FF) determines which of two possible baud rates should be used for the remaining characters in the download operation.

- Next, a binary program is received by the SCI system and is stored in RAM.

- Finally, a jump instruction is executed to pass control from the bootloader firmware to the user's loaded program.

Bootstrap mode is useful both at the component level and after the MCU has been embedded into a finished user system.

At the component level, Freescale uses bootstrap mode to control a monitored burn-in program for the on-chip electrically erasable programmable read-only memory (EEPROM). Units to be tested are loaded into special circuit boards that each hold many MCUS. These boards are then placed in burn-in ovens. Driver boards outside the ovens download an EEPROM exercise and diagnostic program to all MCUs in parallel. The MCUs under test independently exercise their internal EEPROM and monitor programming and erase operations. This technique could be utilized by an end user to load program information into the EPROM or EEPROM of an M68HC11 before it is installed into an end product. As in the burn-in setup, many M68HC11s can be gang programmed in parallel. This technique can also be used to program the EPROM of finished products after final assembly.

Freescale also uses bootstrap mode for programming target devices on the M68HC11 evaluation modules (EVM). Because bootstrap mode is a privileged mode like special test, the EEPROM-based configuration register (CONFIG) can be programmed using bootstrap mode on the EVM.

The greatest benefits from bootstrap mode are realized by designing the finished system so that bootstrap mode can be used after final assembly. The finished system need not be a single-chip mode application for the bootstrap mode to be useful because the expansion bus can be enabled after resetting the MCU in bootstrap mode. Allowing this capability requires almost no hardware or design cost and the addition of this capability is invisible in the end product until it is needed.

The ability to control the embedded processor through downloaded programs is achieved without the disassembly and chip-swapping usually associated with such control. This mode provides an easy way to load non-volatile memories such as EEPROM with calibration tables or to program the application firmware into a one-time programmable (OTP) MCU after final assembly.

Another powerful use of bootstrap mode in a finished assembly is for final test. Short programs can be downloaded to check parts of the system, including components and circuitry external to the embedded MCU. If any problems appear during product development, diagnostic programs can be downloaded to find the problems, and corrected routines can be downloaded and checked before incorporating them into the main application program.

Listing 1. MCU-to-MCU Duplicator Program

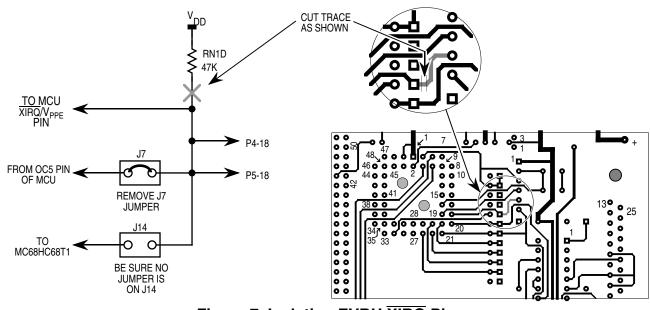

Figure 7. Isolating EVBU XIRQ Pin

# Listing 1. MCU-to-MCU Duplicator Program

| 1  |      | ********    | ******   | * * * * * * * * * * * * * * * * * * * | * * * * * * * * * * * * * * *  |

|----|------|-------------|----------|---------------------------------------|--------------------------------|

| 2  |      | * 68HC711E9 | Duplic   | cator Program for                     | AN1060                         |

| 3  |      | *******     | *******  | * * * * * * * * * * * * * * * * * * * | * * * * * * * * * * * * * * *  |

| 4  |      |             |          |                                       |                                |

| 5  |      | * * * * *   |          |                                       |                                |

| 6  |      | * Equates - | - All re | eg addrs except II                    | NIT are 2-digit                |

| 7  |      | *           |          | irect addressing                      | 5                              |

| 8  |      | * * * * *   |          | 5                                     |                                |

| 9  | 103D | INIT        | EQU      | \$103D                                | RAM, Reg mapping               |

| 10 | 0028 | SPCR        | EQU      | \$28                                  | DWOM in bit-5                  |

| 11 | 0004 | PORTB       | EQU      | \$04                                  | Red LED = bit-1, $Grn = bit-0$ |

| 12 |      | * Reset of  | prog so  | ocket = bit-7                         |                                |

| 13 | 0080 | RESET       | EQU      | 81000000                              |                                |

| 14 | 0002 | RED         | EQU      | %0000010                              |                                |

| 15 | 0001 | GREEN       | EQU      | 80000001                              |                                |

| 16 | A000 | PORTE       | EQU      | \$0A                                  | Vpp Sense in bit-7, 1=ON       |

| 17 | 002E | SCSR        | EQU      | \$2E                                  | SCI status register            |

| 18 |      | * TDRE, TC, | RDRF,    | IDLE; OR, NF, FE                      | ,                              |

| 19 | 0080 | TDRE        | EQU      | 81000000                              |                                |

| 20 | 0020 | RDRF        | EQU      | %00100000                             |                                |

| 21 | 002F | SCDR        | EQU      | \$2F                                  | SCI data register              |

| 22 | BF00 | PROGRAM     | EQU      | \$BF00                                | EPROM prog utility in boot ROM |

| 23 | D000 | EPSTRT      | EQU      | \$D000                                | Starting address of EPROM      |

| 24 |      |             |          |                                       | -                              |

| 25 | B600 |             | ORG      | \$B600                                | Start of EEPROM                |

| 26 |      |             |          |                                       |                                |

## Bootloading a Program to Performa ROM Checksum

The bootloader ROM must be turned off before performing the checksum program. To remove the boot ROM from the memory map, clear the RBOOT bit in the HPRIO register. This is normally a write-protected bit that is 0, but in bootstrap mode it is reset to 1 and can be written. If the boot ROM is not disabled, the checksum routine will read the contents of the boot ROM rather than the user's mask ROM or EPROM at the same addresses.

#### Inherent Delays Caused by Double Buffering of SCI Data

This problem is troublesome in cases where one MCU is bootloading to another MCU.

Because of transmitter double buffering, there may be one character in the serial shifter as a new character is written into the transmit data register. In cases such as downloading in which this 2-character pipeline is kept full, a 2-character time delay occurs between when a character is written to the transmit data register and when that character finishes transmitting. A little more than one more character time delay occurs between the target MCU receiving the character and echoing it back. If the master MCU waits for the echo of each downloaded character before sending the next one, the download process takes about twice as long as it would if transmission is treated as a separate process or if verify data is ignored.

## **Boot ROM Variations**

Different versions of the M68HC11 have different versions of the bootstrap ROM program. Table 3 summarizes the features of the boot ROMs in 16 members of the M68HC11 Family.

The boot ROMs for the MC68HC11F1, the MC68HC711K4, and the MC68HC11K4 allow additional choices of baud rates for bootloader communications. For the three new baud rates, the first character used to determine the baud rate is not \$FF as it was in earlier M68HC11s. The intercharacter delay that terminates the variable-length download is also different for these new baud rates. Table 3 shows the synchronization characters, delay times, and baud rates as they relate to E-clock frequency.

## **Commented Boot ROM Listing**

Listing 3. MC68HC711E9 Bootloader ROM contains a complete commented listing of the boot ROM program in the MC68HC711E9 version of the M68HC11. Other versions can be found in **Appendix B** of the *M68HC11 Reference Manual*.

| Sync<br>Character | Timeout         | Baud Rates at E Clock = |         |        |          |        |         |  |  |

|-------------------|-----------------|-------------------------|---------|--------|----------|--------|---------|--|--|

|                   | Delay           | 2 MHz                   | 2.1 MHz | 3 MHz  | 3.15 MHz | 4 MHz  | 4.2 MHz |  |  |

| \$FF              | 4 characters    | 7812                    | 8192    | 11,718 | 12,288   | 15,624 | 16,838  |  |  |

| \$FF              | 4 characters    | 1200                    | 1260    | 1800   | 1890     | 2400   | 2520    |  |  |

| \$F0              | 4.9 characters  | 9600                    | 10,080  | 14,400 | 15,120   | 19,200 | 20,160  |  |  |

| \$FD              | 17.3 characters | 5208                    | 5461    | 7812   | 8192     | 10,416 | 10,922  |  |  |

| \$FD              | 13 characters   | 3906                    | 4096    | 5859   | 6144     | 7812   | 8192    |  |  |

**Table 3. Bootloader Baud Rates**

M68HC11 Bootstrap Mode, Rev. 1.1