Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                 |

| Core Processor             | HC11                                                                     |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 2MHz                                                                     |

| Connectivity               | SCI, SPI                                                                 |

| Peripherals                | POR, WDT                                                                 |

| Number of I/O              | 38                                                                       |

| Program Memory Size        | -                                                                        |

| Program Memory Type        | ROMIess                                                                  |

| EEPROM Size                | 512 x 8                                                                  |

| RAM Size                   | 512 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                              |

| Data Converters            | A/D 8x8b                                                                 |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 52-LCC (J-Lead)                                                          |

| Supplier Device Package    | 52-PLCC (19.1x19.1)                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc68hcp11e1vfne2 |

|  |  |  | nts |

|--|--|--|-----|

|  |  |  |     |

|  |  |  |     |

| 10.15 | Expansion Bus Timing Characteristics                                                         | 168 |

|-------|----------------------------------------------------------------------------------------------|-----|

| 10.16 | MC68L11E9/E20 Expansion Bus Timing Characteristics                                           | 169 |

| 10.17 | Serial Peripheral Interface Timing Characteristics                                           | 171 |

| 10.18 | MC68L11E9/E20 Serial Peirpheral Interface Characteristics                                    | 172 |

| 10.19 | EEPROM Characteristics                                                                       | 175 |

| 10.20 | MC68L11E9/E20 EEPROM Characteristics                                                         | 175 |

|       | EPROM Characteristics                                                                        |     |

|       | Chapter 11                                                                                   |     |

|       | Chapter 11 Ordering Information and Mechanical Specifications                                |     |

| 11.1  | Introduction                                                                                 | 177 |

| 11.2  | Standard Device Ordering Information                                                         |     |

| 11.3  | Custom ROM Device Ordering Information                                                       |     |

| 11.4  | Extended Voltage Device Ordering Information (3.0 Vdc to 5.5 Vdc)                            |     |

| 11.5  | 52-Pin Plastic-Leaded Chip Carrier (Case 778)                                                |     |

| 11.6  | 52-Pin Windowed Ceramic-Leaded Chip Carrier (Case 778B)                                      |     |

| 11.7  | 64-Pin Quad Flat Pack (Case 840C)                                                            |     |

| 11.8  | 52-Pin Thin Quad Flat Pack (Case 848D)                                                       |     |

| 11.9  | 56-Pin Dual in-Line Package (Case 859).                                                      |     |

| 11.10 | 48-Pin Plastic DIP (Case 767)                                                                |     |

|       |                                                                                              |     |

|       | Appendix A Development Support                                                               |     |

| A.1   | Introduction                                                                                 | 187 |

| A.2   | M68HC11 E-Series Development Tools                                                           |     |

| A.3   | EVS — Evaluation System                                                                      |     |

| A.4   | Modular Development System (MMDS11)                                                          |     |

| A.5   | SPGMR11 — Serial Programmer for M68HC11 MCUs                                                 |     |

| 71.0  |                                                                                              | 100 |

|       | Appendix B                                                                                   |     |

|       | EVBU Schematic                                                                               |     |

| AN106 | 60 — M68HC11 Bootstrap Mode                                                                  | 193 |

| ED404 | Frankling the Convity Frankling on the MCCOLIC711FO Devices with DChurc11 on the             |     |

|       | — Enabling the Security Feature on the MC68HC711E9 Devices with PCbug11 on the S8HC711E9PGMR | 229 |

| IVIC  | STIOT TIEST GIVIT                                                                            |     |

|       | B — Enabling the Security Feature on M68HC811E2 Devices                                      |     |

| wit   | h PCbug11 on the M68HC711E9PGMR                                                              | 233 |

| FB296 | 6 — Programming MC68HC711E9 Devices with PCbug11                                             |     |

|       | d the M68HC11EVBU                                                                            | 237 |

M68HC11E Family Data Sheet, Rev. 5.1

# 1.4.1 $V_{DD}$ and $V_{SS}$

Power is supplied to the MCU through  $V_{DD}$  and  $V_{SS}$ .  $V_{DD}$  is the power supply,  $V_{SS}$  is ground. The MCU operates from a single 5-volt (nominal) power supply. Low-voltage devices in the E series operate at 3.0–5.5 volts.

Very fast signal transitions occur on the MCU pins. The short rise and fall times place high, short duration current demands on the power supply. To prevent noise problems, provide good power supply bypassing at the MCU. Also, use bypass capacitors that have good

high-frequency characteristics and situate them as close to the MCU as possible. Bypass requirements vary, depending on how heavily the MCU pins are loaded.

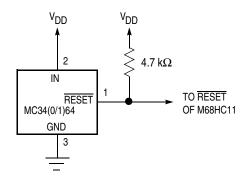

Figure 1-7. External Reset Circuit

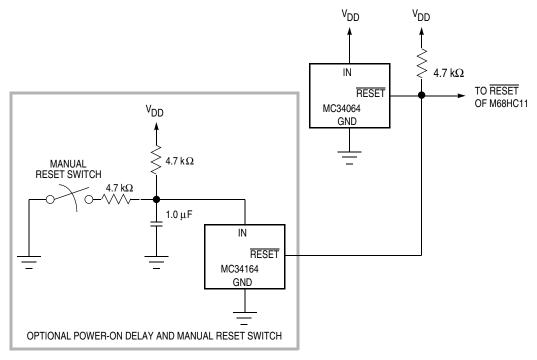

Figure 1-8. External Reset Circuit with Delay

#### **General Description**

#### NOTE

IRQ must be configured for level-sensitive operation if there is more than one source of IRQ interrupt.

There should be a single pullup resistor near the MCU interrupt input pin (typically 4.7  $k\Omega$ ). There must also be an interlock mechanism at each interrupt source so that the source holds the interrupt line low until the MCU recognizes and acknowledges the interrupt request. If one or more interrupt sources are still pending after the MCU services a request, the interrupt line will still be held low and the MCU will be interrupted again as soon as the interrupt mask bit in the MCU is cleared (normally upon return from an interrupt). Refer to Chapter 5 Resets and Interrupts.

V<sub>PPE</sub> is the input for the 12-volt nominal programming voltage required for EPROM/OTPROM programming. On devices without EPROM/OTPROM, this pin is only an XIRQ input.

#### **CAUTION**

During EPROM programming of the MC68HC711E9 device, the V<sub>PPE</sub> pin circuitry may latch-up and be damaged if the input current is not limited to 10 mA. For more information please refer to MC68HC711E9 8-Bit Microcontroller Unit Mask Set Errata 3 (Freescale document order number 68HC711E9MSE3.

# 1.4.7 MODA and MODB (MODA/LIR and MODB/V<sub>STBY</sub>)

During reset, MODA and MODB select one of the four operating modes:

- Single-chip mode

- Expanded mode

- Test mode

- Bootstrap mode

Refer to Chapter 2 Operating Modes and On-Chip Memory.

After the operating mode has been selected, the load instruction register (LIR) pin provides an open-drain output to indicate that execution of an instruction has begun. A series of E-clock cycles occurs during execution of each instruction. The LIR signal goes low during the first E-clock cycle of each instruction (opcode fetch). This output is provided for assistance in program debugging.

The  $V_{STBY}$  pin is used to input random-access memory (RAM) standby power. When the voltage on this pin is more than one MOS threshold (about 0.7 volts) above the  $V_{DD}$  voltage, the internal RAM and part of the reset logic are powered from this signal rather than the  $V_{DD}$  input. This allows RAM contents to be retained without  $V_{DD}$  power applied to the MCU. Reset must be driven low before  $V_{DD}$  is removed and must remain low until  $V_{DD}$  has been restored to a valid level.

# 1.4.8 $V_{RI}$ and $V_{RH}$

These two inputs provide the reference voltages for the analog-to-digital (A/D) converter circuitry:

- V<sub>RL</sub> is the low reference, typically 0 Vdc.

- V<sub>RH</sub> is the high reference.

For proper A/D converter operation:

- V<sub>RH</sub> should be at least 3 Vdc greater than V<sub>RI</sub>.

- V<sub>RL</sub> and V<sub>RH</sub> should be between V<sub>SS</sub> and V<sub>DD</sub>.

M68HC11E Family Data Sheet, Rev. 5.1

# **General Description**

**Table 1-1. Port Signal Functions**

| Port/Bit | Single-Chip and<br>Bootstrap Modes | Expanded and<br>Test Modes |  |  |  |  |

|----------|------------------------------------|----------------------------|--|--|--|--|

| PA0      | PA0                                | /IC3                       |  |  |  |  |

| PA1      | PA1/IC2                            |                            |  |  |  |  |

| PA2      | PA2/IC1                            |                            |  |  |  |  |

| PA3      | PA3/OC5/IC4/OC1                    |                            |  |  |  |  |

| PA4      | PA4/OC4/OC1                        |                            |  |  |  |  |

| PA5      | PA5/OC3/OC1                        |                            |  |  |  |  |

| PA6      | PA6/OC2/OC1                        |                            |  |  |  |  |

| PA7      | PA7/PA                             | AI/OC1                     |  |  |  |  |

| PB0      | PB0                                | ADDR8                      |  |  |  |  |

| PB1      | PB1                                | ADDR9                      |  |  |  |  |

| PB2      | PB2                                | ADDR10                     |  |  |  |  |

| PB3      | PB3                                | ADDR11                     |  |  |  |  |

| PB4      | PB4                                | ADDR12                     |  |  |  |  |

| PB5      | PB5                                | ADDR13                     |  |  |  |  |

| PB6      | PB6                                | ADDR14                     |  |  |  |  |

| PB7      | PB7                                | ADDR15                     |  |  |  |  |

| PC0      | PC0                                | ADDR0/DATA0                |  |  |  |  |

| PC1      | PC1                                | ADDR1/DATA1                |  |  |  |  |

| PC2      | PC2                                | ADDR2/DATA2                |  |  |  |  |

| PC3      | PC3                                | ADDR3/DATA3                |  |  |  |  |

| PC4      | PC4                                | ADDR4/DATA4                |  |  |  |  |

| PC5      | PC5                                | ADDR5/DATA5                |  |  |  |  |

| PC6      | PC6                                | ADDR6/DATA6                |  |  |  |  |

| PC7      | PC7                                | ADDR7/DATA7                |  |  |  |  |

| PD0      | PD0/RxD                            |                            |  |  |  |  |

| PD1      | PD1.                               | /TxD                       |  |  |  |  |

| PD2      | PD2/I                              | MISO                       |  |  |  |  |

| PD3      | PD3/l                              | MOSI                       |  |  |  |  |

| PD4      | PD4/SCK                            |                            |  |  |  |  |

| PD5      | PD5                                | 5/ <u>SS</u>               |  |  |  |  |

| _        | STRA                               | AS                         |  |  |  |  |

| _        | STRB                               | R/W                        |  |  |  |  |

| PE0      | PE0/                               | /ANO                       |  |  |  |  |

| PE1      | PE1/                               |                            |  |  |  |  |

| PE2      |                                    | /AN2                       |  |  |  |  |

| PE3      |                                    | /AN3                       |  |  |  |  |

| PE4      |                                    | /AN4                       |  |  |  |  |

| PE5      | PE5/AN5                            |                            |  |  |  |  |

| PE6      | PE6/AN6                            |                            |  |  |  |  |

| PE7      | PE7/AN7                            |                            |  |  |  |  |

| 1        | 1 - 11:51                          |                            |  |  |  |  |

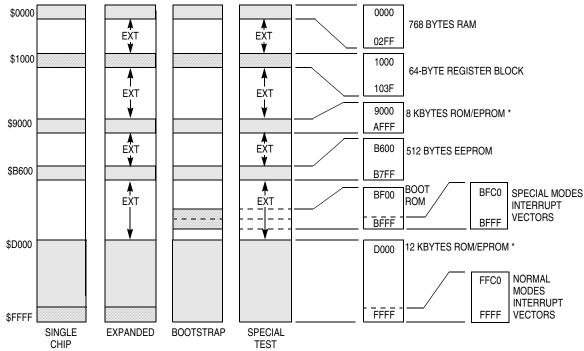

<sup>\* 20</sup> Kbytes ROM/EPROM are contained in two segments of 8 Kbytes and 12 Kbytes each.

Figure 2-5. Memory Map for MC68HC(7)11E20

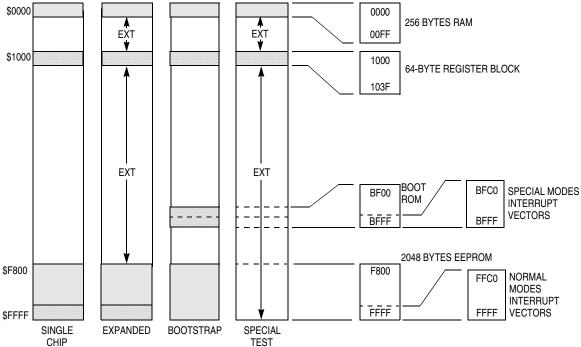

Figure 2-6. Memory Map for MC68HC811E2

M68HC11E Family Data Sheet, Rev. 5.1

Analog-to-Digital (A/D) Converter

# 3.3 A/D Converter Power-Up and Clock Select

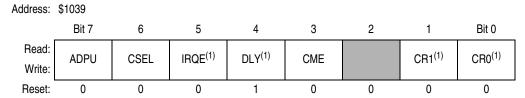

Bit 7 of the OPTION register controls A/D converter power-up. Clearing ADPU removes power from and disables the A/D converter system. Setting ADPU enables the A/D converter system. Stabilization of the analog bias voltages requires a delay of as much as 100 µs after turning on the A/D converter. When the A/D converter system is operating with the MCU E clock, all switching and comparator operations are inherently synchronized to the main MCU clocks. This allows the comparator output to be sampled at relatively quiet times during MCU clock cycles. Since the internal RC oscillator is asynchronous to the MCU clock, there is more error attributable to internal system clock noise. A/D converter accuracy is reduced slightly while the internal RC oscillator is being used (CSEL = 1).

1. Can be written only once in first 64 cycles out of reset in normal modes or at any time in special modes

Figure 3-4. System Configuration Options Register (OPTION)

# ADPU — A/D Power-Up Bit

0 = A/D powered down

1 = A/D powered up

#### CSEL — Clock Select Bit

0 = A/D and EEPROM use system E clock.

1 = A/D and EEPROM use internal RC clock.

#### IRQE — Configure IRQ for Edge-Sensitive Only Operation

Refer to Chapter 5 Resets and Interrupts.

#### DLY — Enable Oscillator Startup Delay Bit

- 0 = The oscillator startup delay coming out of stop is bypassed and the MCU resumes processing within about four bus cycles.

- 1 = A delay of approximately 4000 E-clock cycles is imposed as the MCU is started up from the stop power-saving mode. This delay allows the crystal oscillator to stabilize.

#### **CME** — Clock Monitor Enable Bit

Refer to Chapter 5 Resets and Interrupts.

## Bit 2 — Not implemented

Always reads 0

#### CR[1:0] — COP Timer Rate Select Bits

Refer to Chapter 5 Resets and Interrupts and Chapter 9 Timing Systems.

When this control bit is clear, the four requested conversions are performed once to fill the four result registers. When this control bit is set, conversions are performed continuously with the result registers updated as data becomes available.

#### **MULT** — Multiple Channel/Single Channel Control Bit

When this bit is clear, the A/D converter system is configured to perform four consecutive conversions on the single channel specified by the four channel select bits CD:CA (bits [3:0] of the ADCTL register). When this bit is set, the A/D system is configured to perform a conversion on each of four channels where each result register corresponds to one channel.

#### NOTE

When the multiple-channel continuous scan mode is used, extra care is needed in the design of circuitry driving the A/D inputs. The charge on the capacitive DAC array before the sample time is related to the voltage on the previously converted channel. A charge share situation exists between the internal DAC capacitance and the external circuit capacitance. Although the amount of charge involved is small, the rate at which it is repeated is every  $64\,\mu s$  for an E clock of 2 MHz. The RC charging rate of the external circuit must be balanced against this charge sharing effect to avoid errors in accuracy. Refer to M68HC11 Reference Manual, Freescale document order number M68HC11RM/AD, for further information.

#### CD:CA — Channel Selects D:A Bits

Refer to Table 3-2. When a multiple channel mode is selected (MULT = 1), the two least significant channel select bits (CB and CA) have no meaning and the CD and CC bits specify which group of four channels is to be converted.

| Channel Select Control Bits CD:CC:CB:CA | Channel Signal                      | Result in ADRx<br>if MULT = 1 |  |  |  |  |

|-----------------------------------------|-------------------------------------|-------------------------------|--|--|--|--|

|                                         | ANIO                                | ADD4                          |  |  |  |  |

| 0000                                    | AN0                                 | ADR1                          |  |  |  |  |

| 0001                                    | AN1                                 | ADR2                          |  |  |  |  |

| 0010                                    | AN2                                 | ADR3                          |  |  |  |  |

| 0011                                    | AN3                                 | ADR4                          |  |  |  |  |

| 0100                                    | AN4                                 | ADR1                          |  |  |  |  |

| 0101                                    | AN5                                 | ADR2                          |  |  |  |  |

| 0110                                    | AN6                                 | ADR3                          |  |  |  |  |

| 0111                                    | AN7                                 | ADR4                          |  |  |  |  |

| 10XX                                    | Reserved                            | _                             |  |  |  |  |

| 1100                                    | V <sub>RH</sub> <sup>(1)</sup>      | ADR1                          |  |  |  |  |

| 1101                                    | V <sub>RL</sub> <sup>(1)</sup>      | ADR2                          |  |  |  |  |

| 1110                                    | (V <sub>RH</sub> )/2 <sup>(1)</sup> | ADR3                          |  |  |  |  |

| 1111                                    | Reserved <sup>(1)</sup>             | ADR4                          |  |  |  |  |

Table 3-2. A/D Converter Channel Selection

<sup>1.</sup> Used for factory testing

# **Central Processor Unit (CPU)**

# Table 4-2. Instruction Set (Sheet 5 of 7)

| Manager    | 0                                  | Description (                       | Addressing                        | Ir                            | nstruction              |                       |   |              | Co | onditio | n Co | des |   |   |

|------------|------------------------------------|-------------------------------------|-----------------------------------|-------------------------------|-------------------------|-----------------------|---|--------------|----|---------|------|-----|---|---|

| Mnemonic   | Operation                          | Description                         | Mode                              | Opcode                        | Operand                 | Cycles                | S | Х            | Н  | П       | N    | Z   | ٧ | С |

| LSRD       | Logical Shift<br>Right Double      | 0                                   | INH                               | 04                            | _                       | 3                     | _ | _            | _  | _       | 0    | Δ   | Δ | Δ |

| MUL        | Multiply 8 by 8                    | $A * B \Rightarrow D$               | INH                               | 3D                            | _                       | 10                    | _ | _            | _  | _       | _    | _   | _ | Δ |

| NEG (opr)  | Two's<br>Complement<br>Memory Byte | 0 − M ⇒ M                           | EXT<br>IND,X<br>IND,Y             | 70<br>60<br>18 60             | hh 11<br>ff<br>ff       | 6<br>6<br>7           | _ | _            | _  | _       | Δ    | Δ   | Δ | Δ |

| NEGA       | Two's<br>Complement<br>A           | 0 − A ⇒ A                           | A INH                             | 40                            | _                       | 2                     | _ | _            | _  | _       | Δ    | Δ   | Δ | Δ |

| NEGB       | Two's<br>Complement<br>B           | 0 − B ⇒ B                           | B INH                             | 50                            | _                       | 2                     | _ | -            | _  | _       | Δ    | Δ   | Δ | Δ |

| NOP        | No operation                       | No Operation                        | INH                               | 01                            | _                       | 2                     | _ | _            | _  | _       | _    | _   | _ | _ |

| ORAA (opr) | OR<br>Accumulator<br>A (Inclusive) | A + M ⇒ A                           | A IMM A DIR A EXT A IND,X A IND,Y | 8A<br>9A<br>BA<br>AA<br>18 AA | ii<br>dd<br>hh ll<br>ff | 2<br>3<br>4<br>4<br>5 | _ | _            | _  | _       | Δ    | Δ   | 0 | _ |

| ORAB (opr) | OR<br>Accumulator<br>B (Inclusive) | B + M ⇒ B                           | B IMM B DIR B EXT B IND,X B IND,Y | CA<br>DA<br>FA<br>EA<br>18 EA | ii<br>dd<br>hh ll<br>ff | 2<br>3<br>4<br>4<br>5 | _ | _            | _  | _       | Δ    | Δ   | 0 | _ |

| PSHA       | Push A onto<br>Stack               | ,                                   | A INH                             | 36                            | _                       | 3                     | _ | _            | _  | _       | _    | _   | _ | _ |

| PSHB       | Push B onto<br>Stack               | $B \Rightarrow Stk, SP = SP - 1$    |                                   | 37                            | _                       | 3                     | _ | _            | _  | _       | _    | _   | _ | _ |

| PSHX       | Push X onto<br>Stack (Lo<br>First) | $IX \Rightarrow Stk, SP = SP - 2$   | INH                               | 3C                            | _                       | 4                     | _ | _            | _  | _       | _    | _   | _ | _ |

| PSHY       | Push Y onto<br>Stack (Lo<br>First) | $IY \Rightarrow Stk, SP = SP - 2$   | INH                               | 18 3C                         | _                       | 5                     | _ | _            | _  | _       | _    | _   | _ | _ |

| PULA       | Pull A from<br>Stack               | $SP = SP + 1$ , $A \leftarrow Stk$  | A INH                             | 32                            | _                       | 4                     | _ | _            | _  | _       | _    | _   | _ | _ |

| PULB       | Pull B from<br>Stack               | $SP = SP + 1, B \Leftarrow Stk$     | B INH                             | 33                            | _                       | 4                     | _ | -            | _  | _       | _    | _   | _ | _ |

| PULX       | Pull X From<br>Stack (Hi<br>First) | $SP = SP + 2$ , $IX \Leftarrow Stk$ | INH                               | 38                            | _                       | 5                     | _ | _            | _  | _       | _    | _   | _ | _ |

| PULY       | Pull Y from<br>Stack (Hi<br>First) | $SP = SP + 2$ , $IY \Leftarrow Stk$ | INH                               | 18 38                         | _                       | 6                     | _ | _            | _  | _       | _    | _   | _ | _ |

| ROL (opr)  | Rotate Left                        | C b7 b0                             | EXT<br>IND,X<br>IND,Y             | 79<br>69<br>18 69             | hh 11<br>ff<br>ff       | 6<br>6<br>7           | _ | _            | _  | _       | Δ    | Δ   | Δ | Δ |

| ROLA       | Rotate Left A                      | C b7 b0                             | A INH                             | 49                            | _                       | 2                     | _ | -            | _  | _       | Δ    | Δ   | Δ | Δ |

| ROLB       | Rotate Left B                      | C b7 b0                             | B INH                             | 59                            | _                       | 2                     | _ | _            | _  | _       | Δ    | Δ   | Δ | Δ |

| ROR (opr)  | Rotate Right                       | b7 b0 C                             | EXT<br>IND,X<br>IND,Y             | 76<br>66<br>18 66             | hh 11<br>ff<br>ff       | 6<br>6<br>7           | _ | _            | _  | _       | Δ    | Δ   | Δ | Δ |

| RORA       | Rotate Right A                     | b7 b0 C                             | A INH                             | 46                            | _                       | 2                     | _ | _            |    | _       | Δ    | Δ   | Δ | Δ |

| RORB       | Rotate Right B                     | b7 b0 C                             | B INH                             | 56                            | _                       | 2                     |   | _            | _  | _       | Δ    | Δ   | Δ | Δ |

| RTI        | Return from<br>Interrupt           | See Figure 3–2                      | INH                               | 3B                            | _                       | 12                    | Δ | $\downarrow$ | Δ  | Δ       | Δ    | Δ   | Δ | Δ |

| RTS        | Return from<br>Subroutine          | See Figure 3–2                      | INH                               | 39                            | _                       | 5                     | _ |              | _  | _       | _    | _   | _ | _ |

| SBA        | Subtract B from<br>A               | $A - B \Rightarrow A$               | INH                               | 10                            | _                       | 2                     | _ | _            |    | _       | Δ    | Δ   | Δ | Δ |

#### **Resets and Interrupts**

masked), the MCU starts up, beginning with the stacking sequence leading to normal service of the  $\overline{XIRQ}$  request. If X is set to 1 ( $\overline{XIRQ}$  masked or inhibited), then processing continues with the instruction that immediately follows the STOP instruction, and no  $\overline{XIRQ}$  interrupt service is requested or pending.

Because the oscillator is stopped in stop mode, a restart delay may be imposed to allow oscillator stabilization upon leaving stop. If the internal oscillator is being used, this delay is required; however, if a stable external oscillator is being used, the DLY control bit can be used to bypass this startup delay. The DLY control bit is set by reset and can be optionally cleared during initialization. If the DLY equal to 0 option is used to avoid startup delay on recovery from stop, then reset should not be used as the means of recovering from stop, as this causes DLY to be set again by reset, imposing the restart delay. This same delay also applies to power-on reset, regardless of the state of the DLY control bit, but does not apply to a reset while the clocks are running.

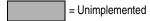

#### **Serial Communications Interface (SCI)**

Note: Refer to Figure B-1. EVBU Schematic Diagram for an example of connecting TxD to a PC.

Figure 7-1. SCI Transmitter Block Diagram

Serial Peripheral Interface (SPI)

|                                |                        |                          | •                     |                                |  |  |  |  |  |

|--------------------------------|------------------------|--------------------------|-----------------------|--------------------------------|--|--|--|--|--|

|                                | XTAL Frequencies       |                          |                       |                                |  |  |  |  |  |

|                                | 4.0 MHz 8.0 MHz        |                          | 12.0 MHz              | Other Rates                    |  |  |  |  |  |

| Control Bits                   | 1.0 MHz                | 2.0 MHz                  | 3.0 MHz               | (E)                            |  |  |  |  |  |

| PR1, PR0                       | 1000 ns                | 1000 ns 500 ns 333 ns (1 |                       |                                |  |  |  |  |  |

|                                | Main Timer Count Rates |                          |                       |                                |  |  |  |  |  |

| 0 0<br>1 count —<br>overflow — | 1000 ns<br>65.536 ms   | 500 ns<br>32.768 ms      | 333 ns<br>21.845 ms   | (E/1)<br>(E/2 <sup>16</sup> )  |  |  |  |  |  |

| 0 1<br>1 count —<br>overflow — | 4.0 μs<br>262.14 ms    | 2.0 μs<br>131.07 ms      | 1.333 μs<br>87.381 ms | (E/4)<br>(E/2 <sup>18</sup> )  |  |  |  |  |  |

| 1 0<br>1 count —<br>overflow — | 8.0 μs<br>524.29 ms    | 4.0 μs<br>262.14 ms      | 2.667 μs<br>174.76 ms | (E/8)<br>(E/2 <sup>19</sup> )  |  |  |  |  |  |

| 1 1<br>1 count —<br>overflow — | 16.0 μs<br>1.049 s     | 8.0 μs<br>524.29 ms      | 5.333 μs<br>349.52 ms | (E/16)<br>(E/2 <sup>20</sup> ) |  |  |  |  |  |

**Table 9-1. Timer Summary**

## 9.2 Timer Structure

Figure 9-2 shows the capture/compare system block diagram. The port A pin control block includes logic for timer functions and for general-purpose I/O. For pins PA3, PA2, PA1, and PA0, this block contains both the edge-detection logic and the control logic that enables the selection of which edge triggers an input capture. The digital level on PA[3:0] can be read at any time (read PORTA register), even if the pin is being used for the input capture function. Pins PA[6:3] are used for either general-purpose I/O, or as output compare pins. When one of these pins is being used for an output compare function, it cannot be written directly as if it were a general-purpose output. Each of the output compare functions (OC[5:2]) is related to one of the port A output pins. Output compare one (OC1) has extra control logic, allowing it optional control of any combination of the PA[7:3] pins. The PA7 pin can be used as a general-purpose I/O pin, as an input to the pulse accumulator, or as an OC1 output pin.

# 9.3 Input Capture

The input capture function records the time an external event occurs by latching the value of the free-running counter when a selected edge is detected at the associated timer input pin. Software can store latched values and use them to compute the periodicity and duration of events. For example, by storing the times of successive edges of an incoming signal, software can determine the period and pulse width of a signal. To measure period, two successive edges of the same polarity are captured. To measure pulse width, two alternate polarity edges are captured.

In most cases, input capture edges are asynchronous to the internal timer counter, which is clocked relative to an internal clock (PH2). These asynchronous capture requests are synchronized to PH2 so that the latching occurs on the opposite half cycle of PH2 from when the timer counter is being incremented. This synchronization process introduces a delay from when the edge occurs to when the counter value is detected. Because these delays offset each other when the time between two edges is being measured, the delay can be ignored. When an input capture is being used with an output compare, there is a similar delay between the actual compare point and when the output pin changes state.

Freescale Semiconductor 129

M68HC11E Family Data Sheet, Rev. 5.1

- Extensive on-line MCU information via the CHIPINFO command. View memory map, vectors, register, and pinout information pertaining to the device being emulated

- Host software supports:

- An editor

- An assembler and user interface

- Source-level debug

- Bus state analysis

- IBM<sup>®</sup> mouse

# A.5 SPGMR11 — Serial Programmer for M68HC11 MCUs

The SPGMR11 is a modular EPROM/EEPROM programming tool for all M68HC11 devices. The programmer features interchangeable adapters that allow programming of various M68HC11 package types.

Programmer features include:

- Programs M68HC11 Family devices that contain an EPROM or EEPROM array.

- Can be operated as a stand-alone programmer connected to a host computer or connected between a host computer and the M68HC11 modular development system (MMDS11) station module

- Uses plug-in programming adapters to accommodate a variety of MCU devices and packages

- On-board programming voltage circuit eliminates the need for an external 12-volt supply.

- Includes programming software and a user's manual

- Includes a +5-volt power cable and a DB9 to DB25 connector adapter

M68HC11E Family Data Sheet, Rev. 5.1

<sup>&</sup>lt;sup>®</sup> IBM is a registered trademark145 of International Business Machines Corporation.

**Development Support**

# Appendix B EVBU Schematic

Refer to Figure B-1 for a schematic diagram of the M68HC11EVBU Universal Evaluation Board. This diagram is included for reference only.

After the MCU sends \$FF [8], it enters the WAIT1 loop [9] and waits for the first data character from the host. When this character is received [10], the MCU programs it into the address pointed to by the Y index register. When the programming time delay is over, the MCU reads the programmed data, transmits it to the host for verification [11], and returns to the top of the WAIT1 loop to wait for the next data character [12]. Because the host previously sent the second data character, it is already waiting in the SCI receiver of the MCU. Steps [13], [14], and [15] correspond to the second pass through the WAIT1 loop.

Back in the host, the first verify character is received, and the third data character is sent [6]. The host then waits for the second verify character [7] to come back from the MCU. The sequence continues as long as the host continues to send data to the MCU. Since the WAIT1 loop in the PROGRAM utility is an indefinite loop, reset is used to end the process in the MCU after the host has finished sending data to be programmed.

# **Allowing for Bootstrap Mode**

Since bootstrap mode requires few connections to the MCU, it is easy to design systems that accommodate bootstrap mode.

Bootstrap mode is useful for diagnosing or repairing systems that have failed due to changes in the CONFIG register or failures of the expansion address/data buses, (rendering programs in external memory useless). Bootstrap mode can also be used to load information into the EPROM or EEPROM of an M68HC11 after final assembly of a module. Bootstrap mode is also useful for performing system checks and calibration routines. The following paragraphs explain system requirements for use of bootstrap mode in a product.

#### **Mode Select Pins**

It must be possible to force the MODA and MODB pins to logic 0, which implies that these two pins should be pulled up to  $V_{DD}$  through resistors rather than being tied directly to  $V_{DD}$ . If mode pins are connected directly to  $V_{DD}$ , it is not possible to force a mode other than the one the MCU is hard wired for. It is also good practice to use pulldown resistors to  $V_{SS}$  rather than connecting mode pins directly to  $V_{SS}$  because it is sometimes a useful debug aid to attempt reset in modes other than the one the system was primarily designed for. Physically, this requirement sometimes calls for the addition of a test point or a wire connected to one or both mode pins. Mode selection only uses the mode pins while RESET is active.

#### RESET

It must be possible to initiate a reset while the mode select pins are held low. In systems where there is no provision for manual reset, it is usually possible to generate a reset by turning power off and back on.

#### RxD Pin

It must be possible to drive the PD0/RxD pin with serial data from a host computer (or another MCU). In many systems, this pin is already used for SCI communications; thus no changes are required.

#### **Driving Boot Mode from a Personal Computer**

A problem arose with the BASIC programming technique used. The draft versions of this program tried saving the object code bytes directly as binary in a string array. This caused "Out of Memory" or "Out of String Space" errors on both a 2-Mbyte Macintosh and a 640-Kbyte PC. The solution was to make the array an integer array and perform the integer-to-binary conversion on each byte as it is sent to the target part.

The one compromise made to accommodate both Macintosh and PC versions of BASIC is in lines 1500 and 1505. Use line 1500 and comment out line 1505 if the program is to be run on a Macintosh, and, conversely, use line 1505 and comment out line 1500 if a PC is used.

After the COM port is opened, the code to be bootloaded is modified by adding the \$FF to the start of the string. \$FF synchronizes the bootloader in the MC68HC711E9 to 1200 baud. The entire string is simply sent to the COM port by PRINTing the string. This is possible since the string is actually queued in BASIC's COM buffer, and the operating system takes care of sending the bytes out one at a time. The M68HC11 echoes the data received for verification. No automatic verification is provided, though the data is printed to the screen for manual verification.

Once the MCU has received this bootloaded code, the bootloader automatically jumps to it. The small bootloaded program in turn includes a jump to the EPROM programming routine in the boot ROM.

Refer to the previous explanation of the EPROM Programming Utility for the following discussion. The host system sends the first byte to be programmed through the COM port to the SCI of the MCU. The SCI port on the MCU buffers one byte while receiving another byte, increasing the throughput of the EPROM programming operation by sending the second byte while the first is being programmed.

When the first byte has been programmed, the MCU reads the EPROM location and sends the result back to the host system. The host then compares what was actually programmed to what was originally sent. A message indicating which byte is being verified is displayed in the lower half of the screen. If there is an error, it is displayed at the top of the screen.

As soon as the first byte is verified, the third byte is sent. In the meantime, the MCU has already started programming the second byte. This process of verifying and queueing a byte continues until the host finishes sending data. If the programming is completely successful, no error messages will have been displayed at the top of the screen. Subroutines follow the end of the program to handle some of the repetitive tasks. These routines are short, and the commenting in the source code should be sufficient explanation.

#### **Modifications**

This example programmed version 3.4 of the BUFFALO monitor into the EPROM of an MC68HC711E9; the changes to the BASIC program to download some other program are minor.

The necessary changes are:

- In line 30, the length of the program to be downloaded must be assigned to the variable CODESIZE%.

- 2. Also in line 30, the starting address of the program is assigned to the variable ADRSTART.

- 3. In line 9570, the start address of the program is stored in the third and fourth items in that DATA statement in hexadecimal.

- 4. If any changes are made to the number of bytes in the boot code in the DATA statements in lines 9500–9580, then the new count must be set in the variable "BOOTCOUNT" in line 25.

#### **Driving Boot Mode from a Personal Computer**

## Operation

Configure the EVBU for boot mode operation by putting a jumper at J3. Ensure that the trace command jumper at J7 is not installed because this would connect the 12-V programming voltage to the OC5 output of the MCU.

Connect the EVBU to its dc power supply. When it is time to program the MCU EPROM, turn on the 12-volt programming power supply to the new circuitry in the wire-wrap area.

Connect the EVBU serial port to the appropriate serial port on the host system. For the Macintosh, this is the modem port with a modem cable. For the MS-DOS® computer, it is connected to COM1 with a straight through or modem cable. Power up the host system and start the BASIC program. If the program has not been compiled, this is accomplished from within the appropriate BASIC compiler or interpreter. Power up the EVBU.

Answer the prompt for filename with either a [RETURN] to accept the default shown or by typing in a new filename and pressing [RETURN].

The program will inform the user that it is working on converting the file from S records to binary. This process will take from 30 seconds to a few minutes, depending on the computer.

A prompt reading, "Comm port open?" will appear at the end of the file conversion. This is the last chance to ensure that everything is properly configured on the EVBU. Pressing [RETURN] will send the bootcode to the target MC68HC711E9. The program then informs the user that the bootload code is being sent to the target, and the results of the echoing of this code are displayed on the screen.

Another prompt reading "Programming is ready to begin. Are you?" will appear. Turn on the 12-volt programming power supply and press [RETURN] to start the actual programming of the target EPROM.

A count of the byte being verified will be updated continually on the screen as the programming progresses. Any failures will be flagged as they occur.

When programming is complete, a message will be displayed as well as a prompt requesting the user to press [RETURN] to quit.

Turn off the 12-volt programming power supply before turning off 5 volts to the EVBU.

<sup>&</sup>lt;sup>®</sup> MS-DOS is a registered trademark of Microsoft Corporation in the United States and oth175190er countries.

# **Listing 2. BASIC Program for Personal Computer**

```

3 1 *

E9BUF.BAS - A PROGRAM TO DEMONSTRATE THE USE OF THE BOOT MODE

ON THE HC11 BY PROGRAMMING AN HC711E9 WITH

5

BUFFALO 3.4

7 ' *

REQUIRES THAT THE S-RECORDS FOR BUFFALO (BUF34.S19)

8 ' *

BE AVAILABLE IN THE SAME DIRECTORY OR FOLDER

9 ' *

10 '*

THIS PROGRAM HAS BEEN RUN BOTH ON A MS-DOS COMPUTER

11 '*

USING QUICKBASIC 4.5 AND ON A MACINTOSH USING

12 '*

QUICKBASIC 1.0.

14 '*

25 H$ = "0123456789ABCDEF"

'STRING TO USE FOR HEX CONVERSIONS

30 DEFINT B, I: CODESIZE% = 8192: ADRSTART= 57344!

35 BOOTCOUNT = 25

'NUMBER OF BYTES IN BOOT CODE

'BUFFALO 3.4 IS 8K BYTES LONG

40 DIM CODE% (CODESIZE%)

45 BOOTCODE$ = ""

'INITIALIZE BOOTCODE$ TO NULL

49 REM **** READ IN AND SAVE THE CODE TO BE BOOT LOADED *****

'# OF BYTES IN BOOT CODE

50 FOR I = 1 TO BOOTCOUNT

55 READ Q$

60 A$ = MID$(Q$, 1, 1)

65 GOSUB 7000

'CONVERTS HEX DIGIT TO DECIMAL

70 \text{ TEMP} = 16 * X

'HANG ON TO UPPER DIGIT

75 A$ = MID$(Q$, 2, 1)

80 GOSUB 7000

85 \text{ TEMP} = \text{TEMP} + X

90 BOOTCODE$ = BOOTCODE$ + CHR$ (TEMP)

'BUILD BOOT CODE

95 NEXT I

96 REM **** S-RECORD CONVERSION STARTS HERE *****

97 FILNAMS="BUF34.S19"

'DEFAULT FILE NAME FOR S-RECORDS

100 CLS

105 PRINT "Filename.ext of S-record file to be downloaded (";FILNAM$;") ";

107 INPUT Q$

110 IF Q$<>"" THEN FILNAM$=Q$

120 OPEN FILNAM$ FOR INPUT AS #1

130 PRINT : PRINT "Converting "; FILNAM$; " to binary..."

999 REM ***** SCANS FOR 'S1' RECORDS *****

1000 GOSUB 6000

'GET 1 CHARACTER FROM INPUT FILE

1010 IF FLAG THEN 1250

'FLAG IS EOF FLAG FROM SUBROUTINE

1020 IF A$ <> "S" THEN 1000

1022 GOSUB 6000

1024 IF A$ <> "1" THEN 1000

1029 REM ***** S1 RECORD FOUND, NEXT 2 HEX DIGITS ARE THE BYTE COUNT *****

1030 GOSUB 6000

1040 GOSUB 7000

'RETURNS DECIMAL IN X

1050 BYTECOUNT = 16 * X

'ADJUST FOR HIGH NIBBLE

1060 GOSUB 6000

1070 GOSUB 7000

1080 BYTECOUNT = BYTECOUNT + X 'ADD LOW NIBBLE

```

#### M68HC11 Bootstrap Mode, Rev. 1.1

#### Listing 3. MC68HC711E9 Bootloader ROM

```

213

************

214

215

* Boot ROM revision level in ASCII

216

(ORG

$BFD1)

FCC

"A"

217 BFD1 41

************

218

219

* Mask set I.D. ($0000 FOR EPROM PARTS)

220

(ORG

$BFD2)

221 BFD2 0000

FDB

$0000

222

'711E9 I.D. - Can be used to determine MCU type

223

224

(ORG

$BFD4)

225 BFD4 71E9

FDB

$71E9

226

************

227

228

* VECTORS - point to RAM for pseudo-vector JUMPs

229

230 BFD6 00C4

FDB

$100-60

SCI

231 BFD8 00C7

FDB

$100-57

SPI

232 BFDA 00CA

PULSE ACCUM INPUT EDGE

$100-54

FDB

233 BFDC 00CD

FDB

$100-51

PULSE ACCUM OVERFLOW

234 BFDE 00D0

FDB

$100-48

TIMER OVERFLOW

235 BFE0 00D3

FDB

$100-45

TIMER OUTPUT COMPARE 5

236 BFE2 00D6

$100-42

TIMER OUTPUT COMPARE

FDB

237 BFE4 00D9

FDB

$100-39

TIMER OUTPUT COMPARE

238 BFE6 00DC

FDB

TIMER OUTPUT COMPARE 2

$100-36

239 BFE8 00DF

FDB

$100-33

TIMER OUTPUT COMPARE 1

240 BFEA 00E2

FDB

$100-30

TIMER INPUT CAPTURE 3

241 BFEC 00E5

FDB

$100-27

TIMER INPUT CAPTURE 2

242 BFEE 00E8

FDB

$100-24

TIMER INPUT CAPTURE 1

243 BFF0 00EB

FDB

$100-21

REAL TIME INT

244 BFF2 00EE

FDB

$100-18

IRQ

245 BFF4 00F1

FDB

$100-15

XIRO

246 BFF6 00F4

FDB

SWI

$100-12

247 BFF8 00F7

FDB

$100-9

ILLEGAL OP-CODE

248 BFFA 00FA

FDB

$100-6

COP FAIL

249 BFFC 00FD

CLOCK MONITOR

FDB

$100-3

250 BFFE BF54

FDB

BEGIN

RESET

251 C000

END

Symbol Table:

Value Def.# Line Number Cross Reference

Symbol Name

BAUD

002B *00037

00160 00180

BAUDOK

BF8A *00183

00178

BEGIN

BF54 *00155

00250

DELAYF

021B *00061

00163

0DB0 *00060

00181

DELAYS

DONEIT

BF47 *00142

00124

EEPMEND

B7FF *00050

B600 *00049 00175

EEPMSTR

ELAT

0020 *00043

00125 00128

EPGM

0001 *00044

00128

EPRMEND

FFFF *00053

EPRMSTR

D000 *00052

00206

```

#### M68HC11 Bootstrap Mode, Rev. 1.1