Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                             |

|----------------------------|-------------------------------------------------------------|

| Product Status             | Obsolete                                                    |

| Core Processor             | HC11                                                        |

| Core Size                  | 8-Bit                                                       |

| Speed                      | 2MHz                                                        |

| Connectivity               | SCI, SPI                                                    |

| Peripherals                | POR, WDT                                                    |

| Number of I/O              | 38                                                          |

| Program Memory Size        | 12KB (12K x 8)                                              |

| Program Memory Type        | OTP                                                         |

| EEPROM Size                | 512 x 8                                                     |

| RAM Size                   | 512 x 8                                                     |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                   |

| Data Converters            | A/D 8x8b                                                    |

| Oscillator Type            | Internal                                                    |

| Operating Temperature      | 0°C ~ 70°C (TA)                                             |

| Mounting Type              | Surface Mount                                               |

| Package / Case             | 52-LCC (J-Lead)                                             |

| Supplier Device Package    | 52-PLCC (19.13x19.13)                                       |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mc68l711e9fne2 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## MC68HC11E Family

#### **Data Sheet**

To provide the most up-to-date information, the revision of our documents on the World Wide Web will be the most current. Your printed copy may be an earlier revision. To verify you have the latest information available, refer to:

http://freescale.com/

The following revision history table summarizes changes contained in this document. For your convenience, the page number designators have been linked to the appropriate location.

Freescale™ and the Freescale logo are trademarks of Freescale Semiconductor, Inc. © Freescale Semiconductor, Inc., 2005. All rights reserved.

#### **Table of Contents**

| 2.4.3   | EPROM and EEPROM Programming Control Register |    |

|---------|-----------------------------------------------|----|

| 2.5     | EEPROM                                        |    |

| 2.5.1   | EEPROM and CONFIG Programming and Erasure     |    |

| 2.5.1.1 | Block Protect Register                        |    |

| 2.5.1.2 | 3 3 - 3 - 3 - 3 - 3 - 3 - 3 - 3 - 3           |    |

| 2.5.1.3 | EEPROM Bulk Erase                             | 54 |

| 2.5.1.4 | EEPROM Row Erase                              | 54 |

| 2.5.1.5 | EEPROM Byte Erase                             | 55 |

| 2.5.1.6 | CONFIG Register Programming                   | 55 |

| 2.5.2   | EEPROM Security                               | 55 |

|         | Chapter 3                                     |    |

|         | Analog-to-Digital (A/D) Converter             |    |

| 3.1     | Introduction                                  |    |

| 3.2     | Overview                                      |    |

| 3.2.1   | Multiplexer                                   | 57 |

| 3.2.2   | Analog Converter                              | 57 |

| 3.2.3   | Digital Control                               | 59 |

| 3.2.4   | Result Registers                              | 59 |

| 3.2.5   | A/D Converter Clocks                          | 59 |

| 3.2.6   | Conversion Sequence                           | 59 |

| 3.3     | A/D Converter Power-Up and Clock Select       | 60 |

| 3.4     | Conversion Process                            |    |

| 3.5     | Channel Assignments                           |    |

| 3.6     | Single-Channel Operation                      |    |

| 3.7     | Multiple-Channel Operation                    |    |

| 3.8     | Operation in Stop and Wait Modes              |    |

|         |                                               |    |

|         | A/D Control/Status Register                   |    |

| 3.10    | A/D Converter Result Registers                | 64 |

|         | Chapter 4                                     |    |

|         | Central Processor Unit (CPU)                  |    |

| 4.1     | Introduction                                  |    |

| 4.2     | CPU Registers                                 |    |

| 4.2.1   | Accumulators A, B, and D                      |    |

| 4.2.2   | Index Register X (IX)                         |    |

| 4.2.3   | Index Register Y (IY)                         |    |

| 4.2.4   | Stack Pointer (SP)                            |    |

| 4.2.5   | Program Counter (PC)                          |    |

| 4.2.6   | Condition Code Register (CCR)                 |    |

| 4.2.6.1 | Carry/Borrow (C)                              |    |

| 4.2.6.2 |                                               |    |

| 4.2.6.3 |                                               |    |

| 4.2.6.4 |                                               |    |

| 4.2.6.5 |                                               |    |

| 4.2.6.6 |                                               |    |

| 4.2.6.7 |                                               |    |

| 4.2.6.8 | STOP Disable (S)                              | 69 |

M68HC11E Family Data Sheet, Rev. 5.1

#### **General Description**

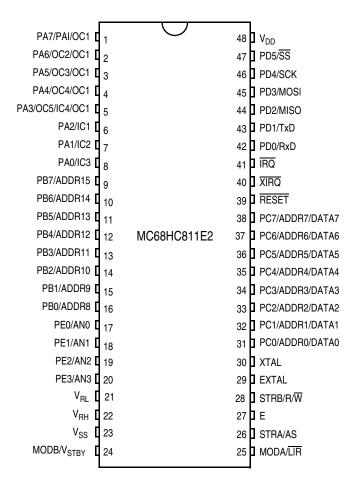

Figure 1-6. Pin Assignments for 48-Pin DIP (MC68HC811E2)

#### **General Description**

#### NOTE

IRQ must be configured for level-sensitive operation if there is more than one source of IRQ interrupt.

There should be a single pullup resistor near the MCU interrupt input pin (typically 4.7  $k\Omega$ ). There must also be an interlock mechanism at each interrupt source so that the source holds the interrupt line low until the MCU recognizes and acknowledges the interrupt request. If one or more interrupt sources are still pending after the MCU services a request, the interrupt line will still be held low and the MCU will be interrupted again as soon as the interrupt mask bit in the MCU is cleared (normally upon return from an interrupt). Refer to Chapter 5 Resets and Interrupts.

V<sub>PPE</sub> is the input for the 12-volt nominal programming voltage required for EPROM/OTPROM programming. On devices without EPROM/OTPROM, this pin is only an XIRQ input.

#### **CAUTION**

During EPROM programming of the MC68HC711E9 device, the V<sub>PPE</sub> pin circuitry may latch-up and be damaged if the input current is not limited to 10 mA. For more information please refer to MC68HC711E9 8-Bit Microcontroller Unit Mask Set Errata 3 (Freescale document order number 68HC711E9MSE3.

## 1.4.7 MODA and MODB (MODA/LIR and MODB/V<sub>STBY</sub>)

During reset, MODA and MODB select one of the four operating modes:

- Single-chip mode

- Expanded mode

- Test mode

- Bootstrap mode

Refer to Chapter 2 Operating Modes and On-Chip Memory.

After the operating mode has been selected, the load instruction register (LIR) pin provides an open-drain output to indicate that execution of an instruction has begun. A series of E-clock cycles occurs during execution of each instruction. The LIR signal goes low during the first E-clock cycle of each instruction (opcode fetch). This output is provided for assistance in program debugging.

The  $V_{STBY}$  pin is used to input random-access memory (RAM) standby power. When the voltage on this pin is more than one MOS threshold (about 0.7 volts) above the  $V_{DD}$  voltage, the internal RAM and part of the reset logic are powered from this signal rather than the  $V_{DD}$  input. This allows RAM contents to be retained without  $V_{DD}$  power applied to the MCU. Reset must be driven low before  $V_{DD}$  is removed and must remain low until  $V_{DD}$  has been restored to a valid level.

#### 1.4.8 $V_{RI}$ and $V_{RH}$

These two inputs provide the reference voltages for the analog-to-digital (A/D) converter circuitry:

- V<sub>RL</sub> is the low reference, typically 0 Vdc.

- V<sub>RH</sub> is the high reference.

For proper A/D converter operation:

- V<sub>RH</sub> should be at least 3 Vdc greater than V<sub>RI</sub>.

- V<sub>RL</sub> and V<sub>RH</sub> should be between V<sub>SS</sub> and V<sub>DD</sub>.

M68HC11E Family Data Sheet, Rev. 5.1

Table 2-4. RAM Mapping

| rabic 2 4. HAIII iliapping |               |  |  |  |  |

|----------------------------|---------------|--|--|--|--|

| RAM[3:0]                   | Address       |  |  |  |  |

| 0000                       | \$0000-\$0xFF |  |  |  |  |

| 0001                       | \$1000-\$1xFF |  |  |  |  |

| 0010                       | \$2000-\$2xFF |  |  |  |  |

| 0011                       | \$3000-\$3xFF |  |  |  |  |

| 0100                       | \$4000-\$4xFF |  |  |  |  |

| 0101                       | \$5000-\$5xFF |  |  |  |  |

| 0110                       | \$6000-\$6xFF |  |  |  |  |

| 0111                       | \$7000-\$7xFF |  |  |  |  |

| 1000                       | \$8000-\$8xFF |  |  |  |  |

| 1001                       | \$9000-\$9xFF |  |  |  |  |

| 1010                       | \$A000-\$AxFF |  |  |  |  |

| 1011                       | \$B000-\$BxFF |  |  |  |  |

| 1100                       | \$C000-\$CxFF |  |  |  |  |

| 1101                       | \$D000-\$DxFF |  |  |  |  |

| 1110                       | \$E000-\$ExFF |  |  |  |  |

| 1111                       | \$F000-\$FxFF |  |  |  |  |

|                            |               |  |  |  |  |

Table 2-5. Register Mapping

| REG[3:0] | Address       |

|----------|---------------|

| 0000     | \$0000-\$003F |

| 0001     | \$1000-\$103F |

| 0010     | \$2000-\$203F |

| 0011     | \$3000-\$303F |

| 0100     | \$4000-\$403F |

| 0101     | \$5000-\$503F |

| 0110     | \$6000-\$603F |

| 0111     | \$7000-\$703F |

| 1000     | \$8000-\$803F |

| 1001     | \$9000-\$903F |

| 1010     | \$A000-\$A03F |

| 1011     | \$B000-\$B03F |

| 1100     | \$C000-\$C03F |

| 1101     | \$D000-\$D03F |

| 1110     | \$E000-\$E03F |

| 1111     | \$F000-\$F03F |

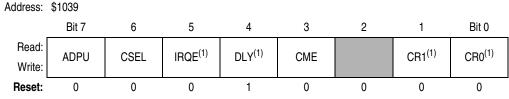

#### 2.3.3.3 System Configuration Options Register

The 8-bit, special-purpose system configuration options register (OPTION) sets internal system configuration options during initialization. The time protected control bits, IRQE, DLY, and CR[1:0], can be written only once after a reset and then they become read-only. This minimizes the possibility of any accidental changes to the system configuration.

Can be written only once in first 64 cycles out of reset in normal modes or at any time during special modes.

= Unimplemented

Figure 2-13. System Configuration Options Register (OPTION)

#### ADPU — Analog-to-Digital Converter Power-Up Bit

Refer to Chapter 3 Analog-to-Digital (A/D) Converter.

#### **CSEL** — Clock Select Bit

Selects alternate clock source for on-chip EEPROM charge pump. Refer to 2.5.1 EEPROM and CONFIG Programming and Erasure for more information on EEPROM use.

CSEL also selects the clock source for the A/D converter, a function discussed in Chapter 3 Analog-to-Digital (A/D) Converter.

M68HC11E Family Data Sheet, Rev. 5.1

# Chapter 3 Analog-to-Digital (A/D) Converter

#### 3.1 Introduction

The analog-to-digital (A/D) system, a successive approximation converter, uses an all-capacitive charge redistribution technique to convert analog signals to digital values.

#### 3.2 Overview

The A/D system is an 8-channel, 8-bit, multiplexed-input converter. The converter does not require external sample and hold circuits because of the type of charge redistribution technique used. A/D converter timing can be synchronized to the system E clock or to an internal resistor capacitor (RC) oscillator.

The A/D converter system consists of four functional blocks: multiplexer, analog converter, digital control, and result storage. Refer to Figure 3-1.

#### 3.2.1 Multiplexer

The multiplexer selects one of 16 inputs for conversion. Input selection is controlled by the value of bits CD:CA in the ADCTL register. The eight port E pins are fixed-direction analog inputs to the multiplexer, and additional internal analog signal lines are routed to it.

Port E pins also can be used as digital inputs. Digital reads of port E pins are not recommended during the sample portion of an A/D conversion cycle, when the gate signal to the N-channel input gate is on. Because no P-channel devices are directly connected to either input pins or reference voltage pins, voltages above V<sub>DD</sub> do not cause a latchup problem, although current should be limited according to maximum ratings. Refer to Figure 3-2, which is a functional diagram of an input pin.

#### 3.2.2 Analog Converter

Conversion of an analog input selected by the multiplexer occurs in this block. It contains a digital-to-analog capacitor (DAC) array, a comparator, and a successive approximation register (SAR). Each conversion is a sequence of eight comparison operations, beginning with the most significant bit (MSB). Each comparison determines the value of a bit in the successive approximation register.

The DAC array performs two functions. It acts as a sample and hold circuit during the entire conversion sequence and provides comparison voltage to the comparator during each successive comparison.

The result of each successive comparison is stored in the SAR. When a conversion sequence is complete, the contents of the SAR are transferred to the appropriate result register.

A charge pump provides switching voltage to the gates of analog switches in the multiplexer. Charge pump output must stabilize between 7 and 8 volts within up to  $100 \,\mu s$  before the converter can be used. The charge pump is enabled by the ADPU bit in the OPTION register.

## Table 4-2. Instruction Set (Sheet 2 of 7)

| Magazza                      | Omenation                                     | Addressing Instruction    |                                               |                               | Condition Codes         |                       |   |   |   |   |   |   |   |   |

|------------------------------|-----------------------------------------------|---------------------------|-----------------------------------------------|-------------------------------|-------------------------|-----------------------|---|---|---|---|---|---|---|---|

| Mnemonic                     | Operation                                     | Description               | Mode                                          | Opcode                        | Operand                 | Cycles                | S | Х | Н | ı | N | Z | ٧ | С |

| BGT (rel)                    | Branch if > Zero                              | ? Z + (N ⊕ V) = 0         | REL                                           | 2E                            | rr                      | 3                     | _ | _ | _ | _ | _ | _ | _ | _ |

| BHI (rel)                    | Branch if<br>Higher                           | ? C + Z = 0               | REL                                           | 22                            | rr                      | 3                     | _ | _ | _ | _ | _ | _ |   | _ |

| BHS (rel)                    | Branch if<br>Higher or Same                   | ? C = 0                   | REL                                           | 24                            | rr                      | 3                     | _ | _ | _ | _ | _ | _ | _ | _ |

| BITA (opr)                   | Bit(s) Test A<br>with Memory                  | A • M                     | A IMM<br>A DIR<br>A EXT<br>A IND,X<br>A IND,Y | 85<br>95<br>B5<br>A5<br>18 A5 | ii<br>dd<br>hh ll<br>ff | 2<br>3<br>4<br>4<br>5 | _ | _ | _ | _ | Δ | Δ | 0 | _ |

| BITB (opr)                   | Bit(s) Test B<br>with Memory                  | B • M                     | B IMM B DIR B EXT B IND,X B IND,Y             | C5<br>D5<br>F5<br>E5          | ii<br>dd<br>hh 11<br>ff | 2<br>3<br>4<br>4<br>5 | _ | _ | _ | _ | Δ | Δ | 0 | _ |

| BLE (rel)                    | Branch if $\Delta$ Zero                       | ? Z + (N ⊕ V) = 1         | REL                                           | 2F                            | rr                      | 3                     | _ | _ | _ | _ | _ | _ | _ | _ |

| BLO (rel)                    | Branch if Lower<br>Branch if Lower<br>or Same | ? C = 1<br>? C + Z = 1    | REL<br>REL                                    | 25<br>23                      | rr                      | 3                     | _ | = | _ | = | _ | _ | = |   |

| BLT (rel)                    | Branch if < Zero                              | ? N ⊕ V = 1               | REL                                           | 2D                            | rr                      | 3                     | _ | _ | _ | _ | _ | _ | _ | _ |

| BMI (rel)                    | Branch if Minus                               | ? N = 1                   | REL                                           | 2B                            | rr                      | 3                     | _ | _ | _ | _ | _ | _ | _ | _ |

| BNE (rel)                    | Branch if not = Zero                          | ? Z = 0                   | REL                                           | 26                            | rr                      | 3                     | _ | _ | _ | _ | _ | _ |   | _ |

| BPL (rel)                    | Branch if Plus                                | ? N = 0                   | REL                                           | 2A                            | rr                      | 3                     | _ | _ | _ | _ | _ | _ | _ | _ |

| BRA (rel)                    | Branch Always                                 | ? 1 = 1                   | REL                                           | 20                            | rr                      | 3                     | _ | _ | _ | _ | _ | _ | _ | _ |

| BRCLR(opr)<br>(msk)<br>(rel) | Branch if<br>Bit(s) Clear                     | ? M • mm = 0              | DIR<br>IND,X<br>IND,Y                         | 13<br>1F<br>18 1F             | dd mm rr ff mm rr ff mm | 6<br>7<br>8           | _ | _ | _ | _ | _ | _ | _ |   |

| BRN (rel)                    | Branch Never                                  | ? 1 = 0                   | REL                                           | 21                            | rr                      | 3                     | _ | _ | _ | _ | _ | _ | _ | _ |

| BRSET(opr)<br>(msk)<br>(rel) | Branch if Bit(s)<br>Set                       | ? (M) • mm = 0            | DIR<br>IND,X<br>IND,Y                         | 12<br>1E<br>18 1E             | dd mm rr ff mm rr ff mm | 6<br>7<br>8           | _ | _ | _ | _ | _ | _ | _ | _ |

| BSET (opr)<br>(msk)          | Set Bit(s)  Branch to                         | M + mm ⇒ M See Figure 3–2 | DIR<br>IND,X<br>IND,Y<br>REL                  | 14<br>1C<br>18 1C             | dd mm<br>ff mm<br>ff mm | 6<br>7<br>8<br>6      | _ | _ | _ | _ | Δ | Δ | 0 | _ |

| BVC (rel)                    | Subroutine<br>Branch if                       | ? V = 0                   | REL                                           | 28                            |                         | 3                     |   |   |   |   |   |   |   |   |

| , ,                          | Overflow Clear                                |                           |                                               |                               | rr                      |                       |   |   |   |   |   |   |   |   |

| BVS (rel)                    | Branch if<br>Overflow Set                     | ? V = 1                   | REL                                           | 29                            | rr                      | 3                     | _ |   |   |   | _ |   |   |   |

| CBA                          | Compare A to B                                | A – B                     | INH                                           | 11                            | _                       | 2                     | _ | _ | _ | _ | Δ | Δ | Δ | Δ |

| CLC                          | Clear Carry Bit                               | 0 ⇒ C                     | INH                                           | 0C                            | _                       | 2                     | _ | _ | _ | _ | _ | _ | _ | 0 |

| CLI                          | Clear Interrupt<br>Mask                       | 0 ⇒ I                     | INH                                           | 0E                            | _                       | 2                     |   | _ |   | 0 |   |   |   |   |

| CLR (opr)                    | Clear Memory<br>Byte                          | $0 \Rightarrow M$         | EXT<br>IND,X<br>IND,Y                         | 7F<br>6F<br>18 6F             | hh 11<br>ff<br>ff       | 6<br>6<br>7           | _ | _ | _ | _ | 0 | 1 | 0 | 0 |

| CLRA                         | Clear<br>Accumulator A                        | $0 \Rightarrow A$         | A INH                                         | 4F                            | _                       | 2                     | _ | _ | _ | _ | 0 | 1 | 0 | 0 |

| CLRB                         | Clear<br>Accumulator B                        | $0 \Rightarrow B$         | B INH                                         | 5F                            | _                       | 2                     | _ | _ | _ | _ | 0 | 1 | 0 | 0 |

| CLV                          | Clear Overflow<br>Flag                        | 0 ⇒ V                     | INH                                           | 0A                            | _                       | 2                     | _ | - | _ | - | _ | _ | 0 | _ |

| CMPA (opr)                   | Compare A to<br>Memory                        | A – M                     | A IMM A DIR A EXT A IND,X A IND,Y             | 81<br>91<br>B1<br>A1<br>18 A1 | ii<br>dd<br>hh ll<br>ff | 2<br>3<br>4<br>4<br>5 | _ | _ | _ | _ | Δ | Δ | Δ | Δ |

#### **Resets and Interrupts**

#### 5.3.2 Memory Map

After reset, the INIT register is initialized to \$01, mapping the RAM at \$00 and the control registers at \$1000.

For the MC68HC811E2, the CONFIG register resets to \$FF. EEPROM mapping bits (EE[3:0]) place the EEPROM at \$F800. Refer to the memory map diagram for MC68HC811E2 in Chapter 2 Operating Modes and On-Chip Memory.

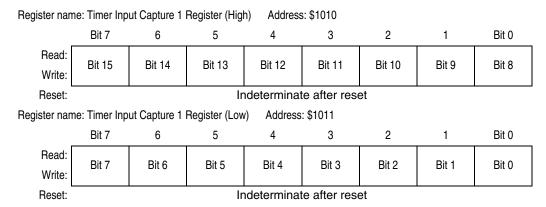

#### 5.3.3 Timer

During reset, the timer system is initialized to a count of \$0000. The prescaler bits are cleared, and all output compare registers are initialized to \$FFFF. All input capture registers are indeterminate after reset. The output compare 1 mask (OC1M) register is cleared so that successful OC1 compares do not affect any I/O pins. The other four output compares are configured so that they do not affect any I/O pins on successful compares. All input capture edge-detector circuits are configured for capture disabled operation. The timer overflow interrupt flag and all eight timer function interrupt flags are cleared. All nine timer interrupts are disabled because their mask bits have been cleared.

The I4/O5 bit in the PACTL register is cleared to configure the I4/O5 function as OC5; however, the OM5:OL5 control bits in the TCTL1 register are clear so OC5 does not control the PA3 pin.

#### 5.3.4 Real-Time Interrupt (RTI)

The real-time interrupt flag (RTIF) is cleared and automatic hardware interrupts are masked. The rate control bits are cleared after reset and can be initialized by software before the real-time interrupt (RTI) system is used.

#### 5.3.5 Pulse Accumulator

The pulse accumulator system is disabled at reset so that the pulse accumulator input (PAI) pin defaults to being a general-purpose input pin.

#### 5.3.6 Computer Operating Properly (COP)

The COP watchdog system is enabled if the NOCOP control bit in the CONFIG register is cleared and disabled if NOCOP is set. The COP rate is set for the shortest duration timeout.

#### 5.3.7 Serial Communications Interface (SCI)

The reset condition of the SCI system is independent of the operating mode. At reset, the SCI baud rate control register (BAUD) is initialized to \$04. All transmit and receive interrupts are masked and both the transmitter and receiver are disabled so the port pins default to being general-purpose I/O lines. The SCI frame format is initialized to an 8-bit character size. The send break and receiver wakeup functions are disabled. The TDRE and TC status bits in the SCI status register (SCSR) are both 1s, indicating that there is no transmit data in either the transmit data register or the transmit serial shift register. The RDRF, IDLE, OR, NF, FE, PF, and RAF receive-related status bits in the SCI control register 2 (SCCR2) are cleared.

#### 5.3.8 Serial Peripheral Interface (SPI)

The SPI system is disabled by reset. The port pins associated with this function default to being general-purpose I/O lines.

#### 5.3.9 Analog-to-Digital (A/D) Converter

The analog-to-digital (A/D) converter configuration is indeterminate after reset. The ADPU bit is cleared by reset, which disables the A/D system. The conversion complete flag is indeterminate.

#### 5.3.10 System

The EEPROM programming controls are disabled, so the memory system is configured for normal read operation. PSEL[3:0] are initialized with the value %0110, causing the external  $\overline{IRQ}$  pin to have the highest I-bit interrupt priority. The  $\overline{IRQ}$  pin is configured for level-sensitive operation (for wired-OR systems). The RBOOT, SMOD, and MDA bits in the HPRIO register reflect the status of the MODB and MODA inputs at the rising edge of reset. MODA and MODB inputs select one of the four operating modes. After reset, writing SMOD and MDA in special modes causes the MCU to change operating modes. Refer to the description of HPRIO register in Chapter 2 Operating Modes and On-Chip Memory for a detailed description of SMOD and MDA. The DLY control bit is set to specify that an oscillator startup delay is imposed upon recovery from stop mode. The clock monitor system is disabled because CME is cleared.

#### 5.4 Reset and Interrupt Priority

Resets and interrupts have a hardware priority that determines which reset or interrupt is serviced first when simultaneous requests occur. Any maskable interrupt can be given priority over other maskable interrupts.

The first six interrupt sources are not maskable. The priority arrangement for these sources is:

- 1. POR or RESET pin

- 2. Clock monitor reset

- 3. COP watchdog reset

- 4. XIRQ interrupt

- 5. Illegal opcode interrupt

- 6. Software interrupt (SWI)

The maskable interrupt sources have this priority arrangement:

- 1. IRQ

- 2. Real-time interrupt

- 3. Timer input capture 1

- 4. Timer input capture 2

- Timer input capture 3

- Timer output compare 1

- 7. Timer output compare 2

- 8. Timer output compare 3

- 9. Timer output compare 4

- 10. Timer input capture 4/output compare 5

- 11. Timer overflow

- 12. Pulse accumulator overflow

- Pulse accumulator input edge

- 14. SPI transfer complete

- 15. SCI system (refer to Figure 5-7)

#### CWOM — Port C Wired-OR Mode Bit (affects all eight port C pins)

It is customary to have an external pullup resistor on lines that are driven by open-drain devices.

- 0 = Port C outputs are normal CMOS outputs.

- 1 = Port C outputs are open-drain outputs.

#### **HNDS** — Handshake Mode Bit

- 0 = Simple strobe mode

- 1 = Full input or output handshake mode

#### OIN — Output or Input Handshake Select Bit

HNDS must be set to 1 for this bit to have meaning.

- 0 = Input handshake

- 1 = Output handshake

#### PLS — Pulsed/Interlocked Handshake Operation Bit

HNDS must be set to 1 for this bit to have meaning. When interlocked handshake is selected, strobe B is active until the selected edge of strobe A is detected.

- 0 = Interlocked handshake

- 1 = Pulsed handshake (Strobe B pulses high for two E-clock cycles.)

#### EGA — Active Edge for Strobe A Bit

- 0 = STRA falling edge selected, high level activates port C outputs (output handshake)

- 1 = STRA rising edge selected, low level activates port C outputs (output handshake)

#### **INVB** — Invert Strobe B Bit

- 0 = Active level is logic 0.

- 1 = Active level is logic 1.

**Serial Communications Interface (SCI)**

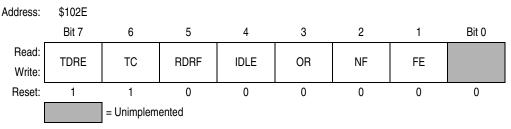

#### 7.7.4 Serial Communication Status Register

The SCSR provides inputs to the interrupt logic circuits for generation of the SCI system interrupt.

Figure 7-6. Serial Communications Status Register (SCSR)

#### **TDRE** — Transmit Data Register Empty Flag

This flag is set when SCDR is empty. Clear the TDRE flag by reading SCSR with TDRE set and then writing to SCDR.

0 = SCDR busy

0 = SCDR empty

#### TC — Transmit Complete Flag

This flag is set when the transmitter is idle (no data, preamble, or break transmission in progress). Clear the TC flag by reading SCSR with TC set and then writing to SCDR.

0 = Transmitter busy

1 = Transmitter idle

#### RDRF — Receive Data Register Full Flag

This flag is set if a received character is ready to be read from SCDR. Clear the RDRF flag by reading SCSR with RDRF set and then reading SCDR.

0 = SCDR empty

1 = SCDR full

#### IDLE — Idle Line Detected Flag

This flag is set if the RxD line is idle. Once cleared, IDLE is not set again until the RxD line has been active and becomes idle again. The IDLE flag is inhibited when RWU = 1. Clear IDLE by reading SCSR with IDLE set and then reading SCDR.

0 = RxD line active

1 = RxD line idle

#### OR — Overrun Error Flag

OR is set if a new character is received before a previously received character is read from SCDR. Clear the OR flag by reading SCSR with OR set and then reading SCDR.

0 = No overrun

1 = Overrun detected

#### NF — Noise Error Flag

NF is set if majority sample logic detects anything other than a unanimous decision. Clear NF by reading SCSR with NF set and then reading SCDR.

0 = Unanimous decision

1 = Noise detected

Serial Peripheral Interface (SPI)

#### 8.5.3 Serial Clock

SCK, an input to a slave device, is generated by the master device and synchronizes data movement in and out of the device through the MOSI and MISO lines. Master and slave devices are capable of exchanging a byte of information during a sequence of eight clock cycles.

Four possible timing relationships can be chosen by using control bits CPOL and CPHA in the serial peripheral control register (SPCR). Both master and slave devices must operate with the same timing. The SPI clock rate select bits, SPR[1:0], in the SPCR of the master device, select the clock rate. In a slave device, SPR[1:0] have no effect on the operation of the SPI.

#### 8.5.4 Slave Select

The slave select  $(\overline{SS})$  input of a slave device must be externally asserted before a master device can exchange data with the slave device.  $\overline{SS}$  must be low before data transactions and must stay low for the duration of the transaction.

The  $\overline{SS}$  line of the master must be held high. If it goes low, a mode fault error flag (MODF) is set in the serial peripheral status register (SPSR). To disable the mode fault circuit, write a 1 in bit 5 of the port D data direction register. This sets the  $\overline{SS}$  pin to act as a general-purpose output rather than the dedicated input to the slave select circuit, thus inhibiting the mode fault flag. The other three lines are dedicated to the SPI whenever the serial peripheral interface is on.

The state of the master and slave CPHA bits affects the operation of  $\overline{SS}$ . CPHA settings should be identical for master and slave. When CPHA = 0, the shift clock is the OR of  $\overline{SS}$  with SCK. In this clock phase mode,  $\overline{SS}$  must go high between successive characters in an SPI message. When CPHA = 1,  $\overline{SS}$  can be left low between successive SPI characters. In cases where there is only one SPI slave MCU, its  $\overline{SS}$  line can be tied to  $V_{SS}$  as long as only CPHA = 1 clock mode is used.

## 8.6 SPI System Errors

Two system errors can be detected by the SPI system. The first type of error arises in a multiple-master system when more than one SPI device simultaneously tries to be a master. This error is called a mode fault. The second type of error, write collision, indicates that an attempt was made to write data to the SPDR while a transfer was in progress.

When the SPI system is configured as a master and the  $\overline{SS}$  input line goes to active low, a mode fault error has occurred — usually because two devices have attempted to act as master at the same time. In cases where more than one device is concurrently configured as a master, there is a chance of contention between two pin drivers. For push-pull CMOS drivers, this contention can cause permanent damage. The mode fault mechanism attempts to protect the device by disabling the drivers. The MSTR control bit in the SPCR and all four DDRD control bits associated with the SPI are cleared and an interrupt is generated subject to masking by the SPIE control bit and the I bit in the CCR.

Other precautions may need to be taken to prevent driver damage. If two devices are made masters at the same time, mode fault does not help protect either one unless one of them selects the other as slave. The amount of damage possible depends on the length of time both devices attempt to act as master.

A write collision error occurs if the SPDR is written while a transfer is in progress. Because the SPDR is not double buffered in the transmit direction, writes to SPDR cause data to be written directly into the SPI shift register. Because this write corrupts any transfer in progress, a write collision error is generated. The transfer continues undisturbed, and the write data that caused the error is not written to the shifter.

#### **Timing Systems**

input capture register pair inhibits a new capture transfer for one bus cycle. If a double-byte read instruction, such as load double accumulator D (LDD), is used to read the captured value, coherency is assured. When a new input capture occurs immediately after a high-order byte read, transfer is delayed for an additional cycle but the value is not lost.

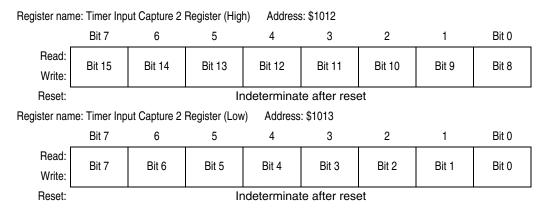

Figure 9-4. Timer Input Capture 1 Register Pair (TIC1)

Figure 9-5. Timer Input Capture 2 Register Pair (TIC2)

Figure 9-6. Timer Input Capture 3 Register Pair (TIC3)

M68HC11E Family Data Sheet, Rev. 5.1

#### **Ordering Information and Mechanical Specifications**

| Description                                | Temperature                     | Frequency | MC Order Number |  |  |  |  |  |  |  |

|--------------------------------------------|---------------------------------|-----------|-----------------|--|--|--|--|--|--|--|

|                                            | 0°C to +70°°C                   | 3 MHz     | MC68HC11E20FN3  |  |  |  |  |  |  |  |

| 20 Kbytes custom ROM                       | -40°C to +85°C                  | 2 MHz     | MC68HC11E20CFN2 |  |  |  |  |  |  |  |

|                                            | -40°C (0 +65°C                  | 3 MHz     | MC68HC11E20CFN3 |  |  |  |  |  |  |  |

|                                            | -40°C to +105°C                 | 2 MHz     | MC68HC11E20VFN2 |  |  |  |  |  |  |  |

|                                            | -40°C to +125°C                 | 2 MHz     | MC68HC11E20MFN2 |  |  |  |  |  |  |  |

| 64-pin quad flat pack (QFP)                |                                 |           |                 |  |  |  |  |  |  |  |

|                                            | 0°C to +70°°C                   | 3 MHz     | MC68HC11E9FU3   |  |  |  |  |  |  |  |

|                                            | -40°C to +85°C                  | 2 MHz     | MC68HC11E9CFU2  |  |  |  |  |  |  |  |

| Custom ROM                                 | -40°C (0 +65°C                  | 3 MHz     | MC68HC11E9CFU3  |  |  |  |  |  |  |  |

|                                            | -40°C to +105°C                 | 2 MHz     | MC68HC11E9VFU2  |  |  |  |  |  |  |  |

|                                            | -40°C to +125°C                 | 2 MHz     | MC68HC11E9MFU2  |  |  |  |  |  |  |  |

| 64-pin quad flat pack (continued)          |                                 |           |                 |  |  |  |  |  |  |  |

|                                            | 0°C to +70°°C                   | 3 MHz     | MC68HC11E20FU3  |  |  |  |  |  |  |  |

|                                            | 4000 1 0500                     | 2 MHz     | MC68HC11E20CFU2 |  |  |  |  |  |  |  |

| 20 Kbytes Custom ROM                       | -40°C to +85°C                  | 3 MHz     | MC68HC11E20CFU3 |  |  |  |  |  |  |  |

|                                            | -40°C to +105°C                 | 2 MHz     | MC68HC11E20VFU2 |  |  |  |  |  |  |  |

|                                            | -40°C to +125°C                 | 2 MHz     | MC68HC11E20MFU2 |  |  |  |  |  |  |  |

| 52-pin thin quad flat pack (10 mm x 10 mm) |                                 |           |                 |  |  |  |  |  |  |  |

|                                            | 0°C to +70°°C                   | 3 MHz     | MC68HC11E9PB3   |  |  |  |  |  |  |  |

|                                            | -40°C to +85°C                  | 2 MHz     | MC68HC11E9CPB2  |  |  |  |  |  |  |  |

| Custom ROM                                 | -40°C t0 +85°C                  | 3 MHz     | MC68HC11E9CPB3  |  |  |  |  |  |  |  |

|                                            | -40°C to +105°C                 | 2 MHz     | MC68HC11E9VPB2  |  |  |  |  |  |  |  |

|                                            | -40°C to +125°C                 | 2 MHz     | MC68HC11E9MPB2  |  |  |  |  |  |  |  |

| 56-pin dual in-line package with           | h 0.70-inch lead spacing (SDIP) |           | -               |  |  |  |  |  |  |  |

|                                            | 0°C to +70°°C                   | 3 MHz     | MC68HC11E9B3    |  |  |  |  |  |  |  |

|                                            | 40°C to 195°C                   | 2 MHz     | MC68HC11E9CB2   |  |  |  |  |  |  |  |

| Custom ROM                                 | -40°C to +85°C                  | 3 MHz     | MC68HC11E9CB3   |  |  |  |  |  |  |  |

|                                            | -40°C to +105°C                 | 2 MHz     | MC68HC11E9VB2   |  |  |  |  |  |  |  |

|                                            | -40°C to +125°C                 | 2 MHz     | MC68HC11E9MB2   |  |  |  |  |  |  |  |

|                                            |                                 |           |                 |  |  |  |  |  |  |  |

**Ordering Information and Mechanical Specifications**

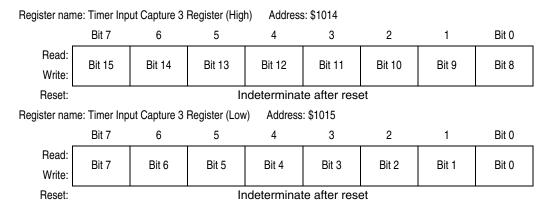

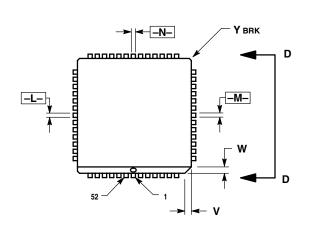

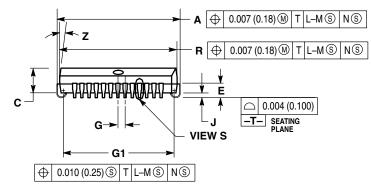

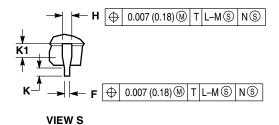

### 11.5 52-Pin Plastic-Leaded Chip Carrier (Case 778)

#### NOTES

- DATUMS -L-, -M-, AND -N- DETERMINED WHERE

TOP OF LEAD SHOULDER EXITS PLASTIC BODY AT

MOLD PARTING LINE.

- MOLD PARTING LINE:

2. DIMENSION G1, TRUE POSITION TO BE MEASURED AT DATUM -T-, SEATING PLANE.

3. DIMENSIONS R AND U DO NOT INCLUDE MOLD

- 3. DIMENSIONS R AND U DO NOT INCLUDE MOLD FLASH. ALLOWABLE MOLD FLASH IS 0.010 (0.250) PER SIDE.

- 4. DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.

- 5. CONTROLLING DIMENSION: INCH.

- 6. THE PACKAGE TOP MAY BE SMALLER THAN THE PACKAGE BOTTOM BY UP TO 0.012 (0.300). DIMENSIONS R AND U ARE DETERMINED AT THE OUTERMOST EXTREMES OF THE PLASTIC BODY EXCLUSIVE OF MOLD FLASH, TIE BAR BURRS, GATE BURRS AND INTERLEAD FLASH, BUT INCLUDING ANY MISMATCH BETWEEN THE TOP AND BOTTOM OF THE PLASTIC BODY.

- 7. DIMENSION H DOES NOT INCLUDE DAMBAR PROTRUSION OR INTRUSION. THE DAMBAR PROTRUSION(S) SHALL NOT CAUSE THE H DIMENSION TO BE GREATER THAN 0.037 (0.940). THE DAMBAR INTRUSION(S) SHALL NOT CAUSE THE H DIMENSION TO BE SMALLER THAN 0.025 (0.635).

|     | INC         | HES   | MILLIMETERS |       |  |  |

|-----|-------------|-------|-------------|-------|--|--|

| DIM | CAM MIN MIC |       | MIN         | MAX   |  |  |

| Α   | 0.785       | 0.795 | 19.94       | 20.19 |  |  |

| В   | 0.785       | 0.795 | 19.94       | 20.19 |  |  |

| С   | 0.165       | 0.180 | 4.20        | 4.57  |  |  |

| Е   | 0.090       | 0.110 | 2.29        | 2.79  |  |  |

| F   | 0.013       | 0.019 | 0.33        | 0.48  |  |  |

| G   | 0.050       | BSC   | 1.27 BSC    |       |  |  |

| Н   | 0.026       | 0.032 | 0.66        | 0.81  |  |  |

| J   | 0.020       |       | 0.51        |       |  |  |

| K   | 0.025       |       | 0.64        |       |  |  |

| R   | 0.750       | 0.756 | 19.05       | 19.20 |  |  |

| U   | 0.750       | 0.756 | 19.05       | 19.20 |  |  |

| ٧   | 0.042       | 0.048 | 1.07        | 1.21  |  |  |

| W   | 0.042       | 0.048 | 1.07        | 1.21  |  |  |

| Х   | 0.042       | 0.056 | 1.07        | 1.42  |  |  |

| Υ   |             | 0.020 |             | 0.50  |  |  |

| Z   | 2°          | 10°   | 2°          | 10°   |  |  |

| G1  | 0.710       | 0.730 | 18.04       | 18.54 |  |  |

| K1  | 0.040       |       | 1.02        |       |  |  |

- Extensive on-line MCU information via the CHIPINFO command. View memory map, vectors, register, and pinout information pertaining to the device being emulated

- Host software supports:

- An editor

- An assembler and user interface

- Source-level debug

- Bus state analysis

- IBM<sup>®</sup> mouse

#### A.5 SPGMR11 — Serial Programmer for M68HC11 MCUs

The SPGMR11 is a modular EPROM/EEPROM programming tool for all M68HC11 devices. The programmer features interchangeable adapters that allow programming of various M68HC11 package types.

Programmer features include:

- Programs M68HC11 Family devices that contain an EPROM or EEPROM array.

- Can be operated as a stand-alone programmer connected to a host computer or connected between a host computer and the M68HC11 modular development system (MMDS11) station module

- Uses plug-in programming adapters to accommodate a variety of MCU devices and packages

- On-board programming voltage circuit eliminates the need for an external 12-volt supply.

- Includes programming software and a user's manual

- Includes a +5-volt power cable and a DB9 to DB25 connector adapter

M68HC11E Family Data Sheet, Rev. 5.1

<sup>&</sup>lt;sup>®</sup> IBM is a registered trademark145 of International Business Machines Corporation.

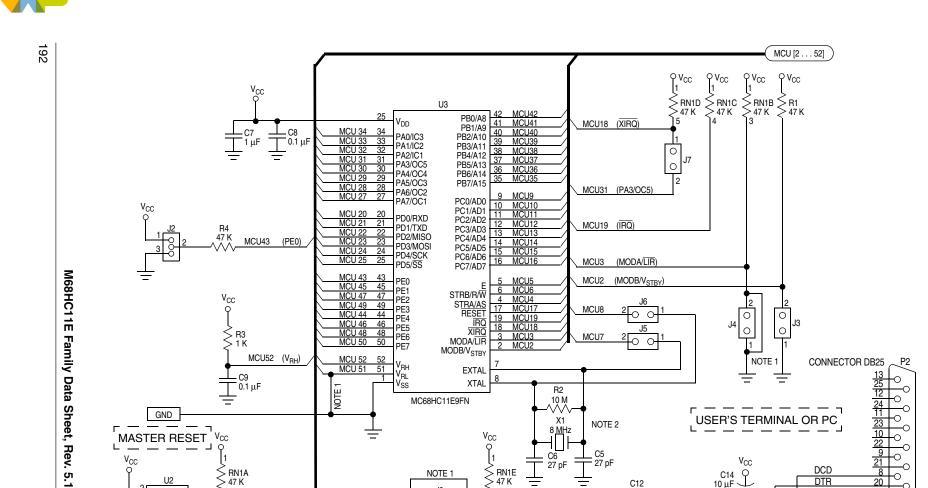

DCD

DTR

DSR

J15

NOTE 1

0

0

C14

10 μF

20 V

4 \

TX1

RX1

TX2 RX2

TX3

RX3

GND

DI1 16 13

DD1

DI2

DD2

DI3

DD3 19

$V_{CC}$ = C11 MC145407 0.1 μF

V<sub>CC</sub>O-

NC

Notes: 1. Default cut traces installed from factory on bottom of the board.

RN1A

MCU17 (RESET)

NPUT

GND

RESE

MC34064P

2. X1 is shipped as a ceramic resonator with built-in capacitors. Holes are provided for a crystal and two capacitors.

MCU21 (PD1/TXD)

MCU20 (PD0/RXD)

Figure B-1. EVBU Schematic Diagram

≥ RN1E ≥ 47 K

NOTE 1

J8

NOTE 1

## Freescale Semiconductor Application Note

AN1060 Rev. 1.1, 07/2005

## M68HC11 Bootstrap Mode

By Jim Sibigtroth Mike Rhoades John Langan Austin, Texas

#### Introduction

The M68HC11 Family of MCUs (microcontroller units) has a bootstrap mode that allows a user-defined program to be loaded into the internal random-access memory (RAM) by way of the serial communications interface (SCI); the M68HC11 then executes this loaded program. The loaded program can do anything a normal user program can do as well as anything a factory test program can do because protected control bits are accessible in bootstrap mode. Although the bootstrap mode is a single-chip mode of operation, expanded mode resources are accessible because the mode control bits can be changed while operating in the bootstrap mode.

This application note explains the operation and application of the M68HC11 bootstrap mode. Although basic concepts associated with this mode are quite simple, the more subtle implications of these functions require careful consideration. Useful applications of this mode are overlooked due to an incomplete understanding of bootstrap mode. Also, common problems associated with bootstrap mode could be avoided by a more complete understanding of its operation and implications.

Topics discussed in this application note include:

- Basic operation of the M68HC11 bootstrap mode

- General discussion of bootstrap mode uses

- Detailed explanation of on-chip bootstrap logic

- Detailed explanation of bootstrap firmware

- Bootstrap firmware vs. EEPROM security

- Incorporating the bootstrap mode into a system

- Driving bootstrap mode from another M68HC11

- Driving bootstrap mode from a personal computer

- Common bootstrap mode problems

- Variations for specific versions of M68HC11

- Commented listings for selected M68HC11 bootstrap ROMs

Figure 2 shows how the bootloader program differentiates between the default baud rate (7812 baud at a 2-MHz E-clock rate) and the alternate baud rate (1200 baud at a 2-MHz E-clock rate). The host computer sends an initial \$FF character, which is used by the bootloader to determine the baud rate that will be used for the downloading operation. The top half of Figure 2 shows normal reception of \$FF. Receive data samples at [1] detect the falling edge of the start bit and then verify the start bit by taking a sample at the center of the start bit time. Samples are then taken at the middle of each bit time [2] to reconstruct the value of the received character (all 1s in this case). A sample is then taken at the middle of the stop bit time as a framing check (a 1 is expected) [3]. Unless another character immediately follows this \$FF character, the receive data line will idle in the high state as shown at [4].

The bottom half of Figure 2 shows how the receiver will incorrectly receive the \$FF character that is sent from the host at 1200 baud. Because the receiver is set to 7812 baud, the receive data samples are taken at the same times as in the upper half of Figure 2. The start bit at 1200 baud [5] is 6.5 times as long as the start bit at 7812 baud [6].

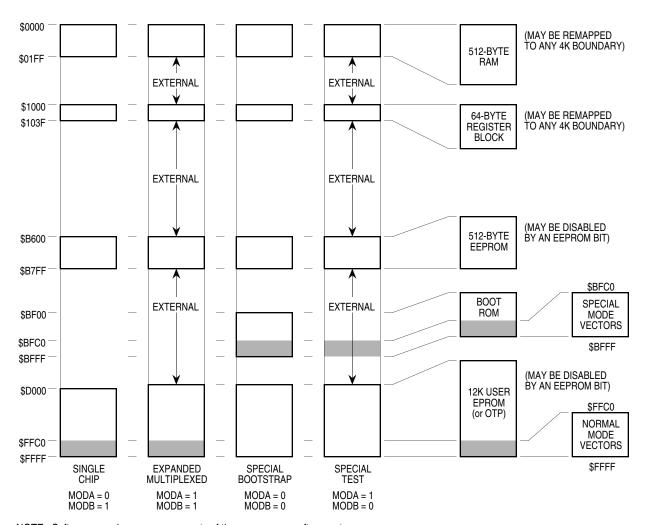

NOTE: Software can change some aspects of the memory map after reset.

Figure 1. MC68HC711E9 Composite Memory Map

To Execute the Program

Enabling the Security Feature on M68HC811E2 Devices with PCbug11 on the M68HC711E9PGMR, Rev. 0.1