Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | ARM® Cortex®-M0+                                                           |

| Core Size                  | 32-Bit Single-Core                                                         |

| Speed                      | 48MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SCI, SPI, UART/USART, USB                        |

| Peripherals                | DMA, POR, PWM, WDT                                                         |

| Number of I/O              | 51                                                                         |

| Program Memory Size        | 128KB (128K x 8)                                                           |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 16K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.62V ~ 3.63V                                                              |

| Data Converters            | A/D 20x12b; D/A 2x12b                                                      |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 64-XFBGA, WLCSP                                                            |

| Supplier Device Package    | 64-WLCSP (3.58x3.28)                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsaml21j17b-uut |

|                            |                                                                            |

- Static and Dynamic Power Gating Architecture

- Battery backup support

- Two Performance Levels

- Embedded Buck/LDO regulator supporting on-the-fly selection

#### Peripherals

- 16-channel Direct Memory Access Controller (DMAC)

- 12-channel Event System

- Up to five 16-bit Timer/Counters (TC) including one low-power TC, each configurable as:

- 16-bit TC with two compare/capture channels

- · 8-bit TC with two compare/capture channels

- 32-bit TC with two compare/capture channels, by using two TCs

- Two 24-bit and one 16-bit Timer/Counters for Control (TCC), with extended functions:

- Up to four compare channels with optional complementary output

- · Generation of synchronized pulse width modulation (PWM) pattern across port pins

- Deterministic fault protection, fast decay and configurable dead-time between complementary output

- · Dithering that increase resolution with up to 5 bit and reduce quantization error

- 32-bit Real Time Counter (RTC) with clock/calendar function

- Watchdog Timer (WDT)

- CRC-32 generator

- One full-speed (12Mbps) Universal Serial Bus (USB) 2.0 interface

- Embedded host and device function

- Eight endpoints

- Up to six Serial Communication Interfaces (SERCOM) including one low-power SERCOM, each configurable to operate as either:

- USART with full-duplex and single-wire half-duplex configuration

- I<sup>2</sup>C up to 3.4MHz

- SPI

- LIN slave

- One AES encryption engine

- One True Random Generator (TRNG)

- One Configurable Custom Logic (CCL)

- One 12-bit, 1MSPS Analog-to-Digital Converter (ADC) with up to 20 channels

- Differential and single-ended input

- Automatic offset and gain error compensation

- Oversampling and decimation in hardware to support 13-, 14-, 15-, or 16-bit resolution

- Two 12-bit, 1MSPS Dual Output Digital-to-Analog Converter (DAC)

- Two Analog Comparators (AC) with window compare function

- Three Operational Amplifiers (OPAMP)

- Peripheral Touch Controller (PTC)

- 169-Channel capacitive touch and proximity sensing

- Wake-up on touch in standby mode

#### Oscillators

32.768kHz crystal oscillator (XOSC32K)

- 0.4-32MHz crystal oscillator (XOSC)

- 32.768kHz internal oscillator (OSC32K)

- 32.768kHz ultra-low-power internal oscillator (OSCULP32K)

- 16/12/8/4MHz high-accuracy internal oscillator (OSC16M)

- 48MHz Digital Frequency Locked Loop (DFLL48M)

- 96MHz Fractional Digital Phased Locked Loop (FDPLL96M)

- I/O

- Up to 51 programmable I/O pins

- Easy migration from SAM D family

- Packages

- 64-pin TQFP, QFN, WLCSP

- 48-pin TQFP, QFN

- 32-pin TQFP, QFN

- Operating Voltage

- 1.62V 3.63V

# **Table of Contents**

| Int | roduc | etion                              | 1  |

|-----|-------|------------------------------------|----|

| 1.  | Des   | cription                           | 5  |

| Fe  | ature | S                                  | 1  |

| 2.  | Con   | figuration Summary                 | 7  |

| 3.  | Orde  | ering Information                  | 10 |

|     | 3.1.  | SAM L21J                           | 10 |

|     | 3.2.  | SAM L21G                           | 11 |

|     | 3.3.  | SAM L21E                           | 11 |

|     | 3.4.  | Device Identification              | 11 |

| 4.  | Bloc  | k Diagram                          | 13 |

| 5.  | Pino  | out                                | 15 |

|     | 5.1.  | SAM L21J                           | 15 |

|     | 5.2.  | SAM L21J WLCSP64                   |    |

|     | 5.3.  | SAM L21G                           | 17 |

|     | 5.4.  | SAM L21E                           |    |

| 6.  | Proc  | duct Mapping                       | 19 |

| 7.  | Proc  | cessor and Architecture            | 20 |

|     | 7.1.  | Cortex M0+ Processor               | 20 |

|     | 7.2.  | Nested Vector Interrupt Controller |    |

|     | 7.3.  | Micro Trace Buffer                 |    |

|     | 7.4.  | High-Speed Bus System              | 24 |

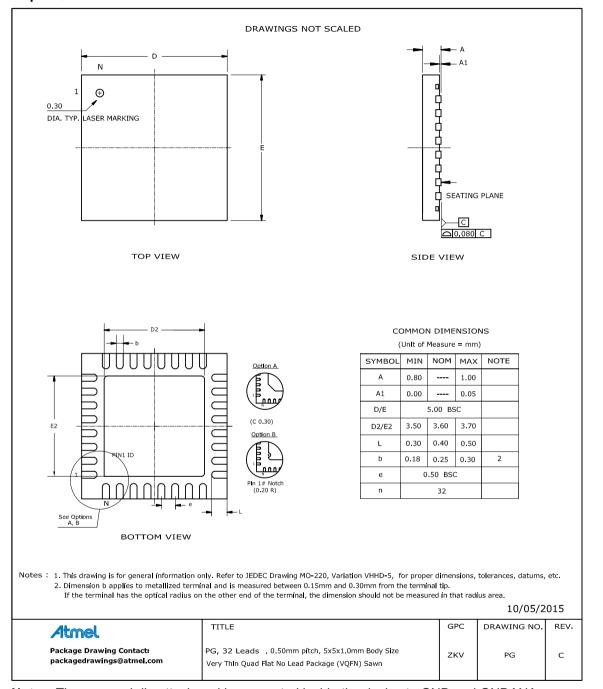

| 8.  | Pacl  | kaging Information                 | 29 |

|     | 8.1.  | Thermal Considerations             | 29 |

|     | 8.2.  | Package Drawings                   |    |

|     | 8.3.  | Soldering Profile                  | 39 |

# 1. Description

Atmel® | SMART SAM L21 is a series of Ultra low-power microcontrollers using the 32-bit ARM® Cortex®-M0+ processor, and ranging from 32- to 64-pins with up to 256KB Flash and 40KB of SRAM. The SAM L21 devices operate at a maximum frequency of 48MHz and reach 2.46 CoreMark®/MHz. They are designed for simple and intuitive migration with identical peripheral modules, hex compatible code, identical linear address map and pin compatible migration paths between all devices in the product series. All devices include intelligent and flexible peripherals, Atmel Event System for inter-peripheral signaling, and support for capacitive touch button, slider and wheel user interfaces.

The Atmel SAM L21 devices provide the following features: In-system programmable Flash, 16-channel direct memory access (DMA) controller, 12-channel Event System, programmable interrupt controller, up to 51 programmable I/O pins, 32-bit real-time clock and calendar, up to five 16-bit Timer/Counters (TC) and three Timer/Counters for Control (TCC) where each TC/TCC can be configured to perform frequency and waveform generation, accurate program execution timing or input capture with time and frequency measurement of digital signals. The TCs can operate in 8- or 16-bit mode, selected TCs can be cascaded to form a 32-bit TC, and three timer/counters have extended functions optimized for motor, lighting and other control applications. Two TCC can operate in 24-bit mode, the third TCC can operate in 16-bit mode. The series provide one full-speed USB 2.0 embedded host and device interface; up to six Serial Communication Modules (SERCOM) that each can be configured to act as an USART, UART, SPI, I<sup>2</sup>C up to 3.4MHz, SMBus, PMBus, and LIN slave; up to twenty channel 1MSPS 12-bit ADC with programmable gain and optional oversampling and decimation supporting up to 16-bit resolution, two 12-bit 1MSPS DACs, two analog comparators with window mode, three independent cascadable OPAMPs supporting internal connection with others analog features. Peripheral Touch Controller supporting up to 192 buttons. sliders, wheels and proximity sensing; programmable Watchdog Timer, brown-out detector and power-on reset and two-pin Serial Wire Debug (SWD) program and debug interface.

All devices have accurate and low-power external and internal oscillators. All oscillators can be used as a source for the system clock. Different clock domains can be independently configured to run at different frequencies, enabling power saving by running each peripheral at its optimal clock frequency, and thus maintaining a high CPU frequency while reducing power consumption.

The SAM L21 devices have four software-selectable sleep modes, idle, standby, backup and off. In idle mode the CPU is stopped while all other functions can be kept running. In standby all clocks and functions are stopped except those selected to continue running. In this mode all RAMs and logic contents are retained. The device supports SleepWalking. This feature allows the peripheral to wake up from sleep based on predefined conditions, and thus allows some internal operation like DMA transfer and/or the CPU to wake up only when needed, e.g. when a threshold is crossed or a result is ready. The Event System supports synchronous and asynchronous events, allowing peripherals to receive, react to and send events even in standby mode.

The SAM L21 devices have two software-selectable performance levels (PL0 and PL2) allowing the user to scale the lowest core voltage level that will support the operating frequency. To further minimize consumption, specifically leakage dissipation, the SAM L21 devices utilizes power domain gating technique with retention to turn off some logic area while keeping its logic state. This technique is fully handled by hardware.

The Flash program memory can be reprogrammed in-system through the SWD interface. The same interface can be used for nonintrusive on-chip debugging of application code. A boot loader running in the device can use any communication interface to download and upgrade the application program in the Flash memory.

|                                                                                                | SAM L21J                                                | SAM L21G            | SAM L21E            |  |

|------------------------------------------------------------------------------------------------|---------------------------------------------------------|---------------------|---------------------|--|

| Real-Time Counter (RTC)                                                                        | Yes                                                     | Yes                 | Yes                 |  |

| RTC alarms                                                                                     | 1                                                       | 1                   | 1                   |  |

| RTC compare values                                                                             | One 32-bit value or                                     | One 32-bit value or | One 32-bit value or |  |

|                                                                                                | two 16-bit values                                       | two 16-bit values   | two 16-bit values   |  |

| External Interrupt lines                                                                       | 16                                                      | 16                  | 16                  |  |

| Peripheral Touch<br>Controller (PTC)<br>channels (X- x Y-Lines)<br>for mutual capacitance      | 169 (13x13)                                             | 81 (9x9)            | 42 (7x6)            |  |

| Peripheral Touch<br>Controller (PTC)<br>channels for self<br>capacitance (Y-Lines<br>only) (3) | 16                                                      | 10                  | 7                   |  |

| Maximum CPU frequency                                                                          | 48MHz                                                   |                     |                     |  |

| Packages                                                                                       | QFN                                                     | QFN                 | QFN                 |  |

|                                                                                                | TQFP                                                    | TQFP                | TQFP                |  |

|                                                                                                | WLCSP <sup>(4)</sup>                                    |                     |                     |  |

| Oscillators                                                                                    | 32.768kHz crystal oscillat                              | or (XOSC32K)        |                     |  |

|                                                                                                | 0.4-32MHz crystal oscillat                              | tor (XOSC)          |                     |  |

|                                                                                                | 32.768kHz internal oscilla                              | ator (OSC32K)       |                     |  |

|                                                                                                | 32KHz ultra-low-power internal oscillator (OSCULP32K)   |                     |                     |  |

|                                                                                                | 16/12/8/4MHz high-accuracy internal oscillator (OSC16M) |                     |                     |  |

|                                                                                                | 48MHz Digital Frequency Locked Loop (DFLL48M)           |                     |                     |  |

|                                                                                                | 96MHz Fractional Digital Phased Locked Loop (FDPLL96M)  |                     |                     |  |

| Event System channels                                                                          | 12                                                      | 12                  | 12                  |  |

| SW Debug Interface                                                                             | Yes                                                     | Yes                 | Yes                 |  |

| Watchdog Timer (WDT)                                                                           | Yes                                                     | Yes                 | Yes                 |  |

## Note:

- 1. For SAM L21E and SAM L21G, only TC0, TC1 and TC4 are available.

- 2. The number of X- and Y-lines depends on the configuration of the device, as some I/O lines can be configured as either X-lines or Y-lines. Refer to *Multiplexed Signals* for details. The number in the Configuration Summary is the maximum number of channels that can be obtained.

## 3.2. SAM L21G

Table 3-2. SAM L21G Ordering Codes

| Ordering Code    | FLASH (bytes) | SRAM (bytes) | Package | Carrier Type |

|------------------|---------------|--------------|---------|--------------|

| ATSAML21G16B-AUT | 64K           | 8K           | TQFP48  | Tape & Reel  |

| ATSAML21G16B-MUT |               |              | QFN48   |              |

| ATSAML21G17B-AUT | 128K          | 16K          | TQFP48  | Tape & Reel  |

| ATSAML21G17B-MUT |               |              | QFN48   |              |

| ATSAML21G18B-AUT | 256K          | 32K          | TQFP48  | Tape & Reel  |

| ATSAML21G18B-MUT |               |              | QFN48   |              |

## 3.3. SAM L21E

Table 3-3. SAM L21E

| Ordering Code    | FLASH (bytes) | SRAM (bytes) | Package | Carrier Type |

|------------------|---------------|--------------|---------|--------------|

| ATSAML21E15B-AUT | 32K           | 4K           | TQFP32  | Tape & Reel  |

| ATSAML21E15B-MUT |               |              | QFN32   |              |

| ATSAML21E16B-AUT | 64K           | 8K           | TQFP32  | Tape & Reel  |

| ATSAML21E16B-MUT |               |              | QFN32   |              |

| ATSAML21E17B-AUT | 128K          | 16K          | TQFP32  | Tape & Reel  |

| ATSAML21E17B-MUT |               |              | QFN32   |              |

| ATSAML21E18B-AUT | 256K          | 32K          | TQFP32  | Tape & Reel  |

| ATSAML21E18B-MUT |               |              | QFN32   |              |

## 3.4. Device Identification

The DSU - Device Service Unit peripheral provides the Device Selection bits in the Device Identification register (DID.DEVSEL) in order to identify the device by software. The SAM L21 variants have a reset value of DID=0x1081drxx, with the LSB identifying the die number ('d'), the die revision ('r') and the device selection ('xx').

Table 3-4. SAM L21 Device Identification Values

| DEVSEL (DID[7:0]) | Device     |

|-------------------|------------|

| 0x00              | SAML21J18A |

| 0x01              | SAML21J17A |

| 0x02              | SAML21J16A |

| 0x03-0x04         | Reserved   |

| 0x05              | SAML21G18A |

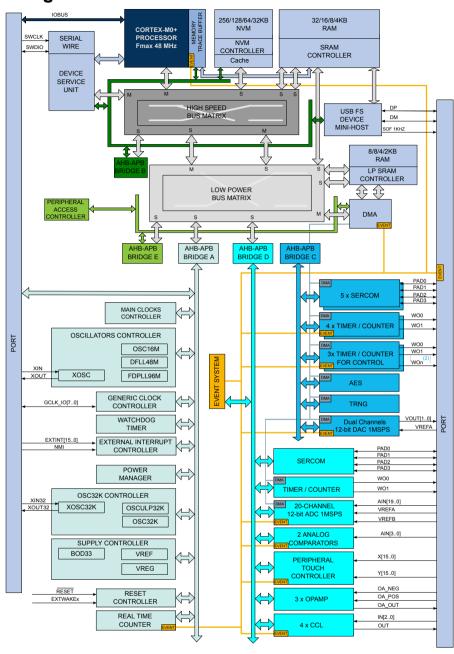

# 4. Block Diagram

## Note:

Some products have different number of SERCOM instances, Timer/Counter instances, PTC signals and ADC signals.

| 2. | The three TCC instances have different configurations, including the number of Waveform Output (WO) lines. |

|----|------------------------------------------------------------------------------------------------------------|

|    |                                                                                                            |

|    |                                                                                                            |

|    |                                                                                                            |

|    |                                                                                                            |

|    |                                                                                                            |

|    |                                                                                                            |

|    |                                                                                                            |

|    |                                                                                                            |

|    |                                                                                                            |

|    |                                                                                                            |

|    |                                                                                                            |

|    |                                                                                                            |

|    |                                                                                                            |

|    |                                                                                                            |

|    |                                                                                                            |

|    |                                                                                                            |

|    |                                                                                                            |

|    |                                                                                                            |

|    |                                                                                                            |

|    |                                                                                                            |

|    |                                                                                                            |

|    |                                                                                                            |

|    |                                                                                                            |

|    |                                                                                                            |

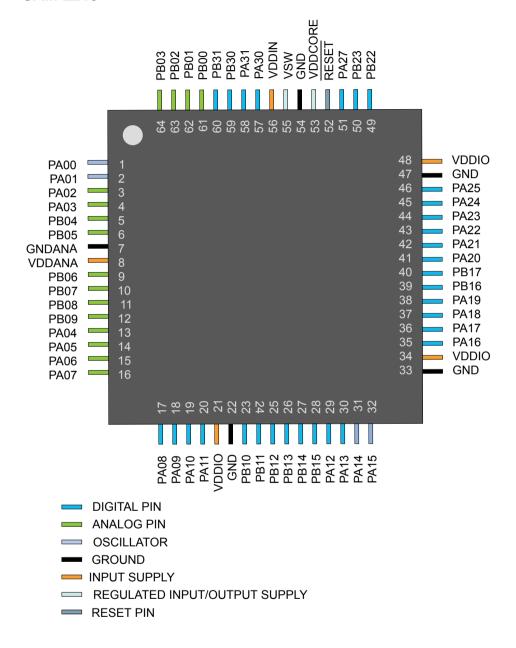

# 5. Pinout

## 5.1. SAM L21J

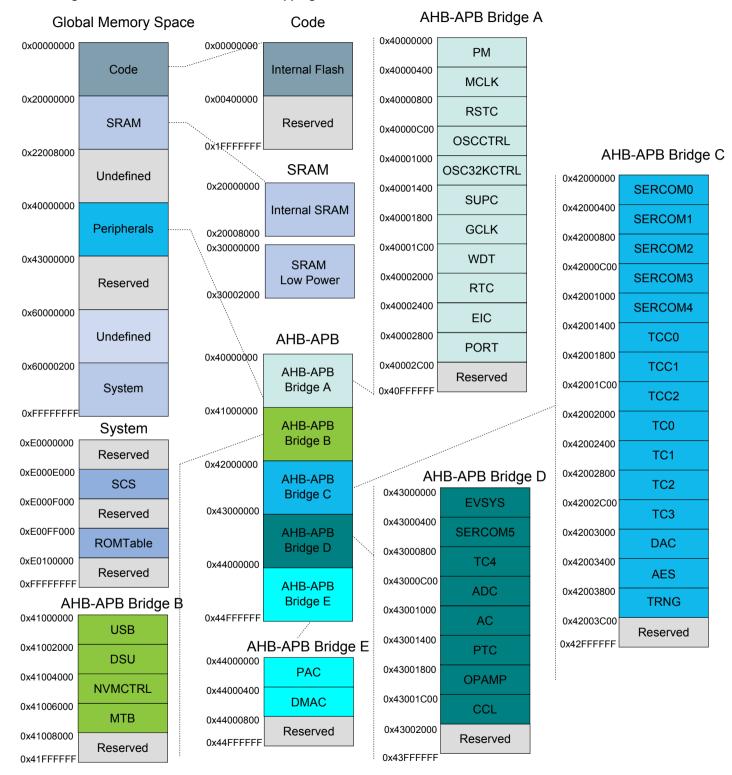

# 6. Product Mapping

Figure 6-1. Atmel SAM L21 Product Mapping

External interrupt signals connect to the NVIC, and the NVIC prioritizes the interrupts.

Software can set the priority of each interrupt. The NVIC and the Cortex-M0+ processor core are closely coupled, providing low latency interrupt processing and efficient processing of late arriving interrupts. Refer to the Cortex-M0+ Technical Reference Manual for details (http://www.arm.com).

**Note:** When the CPU frequency is much higher than the APB frequency it is recommended to insert a memory read barrier after each CPU write to registers mapped on the APB. Failing to do so in such conditions may lead to unexpected behavior such as e.g. re-entering a peripheral interrupt handler just after leaving it.

- System Timer (SysTick)

- The System Timer is a 24-bit timer clocked by CLK\_CPU that extends the functionality of both the processor and the NVIC. Refer to the Cortex-M0+ Technical Reference Manual for details (http://www.arm.com).

- System Control Block (SCB)

- The System Control Block provides system implementation information, and system control.

This includes configuration, control, and reporting of the system exceptions. Refer to the Cortex-M0+ Devices Generic User Guide for details (http://www.arm.com)

- Micro Trace Buffer (MTB)

- The CoreSight MTB-M0+ (MTB) provides a simple execution trace capability to the Cortex-M0+ processor. Refer to section MTB-Micro Trace Buffer and the CoreSight MTB-M0+ Technical Reference Manual for details (http://www.arm.com).

#### **Related Links**

Nested Vector Interrupt Controller on page 21

#### 7.1.1.2. Cortex M0+ Address Map

Table 7-2. Cortex-M0+ Address Map

| Address    | Peripheral                                  |

|------------|---------------------------------------------|

| 0xE000E000 | System Control Space (SCS)                  |

| 0xE000E010 | System Timer (SysTick)                      |

| 0xE000E100 | Nested Vectored Interrupt Controller (NVIC) |

| 0xE000ED00 | System Control Block (SCB)                  |

| 0x41006000 | Micro Trace Buffer (MTB)                    |

#### 7.1.1.3. I/O Interface

The device allows direct access to PORT registers. Accesses to the AMBA<sup>®</sup> AHB-Lite<sup> $^{\text{M}}$ </sup> and the single cycle I/O interface can be made concurrently, so the Cortex M0+ processor can fetch the next instructions while accessing the I/Os. This enables single cycle I/O access to be sustained for as long as necessary.

## 7.2. Nested Vector Interrupt Controller

#### 7.2.1. Overview

The Nested Vectored Interrupt Controller (NVIC) in the SAM L21 supports 32 interrupt lines with four different priority levels. For more details, refer to the Cortex-M0+ Technical Reference Manual (http://www.arm.com).

#### 7.2.2. Interrupt Line Mapping

Each of the 28 interrupt lines is connected to one peripheral instance, as shown in the table below. Each peripheral can have one or more interrupt flags, located in the peripheral's Interrupt Flag Status and Clear (INTFLAG) register.

An interrupt flag is set when the interrupt condition occurs. Each interrupt in the peripheral can be individually enabled by writing a 1 to the corresponding bit in the peripheral's Interrupt Enable Set (INTENSET) register, and disabled by writing 1 to the corresponding bit in the peripheral's Interrupt Enable Clear (INTENCLR) register.

An interrupt request is generated from the peripheral when the interrupt flag is set and the corresponding interrupt is enabled.

The interrupt requests for one peripheral are ORed together on system level, generating one interrupt request for each peripheral. An interrupt request will set the corresponding interrupt pending bit in the NVIC interrupt pending registers (SETPEND/CLRPEND bits in ISPR/ICPR).

For the NVIC to activate the interrupt, it must be enabled in the NVIC interrupt enable register (SETENA/ CLRENA bits in ISER/ICER). The NVIC interrupt priority registers IPR0-IPR7 provide a priority field for each interrupt.

Table 7-3. Interrupt Line Mapping

| Peripheral source                          | NVIC line |

|--------------------------------------------|-----------|

| EIC NMI – External Interrupt Controller    | NMI       |

| PM – Power Manager                         | 0         |

| MCLK - Main Clock                          |           |

| OSCCTRL - Oscillators Controller           |           |

| OSC32KCTRL - 32KHz Oscillators Controller  |           |

| SUPC - Supply Controller                   |           |

| PAC - Protecion Access Controller          |           |

| WDT – Watchdog Timer                       | 1         |

| RTC – Real Time Counter                    | 2         |

| EIC – External Interrupt Controller        | 3         |

| NVMCTRL – Non-Volatile Memory Controller   | 4         |

| DMAC - Direct Memory Access Controller     | 5         |

| USB - Universal Serial Bus                 | 6         |

| EVSYS – Event System                       | 7         |

| SERCOM0 – Serial Communication Interface 0 | 8         |

| SERCOM1 – Serial Communication Interface 1 | 9         |

| SERCOM2 – Serial Communication Interface 2 | 10        |

| SERCOM3 – Serial Communication Interface 3 | 11        |

| SERCOM4 – Serial Communication Interface 4 | 12        |

| Peripheral source                          | NVIC line |

|--------------------------------------------|-----------|

| SERCOM5 – Serial Communication Interface 5 | 13        |

| TCC0 – Timer Counter for Control 0         | 14        |

| TCC1 – Timer Counter for Control 1         | 15        |

| TCC2 – Timer Counter for Control 2         | 16        |

| TC0 – Timer Counter 0                      | 17        |

| TC1 – Timer Counter 1                      | 18        |

| TC2 – Timer Counter 2                      | 19        |

| TC3 – Timer Counter 3                      | 20        |

| TC4 – Timer Counter 4                      | 21        |

| ADC – Analog-to-Digital Converter          | 22        |

| AC – Analog Comparator                     | 23        |

| DAC – Digital-to-Analog Converter          | 24        |

| PTC – Peripheral Touch Controller          | 25        |

| AES - Advanced Encrytpion Standard module  | 26        |

| TRNG - True Random Number Generator        | 27        |

## 7.3. Micro Trace Buffer

## 7.3.1. Features

- Program flow tracing for the Cortex-M0+ processor

- MTB SRAM can be used for both trace and general purpose storage by the processor

- The position and size of the trace buffer in SRAM is configurable by software

- CoreSight compliant

#### 7.3.2. Overview

When enabled, the MTB records the changes in program flow that are reported by the Cortex-M0+ processor over the execution trace interface. This interface is shared between the Cortex-M0+ processor and the CoreSight MTB-M0+. The information is stored by the MTB in the SRAM as trace packets. An off-chip debugger can extract the trace information using the Debug Access Port to read the trace information from the SRAM. The debugger can then reconstruct the program flow from this information.

The MTB stores trace information into the SRAM and gives the processor access to the SRAM simultaneously. The MTB ensures that trace write accesses have priority over processor accesses.

An execution trace packet consists of a pair of 32-bit words that the MTB generates when it detects a non-sequential change of the program pounter (PC) value. A non-sequential PC change can occur during branch instructions or during exception entry. See the CoreSight MTB-M0+ Technical Reference Manual for more details on the MTB execution trace packet format.

Tracing is enabled when the MASTER.EN bit in the Master Trace Control Register is 1. There are various ways to set the bit to 1 to start tracing, or to 0 to stop tracing. See the CoreSight Cortex-M0+ Technical Reference Manual for more details on the Trace start and stop and for a detailed description of the MTB's

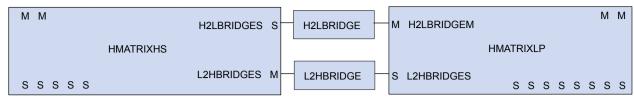

Figure 7-1. High-Speed Bus System Components

## 7.4.2. Configuration

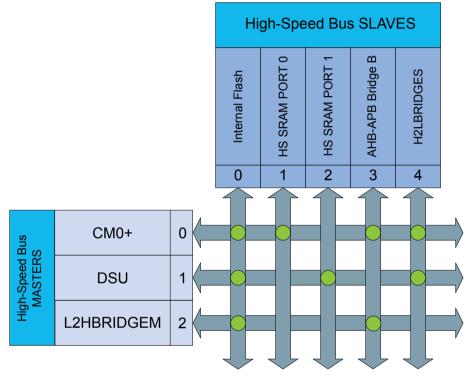

Figure 7-2. Master-Slave Relations High-Speed Bus Matrix

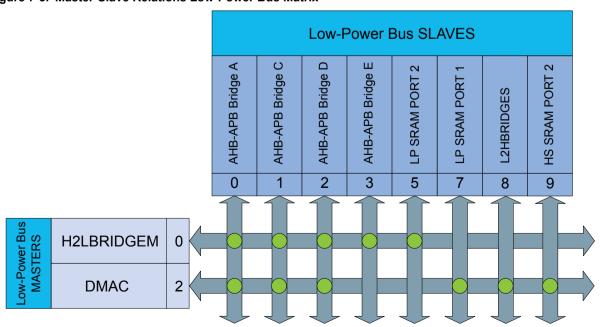

Figure 7-3. Master-Slave Relations Low-Power Bus Matrix

| LP SRAM Port Connection                                    | Port ID | Connection Type | QoS                                   | default QoS |

|------------------------------------------------------------|---------|-----------------|---------------------------------------|-------------|

| H2LBRIDGEM - HS to LP bus matrix AHB to AHB bridge         | 2       | Bus Matrix      | 0x44000924 <sup>(1)</sup> , bits[1:0] | 0x2         |

| DMAC - Direct Memory<br>Access Controller - Data<br>Access | 1       | Bus Matrix      | IP-QOSCTRL.DQOS                       | 0x2         |

## Note:

1. Using 32-bit access only.

# 8. Packaging Information

## 8.1. Thermal Considerations

#### 8.1.1. Thermal Resistance Data

The following table summarizes the thermal resistance data depending on the package.

Table 8-1. Thermal Resistance Data

| Package Type | $\theta_{JA}$ | θ <sub>JC</sub> |

|--------------|---------------|-----------------|

| 32-pin TQFP  | 68°C/W        | 25.8°C/W        |

| 48-pin TQFP  | 78.8°C/W      | 12.3°C/W        |

| 64-pin TQFP  | 66.7°C/W      | 11.9°C/W        |

| 32-pin QFN   | 37.2°C/W      | 3.1°C/W         |

| 48-pin QFN   | 31.6°C/W      | 10.3°C/W        |

| 64-pin QFN   | 32.2°C/W      | 10.1°C/W        |

| 64-pin WLCSP | 36.8°C/W      | 5.0°C/W         |

#### **Related Links**

Junction Temperature on page 29

#### 8.1.2. Junction Temperature

The average chip-junction temperature, T<sub>J</sub>, in °C can be obtained from the following:

1.

$$T_J = T_A + (P_D \times \theta_{JA})$$

2.

$$T_J = T_A + (P_D \times (\theta_{HEATSINK} + \theta_{JC}))$$

#### where:

- $\theta_{JA}$  = Package thermal resistance, Junction-to-ambient (°C/W), see Thermal Resistance Data

- θ<sub>JC</sub> = Package thermal resistance, Junction-to-case thermal resistance (°C/W), see Thermal Resistance Data

- θ<sub>HEATSINK</sub> = Thermal resistance (°C/W) specification of the external cooling device

- P<sub>D</sub> = Device power consumption (W)

- T<sub>A</sub> = Ambient temperature (°C)

From the first equation, the user can derive the estimated lifetime of the chip and decide if a cooling device is necessary or not. If a cooling device is to be fitted on the chip, the second equation should be used to compute the resulting average chip-junction temperature  $T_J$  in °C.

#### **Related Links**

Thermal Resistance Data on page 29

## Table 8-4. Package Reference

| JEDEC Drawing Reference | N/A |

|-------------------------|-----|

| JESD97 Classification   | E1  |

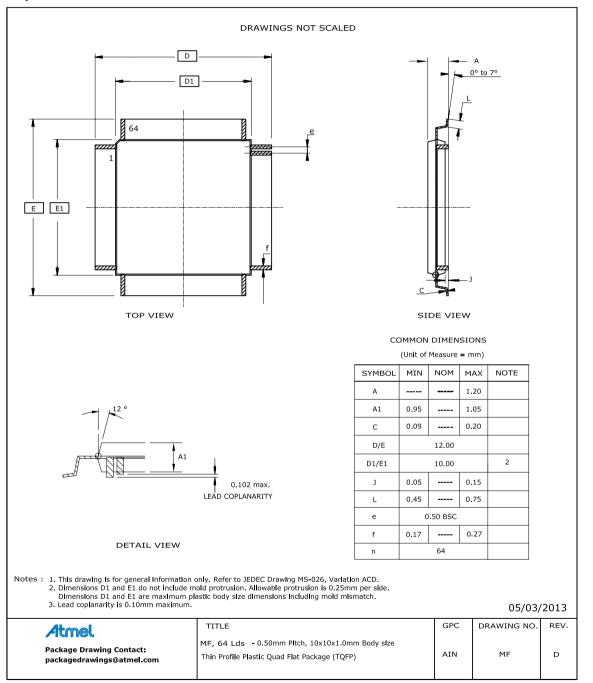

## 8.2.2. 64 pin TQFP

Table 8-5. Device and Package Maximum Weight

| 300 | mg |  |

|-----|----|--|

|     |    |  |

## **Table 8-6. Package Characteristics**

| Moisture Sensitivity Level | MSL3 |

|----------------------------|------|

| ,                          |      |

## Table 8-7. Package Reference

| JEDEC Drawing Reference | MS-026 |

|-------------------------|--------|

| JESD97 Classification   | E3     |

## Table 8-19. Package Reference

| JEDEC Drawing Reference | MS-026 |

|-------------------------|--------|

| JESD97 Classification   | E3     |

## 8.2.7. 32 pin QFN

Note: The exposed die attach pad is connected inside the device to GND and GNDANA.

Table 8-20. Device and Package Maximum Weight

| 90 mg | 90 | mg |

|-------|----|----|

|-------|----|----|

**Atmel Corporation**

1600 Technology Drive, San Jose, CA 95110 USA

**T**: (+1)(408) 441.0311

F: (+1)(408) 436.4200

www.atmel.com

© 2016 Atmel Corporation. / Rev.: Atmel-42385J-SAM L21 Datasheet Summary-06/2016

Atmel®, Atmel logo and combinations thereof, Enabling Unlimited Possibilities®, and others are registered trademarks or trademarks of Atmel Corporation in U.S. and other countries. ARM®, ARM Connected® logo, and others are the registered trademarks or trademarks of ARM Ltd. Other terms and product names may be trademarks of others.

DISCLAIMER: The information in this document is provided in connection with Atmel products. No license, express or implied, by estoppel or otherwise, to any intellectual property right is granted by this document or in connection with the sale of Atmel products. EXCEPT AS SET FORTH IN THE ATMEL TERMS AND CONDITIONS OF SALES LOCATED ON THE ATMEL WEBSITE, ATMEL ASSUMES NO LIABILITY WHATSOEVER AND DISCLAIMS ANY EXPRESS, IMPLIED OR STATUTORY WARRANTY RELATING TO ITS PRODUCTS INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT. IN NO EVENT SHALL ATMEL BE LIABLE FOR ANY DIRECT, INDIRECT, CONSEQUENTIAL, PUNITIVE, SPECIAL OR INCIDENTAL DAMAGES (INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS AND PROFITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUT OF THE USE OR INABILITY TO USE THIS DOCUMENT, EVEN IF ATMEL HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. Atmel makes no representations or warranties with respect to the accuracy or completeness of the contents of this document and reserves the right to make changes to specifications and products descriptions at any time without notice. Atmel does not make any commitment to update the information contained herein. Unless specifically provided otherwise, Atmel products are not suitable for, and shall not be used in, automotive applications. Atmel products are not intended, authorized, or warranted for use as components in applications intended to support or sustain life.

SAFETY-CRITICAL, MILITARY, AND AUTOMOTIVE APPLICATIONS DISCLAIMER: Atmel products are not designed for and will not be used in connection with any applications where the failure of such products would reasonably be expected to result in significant personal injury or death ("Safety-Critical Applications") without an Atmel officer's specific written consent. Safety-Critical Applications include, without limitation, life support devices and systems, equipment or systems for the operation of nuclear facilities and weapons systems. Atmel products are not designed nor intended for use in military or aerospace applications or environments unless specifically designated by Atmel as military-grade. Atmel products are not designed nor intended for use in automotive applications unless specifically designated by Atmel as automotive-grade.