Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 25MHz                                                                     |

| Connectivity               | CANbus, I <sup>2</sup> C, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                               |

| Number of I/O              | 25                                                                        |

| Program Memory Size        | 16KB (8K x 16)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 768 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                               |

| Data Converters            | A/D 8x10b                                                                 |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 28-VQFN Exposed Pad                                                       |

| Supplier Device Package    | 28-QFN (6x6)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f2480-e-ml |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|                   | Pin Number     |          | Pin         | Buffer           |                                                                               |  |  |

|-------------------|----------------|----------|-------------|------------------|-------------------------------------------------------------------------------|--|--|

| Pin Name          | SPDIP,<br>SOIC | QFN      | Ріп<br>Туре | винег<br>Туре    | Description                                                                   |  |  |

|                   |                |          |             |                  | PORTC is a bidirectional I/O port.                                            |  |  |

| RC0/T10S0/T13CKI  | 11             | 8        |             |                  |                                                                               |  |  |

| RC0               |                |          | I/O         | ST               | Digital I/O.                                                                  |  |  |

| T1OSO             |                |          | 0           | _                | Timer1 oscillator output.                                                     |  |  |

| T13CKI            |                |          | I           | ST               | Timer1/Timer3 external clock input.                                           |  |  |

| RC1/T10SI         | 12             | 9        |             |                  |                                                                               |  |  |

| RC1               |                |          | I/O         | ST               | Digital I/O.                                                                  |  |  |

| T1OSI             |                |          | I           | CMOS             | Timer1 oscillator input.                                                      |  |  |

| RC2/CCP1          | 13             | 10       |             |                  |                                                                               |  |  |

| RC2               |                |          | I/O         | ST               | Digital I/O.                                                                  |  |  |

| CCP1              |                |          | I/O         | ST               | Capture 1 input/Compare 1 output/PWM1 output.                                 |  |  |

| RC3/SCK/SCL       | 14             | 11       |             |                  |                                                                               |  |  |

| RC3               |                |          | I/O         | ST               | Digital I/O.                                                                  |  |  |

| SCK               |                |          | I/O         | ST               | Synchronous serial clock input/output for SPI mode.                           |  |  |

| SCL               |                |          | I/O         | l <sup>2</sup> C | Synchronous serial clock input/output for I <sup>2</sup> C <sup>™</sup> mode. |  |  |

| RC4/SDI/SDA       | 15             | 12       |             |                  |                                                                               |  |  |

| RC4               |                |          | I/O         | ST               | Digital I/O.                                                                  |  |  |

| SDI               |                |          | Ι           | ST               | SPI data in.                                                                  |  |  |

| SDA               |                |          | I/O         | I <sup>2</sup> C | I <sup>2</sup> C data I/O.                                                    |  |  |

| RC5/SDO           | 16             | 13       |             |                  |                                                                               |  |  |

| RC5               |                |          | I/O         | ST               | Digital I/O.                                                                  |  |  |

| SDO               |                |          | 0           | —                | SPI data out.                                                                 |  |  |

| RC6/TX/CK         | 17             | 14       |             |                  |                                                                               |  |  |

| RC6               |                |          | I/O         | ST               | Digital I/O.                                                                  |  |  |

| ТХ                |                |          | 0           | —                | EUSART asynchronous transmit.                                                 |  |  |

| CK                |                |          | I/O         | ST               | EUSART synchronous clock (see related RX/DT).                                 |  |  |

| RC7/RX/DT         | 18             | 15       |             |                  |                                                                               |  |  |

| RC7               |                |          | I/O         | ST               | Digital I/O.                                                                  |  |  |

| RX                |                |          | Ι           | ST               | EUSART asynchronous receive.                                                  |  |  |

| DT                |                |          | I/O         | ST               | EUSART synchronous data (see related TX/CK).                                  |  |  |

| RE3               |                | _        |             |                  | See MCLR/VPP/RE3 pin.                                                         |  |  |

| Vss               | 8, 19          | 5, 16    | Р           | _                | Ground reference for logic and I/O pins.                                      |  |  |

| Vdd               | 20             | 17       | Р           | —                | Positive supply for logic and I/O pins.                                       |  |  |

| Legend: TTL = TTL |                |          |             |                  | CMOS = CMOS compatible input or output                                        |  |  |

| ST = Sch          |                | ger inpu | it with (   | CMOS lev         | vels I = Input                                                                |  |  |

#### **TABLE 1-2:** PIC18F2480/2580 PINOUT I/O DESCRIPTIONS (CONTINUED)

Ρ = Power

O = Output  $I^2C$  =  $I^2C^{TM}$ /SMBus input buffer

| Pin Name                                              | Pin Number |     |      | Pin                    | Buffer                 | Description                                                                                                                                                                           |

|-------------------------------------------------------|------------|-----|------|------------------------|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Name                                              | PDIP       | QFN | TQFP | Туре                   | Туре                   | Description                                                                                                                                                                           |

|                                                       |            |     |      |                        |                        | PORTD is a bidirectional I/O port or a Parallel Slave<br>Port (PSP) for interfacing to a microprocessor port.<br>These pins have TTL input buffers when the PSP<br>module is enabled. |

| RD0/PSP0/C1IN+<br>RD0<br>PSP0<br>C1IN+                | 19         | 38  | 38   | I/O<br>I/O<br>I        | ST<br>TTL<br>Analog    | Digital I/O.<br>Parallel Slave Port data.<br>Comparator 1 input (+).                                                                                                                  |

| RD1/PSP1/C1IN-<br>RD1<br>PSP1<br>C1IN-                | 20         | 39  | 39   | I/O<br>I/O<br>I        | ST<br>TTL<br>Analog    | Digital I/O.<br>Parallel Slave Port data.<br>Comparator 1 input (-)                                                                                                                   |

| RD2/PSP2/C2IN+<br>RD2<br>PSP2<br>C2IN+                | 21         | 40  | 40   | I/O<br>I/O<br>I        | ST<br>TTL<br>Analog    | Digital I/O.<br>Parallel Slave Port data.<br>Comparator 2 input (+).                                                                                                                  |

| RD3/PSP3/C2IN-<br>RD3<br>PSP3<br>C2IN-                | 22         | 41  | 41   | I/O<br>I/O<br>I        | ST<br>TTL<br>Analog    | Digital I/O.<br>Parallel Slave Port data.<br>Comparator 2 input (-).                                                                                                                  |

| RD4/PSP4/ECCP1/<br>P1A<br>RD4<br>PSP4<br>ECCP1<br>P1A | 27         | 2   | 2    | I/O<br>I/O<br>I/O<br>O | ST<br>TTL<br>ST<br>TTL | Digital I/O.<br>Parallel Slave Port data.<br>Capture 2 input/Compare 2 output/PWM2 output.<br>ECCP1 PWM Output A.                                                                     |

| RD5/PSP5/P1B<br>RD5<br>PSP5<br>P1B                    | 28         | 3   | 3    | I/O<br>I/O<br>O        | ST<br>TTL<br>TTL       | Digital I/O.<br>Parallel Slave Port data.<br>ECCP1 PWM Output B.                                                                                                                      |

| RD6/PSP6/P1C<br>RD6<br>PSP6<br>P1C                    | 29         | 4   | 4    | I/O<br>I/O<br>O        | ST<br>TTL<br>TTL       | Digital I/O.<br>Parallel Slave Port data.<br>ECCP1 PWM Output C.                                                                                                                      |

| RD7/PSP7/P1D<br>RD7<br>PSP7                           | 30         | 5   | 5    | I/O<br>I/O<br>O        | ST<br>TTL<br>TTL       | Digital I/O.<br>Parallel Slave Port data.<br>ECCP1 PWM Output D.                                                                                                                      |

### TABLE 1-3: PIC18F4480/4580 PINOUT I/O DESCRIPTIONS (CONTINUED)

O = Output  $I^2C = I^2C^{TM}/SMBus input buffer$

### 2.2 Power Supply Pins

### 2.2.1 DECOUPLING CAPACITORS

The use of decoupling capacitors on every pair of power supply pins, such as VDD, VSS, AVDD and AVSS, is required.

Consider the following criteria when using decoupling capacitors:

- Value and type of capacitor: A 0.1  $\mu$ F (100 nF), 10-20V capacitor is recommended. The capacitor should be a low-ESR device, with a resonance frequency in the range of 200 MHz and higher. Ceramic capacitors are recommended.

- Placement on the printed circuit board: The decoupling capacitors should be placed as close to the pins as possible. It is recommended to place the capacitors on the same side of the board as the device. If space is constricted, the capacitor can be placed on another layer on the PCB using a via; however, ensure that the trace length from the pin to the capacitor is no greater than 0.25 inch (6 mm).

- Handling high-frequency noise: If the board is experiencing high-frequency noise (upward of tens of MHz), add a second ceramic type capacitor in parallel to the above described decoupling capacitor. The value of the second capacitor can be in the range of 0.01  $\mu$ F to 0.001  $\mu$ F. Place this second capacitor next to each primary decoupling capacitor. In high-speed circuit designs, consider implementing a decade pair of capacitances as close to the power and ground pins as possible (e.g., 0.1  $\mu$ F in parallel with 0.001  $\mu$ F).

- Maximizing performance: On the board layout from the power supply circuit, run the power and return traces to the decoupling capacitors first, and then to the device pins. This ensures that the decoupling capacitors are first in the power chain. Equally important is to keep the trace length between the capacitor and the power pins to a minimum, thereby reducing PCB trace inductance.

### 2.2.2 TANK CAPACITORS

On boards with power traces running longer than six inches in length, it is suggested to use a tank capacitor for integrated circuits, including microcontrollers, to supply a local power source. The value of the tank capacitor should be determined based on the trace resistance that connects the power supply source to the device, and the maximum current drawn by the device in the application. In other words, select the tank capacitor so that it meets the acceptable voltage sag at the device. Typical values range from 4.7  $\mu$ F to 47  $\mu$ F.

### 2.2.3 CONSIDERATIONS WHEN USING BOR

When the Brown-out Reset (BOR) feature is enabled, a sudden change in VDD may result in a spontaneous BOR event. This can happen when the microcontroller is operating under normal operating conditions, regardless of what the BOR set point has been programmed to, and even if VDD does not approach the set point. The precipitating factor in these BOR events is a rise or fall in VDD with a slew rate faster than  $0.15V/\mu s$ .

An application that incorporates adequate decoupling between the power supplies will not experience such rapid voltage changes. Additionally, the use of an electrolytic tank capacitor across VDD and Vss, as described above, will be helpful in preventing high slew rate transitions.

If the application has components that turn on or off, and share the same VDD circuit as the microcontroller, the BOR can be disabled in software by using the SBOREN bit before switching the component. Afterwards, allow a small delay before re-enabling the BOR. By doing this, it is ensured that the BOR is disabled during the interval that might cause high slew rate changes of VDD.

Note: Not all devices incorporate software BOR control. See Section 5.0 "Reset" for device-specific information.

## TABLE 3-2:CAPACITOR SELECTION FOR<br/>CRYSTAL OSCILLATOR

| Crystal | Typical Capacitor Values<br>Tested:                           |                                                                                                                                                                                                                    |  |  |

|---------|---------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| гіеч    | C1                                                            | C2                                                                                                                                                                                                                 |  |  |

| 32 kHz  | 33 pF                                                         | 33 pF                                                                                                                                                                                                              |  |  |

| 200 kHz | 15 pF                                                         | 15 pF                                                                                                                                                                                                              |  |  |

| 1 MHz   | 33 pF                                                         | 33 pF                                                                                                                                                                                                              |  |  |

| 4 MHz   | 27 pF                                                         | 27 pF                                                                                                                                                                                                              |  |  |

| 4 MHz   | 27 pF                                                         | 27 pF                                                                                                                                                                                                              |  |  |

| 8 MHz   | 22 pF                                                         | 22 pF                                                                                                                                                                                                              |  |  |

| 20 MHz  | 15 pF                                                         | 15 pF                                                                                                                                                                                                              |  |  |

|         | Freq<br>32 kHz<br>200 kHz<br>1 MHz<br>4 MHz<br>4 MHz<br>8 MHz | Crystal<br>Freq         Tes           32 kHz         33 pF           200 kHz         15 pF           1 MHz         33 pF           4 MHz         27 pF           4 MHz         27 pF           8 MHz         22 pF |  |  |

### Capacitor values are for design guidance only.

These capacitors were tested with the crystals listed below for basic start-up and operation. **These values are not optimized.**

Different capacitor values may be required to produce acceptable oscillator operation. The user should test the performance of the oscillator over the expected VDD and temperature range for the application.

See the notes following this table for additional information.

| Crystals Used: |        |  |  |  |  |  |

|----------------|--------|--|--|--|--|--|

| 32 kHz         | 4 MHz  |  |  |  |  |  |

| 200 kHz        | 8 MHz  |  |  |  |  |  |

| 1 MHz          | 20 MHz |  |  |  |  |  |

- Note 1: Higher capacitance increases the stability of the oscillator but also increases the start-up time.

- When operating below 3V VDD, or when using certain ceramic resonators at any voltage, it may be necessary to use the HS mode or switch to a crystal oscillator.

- 3: Since each resonator/crystal has its own characteristics, the user should consult the resonator/crystal manufacturer for appropriate values of external components.

- 4: Rs may be required to avoid overdriving crystals with low drive level specification.

- Always verify oscillator performance over the VDD and temperature range that is expected for the application.

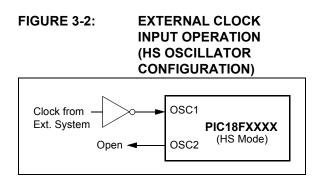

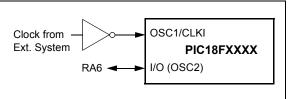

An external clock source may also be connected to the OSC1 pin in the HS mode, as shown in Figure 3-2.

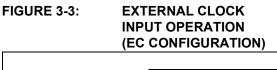

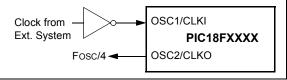

### 3.3 External Clock Input

The EC and ECIO Oscillator modes require an external clock source to be connected to the OSC1 pin. There is no oscillator start-up time required after a Power-on Reset or after an exit from Sleep mode.

In the EC Oscillator mode, the oscillator frequency divided by 4 is available on the OSC2 pin. This signal may be used for test purposes or to synchronize other logic. Figure 3-3 shows the pin connections for the EC Oscillator mode.

The ECIO Oscillator mode functions like the EC mode, except that the OSC2 pin becomes an additional general purpose I/O pin. The I/O pin becomes bit 6 of PORTA (RA6). Figure 3-4 shows the pin connections for the ECIO Oscillator mode.

### 3.7.1 OSCILLATOR CONTROL REGISTER

The OSCCON register (Register 3-2) controls several aspects of the device clock's operation, both in full-power operation and in power-managed modes.

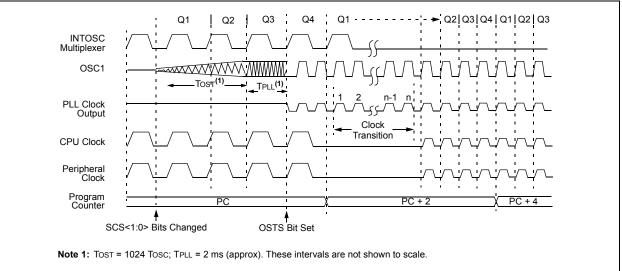

The System Clock Select bits, SCS<1:0>, select the clock source. The available clock sources are the primary clock (defined by the FOSC<3:0> Configuration bits), the secondary clock (Timer1 oscillator) and the internal oscillator block. The clock source changes immediately after one or more of the bits is written to, following a brief clock transition interval. The SCS bits are cleared on all forms of Reset.

The Internal Oscillator Frequency Select bits, IRCF<2:0>, select the frequency output of the internal oscillator block to drive the device clock. The choices are the INTRC source, the INTOSC source (8 MHz) or one of the frequencies derived from the INTOSC post-scaler (31 kHz to 4 MHz). If the internal oscillator block is supplying the device clock, changing the states of these bits will have an immediate change on the internal oscillator's output. On device Resets, the default output frequency of the internal oscillator block is set at 1 MHz.

When an output frequency of 31 kHz is selected (IRCF<2:0> = 000), users may choose which internal oscillator acts as the source. This is done with the INTSRC bit in the OSCTUNE register (OSCTUNE<7>). Setting this bit selects INTOSC as a 31.25 kHz clock source by enabling the divide-by-256 output of the INTOSC postscaler. Clearing INTSRC selects INTRC (nominally 31 kHz) as the clock source.

This option allows users to select the tunable and more precise INTOSC as a clock source, while maintaining power savings with a very low clock speed. Regardless of the setting of INTSRC, INTRC always remains the clock source for features such as the Watchdog Timer and the Fail-Safe Clock Monitor.

The OSTS, IOFS and T1RUN bits indicate which clock source is currently providing the device clock. The OSTS bit indicates that the Oscillator Start-up Timer (OST) has timed out and the primary clock is providing the device clock in primary clock modes. The IOFS bit indicates when the internal oscillator block has stabilized and is providing the device clock in RC Clock modes. The T1RUN bit (T1CON<6>) indicates when the Timer1 oscillator is providing the device clock in secondary clock modes. In power-managed modes, only one of these three bits will be set at any time. If none of these bits are set, the INTRC is providing the clock or the internal oscillator block has just started and is not yet stable. The IDLEN bit determines if the device goes into Sleep mode or one of the Idle modes when the SLEEP instruction is executed.

The use of the flag and control bits in the OSCCON register is discussed in more detail in **Section 4.0** "Power-Managed Modes".

- Note 1: The Timer1 oscillator must be enabled to select the secondary clock source. The Timer1 oscillator is enabled by setting the T1OSCEN bit in the Timer1 Control register (T1CON<3>). If the Timer1 oscillator is not enabled, then any attempt to select a secondary clock source when executing a SLEEP instruction will be ignored.

- 2: It is recommended that the Timer1 oscillator be operating and stable before executing the SLEEP instruction, or a very long delay may occur while the Timer1 oscillator starts.

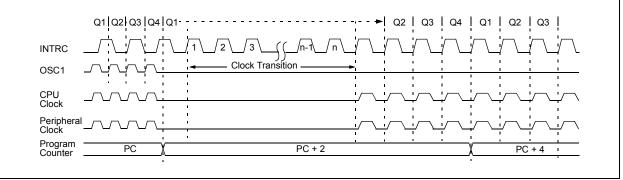

### 3.7.2 OSCILLATOR TRANSITIONS

PIC18F2480/2580/4480/4580 devices contain circuitry to prevent clock "glitches" when switching between clock sources. A short pause in the device clock occurs during the clock switch. The length of this pause is the sum of two cycles of the old clock source and three to four cycles of the new clock source. This formula assumes that the new clock source is stable.

Clock transitions are discussed in greater detail in **Section 4.1.2 "Entering Power-Managed Modes"**.

If the IRCF bits and the INTSRC bit are all clear, the INTOSC output is not enabled and the IOFS bit will remain clear; there will be no indication of the current clock source. The INTRC source is providing the device clocks.

If the IRCF bits are changed from all clear (thus, enabling the INTOSC output) or if INTSRC is set, the IOFS bit becomes set after the INTOSC output becomes stable. Clocks to the device continue while the INTOSC source stabilizes after an interval of TIOBST.

If the IRCF bits were previously at a non-zero value or if INTSRC was set before setting SCS1 and the INTOSC source was already stable, the IOFS bit will remain set. On transitions from RC\_RUN mode to PRI\_RUN mode, the device continues to be clocked from the INTOSC multiplexer while the primary clock is started. When the primary clock becomes ready, a clock switch to the primary clock occurs (see Figure 4-4). When the clock switch is complete, the IOFS bit is cleared, the OSTS bit is set and the primary clock is providing the device clock. The IDLEN and SCS bits are not affected by the switch. The INTRC source will continue to run if either the WDT or the Fail-Safe Clock Monitor is enabled.

| File Name | Bit 7   | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   | Value on<br>POR, BOR | Details on<br>Page: |

|-----------|---------|---------|---------|---------|---------|---------|---------|---------|----------------------|---------------------|

| TXB1D1    | TXB1D17 | TXB1D16 | TXB1D15 | TXB1D14 | TXB1D13 | TXB1D12 | TXB1D11 | TXB1D10 | XXXX XXXX            | 60, 290             |

| TXB1D0    | TXB1D07 | TXB1D06 | TXB1D05 | TXB1D04 | TXB1D03 | TXB1D02 | TXB1D01 | TXB1D00 | XXXX XXXX            | 60, 290             |

| TXB1DLC   | _       | TXRTR   | _       | _       | DLC3    | DLC2    | DLC1    | DLC0    | -x xxxx              | 60, 291             |

| TXB1EIDL  | EID7    | EID6    | EID5    | EID4    | EID3    | EID2    | EID1    | EID0    | XXXX XXXX            | 60, 290             |

| TXB1EIDH  | EID15   | EID14   | EID13   | EID12   | EID11   | EID10   | EID9    | EID8    | XXXX XXXX            | 60, 289             |

| TXB1SIDL  | SID2    | SID1    | SID0    | _       | EXIDE   |         | EID17   | EID16   | xxx- x-xx            | 60, 289             |

| TXB1SIDH  | SID10   | SID9    | SID8    | SID7    | SID6    | SID5    | SID4    | SID3    | XXXX XXXX            | 60, 289             |

| TXB1CON   | TXBIF   | TXABT   | TXLARB  | TXERR   | TXREQ   |         | TXPRI1  | TXPRI0  | 0000 0-00            | 60, 288             |

| TXB2D7    | TXB2D77 | TXB2D76 | TXB2D75 | TXB2D74 | TXB2D73 | TXB2D72 | TXB2D71 | TXB2D70 | XXXX XXXX            | 60, 290             |

| TXB2D6    | TXB2D67 | TXB2D66 | TXB2D65 | TXB2D64 | TXB2D63 | TXB2D62 | TXB2D61 | TXB2D60 | XXXX XXXX            | 61, 290             |

| TXB2D5    | TXB2D57 | TXB2D56 | TXB2D55 | TXB2D54 | TXB2D53 | TXB2D52 | TXB2D51 | TXB2D50 | XXXX XXXX            | 61, 290             |

| TXB2D4    | TXB2D47 | TXB2D46 | TXB2D45 | TXB2D44 | TXB2D43 | TXB2D42 | TXB2D41 | TXB2D40 | XXXX XXXX            | 61, 290             |

| TXB2D3    | TXB2D37 | TXB2D36 | TXB2D35 | TXB2D34 | TXB2D33 | TXB2D32 | TXB2D31 | TXB2D30 | XXXX XXXX            | 61, 290             |

| TXB2D2    | TXB2D27 | TXB2D26 | TXB2D25 | TXB2D24 | TXB2D23 | TXB2D22 | TXB2D21 | TXB2D20 | XXXX XXXX            | 61, 290             |

| TXB2D1    | TXB2D17 | TXB2D16 | TXB2D15 | TXB2D14 | TXB2D13 | TXB2D12 | TXB2D11 | TXB2D10 | XXXX XXXX            | 61, 290             |

| TXB2D0    | TXB2D07 | TXB2D06 | TXB2D05 | TXB2D04 | TXB2D03 | TXB2D02 | TXB2D01 | TXB2D00 | XXXX XXXX            | 61, 290             |

| TXB2DLC   | _       | TXRTR   | —       | _       | DLC3    | DLC2    | DLC1    | DLC0    | -x xxxx              | 61, 291             |

| TXB2EIDL  | EID7    | EID6    | EID5    | EID4    | EID3    | EID2    | EID1    | EID0    | XXXX XXXX            | 61, 290             |

| TXB2EIDH  | EID15   | EID14   | EID13   | EID12   | EID11   | EID10   | EID9    | EID8    | XXXX XXXX            | 61, 289             |

| TXB2SIDL  | SID2    | SID1    | SID0    | _       | EXIDE   |         | EID17   | EID16   | хххх х-хх            | 61, 289             |

| TXB2SIDH  | SID10   | SID9    | SID8    | SID7    | SID6    | SID5    | SID4    | SID3    | xxx- x-xx            | 61, 289             |

| TXB2CON   | TXBIF   | TXABT   | TXLARB  | TXERR   | TXREQ   |         | TXPRI1  | TXPRI0  | 0000 0-00            | 61, 288             |

| RXM1EIDL  | EID7    | EID6    | EID5    | EID4    | EID3    | EID2    | EID1    | EID0    | XXXX XXXX            | 61, 310             |

| RXM1EIDH  | EID15   | EID14   | EID13   | EID12   | EID11   | EID10   | EID9    | EID8    | XXXX XXXX            | 61, 310             |

| RXM1SIDL  | SID2    | SID1    | SID0    | _       | EXIDEN  |         | EID17   | EID16   | xxx- x-xx            | 61, 310             |

| RXM1SIDH  | SID10   | SID9    | SID8    | SID7    | SID6    | SID5    | SID4    | SID3    | XXXX XXXX            | 61, 310             |

| RXM0EIDL  | EID7    | EID6    | EID5    | EID4    | EID3    | EID2    | EID1    | EID0    | XXXX XXXX            | 61, 310             |

| RXM0EIDH  | EID15   | EID14   | EID13   | EID12   | EID11   | EID10   | EID9    | EID8    | XXXX XXXX            | 61, 310             |

| RXM0SIDL  | SID2    | SID1    | SID0    | _       | EXIDEN  | _       | EID17   | EID16   | xxx- x-xx            | 61, 310             |

| RXM0SIDH  | SID10   | SID9    | SID8    | SID7    | SID6    | SID5    | SID4    | SID3    | XXXX XXXX            | 61, 309             |

| RXF5EIDL  | EID7    | EID6    | EID5    | EID4    | EID3    | EID2    | EID1    | EID0    | XXXX XXXX            | 61, 309             |

| RXF5EIDH  | EID15   | EID14   | EID13   | EID12   | EID11   | EID10   | EID9    | EID8    | XXXX XXXX            | 61, 309             |

| RXF5SIDL  | SID2    | SID1    | SID0    | _       | EXIDEN  |         | EID17   | EID16   | xxx- x-xx            | 61, 308             |

| RXF5SIDH  | SID10   | SID9    | SID8    | SID7    | SID6    | SID5    | SID4    | SID3    | XXXX XXXX            | 61, 308             |

| RXF4EIDL  | EID7    | EID6    | EID5    | EID4    | EID3    | EID2    | EID1    | EID0    | XXXX XXXX            | 61, 309             |

| RXF4EIDH  | EID15   | EID14   | EID13   | EID12   | EID11   | EID10   | EID9    | EID8    | XXXX XXXX            | 61, 309             |

| RXF4SIDL  | SID2    | SID1    | SID0    | —       | EXIDEN  | _       | EID17   | EID16   | xxx- x-xx            | 61, 308             |

| RXF4SIDH  | SID10   | SID9    | SID8    | SID7    | SID6    | SID5    | SID4    | SID3    | XXXX XXXX            | 61, 308             |

| RXF3EIDL  | EID7    | EID6    | EID5    | EID4    | EID3    | EID2    | EID1    | EID0    | XXXX XXXX            | 61, 309             |

| RXF3EIDH  | EID15   | EID14   | EID13   | EID12   | EID11   | EID10   | EID9    | EID8    | XXXX XXXX            | 61, 309             |

| RXF3SIDL  | SID2    | SID1    | SID0    | _       | EXIDEN  | _       | EID17   | EID16   | xxx- x-xx            | 62, 308             |

### TABLE 6-2:REGISTER FILE SUMMARY (PIC18F2480/2580/4480/4580) (CONTINUED)

$\label{eq:logend: x = unknown, u = unchanged, - = unimplemented, q = value depends on condition$

Note 1: Bit 21 of the PC is only available in Test mode and Serial Programming modes.

The SBOREN bit is only available when CONFIG2L<1:0> = 01; otherwise, it is disabled and reads as '0'. See Section 5.4 "Brown-out Reset (BOR)".

These registers and/or bits are not implemented on PIC18F2X80 devices and are read as '0'. Reset values are shown for PIC18F4X80 devices;

These registers and/or bits are not implemented on PiC for 2X60 devices and are read as "0". Reset values are shown for PiC for 4X60 devices, individual unimplemented bits should be interpreted as '—'.

The PLLEN bit is only available in specific oscillator configuration; otherwise, it is disabled and reads as '0'. See Section 3.6.4 "PLL in INTOSC

4: The PLLEN bit is only available in specific oscillator configuration; otherwise, it is disabled and reads as '0'. See Section 3.6.4 "PLL in INTOS' Modes".

5: The RE3 bit is only available when Master Clear Reset is disabled (CONFIG3H<7> = 0); otherwise, RE3 reads as '0'. This bit is read-only.

6: RA6/RA7 and their associated latch and direction bits are individually configured as port pins based on various primary oscillator modes. When disabled, these bits read as '0'.

7: CAN bits have multiple functions depending on the selected mode of the CAN module.

8: This register reads all '0's until the ECAN™ technology is set up in Mode 1 or Mode 2.

9: These registers are available on PIC18F4X80 devices only.

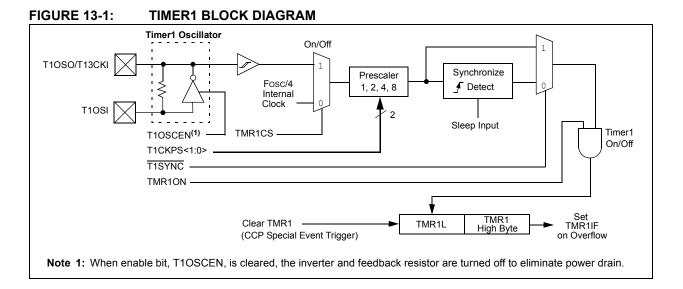

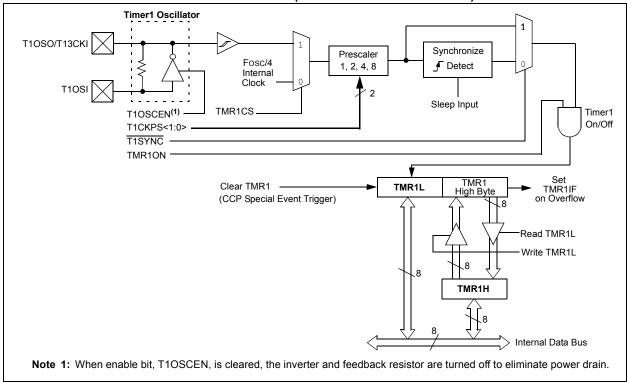

### 13.1 Timer1 Operation

Timer1 can operate in one of these modes:

- Timer

- Synchronous Counter

- Asynchronous Counter

The operating mode is determined by the clock select bit, TMR1CS (T1CON<1>). When TMR1CS is cleared (= 0), Timer1 increments on every internal instruction

cycle (Fosc/4). When the bit is set, Timer1 increments on every rising edge of the Timer1 external clock input or the Timer1 oscillator, if enabled.

When Timer1 is enabled, the RC1/T1OSI and RC0/T10SO/T13CKI pins become inputs. This means the values of TRISC<1:0> are ignored and the pins are read as '0'.

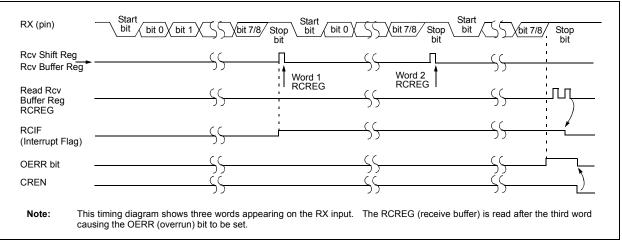

### FIGURE 19-7: ASYNCHRONOUS RECEPTION

### TABLE 19-6: REGISTERS ASSOCIATED WITH ASYNCHRONOUS RECEPTION

| Name    | Bit 7                                          | Bit 6       | Bit 5       | Bit 4       | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on Page: |

|---------|------------------------------------------------|-------------|-------------|-------------|-------|--------|--------|--------|-----------------------------|

| INTCON  | GIE/GIEH                                       | PEIE/GIEL   | TMR0IE      | INT0IE      | RBIE  | TMR0IF | INT0IF | RBIF   | 55                          |

| PIR1    | PSPIF <sup>(1)</sup>                           | ADIF        | RCIF        | TXIF        | SSPIF | CCP1IF | TMR2IF | TMR1IF | 58                          |

| PIE1    | PSPIE <sup>(1)</sup>                           | ADIE        | RCIE        | TXIE        | SSPIE | CCP1IE | TMR2IE | TMR1IE | 58                          |

| IPR1    | PSPIP <sup>(1)</sup>                           | ADIP        | RCIP        | TXIP        | SSPIP | CCP1IP | TMR2IP | TMR1IP | 58                          |

| RCSTA   | SPEN                                           | RX9         | SREN        | CREN        | ADDEN | FERR   | OERR   | RX9D   | 57                          |

| RCREG   | EUSART F                                       | Receive Reg | ister       |             |       |        |        |        | 57                          |

| TXSTA   | CSRC                                           | TX9         | TXEN        | SYNC        | SENDB | BRGH   | TRMT   | TX9D   | 57                          |

| BAUDCON | ABDOVF                                         | RCIDL       | _           | SCKP        | BRG16 | _      | WUE    | ABDEN  | 57                          |

| SPBRGH  | EUSART Baud Rate Generator Register, High Byte |             |             |             |       |        |        |        | 57                          |

| SPBRG   | EUSART E                                       | Baud Rate G | enerator Re | gister, Low | Byte  |        |        |        | 57                          |

**Legend:** — = unimplemented locations read as '0'. Shaded cells are not used for asynchronous reception.

**Note 1:** Reserved in PIC18F2X80 devices; always maintain these bits clear.

NOTES:

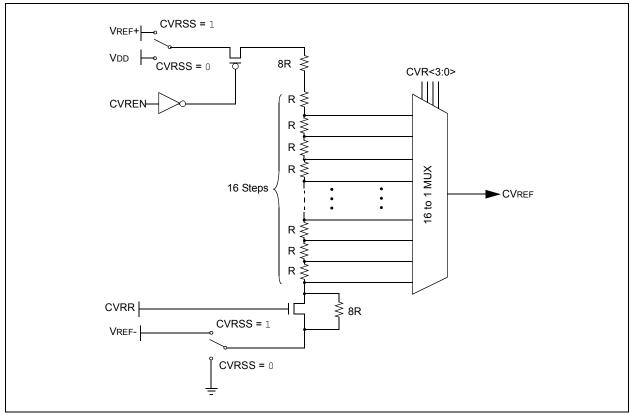

### 22.0 COMPARATOR VOLTAGE REFERENCE MODULE

The comparator voltage reference is a 16-tap resistor ladder network that provides a selectable reference voltage. Although its primary purpose is to provide a reference for the analog comparators, it may also be used independently of them.

A block diagram is of the module shown in Figure 22-1.The resistor ladder is segmented to provide two ranges of CVREF values and has a power-down function to conserve power when the reference is not being used. The module's supply reference can be provided from either device VDD/Vss or an external voltage reference.

### 22.1 Configuring the Comparator Voltage Reference

The voltage reference module is controlled through the CVRCON register (Register 22-1). The comparator voltage reference provides two ranges of output voltage,

each with 16 distinct levels. The range to be used is selected by the CVRR bit (CVRCON<5>). The primary difference between the ranges is the size of the steps selected by the CVREF Selection bits (CVR<3:0>), with one range offering finer resolution. The equations used to calculate the output of the comparator voltage reference are as follows:

```

<u>If CVRR = 1:</u>

CVREF = ((CVR<3:0>)/24) x CVRSRC

<u>If CVRR = 0:</u>

CVREF = (CVDD x 1/4) + (((CVR<3:0>)/32) x

CVRSRC)

```

The comparator reference supply voltage can come from either VDD and VSS, or the external VREF+ and VREF- that are multiplexed with RA2 and RA3. The voltage source is selected by the CVRSS bit (CVRCON<4>).

The settling time of the comparator voltage reference must be considered when changing the CVREF output (see Table 28-3 in Section 28.0 "Electrical Characteristics").

### REGISTER 22-1: CVRCON: COMPARATOR VOLTAGE REFERENCE CONTROL REGISTER

| R/W-0       | R/W-0                | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------------|----------------------|-------|-------|-------|-------|-------|-------|

| CVREN       | CVROE <sup>(1)</sup> | CVRR  | CVRSS | CVR3  | CVR2  | CVR1  | CVR0  |

| bit 7 bit 0 |                      |       |       |       |       |       |       |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 7   | CVREN: Comparator Voltage Reference Enable bit                                                                                                            |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <ul> <li>1 = CVREF circuit powered on</li> <li>0 = CVREF circuit powered down</li> </ul>                                                                  |

| bit 6   | CVROE: Comparator VREF Output Enable bit <sup>(1)</sup>                                                                                                   |

|         | <ul> <li>1 = CVREF voltage level is also output on the RA0/AN0/CVREF pin</li> <li>0 = CVREF voltage is disconnected from the RA0/AN0/CVREF pin</li> </ul> |

| bit 5   | CVRR: Comparator VREF Range Selection bit                                                                                                                 |

|         | <ul> <li>1 = 0.00 CVRsRc to 0.75 CVRsRc, with CVRsRc/24 step size</li> <li>0 = 0.25 CVRsRc to 0.75 CVRsRc, with CVRsRc/32 step size</li> </ul>            |

| bit 4   | CVRSS: Comparator VREF Source Selection bit                                                                                                               |

|         | <ul> <li>1 = Comparator reference source, CVRSRC = (VREF+) – (VREF-)</li> <li>0 = Comparator reference source, CVRSRC = VDD – VSS</li> </ul>              |

| bit 3-0 | <b>CVR&lt;3:0&gt;:</b> Comparator VREF Value Selection bits ( $0 \le (CVR<3:0>) \le 15$ )                                                                 |

|         | When CVRR = 1:                                                                                                                                            |

|         | $CVREF = ((CVR < 3:0 >)/24) \bullet (CVRSRC)$                                                                                                             |

|         | When CVRR = 0:                                                                                                                                            |

|         | $CVREF = (CVRSRC/4) + ((CVR<3:0>)/32) \bullet (CVRSRC)$                                                                                                   |

|         |                                                                                                                                                           |

**Note 1:** CVROE overrides the TRISA<0> bit setting. If enabled for output, RA2 must also be configured as an input by setting TRISA<2> to '1'.

### FIGURE 22-1: COMPARATOR VOLTAGE REFERENCE BLOCK DIAGRAM

### 22.2 Voltage Reference Accuracy/Error

The full range of voltage reference cannot be realized due to the construction of the module. The transistors on the top and bottom of the resistor ladder network (Figure 22-1) keep CVREF from approaching the reference source rails. The voltage reference is derived from the reference source; therefore, the CVREF output changes with fluctuations in that source. The tested absolute accuracy of the voltage reference can be found in **Section 28.0 "Electrical Characteristics"**.

### 22.3 Operation During Sleep

When the device wakes up from Sleep through an interrupt or a Watchdog Timer time-out, the contents of the CVRCON register are not affected. To minimize current consumption in Sleep mode, the voltage reference should be disabled.

### 22.4 Effects of a Reset

A device Reset disables the voltage reference by clearing bit, CVREN (CVRCON<7>). This Reset also disconnects the reference from the RA0 pin by clearing bit, CVROE (CVRCON<6>), and selects the high-voltage range by clearing bit, CVRR (CVRCON<5>). The CVR value select bits are also cleared.

### 22.5 Connection Considerations

The voltage reference module operates independently of the comparator module. The output of the reference generator may be connected to the RA0 pin if the TRISA<0> bit and the CVROE bit are both set. Enabling the voltage reference output onto the RA0 pin, with an input signal present, will increase current consumption. Connecting RA0 as a digital output with CVRSS enabled will also increase current consumption.

The RA0 pin can be used as a simple D/A output with limited drive capability. Due to the limited current drive capability, a buffer must be used on the voltage reference output for external connections to VREF. Figure 22-2 shows an example buffering technique.

# $\label{eq:register24-28: BnEIDH: TX/RX BUFFER n EXTENDED IDENTIFIER REGISTERS, \\ HIGH BYTE IN RECEIVE MODE [0 \le n \le 5, TXnEN (BSEL0<n>) = 0]^{(1)}$

| R-x     | R-x   | R-x   | R-x   | R-x   | R-x   | R-x  | R-x   |

|---------|-------|-------|-------|-------|-------|------|-------|

| EID15   | EID14 | EID13 | EID12 | EID11 | EID10 | EID9 | EID8  |

| bit 7   |       |       |       |       |       |      | bit 0 |

|         |       |       |       |       |       |      |       |

| Legend: |       |       |       |       |       |      |       |

| Legenu.           |                  |                            |                    |  |  |

|-------------------|------------------|----------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | it, read as '0'    |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |  |  |

bit 7-0 EID<15:8>: Extended Identifier bits

Note 1: These registers are available in Mode 1 and 2 only.

## $\label{eq:register24-29: BnEIDH: TX/RX BUFFER n EXTENDED IDENTIFIER REGISTERS, \\ HIGH BYTE IN TRANSMIT MODE [0 \le n \le 5, TXnEN (BSEL0<n>) = 1]^{(1)}$

| R/W-x |

|-------|-------|-------|-------|-------|-------|-------|-------|

| EID15 | EID14 | EID13 | EID12 | EID11 | EID10 | EID9  | EID8  |

| bit 7 |       |       |       |       |       |       | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | l as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 7-0 EID<15:8>: Extended Identifier bits

Note 1: These registers are available in Mode 1 and 2 only.

# $\label{eq:register24-30:BnEIDL: TX/RX BUFFER n EXTENDED IDENTIFIER REGISTERS, \\ LOW BYTE IN RECEIVE MODE [0 \le n \le 5, TXnEN (BSEL<n>) = 0]^{(1)}$

| R-x             | R-x  | R-x              | R-x  | R-x              | R-x              | R-x             | R-x   |

|-----------------|------|------------------|------|------------------|------------------|-----------------|-------|

| EID7            | EID6 | EID5             | EID4 | EID3             | EID2             | EID1            | EID0  |

| bit 7           |      |                  |      |                  |                  |                 | bit 0 |

|                 |      |                  |      |                  |                  |                 |       |

| Legend:         |      |                  |      |                  |                  |                 |       |

| R = Readable    | bit  | W = Writable     | bit  | U = Unimpler     | mented bit, read | as '0'          |       |

| -n = Value at F | POR  | '1' = Bit is set |      | '0' = Bit is cle | ared             | x = Bit is unkr | nown  |

bit 7-0 EID<7:0>: Extended Identifier bits

Note 1: These registers are available in Mode 1 and 2 only.

| R/W-0         | R/W-0                          | R/W-0            | R/W-0           | R/W-0            | R/W-0            | R/W-0           | R/W-0   |

|---------------|--------------------------------|------------------|-----------------|------------------|------------------|-----------------|---------|

| FIL15_1       | FIL15_0                        | FIL14_1          | FIL14_0         | FIL13_1          | FIL13_0          | FIL12_1         | FIL12_0 |

| bit 7         |                                |                  |                 |                  |                  |                 | bit C   |

|               |                                |                  |                 |                  |                  |                 |         |

| Legend:       |                                |                  |                 |                  |                  |                 |         |

| R = Readable  | e bit                          | W = Writable     | bit             | U = Unimpler     | mented bit, read | l as '0'        |         |

| -n = Value at | POR                            | '1' = Bit is set | t               | '0' = Bit is cle | ared             | x = Bit is unki | nown    |

|               |                                |                  |                 |                  |                  |                 |         |

| bit 7-6       | FIL15_<1:0>:                   | : Filter 15 Sele | ct bits 1 and 0 |                  |                  |                 |         |

|               | 11 = No masl                   | -                |                 |                  |                  |                 |         |

|               | 10 = Filter 15<br>01 = Accepta |                  |                 |                  |                  |                 |         |

|               | 00 = Accepta                   |                  |                 |                  |                  |                 |         |

| bit 5-4       | FIL14_<1:0>:                   | : Filter 14 Sele | ct bits 1 and 0 |                  |                  |                 |         |

|               | 11 = No masl                   | k                |                 |                  |                  |                 |         |

|               | 10 = Filter 15                 |                  |                 |                  |                  |                 |         |

|               | 01 = Accepta<br>00 = Accepta   |                  |                 |                  |                  |                 |         |

| bit 3-2       | •                              | : Filter 13 Sele | ct bits 1 and 0 |                  |                  |                 |         |

|               | 11 = No masl                   |                  |                 |                  |                  |                 |         |

|               | 10 = Filter 15                 |                  |                 |                  |                  |                 |         |

|               | 01 = Accepta                   |                  |                 |                  |                  |                 |         |

| h:4 0         | 00 = Accepta                   |                  |                 |                  |                  |                 |         |

| bit 1-0       | 11 = No mas                    | : Filter 12 Sele | ct bits 1 and 0 |                  |                  |                 |         |

|               | 10 = Filter 15                 | -                |                 |                  |                  |                 |         |

|               | 01 = Accepta                   |                  |                 |                  |                  |                 |         |

|               | 00 = Accepta                   | nce Mask 0       |                 |                  |                  |                 |         |

|               |                                |                  |                 |                  |                  |                 |         |

### REGISTER 24-51: MSEL3: MASK SELECT REGISTER 3<sup>(1)</sup>

**Note 1:** This register is available in Mode 1 and 2 only.

### 24.13 Bit Timing Configuration Registers

The Baud Rate Control registers (BRGCON1, BRGCON2, BRGCON3) control the bit timing for the CAN bus interface. These registers can only be modified when the PIC18F2480/2580/4480/4580 devices are in Configuration mode.

### 24.13.1 BRGCON1

The BRP bits control the baud rate prescaler. The SJW<1:0> bits select the synchronization jump width in terms of multiples of TQ.

### 24.13.2 BRGCON2

The PRSEG bits set the length of the propagation segment in terms of Tq. The SEG1PH bits set the length of Phase Segment 1 in To. The SAM bit controls how many times the RXCAN pin is sampled. Setting this bit to a '1' causes the bus to be sampled three times: twice at TQ/2 before the sample point and once at the normal sample point (which is at the end of Phase Segment 1). The value of the bus is determined to be the value read during at least two of the samples. If the SAM bit is set to a '0', then the RXCAN pin is sampled only once at the sample point. The SEG2PHTS bit controls how the length of Phase Segment 2 is determined. If this bit is set to a '1', then the length of Phase Segment 2 is determined by the SEG2PH bits of BRGCON3. If the SEG2PHTS bit is set to a '0', then the length of Phase Segment 2 is the greater of Phase Segment 1 and the information processing time (which is fixed at 2 To for the PIC18F2480/2580/4480/4580).

### 24.13.3 BRGCON3

The PHSEG2<2:0> bits set the length (in TQ) of Phase Segment 2 if the SEG2PHTS bit is set to a '1'. If the SEG2PHTS bit is set to a '0', then the PHSEG2<2:0> bits have no effect.

### 24.14 Error Detection

The CAN protocol provides sophisticated error detection mechanisms. The following errors can be detected.

### 24.14.1 CRC ERROR

With the Cyclic Redundancy Check (CRC), the transmitter calculates special check bits for the bit sequence, from the start of a frame until the end of the data field. This CRC sequence is transmitted in the CRC field. The receiving node also calculates the CRC sequence using the same formula and performs a comparison to the received sequence. If a mismatch is detected, a CRC error has occurred and an error frame is generated. The message is repeated.

### 24.14.2 ACKNOWLEDGE ERROR

In the Acknowledge field of a message, the transmitter checks if the Acknowledge slot (which was sent out as a recessive bit) contains a dominant bit. If not, no other node has received the frame correctly. An Acknowledge error has occurred, an error frame is generated and the message will have to be repeated.

### 24.14.3 FORM ERROR

If a node detects a dominant bit in one of the four segments, including End-Of-Frame (EOF), interframe space, Acknowledge delimiter or CRC delimiter, then a form error has occurred and an error frame is generated. The message is repeated.

### 24.14.4 BIT ERROR

A bit error occurs if a transmitter sends a dominant bit and detects a recessive bit, or if it sends a recessive bit and detects a dominant bit, when monitoring the actual bus level and comparing it to the just transmitted bit. In the case where the transmitter sends a recessive bit and a dominant bit is detected during the arbitration field and the Acknowledge slot, no bit error is generated because normal arbitration is occurring.

### 24.14.5 STUFF BIT ERROR

If, between the Start-Of-Frame (SOF) and the CRC delimiter, six consecutive bits with the same polarity are detected, the bit stuffing rule has been violated. A stuff bit error occurs and an error frame is generated. The message is repeated.

### 24.14.6 ERROR STATES

Detected errors are made public to all other nodes via error frames. The transmission of the erroneous message is aborted and the frame is repeated as soon as possible. Furthermore, each CAN node is in one of the three error states; "error-active", "error-passive" or "bus-off", according to the value of the internal error counters. The error-active state is the usual state where the bus node can transmit messages and activate error frames (made of dominant bits) without any restrictions. In the error-passive state, messages and passive error frames (made of recessive bits) may be transmitted. The bus-off state makes it temporarily impossible for the node to participate in the bus communication. During this state, messages can neither be received nor transmitted.

### 24.14.7 ERROR MODES AND ERROR COUNTERS

The PIC18F2480/2580/4480/4580 devices contain two error counters: the Receive Error Counter (RXERRCNT) and the Transmit Error Counter (TXERRCNT). The values of both counters can be read by the MCU. These counters are incremented or decremented in accordance with the CAN bus specification.

| TABLE 26  | 9-2: PI |                                | ET (CON    | INUE | U)        |          |      | 1         |       |

|-----------|---------|--------------------------------|------------|------|-----------|----------|------|-----------|-------|

| Mnemo     | onic,   | Description                    | Cycles     | 16-E | Bit Instr | uction V | Vord | Status    | Notes |

| Opera     | inds    | Description                    | Cycles     | MSb  |           |          | LSb  | Affected  | notes |

| BIT-ORIEN | ITED OP | ERATIONS                       |            |      |           |          |      |           |       |

| BCF       | f, b, a | Bit Clear f                    | 1          | 1001 | bbba      | ffff     | ffff | None      | 1, 2  |

| BSF       |         | Bit Set f                      | 1          | 1000 | bbba      | ffff     | ffff | None      | 1, 2  |

| BTFSC     | f, b, a | Bit Test f, Skip if Clear      | 1 (2 or 3) | 1011 | bbba      | ffff     | ffff | None      | 3, 4  |

| BTFSS     | f, b, a | Bit Test f, Skip if Set        | 1 (2 or 3) | 1010 | bbba      | ffff     | ffff | None      | 3, 4  |

| BTG       | f, b, a | Bit Toggle f                   | 1          | 0111 | bbba      | ffff     | ffff | None      | 1, 2  |

| CONTROL   | . OPERA | TIONS                          |            |      |           |          |      |           |       |

| BC        | n       | Branch if Carry                | 1 (2)      | 1110 | 0010      | nnnn     | nnnn | None      |       |

| BN        | n       | Branch if Negative             | 1 (2)      | 1110 | 0110      | nnnn     | nnnn | None      |       |

| BNC       | n       | Branch if Not Carry            | 1 (2)      | 1110 | 0011      | nnnn     | nnnn | None      |       |

| BNN       | n       | Branch if Not Negative         | 1 (2)      | 1110 | 0111      | nnnn     | nnnn | None      |       |

| BNOV      | n       | Branch if Not Overflow         | 1 (2)      | 1110 | 0101      | nnnn     | nnnn | None      |       |

| BNZ       | n       | Branch if Not Zero             | 1 (2)      | 1110 | 0001      | nnnn     | nnnn | None      |       |

| BOV       | n       | Branch if Overflow             | 1 (2)      | 1110 | 0100      | nnnn     | nnnn | None      |       |

| BRA       | n       | Branch Unconditionally         | 2          | 1101 | 0nnn      | nnnn     | nnnn | None      |       |

| BZ        | n       | Branch if Zero                 | 1 (2)      | 1110 | 0000      | nnnn     | nnnn | None      |       |

| CALL      | n, s    | Call Subroutine 1st word       | 2          | 1110 | 110s      | kkkk     | kkkk | None      |       |

|           |         | 2nd word                       |            | 1111 | kkkk      | kkkk     | kkkk |           |       |

| CLRWDT    | _       | Clear Watchdog Timer           | 1          | 0000 | 0000      | 0000     | 0100 | TO, PD    |       |

| DAW       | _       | Decimal Adjust WREG            | 1          | 0000 | 0000      | 0000     | 0111 | С         |       |

| GOTO      | n       | Go to Address 1st word         | 2          | 1110 | 1111      | kkkk     | kkkk | None      |       |

|           |         | 2nd word                       |            | 1111 | kkkk      | kkkk     | kkkk |           |       |

| NOP       | —       | No Operation                   | 1          | 0000 | 0000      | 0000     | 0000 | None      |       |

| NOP       | —       | No Operation                   | 1          | 1111 | XXXX      | XXXX     | XXXX | None      | 4     |

| POP       | —       | Pop Top of Return Stack (TOS)  | 1          | 0000 | 0000      | 0000     | 0110 | None      |       |

| PUSH      | —       | Push Top of Return Stack (TOS) | 1          | 0000 | 0000      | 0000     | 0101 | None      |       |

| RCALL     | n       | Relative Call                  | 2          | 1101 | 1nnn      | nnnn     | nnnn | None      |       |

| RESET     |         | Software Device Reset          | 1          | 0000 | 0000      | 1111     |      | All       |       |

| RETFIE    | S       | Return from Interrupt Enable   | 2          | 0000 | 0000      | 0001     | 000s | GIE/GIEH, |       |

|           |         |                                |            |      |           |          |      | PEIE/GIEL |       |

| RETLW     | k       | Return with Literal in WREG    | 2          | 0000 | 1100      | kkkk     | kkkk | None      |       |

| RETURN    | S       | Return from Subroutine         | 2          | 0000 | 0000      | 0001     | 001s | None      |       |

| SLEEP     | _       | Go into Standby mode           | 1          | 0000 | 0000      | 0000     | 0011 | TO, PD    |       |

### TABLE 26-2: PIC18FXXXX INSTRUCTION SET (CONTINUED)

**Note 1:** When a PORT register is modified as a function of itself (e.g., MOVF PORTB, 1, 0), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

2: If this instruction is executed on the TMR0 register (and where applicable, 'd' = 1), the prescaler will be cleared if assigned.

**3:** If the Program Counter (PC) is modified or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

4: Some instructions are two-word instructions. The second word of these instructions will be executed as a NOP unless the first word of the instruction retrieves the information embedded in these 16 bits. This ensures that all program memory locations have a valid instruction.

5: If the table write starts the write cycle to internal memory, the write will continue until terminated.

| IORLW              | Inclusive                             | OR Lite         | eral with | W         |

|--------------------|---------------------------------------|-----------------|-----------|-----------|

| Syntax:            | IORLW k                               |                 |           |           |

| Operands:          | $0 \le k \le 255$                     | 5               |           |           |

| Operation:         | (W) .OR. k                            | $\rightarrow W$ |           |           |

| Status Affected:   | N, Z                                  |                 |           |           |

| Encoding:          | 0000                                  | 1001            | kkkk      | kkkk      |

| Description:       | The conter<br>eight-bit lite<br>in W. |                 |           |           |

| Words:             | 1                                     |                 |           |           |

| Cycles:            | 1                                     |                 |           |           |

| Q Cycle Activity:  |                                       |                 |           |           |

| Q1                 | Q2                                    | Q3              | 3         | Q4        |

| Decode             | Read<br>literal 'k'                   | Proce<br>Data   |           | rite to W |

| Example:           | IORLW                                 | 35h             |           |           |

| Before Instru<br>W | = 9Ah                                 |                 |           |           |

| IORWF             | Inclusive                                                                                                                                                                                                                                                       | OR W with                                                                                                                                                       | f                                                                                                                                                                        |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:           | IORWF f                                                                                                                                                                                                                                                         | {,d {,a}}                                                                                                                                                       |                                                                                                                                                                          |

| Operands:         | $0 \le f \le 255$<br>$d \in [0,1]$<br>$a \in [0,1]$                                                                                                                                                                                                             |                                                                                                                                                                 |                                                                                                                                                                          |

| Operation:        | (W) .OR. (f)                                                                                                                                                                                                                                                    | ) $\rightarrow$ dest                                                                                                                                            |                                                                                                                                                                          |

| Status Affected:  | N, Z                                                                                                                                                                                                                                                            |                                                                                                                                                                 |                                                                                                                                                                          |

| Encoding:         | 0001                                                                                                                                                                                                                                                            | 00da ff                                                                                                                                                         | ff ffff                                                                                                                                                                  |

| Description:      | <ul> <li>'0', the result is<br/>the result is</li> <li>If 'a' is '0', t</li> <li>If 'a' is '1', t</li> <li>GPR bank.</li> <li>If 'a' is '0' a</li> <li>set is enable</li> <li>in Indexed</li> <li>mode when</li> <li>Section 26</li> <li>Bit-Oriente</li> </ul> | placed back<br>he Access Ba<br>he BSR is use<br>nd the extend<br>led, this instru<br>Literal Offset /<br>iever $f \le 95$ (5<br>.2.3 "Byte-Or<br>ed Instruction | W. If 'd' is '1',<br>in register 'f'.<br>nk is selected.<br>d to select the<br>ed instruction<br>ction operates<br>Addressing<br>Fh). See<br>iented and<br>is in Indexed |

|                   |                                                                                                                                                                                                                                                                 | set Mode" for                                                                                                                                                   | details.                                                                                                                                                                 |

| Words:            | 1                                                                                                                                                                                                                                                               |                                                                                                                                                                 |                                                                                                                                                                          |

| Cycles:           | 1                                                                                                                                                                                                                                                               |                                                                                                                                                                 |                                                                                                                                                                          |

| Q Cycle Activity: |                                                                                                                                                                                                                                                                 |                                                                                                                                                                 |                                                                                                                                                                          |

| Q1                | Q2                                                                                                                                                                                                                                                              | Q3                                                                                                                                                              | Q4                                                                                                                                                                       |

| Decode            | Read<br>register 'f'                                                                                                                                                                                                                                            | Process<br>Data                                                                                                                                                 | Write to destination                                                                                                                                                     |

### Example:

| imple:             | IORWF          | RESULT, | Ο, | 1 |

|--------------------|----------------|---------|----|---|

| Before Instruction | on             |         |    |   |

| RESULT =<br>W =    | = 13h<br>= 91h |         |    |   |

| After Instruction  |                |         |    |   |

| RESULT =<br>W =    | = 13h<br>= 93h |         |    |   |

After Instruction BFh W =

Move W to f MOVWF f {,a}

$0 \leq f \leq 255$  $a \in [0,1]$

$(\mathsf{W}) \to \mathsf{f}$

MOVWF

Syntax: Operands:

Operation:

W REG

| MOVLW             | Move Lite           | eral to V     | V         |              |

|-------------------|---------------------|---------------|-----------|--------------|

| Syntax:           | MOVLW               | k             |           |              |

| Operands:         | $0 \le k \le 255$   | 5             |           |              |

| Operation:        | $k\toW$             |               |           |              |

| Status Affected:  | None                |               |           |              |

| Encoding:         | 0000                | 1110          | kkk!      | k kkkk       |

| Description:      | The eight-l         | bit literal ' | k' is loa | aded into W. |

| Words:            | 1                   |               |           |              |

| Cycles:           | 1                   |               |           |              |

| Q Cycle Activity: |                     |               |           |              |

| Q1                | Q2                  | Q3            |           | Q4           |

| Decode            | Read<br>literal 'k' | Proce<br>Data |           | Write to W   |

|                   |                     |               |           |              |

| Example:          | MOVLW               | 5Ah           |           |              |

After Instruction W

=

5Ah

|                   | . ,                                                                                             |                                                                      |                                                                 |                                                |

|-------------------|-------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|-----------------------------------------------------------------|------------------------------------------------|

| Status Affected:  | None                                                                                            |                                                                      |                                                                 |                                                |

| Encoding:         | 0110                                                                                            | 111a                                                                 | ffff                                                            | ffff                                           |

| Description:      | Move data<br>Location 'f<br>256-byte b                                                          | " can be a                                                           | 0                                                               |                                                |

|                   | If 'a' is '0',<br>If 'a' is '1',<br>GPR bank                                                    | the BSR i                                                            |                                                                 |                                                |

|                   | If 'a' is '0'<br>set is enal<br>in Indexed<br>mode whe<br>Section 2<br>Bit-Orient<br>Literal Of | bled, this i<br>I Literal O<br>enever f ≤<br>6.2.3 "By<br>ted Instru | nstructior<br>ffset Addr<br>95 (5Fh).<br>te-Orient<br>ctions in | operates<br>essing<br>See<br>ed and<br>Indexed |