#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 25MHz                                                                     |

| Connectivity               | CANbus, I <sup>2</sup> C, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                               |

| Number of I/O              | 25                                                                        |

| Program Memory Size        | 16KB (8K x 16)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 768 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                               |

| Data Converters            | A/D 8x10b                                                                 |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Through Hole                                                              |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                   |

| Supplier Device Package    | 28-SPDIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f2480-e-sp |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

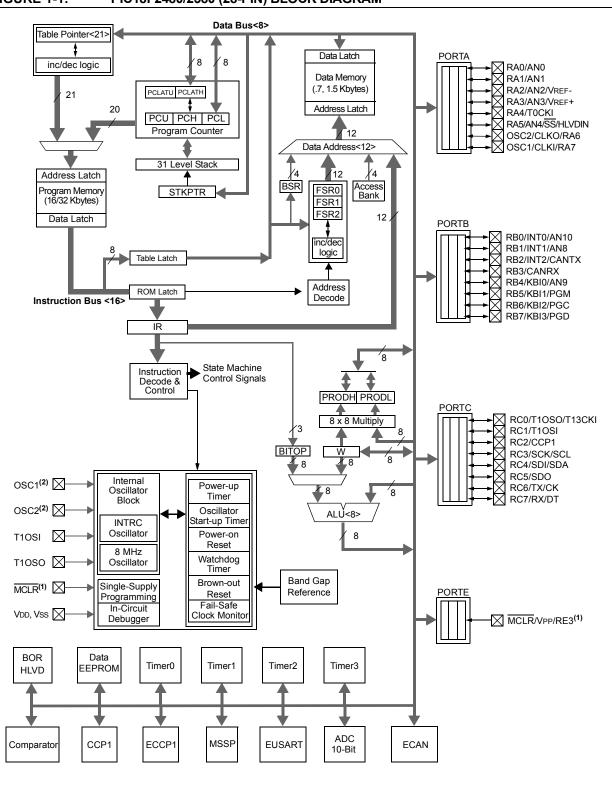

### FIGURE 1-1: PIC18F2480/2580 (28-PIN) BLOCK DIAGRAM

Note 1: RE3 is multiplexed with MCLR and is only available when the MCLR Resets are disabled.

2: OSC1/CLKI and OSC2/CLKO are only available in select oscillator modes and when these pins are not being used as digital I/O. Refer to Section 3.0 "Oscillator Configurations" for additional information.

### 3.0 OSCILLATOR CONFIGURATIONS

### 3.1 Oscillator Types

PIC18F2480/2580/4480/4580 devices can be operated in ten different oscillator modes. The user can program the Configuration bits, FOSC<3:0>, in Configuration Register 1H to select one of these ten modes:

- 1. LP Low-Power Crystal

- 2. XT Crystal/Resonator

- 3. HS High-Speed Crystal/Resonator

- 4. HSPLL High-Speed Crystal/Resonator with PLL Enabled

- 5. RC External Resistor/Capacitor with Fosc/4 Output on RA6

- 6. RCIO External Resistor/Capacitor with I/O on RA6

- 7. INTIO1 Internal Oscillator with Fosc/4 Output on RA6 and I/O on RA7

- 8. INTIO2 Internal Oscillator with I/O on RA6 and RA7

- 9. EC External Clock with Fosc/4 Output

- 10. ECIO External Clock with I/O on RA6

### 3.2 Crystal Oscillator/Ceramic Resonators

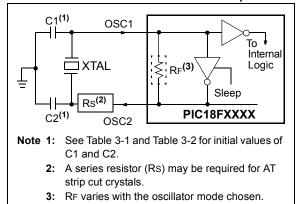

In XT, LP, HS or HSPLL Oscillator modes, a crystal or ceramic resonator is connected to the OSC1 and OSC2 pins to establish oscillation. Figure 3-1 shows the pin connections.

The oscillator design requires the use of a parallel resonant crystal.

Note: Use of a series resonant crystal may give a frequency out of the crystal manufacturer's specifications. FIGURE 3-1:

#### CRYSTAL/CERAMIC RESONATOR OPERATION (XT, LP, HS OR HSPLL CONFIGURATION)

## TABLE 3-1:CAPACITOR SELECTION FOR<br/>CERAMIC RESONATORS

#### **Typical Capacitor Values Used:** Mode OSC1 OSC2 Freq XT 56 pF 455 kHz 56 pF 47 pF 47 pF 2.0 MHz 4.0 MHz 33 pF 33 pF HS 8.0 MHz 27 pF 27 pF 16.0 MHz 22 pF 22 pF

#### Capacitor values are for design guidance only.

These capacitors were tested with the resonators listed below for basic start-up and operation. **These values are not optimized**.

Different capacitor values may be required to produce acceptable oscillator operation. The user should test the performance of the oscillator over the expected VDD and temperature range for the application.

See the notes on page 30 for additional information.

| Resonators Used: |         |  |  |  |  |  |

|------------------|---------|--|--|--|--|--|

| 455 kHz 4.0 MHz  |         |  |  |  |  |  |

| 2.0 MHz          | 8.0 MHz |  |  |  |  |  |

| 16               | .0 MHz  |  |  |  |  |  |

Note: When using resonators with frequencies above 3.5 MHz, the use of HS mode, rather than XT mode, is recommended. HS mode may be used at any VDD for which the controller is rated. If HS is selected, it is possible that the gain of the oscillator will overdrive the resonator. Therefore, a series resistor should be placed between the OSC2 pin and the resonator. As a good starting point, the recommended value of Rs is 330Ω.

### 3.7.1 OSCILLATOR CONTROL REGISTER

The OSCCON register (Register 3-2) controls several aspects of the device clock's operation, both in full-power operation and in power-managed modes.

The System Clock Select bits, SCS<1:0>, select the clock source. The available clock sources are the primary clock (defined by the FOSC<3:0> Configuration bits), the secondary clock (Timer1 oscillator) and the internal oscillator block. The clock source changes immediately after one or more of the bits is written to, following a brief clock transition interval. The SCS bits are cleared on all forms of Reset.

The Internal Oscillator Frequency Select bits, IRCF<2:0>, select the frequency output of the internal oscillator block to drive the device clock. The choices are the INTRC source, the INTOSC source (8 MHz) or one of the frequencies derived from the INTOSC post-scaler (31 kHz to 4 MHz). If the internal oscillator block is supplying the device clock, changing the states of these bits will have an immediate change on the internal oscillator's output. On device Resets, the default output frequency of the internal oscillator block is set at 1 MHz.

When an output frequency of 31 kHz is selected (IRCF<2:0> = 000), users may choose which internal oscillator acts as the source. This is done with the INTSRC bit in the OSCTUNE register (OSCTUNE<7>). Setting this bit selects INTOSC as a 31.25 kHz clock source by enabling the divide-by-256 output of the INTOSC postscaler. Clearing INTSRC selects INTRC (nominally 31 kHz) as the clock source.

This option allows users to select the tunable and more precise INTOSC as a clock source, while maintaining power savings with a very low clock speed. Regardless of the setting of INTSRC, INTRC always remains the clock source for features such as the Watchdog Timer and the Fail-Safe Clock Monitor.

The OSTS, IOFS and T1RUN bits indicate which clock source is currently providing the device clock. The OSTS bit indicates that the Oscillator Start-up Timer (OST) has timed out and the primary clock is providing the device clock in primary clock modes. The IOFS bit indicates when the internal oscillator block has stabilized and is providing the device clock in RC Clock modes. The T1RUN bit (T1CON<6>) indicates when the Timer1 oscillator is providing the device clock in secondary clock modes. In power-managed modes, only one of these three bits will be set at any time. If none of these bits are set, the INTRC is providing the clock or the internal oscillator block has just started and is not yet stable. The IDLEN bit determines if the device goes into Sleep mode or one of the Idle modes when the SLEEP instruction is executed.

The use of the flag and control bits in the OSCCON register is discussed in more detail in **Section 4.0** "Power-Managed Modes".

- Note 1: The Timer1 oscillator must be enabled to select the secondary clock source. The Timer1 oscillator is enabled by setting the T1OSCEN bit in the Timer1 Control register (T1CON<3>). If the Timer1 oscillator is not enabled, then any attempt to select a secondary clock source when executing a SLEEP instruction will be ignored.

- 2: It is recommended that the Timer1 oscillator be operating and stable before executing the SLEEP instruction, or a very long delay may occur while the Timer1 oscillator starts.

### 3.7.2 OSCILLATOR TRANSITIONS

PIC18F2480/2580/4480/4580 devices contain circuitry to prevent clock "glitches" when switching between clock sources. A short pause in the device clock occurs during the clock switch. The length of this pause is the sum of two cycles of the old clock source and three to four cycles of the new clock source. This formula assumes that the new clock source is stable.

Clock transitions are discussed in greater detail in **Section 4.1.2 "Entering Power-Managed Modes"**.

#### 6.2.3 INSTRUCTIONS IN PROGRAM MEMORY

The program memory is addressed in bytes. Instructions are stored as two bytes or four bytes in program memory. The Least Significant Byte of an instruction word is always stored in a program memory location with an even address (LSB = 0). To maintain alignment with instruction boundaries, the PC increments in steps of 2 and the LSB will always read '0' (see **Section 6.1.1 "Program Counter"**).

Figure 6-4 shows an example of how instruction words are stored in the program memory.

The CALL and GOTO instructions have the absolute program memory address embedded into the instruction. Since instructions are always stored on word boundaries, the data contained in the instruction is a word address. The word address is written to PC<20:1>, which accesses the desired byte address in program memory. Instruction #2 in Figure 6-4 shows how the instruction, GOTO 0006h, is encoded in the program memory. Program branch instructions, which encode a relative address offset, operate in the same manner. The offset value stored in a branch instruction represents the number of single-word instructions that the PC will be offset by. **Section 26.0 "Instruction Set Summary"** provides further details of the instruction set.

|                | _          |                    | LSB = 1 | LSB = 0 | Word Address $\downarrow$ |

|----------------|------------|--------------------|---------|---------|---------------------------|

|                | Program N  | •                  |         |         | 000000h                   |

|                | Byte Locat | ions $\rightarrow$ |         |         | 000002h                   |

|                |            |                    |         |         | 000004h                   |

|                |            |                    |         |         | 000006h                   |

| Instruction 1: | MOVLW      | 055h               | 0Fh     | 55h     | 000008h                   |

| Instruction 2: | GOTO       | 0006h              | EFh     | 03h     | 00000Ah                   |

|                |            |                    | F0h     | 00h     | 00000Ch                   |

| Instruction 3: | MOVFF      | 123h, 456h         | C1h     | 23h     | 00000Eh                   |

|                |            |                    | F4h     | 56h     | 000010h                   |

|                |            |                    |         |         | 000012h                   |

|                |            |                    |         |         | 000014h                   |

### FIGURE 6-4: INSTRUCTIONS IN PROGRAM MEMORY

### 6.2.4 TWO-WORD INSTRUCTIONS

The standard PIC18 instruction set has four, two-word instructions: CALL, MOVFF, GOTO and LSFR. In all cases, the second word of the instructions always has '1111' as its four Most Significant bits; the other 12 bits are literal data, usually a data memory address.

The use of '1111' in the 4 MSbs of an instruction specifies a special form of NOP. If the instruction is executed in proper sequence – immediately after the first word – the data in the second word is accessed and used by the instruction sequence. If the first word is skipped for some reason and the second word is executed by itself, a NOP is executed instead. This is necessary for cases when the two-word instruction is preceded by a conditional instruction that changes the PC. Example 6-4 shows how this works.

| Note: | See Section 6.5 "Program Memory and      |

|-------|------------------------------------------|

|       | the Extended Instruction Set" for infor- |

|       | mation on two-word instructions in the   |

|       | extended instruction set.                |

| CASE 1:             |                |                              |

|---------------------|----------------|------------------------------|

| Object Code         | Source Code    |                              |

| 0110 0110 0000 0000 | TSTFSZ REG1    | ; is RAM location 0?         |

| 1100 0001 0010 0011 | MOVFF REG1, RE | G2 ; No, skip this word      |

| 1111 0100 0101 0110 |                | ; Execute this word as a NOP |

| 0010 0100 0000 0000 | ADDWF REG3     | ; continue code              |

| CASE 2:             |                |                              |

| Object Code         | Source Code    |                              |

| 0110 0110 0000 0000 | TSTFSZ REG1    | ; is RAM location 0?         |

| 1100 0001 0010 0011 | MOVFF REG1, RE | G2 ; Yes, execute this word  |

| 1111 0100 0101 0110 |                | ; 2nd word of instruction    |

| 0010 0100 0000 0000 | ADDWF REG3     | ; continue code              |

### EXAMPLE 6-4: TWO-WORD INSTRUCTIONS

#### 6.4 Data Addressing Modes

Note: The execution of some instructions in the core PIC18 instruction set are changed when the PIC18 extended instruction set is enabled. See Section 6.6 "Data Memory and the Extended Instruction Set" for more information.

While the program memory can be addressed in only one way – through the program counter – information in the data memory space can be addressed in several ways. For most instructions, the addressing mode is fixed. Other instructions may use up to three modes, depending on which operands are used and whether or not the extended instruction set is enabled.

The addressing modes are:

- Inherent

- Literal

- Direct

- Indirect

An additional addressing mode, Indexed Literal Offset, is available when the extended instruction set is enabled (XINST Configuration bit = 1). Its operation is discussed in greater detail in **Section 6.6.1 "Indexed Addressing with Literal Offset**".

### 6.4.1 INHERENT AND LITERAL ADDRESSING

Many PIC18 control instructions do not need any argument at all; they either perform an operation that globally affects the device or they operate implicitly on one register. This addressing mode is known as Inherent Addressing. Examples include SLEEP, RESET and DAW.

Other instructions work in a similar way but require an additional explicit argument in the opcode. This is known as Literal Addressing mode because they require some literal value as an argument. Examples include ADDLW and MOVLW which, respectively, add or move a literal value to the W register. Other examples include CALL and GOTO, which include a 20-bit program memory address.

#### 6.4.2 DIRECT ADDRESSING

Direct Addressing specifies all or part of the source and/or destination address of the operation within the opcode itself. The options are specified by the arguments accompanying the instruction.

In the core PIC18 instruction set, bit-oriented and byte-oriented instructions use some version of Direct Addressing by default. All of these instructions include some 8-bit literal address as their Least Significant Byte. This address specifies either a register address in one of the banks of data RAM (Section 6.3.3 "General **Purpose Register File**") or a location in the Access Bank (Section 6.3.2 "Access Bank") as the data source for the instruction.

The Access RAM bit 'a' determines how the address is interpreted. When 'a' is '1', the contents of the BSR (Section 6.3.1 "Bank Select Register (BSR)") are used with the address to determine the complete 12-bit address of the register. When 'a' is '0', the address is interpreted as being a register in the Access Bank. Addressing that uses the Access RAM is sometimes also known as Direct Forced Addressing mode.

A few instructions, such as MOVFF, include the entire 12-bit address (either source or destination) in their opcodes. In these cases, the BSR is ignored entirely.

The destination of the operation's results is determined by the destination bit, 'd'. When 'd' is '1', the results are stored back in the source register, overwriting its original contents. When 'd' is '0', the results are stored in the W register. Instructions without the 'd' argument have a destination that is implicit in the instruction; their destination is either the target register being operated on or the W register.

### 6.4.3 INDIRECT ADDRESSING

Indirect Addressing allows the user to access a location in data memory without giving a fixed address in the instruction. This is done by using File Select Registers (FSRs) as pointers to the locations to be read or written to. Since the FSRs are themselves located in RAM as Special File Registers, they can also be directly manipulated under program control. This makes FSRs very useful in implementing data structures, such as tables and arrays in data memory.

The registers for Indirect Addressing are also implemented with Indirect File Operands (INDFs) that permit automatic manipulation of the pointer value with auto-incrementing, auto-decrementing or offsetting with another value. This allows for efficient code, using loops, such as the example of clearing an entire RAM bank in Example 6-5.

### EXAMPLE 6-5: HOW TO CLEAR RAM (BANK 1) USING INDIRECT ADDRESSING

|        | LFSR  | FSR0, 100h | ; |                |

|--------|-------|------------|---|----------------|

| NEXT   | CLRF  | POSTINCO   | ; | Clear INDF     |

|        |       |            | ; | register then  |

|        |       |            | ; | inc pointer    |

|        | BTFSS | FSROH,1    | ; | All done with  |

|        |       |            | ; | Bank1?         |

|        | BRA   | NEXT       | ; | NO, clear next |

| CONTIN | UE    |            | ; | YES, continue  |

|        |       |            |   |                |

### 7.4 Erasing Flash Program Memory

The minimum erase block is 32 words or 64 bytes. Only through the use of an external programmer, or through ICSP control, can larger blocks of program memory be bulk erased. Word erase in the Flash array is not supported.

When initiating an erase sequence from the microcontroller itself, a block of 64 bytes of program memory is erased. The Most Significant 16 bits of the TBLPTR<21:5> point to the block being erased. TBLPTR<4:0> are ignored.

The EECON1 register commands the erase operation. The EEPGD bit must be set to point to the Flash program memory. The WREN bit must be set to enable write operations. The FREE bit is set to select an erase operation.

For protection, the write initiate sequence for EECON2 must be used.

A long write is necessary for erasing the internal Flash. Instruction execution is halted while in a long write cycle. The long write will be terminated by the internal programming timer.

### 7.4.1 FLASH PROGRAM MEMORY ERASE SEQUENCE

The sequence of events for erasing a block of internal program memory location is:

- 1. Load Table Pointer register with address of row being erased.

- 2. Set the EECON1 register for the erase operation:

- set EEPGD bit to point to program memory;

- · clear the CFGS bit to access program memory;

- set WREN bit to enable writes;

- set FREE bit to enable the erase.

- 3. Disable interrupts.

- 4. Write 55h to EECON2.

- 5. Write 0AAh to EECON2.

- 6. Set the WR bit. This will begin the row erase cycle.

- 7. The CPU will stall for duration of the erase (about 2 ms using internal timer).

- 8. Re-enable interrupts.

| EXAMPLE 7-2: | ERASING A FLASH PROGRAM MEMORY ROW |

|--------------|------------------------------------|

|              |                                    |

|           | MOVLW<br>MOVWF<br>MOVLW<br>MOVLW<br>MOVLW | CODE_ADDR_UPPER<br>TBLPTRU<br>CODE_ADDR_HIGH<br>TBLPTRH<br>CODE_ADDR_LOW<br>TBLPTRL |   | load TBLPTR with the base<br>address of the memory block |

|-----------|-------------------------------------------|-------------------------------------------------------------------------------------|---|----------------------------------------------------------|

| ERASE_ROW |                                           |                                                                                     |   |                                                          |

|           | BSF                                       | EECON1, EEPGD                                                                       | ; | point to Flash program memory                            |

|           | BCF                                       | EECON1, CFGS                                                                        | ; | access Flash program memory                              |

|           | BSF                                       | EECON1, WREN                                                                        | ; | enable write to memory                                   |

|           | BSF                                       | EECON1, FREE                                                                        | ; | enable Row Erase operation                               |

|           | BCF                                       | INTCON, GIE                                                                         | ; | disable interrupts                                       |

| Required  | MOVLW                                     | 55h                                                                                 |   |                                                          |

| Sequence  | MOVWF                                     | EECON2                                                                              | ; | write 55h                                                |

|           | MOVLW                                     | 0AAh                                                                                |   |                                                          |

|           | MOVWF                                     | EECON2                                                                              | ; | write OAAh                                               |

|           | BSF                                       | EECON1, WR                                                                          | ; | start erase (CPU stall)                                  |

|           | BSF                                       | INTCON, GIE                                                                         | ; | re-enable interrupts                                     |

| Pin Name          | Function             | I/O | TRIS | Buffer | Description                                                                                                                    |  |  |

|-------------------|----------------------|-----|------|--------|--------------------------------------------------------------------------------------------------------------------------------|--|--|

| RA0/AN0/CVREF     | RA0                  | OUT | 0    | DIG    | LATA<0> data output.                                                                                                           |  |  |

|                   |                      | IN  | 1    | TTL    | PORTA<0> data input.                                                                                                           |  |  |

|                   | AN0                  | IN  | 1    | ANA    | A/D Input Channel 0. Enabled on POR; this analog input overrides the digital input (read as clear – low level).                |  |  |

|                   | CVREF <sup>(1)</sup> | OUT | х    | ANA    | Comparator voltage reference analog output. Enabling this analog output overrides the digital I/O (read as clear – low level). |  |  |

| RA1/AN1           | RA1                  | OUT | 0    | DIG    | LATA<1> data output.                                                                                                           |  |  |

|                   |                      | IN  | 1    | TTL    | PORTA<1> data input.                                                                                                           |  |  |

|                   | AN1                  | IN  | 1    | ANA    | A/D Input Channel 1. Enabled on POR; this analog input overrides the digital input (read as clear – low level).                |  |  |

| RA2/AN2/VREF-     | RA2                  | OUT | 0    | DIG    | LATA<2> data output.                                                                                                           |  |  |

|                   |                      | IN  | 1    | TTL    | PORTA<2> data input.                                                                                                           |  |  |

|                   | AN2                  | IN  | 1    | ANA    | A/D Input Channel 2. Enabled on POR; this analog input overrides the digital input (read as clear – low level).                |  |  |

|                   | VREF-                | IN  | 1    | ANA    | A/D and comparator negative voltage analog input.                                                                              |  |  |

| RA3/AN3/VREF+     | RA3                  | OUT | 0    | DIG    | LATA<3> data output.                                                                                                           |  |  |

|                   |                      | IN  | 1    | TTL    | PORTA<3> data input.                                                                                                           |  |  |

|                   | AN3                  | IN  | 1    | ANA    | A/D Input Channel 3. Enabled on POR; this analog input override digital input (read as clear – low level).                     |  |  |

|                   | VREF+                | IN  | 1    | ANA    | A/D and comparator positive voltage analog input.                                                                              |  |  |

| RA4/T0CKI         | RA4                  | OUT | 0    | DIG    | LATA<4> data output.                                                                                                           |  |  |

|                   |                      | IN  | 1    | TTL    | PORTA<4> data input.                                                                                                           |  |  |

|                   | T0CKI                | IN  | 1    | ST     | Timer0 clock input.                                                                                                            |  |  |

| RA5/AN4/SS/HLVDIN | RA5                  | OUT | 0    | DIG    | LATA<5> data output.                                                                                                           |  |  |

|                   |                      | IN  | 1    | TTL    | PORTA<5> data input.                                                                                                           |  |  |

|                   | AN4                  | IN  | 1    | ANA    | A/D Input Channel 4. Enabled on POR; this analog input overrides the digital input (read as clear – low level).                |  |  |

|                   | SS                   | IN  | 1    | TTL    | Slave select input for MSSP.                                                                                                   |  |  |

|                   | HLVDIN               | IN  | 1    | ANA    | High/Low-Voltage Detect external trip point input.                                                                             |  |  |

| OSC2/CLKO/RA6     | OSC2                 | OUT | X    | ANA    | Output connection; selected by FOSC<3:0> Configuration bits.<br>Enabling OSC2 overrides digital I/O.                           |  |  |

|                   | CLKO                 | OUT | Х    | DIG    | Output connection; selected by FOSC<3:0> Configuration bits.<br>Enabling CLKO overrides digital I/O (FOSC/4).                  |  |  |

|                   | RA6                  | OUT | 0    | DIG    | LATA<6> data output.                                                                                                           |  |  |

|                   |                      | IN  | 1    | TTL    | PORTA<6> data input.                                                                                                           |  |  |

| OSC1/CLKI/RA7     | OSC1                 | IN  | X    | ANA    | Main oscillator input connection determined by FOSC<3:0><br>Configuration bits. Enabling OSC1 overrides digital I/O.           |  |  |

|                   | CLKI                 | IN  | Х    | ANA    | Main clock input connection determined by FOSC<3:0><br>Configuration bits. Enabling CLKI overrides digital I/O.                |  |  |

|                   | RA7                  | OUT | 0    | DIG    | LATA<7> data output.                                                                                                           |  |  |

|                   |                      | IN  | 1    | TTL    | PORTA<7> data input.                                                                                                           |  |  |

### TABLE 11-1: PORTA I/O SUMMARY

Legend: OUT = Output, IN = Input, ANA = Analog Signal, DIG = Digital Output, ST = Schmitt Buffer Input, TTL = TTL Buffer Input Note 1: Available on 40/44-pin devices only.

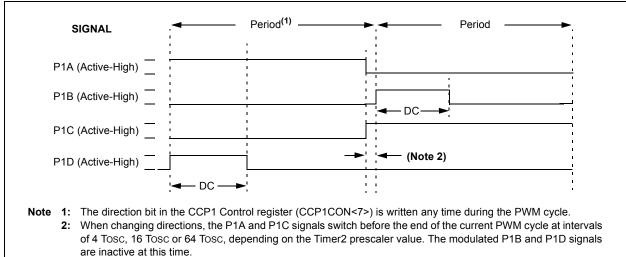

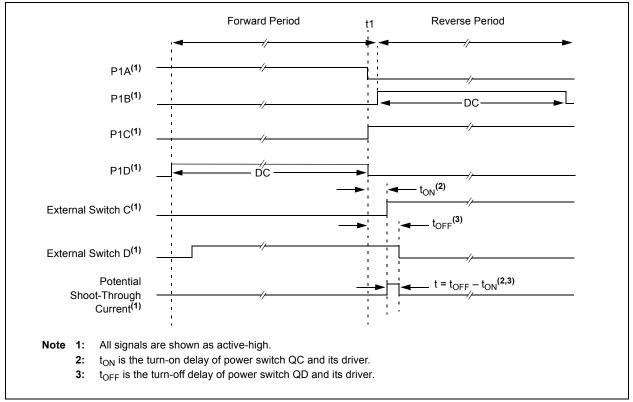

FIGURE 17-9: PWM DIRECTION CHANGE AT NEAR 100% DUTY CYCLE

### 17.4.7.1 Auto-Shutdown and Auto-Restart

The auto-shutdown feature can be configured to allow automatic restarts of the module following a shutdown event. This is enabled by setting the PRSEN bit of the ECCP1DEL register (ECCP1DEL<7>).

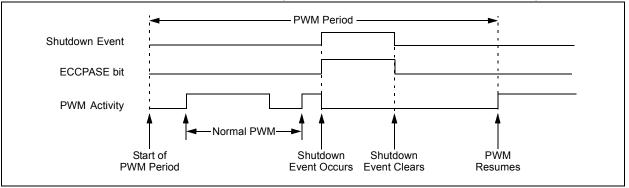

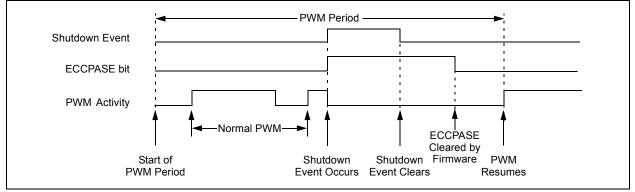

In Shutdown mode with PRSEN = 1 (Figure 17-10), the ECCPASE bit will remain set for as long as the cause of the shutdown continues. When the shutdown condition clears, the ECCP1ASE bit is cleared. If PRSEN = 0 (Figure 17-11), once a shutdown condition occurs, the ECCPASE bit will remain set until it is cleared by firmware. Once ECCPASE is cleared, the Enhanced PWM will resume at the beginning of the next PWM period.

| Note: | Writing to the ECCPASE bit is disabled |

|-------|----------------------------------------|

|       | while a shutdown condition is active.  |

Independent of the PRSEN bit setting, if the auto-shutdown source is one of the comparators, the shutdown condition is a level. The ECCPASE bit cannot be cleared as long as the cause of the shutdown persists.

The Auto-Shutdown mode can be forced by writing a '1' to the ECCPASE bit.

### 17.4.8 START-UP CONSIDERATIONS

When the ECCP module is used in the PWM mode, the application hardware must use the proper external pull-up and/or pull-down resistors on the PWM output pins. When the microcontroller is released from Reset, all of the I/O pins are in the high-impedance state. The external circuits must keep the power switch devices in the off state until the microcontroller drives the I/O pins with the proper signal levels, or activates the PWM output(s).

The CCP1M<1:0> bits (ECCP1CON<1:0>) allow the user to choose whether the PWM output signals are active-high or active-low for each pair of PWM output pins (P1A/P1C and P1B/P1D). The PWM output polarities must be selected before the PWM pins are configured as outputs. Changing the polarity configuration while the PWM pins are configured as outputs is not recommended, since it may result in damage to the application circuits.

The P1A, P1B, P1C and P1D output latches may not be in the proper states when the PWM module is initialized. Enabling the PWM pins for output at the same time as the ECCP module may cause damage to the application circuit. The ECCP module must be enabled in the proper output mode and complete a full PWM cycle before configuring the PWM pins as outputs. The completion of a full PWM cycle is indicated by the TMR2IF bit being set as the second PWM period begins.

### FIGURE 17-10: PWM AUTO-SHUTDOWN (PRSEN = 1, AUTO-RESTART ENABLED)

### FIGURE 17-11: PWM AUTO-SHUTDOWN (PRSEN = 0, AUTO-RESTART DISABLED)

| BRG Value               | XXXXh       |                                                                                              | 001Ch                                   |

|-------------------------|-------------|----------------------------------------------------------------------------------------------|-----------------------------------------|

| RX Pin                  |             | Edge #1Edge #2Edge #3Edge #4<br><u>Start Bit 0 Bit 1 Bit 2 Bit 3 Bit 4 Bit 5 Bit 6 Bit 7</u> | Edge #5<br>Stop Bit                     |

| BRG Clock               |             |                                                                                              | _10000400000000000000000000000000000000 |

| ABDEN bit               | Set by User |                                                                                              | Auto-Cleared                            |

| RCIF bit<br>(Interrupt) |             |                                                                                              |                                         |

| Read<br>RCREG           |             |                                                                                              |                                         |

| SPBRG                   |             | XXXXh                                                                                        | X 1Ch                                   |

| SPBRGH                  |             | XXXXh                                                                                        | ) 00h                                   |

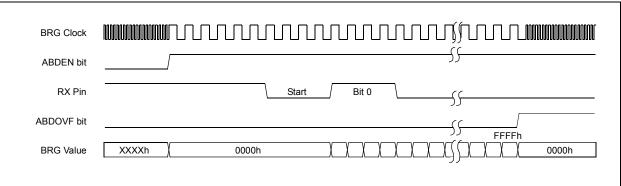

### FIGURE 19-2: BRG OVERFLOW SEQUENCE

# REGISTER 24-34: BnDLC: TX/RX BUFFER n DATA LENGTH CODE REGISTERS IN RECEIVE MODE $[0 \le n \le 5, TXnEN (BSEL \le n) = 0]^{(1)}$

| Legend:   R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'   -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown   bit 7 Unimplemented: Read as '0'   bit 6 RXRTR: Receiver Remote Transmission Request bit   1 = This is a remote transmission request   0 = This is not a remote transmission request   bit 5 RB1: Reserved bit 1   Reserved by CAN Spec and read as '0'.   bit 4 RB0: Reserved bit 0   Reserved by CAN Spec and read as '0'.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | U-0             | R-x                                   | R-x              | R-x          | R-x              | R-x             | R-x             | R-x   |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|---------------------------------------|------------------|--------------|------------------|-----------------|-----------------|-------|--|--|--|

| Legend:<br>R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'<br>-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown<br>bit 7 Unimplemented: Read as '0'<br>bit 6 RXRTR: Receiver Remote Transmission Request bit<br>1 = This is a remote transmission request<br>0 = This is not a remote transmission request<br>bit 5 RB1: Reserved bit 1<br>Reserved by CAN Spec and read as '0'.<br>bit 4 RB0: Reserved bit 0<br>Reserved by CAN Spec and read as '0'.<br>bit 3-0 DLC<3:0>: Data Length Code bits<br>1111 = Reserved<br>1101 = Reserved<br>1101 = Reserved<br>1011 = Reserved<br>1011 = Reserved<br>1011 = Reserved<br>1011 = Reserved<br>1010 = Data length = 8 bytes<br>0111 = Data length = 7 bytes<br>0101 = Data length = 4 bytes<br>0101 = Data length = 4 bytes<br>0101 = Data length = 3 bytes<br>0101 = Data length = 3 bytes<br>0101 = Data length = 4 bytes<br>0101 = Data length = 4 bytes<br>0101 = Data length = 3 bytes<br>0111 = Data length = 4 bytes<br>0112 = Data length = 4 bytes<br>0113 = Data length = 4 bytes<br>0114 = Data length = 4 bytes<br>0115 = Data length = 4 bytes<br>0115 = Data length = 4 bytes<br>0116 = Data length = 4 bytes<br>0117 = Data length = 4 bytes<br>0118 = Data length = 4 bytes<br>0119 = Data length = 4 bytes<br>0111 = Dat       | —               | RXRTR                                 | RB1              | RB0          | DLC3             | DLC2            | DLC1            | DLC0  |  |  |  |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'   -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown   bit 7 Unimplemented: Read as '0'   bit 6 RXRTR: Receiver Remote Transmission Request bit   1 = This is a remote transmission request 0 = This is not a remote transmission request   0 = This is not a remote transmission request 0 = This is not a remote transmission request   bit 5 RB1: Reserved bit 1   Reserved by CAN Spec and read as '0'.   bit 4 RB0: Reserved bit 0   Reserved by CAN Spec and read as '0'.   bit 3-0 DLC<3:0>: Data Length Code bits   1111 = Reserved   1100 = Reserved   1011 = Reserved   1001 = Reserved   1001 = Reserved   1002 = Reserved   1003 = Data length = 8 bytes   0111 = Data length = 7 bytes   0111 = Data length = 7 bytes   0112 = Data length = 4 bytes   0113 = Data length = 5 bytes   0141 = Data length = 5 bytes   0151 = Data length = 5 bytes   0161 = Data length = 2 bytes   017 = Data length = 2 bytes   018 = Data lengt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | bit 7           |                                       |                  |              |                  |                 |                 | bit 0 |  |  |  |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'   -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown   bit 7 Unimplemented: Read as '0'   bit 6 RXRTR: Receiver Remote Transmission Request bit   1 = This is a remote transmission request 0 = This is not a remote transmission request   0 = This is not a remote transmission request 0 = This is not a remote transmission request   bit 5 RB1: Reserved bit 1   Reserved by CAN Spec and read as '0'.   bit 4 RB0: Reserved bit 0   Reserved by CAN Spec and read as '0'.   bit 3-0 DLC<3:0>: Data Length Code bits   1111 = Reserved   1100 = Reserved   1011 = Reserved   1001 = Reserved   1001 = Reserved   1002 = Reserved   1003 = Data length = 8 bytes   0111 = Data length = 7 bytes   0111 = Data length = 7 bytes   0112 = Data length = 4 bytes   0113 = Data length = 5 bytes   0141 = Data length = 5 bytes   0151 = Data length = 5 bytes   0161 = Data length = 2 bytes   017 = Data length = 2 bytes   018 = Data lengt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                 |                                       |                  |              |                  |                 |                 |       |  |  |  |

| -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown   bit 7 Unimplemented: Read as '0'   bit 6 RXRTR: Receiver Remote Transmission Request bit   1 = This is a remote transmission request 0 = This is not a remote transmission request   bit 5 RB1: Reserved bit 1   Reserved by CAN Spec and read as '0'.   bit 4 RB0: Reserved bit 0   Reserved by CAN Spec and read as '0'.   bit 3-0 DLC<3:0>: Data Length Code bits   1111 = Reserved   1100 = Reserved   1010 = Reserved   1011 = Reserved   1000 = Data length = 8 bytes   0111 = Data length = 7 bytes   0101 = Data length = 5 bytes   0101 = Data length = 4 bytes   0101 = Data length = 4 bytes   0101 = Data length = 2 bytes   0101 = Data length = 4 bytes   0111 = Data length = 4 bytes   0111 = Data length = 1 bytes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Legend:         |                                       |                  |              |                  |                 |                 |       |  |  |  |

| bit 7 Unimplemented: Read as '0'<br>bit 6 RXRTR: Receiver Remote Transmission Request bit<br>1 = This is a remote transmission request<br>0 = This is not a remote transmission request<br>bit 5 RB1: Reserved bit 1<br>Reserved by CAN Spec and read as '0'.<br>bit 4 RB0: Reserved bit 0<br>Reserved by CAN Spec and read as '0'.<br>bit 3-0 DLC<3:0>: Data Length Code bits<br>1111 = Reserved<br>1110 = Reserved<br>1101 = Reserved<br>1101 = Reserved<br>1001 = Reserved<br>1001 = Reserved<br>1001 = Reserved<br>1002 = Data length = 8 bytes<br>0111 = Data length = 7 bytes<br>0103 = Data length = 5 bytes<br>0104 = Data length = 4 bytes<br>0105 = Data length = 2 bytes<br>0105 = Data length = 2 bytes<br>0106 = Data length = 2 bytes<br>0107 = Data length = 2 bytes<br>0108 = Data length = 1 bytes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | R = Readable    | bit                                   | W = Writable     | bit          | U = Unimpler     | mented bit, rea | d as '0'        |       |  |  |  |

| bit 6 RXRTR: Receiver Remote Transmission Request bit<br>1 = This is a remote transmission request<br>0 = This is not a remote transmission request<br>bit 5 RB1: Reserved bit 1<br>Reserved by CAN Spec and read as '0'.<br>bit 4 RB0: Reserved bit 0<br>Reserved by CAN Spec and read as '0'.<br>bit 3-0 DLC<3:0>: Data Length Code bits<br>1111 = Reserved<br>1101 = Reserved<br>1100 = Reserved<br>1001 = Reserved<br>1001 = Reserved<br>1011 = Reserved<br>1010 = Reserved<br>1010 = Reserved<br>1011 = Reserved<br>1010 = Data length = 8 bytes<br>0111 = Data length = 5 bytes<br>0102 = Data length = 4 bytes<br>0112 = Data length = 4 bytes<br>0112 = Data length = 2 bytes<br>0112 = Data length = 2 bytes<br>0112 = Data length = 1 bytes<br>0114 = Data length = 1 bytes<br>0115 = Data length = 1 bytes<br>1016 = Data length = 1 bytes<br>1017 = Data length = 1 bytes<br>1018 = Data length = 1 bytes<br>1019 = Data length = 1 bytes<br>1010 = Data length = 1 bytes<br>1011 = Data len | -n = Value at F | POR                                   | '1' = Bit is set |              | '0' = Bit is cle | ared            | x = Bit is unkr | nown  |  |  |  |

| bit 6 RXRTR: Receiver Remote Transmission Request bit<br>1 = This is a remote transmission request<br>0 = This is not a remote transmission request<br>bit 5 RB1: Reserved bit 1<br>Reserved by CAN Spec and read as '0'.<br>bit 4 RB0: Reserved bit 0<br>Reserved by CAN Spec and read as '0'.<br>bit 3-0 DLC<3:0>: Data Length Code bits<br>1111 = Reserved<br>1101 = Reserved<br>1100 = Reserved<br>1001 = Reserved<br>1001 = Reserved<br>1011 = Reserved<br>1010 = Reserved<br>1010 = Reserved<br>1011 = Reserved<br>1010 = Data length = 8 bytes<br>0111 = Data length = 5 bytes<br>0102 = Data length = 4 bytes<br>0112 = Data length = 4 bytes<br>0112 = Data length = 2 bytes<br>0112 = Data length = 2 bytes<br>0112 = Data length = 1 bytes<br>0114 = Data length = 1 bytes<br>0115 = Data length = 1 bytes<br>1016 = Data length = 1 bytes<br>1017 = Data length = 1 bytes<br>1018 = Data length = 1 bytes<br>1019 = Data length = 1 bytes<br>1010 = Data length = 1 bytes<br>1011 = Data len |                 |                                       |                  |              |                  |                 |                 |       |  |  |  |

| 1 = This is a remote transmission request   0 = This is not a remote transmission request   bit 5 RB1: Reserved bit 1   Reserved by CAN Spec and read as '0'.   bit 4 RB0: Reserved bit 0   Reserved by CAN Spec and read as '0'.   bit 3-0 DLC<3:0>: Data Length Code bits   1111 = Reserved   1100 = Reserved   1011 = Reserved   1001 = Reserved   1000 = Data length = 8 bytes   0111 = Data length = 7 bytes   0101 = Data length = 5 bytes   0101 = Data length = 5 bytes   0101 = Data length = 3 bytes   0101 = Data length = 3 bytes   0101 = Data length = 2 bytes   0010 = Data length = 1 bytes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | bit 7           | Unimplemen                            | ted: Read as '   | )'           |                  |                 |                 |       |  |  |  |

| 0 = This is not a remote transmission request   bit 5 RB1: Reserved bit 1<br>Reserved by CAN Spec and read as '0'.   bit 4 RB0: Reserved bit 0<br>Reserved by CAN Spec and read as '0'.   bit 3-0 DLC<3:0>: Data Length Code bits   1111 = Reserved 1101 = Reserved   1100 = Reserved 1001 = Reserved   1010 = Reserved 1001 = Reserved   1001 = Reserved 1001 = Reserved   1001 = Reserved 1001 = Reserved   1000 = Data length = 8 bytes 0111 = Data length = 5 bytes   0101 = Data length = 5 bytes 0100 = Data length = 3 bytes   0101 = Data length = 2 bytes 0011 = Data length = 3 bytes   0101 = Data length = 1 bytes 0001 = Data length = 1 bytes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | bit 6           | RXRTR: Rec                            | eiver Remote T   | ransmission  | Request bit      |                 |                 |       |  |  |  |

| Reserved by CAN Spec and read as '0'.   bit 4 RB0: Reserved bit 0   Reserved by CAN Spec and read as '0'.   bit 3-0 DLC<3:0>: Data Length Code bits   1111 = Reserved   1101 = Reserved   1010 = Reserved   1011 = Reserved   1010 = Reserved   1010 = Reserved   1010 = Reserved   1011 = Reserved   1010 = Reserved   1010 = Data length = 8 bytes   0111 = Data length = 7 bytes   0110 = Data length = 6 bytes   0101 = Data length = 5 bytes   0101 = Data length = 3 bytes   0110 = Data length = 4 bytes   011 = Data length = 3 bytes   0110 = Data length = 1 bytes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                 |                                       |                  |              |                  |                 |                 |       |  |  |  |

| bit 4 RB0: Reserved bit 0<br>Reserved by CAN Spec and read as '0'.<br>bit 3-0 DLC<3:0>: Data Length Code bits<br>1111 = Reserved<br>1110 = Reserved<br>1101 = Reserved<br>1001 = Reserved<br>1010 = Reserved<br>1010 = Reserved<br>1001 = Reserved<br>1001 = Reserved<br>1000 = Data length = 8 bytes<br>0111 = Data length = 7 bytes<br>0110 = Data length = 5 bytes<br>0100 = Data length = 4 bytes<br>0101 = Data length = 3 bytes<br>0101 = Data length = 2 bytes<br>0001 = Data length = 1 bytes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | bit 5           | RB1: Reserve                          | ed bit 1         |              |                  |                 |                 |       |  |  |  |

| Reserved by CAN Spec and read as '0'.<br>bit 3-0 DLC<3:0>: Data Length Code bits<br>1111 = Reserved<br>1100 = Reserved<br>1101 = Reserved<br>1011 = Reserved<br>1010 = Reserved<br>1010 = Reserved<br>1001 = Reserved<br>1000 = Data length = 8 bytes<br>0111 = Data length = 7 bytes<br>0110 = Data length = 6 bytes<br>0101 = Data length = 5 bytes<br>0100 = Data length = 4 bytes<br>0101 = Data length = 3 bytes<br>0011 = Data length = 2 bytes<br>0010 = Data length = 1 bytes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                 | Reserved by                           | CAN Spec and     | read as '0'. |                  |                 |                 |       |  |  |  |

| bit 3-0 DLC<3:0>: Data Length Code bits<br>1111 = Reserved<br>1100 = Reserved<br>1101 = Reserved<br>1000 = Reserved<br>1011 = Reserved<br>1010 = Reserved<br>1001 = Reserved<br>1000 = Data length = 8 bytes<br>0111 = Data length = 7 bytes<br>0110 = Data length = 6 bytes<br>0101 = Data length = 5 bytes<br>0100 = Data length = 4 bytes<br>0101 = Data length = 3 bytes<br>0111 = Data length = 2 bytes<br>0001 = Data length = 1 bytes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | bit 4           | RB0: Reserve                          | ed bit 0         |              |                  |                 |                 |       |  |  |  |

| 1111 = Reserved<br>1110 = Reserved<br>1101 = Reserved<br>1010 = Reserved<br>1011 = Reserved<br>1010 = Reserved<br>1001 = Reserved<br>1000 = Data length = 8 bytes<br>0111 = Data length = 7 bytes<br>0110 = Data length = 6 bytes<br>0101 = Data length = 5 bytes<br>0100 = Data length = 4 bytes<br>0111 = Data length = 3 bytes<br>0011 = Data length = 2 bytes<br>0010 = Data length = 1 bytes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                 | Reserved by CAN Spec and read as '0'. |                  |              |                  |                 |                 |       |  |  |  |

| 1110 = Reserved<br>1101 = Reserved<br>1100 = Reserved<br>1011 = Reserved<br>1010 = Reserved<br>1000 = Data length = 8 bytes<br>0111 = Data length = 7 bytes<br>0110 = Data length = 6 bytes<br>0101 = Data length = 5 bytes<br>0101 = Data length = 4 bytes<br>0101 = Data length = 3 bytes<br>0011 = Data length = 2 bytes<br>0001 = Data length = 1 bytes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | bit 3-0         | DLC<3:0>: D                           | ata Length Coo   | le bits      |                  |                 |                 |       |  |  |  |

| 1101 = Reserved<br>1100 = Reserved<br>1011 = Reserved<br>1010 = Reserved<br>1000 = Data length = 8 bytes<br>0111 = Data length = 7 bytes<br>0110 = Data length = 6 bytes<br>0101 = Data length = 5 bytes<br>0100 = Data length = 4 bytes<br>0101 = Data length = 3 bytes<br>0011 = Data length = 2 bytes<br>0001 = Data length = 1 bytes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                 |                                       |                  |              |                  |                 |                 |       |  |  |  |

| 1100 = Reserved<br>1011 = Reserved<br>1010 = Reserved<br>1001 = Reserved<br>1000 = Data length = 8 bytes<br>0111 = Data length = 7 bytes<br>0110 = Data length = 6 bytes<br>0101 = Data length = 5 bytes<br>0100 = Data length = 4 bytes<br>0011 = Data length = 3 bytes<br>0011 = Data length = 2 bytes<br>0001 = Data length = 1 bytes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                 |                                       |                  |              |                  |                 |                 |       |  |  |  |