Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 25MHz                                                                     |

| Connectivity               | CANbus, I <sup>2</sup> C, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                               |

| Number of I/O              | 25                                                                        |

| Program Memory Size        | 32KB (16K x 16)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 1.5K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                               |

| Data Converters            | A/D 8x10b                                                                 |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 28-VQFN Exposed Pad                                                       |

| Supplier Device Package    | 28-QFN (6x6)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f2580-e-ml |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Table of Contents**

| 1.0  | Device Overview                                              | 9   |

|------|--------------------------------------------------------------|-----|

| 2.0  | Guidelines for Getting Started with PIC18F Microcontrollers  |     |

| 3.0  | Oscillator Configurations                                    |     |

| 4.0  | Power-Managed Modes                                          |     |

| 5.0  | Reset                                                        |     |

| 6.0  | Memory Organization                                          |     |

| 7.0  | Flash Program Memory                                         | 101 |

| 8.0  | Data EEPROM Memory                                           | 111 |

| 9.0  | 8 x 8 Hardware Multiplier                                    | 117 |

| 10.0 | Interrupts                                                   | 119 |

| 11.0 | I/O Ports                                                    | 135 |

| 12.0 | Timer0 Module                                                | 151 |

| 13.0 | Timer1 Module                                                | 155 |

| 14.0 | Timer2 Module                                                |     |

|      | Timer3 Module                                                |     |

|      | Capture/Compare/PWM (CCP) Modules                            |     |

| 17.0 | Enhanced Capture/Compare/PWM (ECCP) Module                   |     |

| 18.0 | Master Synchronous Serial Port (MSSP) Module                 |     |

| 19.0 | Enhanced Universal Synchronous Receiver Transmitter (EUSART) |     |

| 20.0 | 10-Bit Analog-to-Digital Converter (A/D) Module              |     |

| 21.0 | Comparator Module                                            |     |

| 22.0 | Comparator Voltage Reference Module                          |     |

| 23.0 | High/Low-Voltage Detect (HLVD)                               |     |

|      | ECAN Module                                                  |     |

| 25.0 | Special Features of the CPU                                  |     |

| 26.0 |                                                              |     |

| 27.0 | Development Support                                          |     |

|      | Electrical Characteristics                                   |     |

|      | Packaging Information                                        |     |

|      | endix A: Revision History                                    |     |

|      | endix B: Device Differences                                  |     |

| •••  | endix C: Conversion Considerations                           |     |

|      | endix D: Migration from Baseline to Enhanced Devices         |     |

|      | endix E: Migration From Mid-Range to Enhanced Devices        |     |

|      | endix F: Migration From High-End to Enhanced Devices         |     |

|      | Microchip Web Site                                           |     |

|      | omer Change Notification Service                             |     |

|      | omer Support                                                 |     |

|      | ler Response                                                 |     |

| PIC1 | 8F2480/2580/4480/4580 Product Identification System          |     |

NOTES:

## 5.6 Reset State of Registers

Most registers are unaffected by a Reset. Their status is unknown on a Power-on Reset and unchanged by all other Resets. The other registers are forced to a "Reset state" depending on the type of Reset that occurred.

Most registers are not affected by a WDT wake-up, since this is viewed as the resumption of normal operation. Status bits from the RCON register, RI, TO, PD, POR and BOR, are set or cleared differently in different Reset situations, as indicated in Table 5-3. These bits are used in software to determine the nature of the Reset.

Table 5-4 describes the Reset states for all of the Special Function Registers. These are categorized by Power-on and Brown-out Resets, Master Clear and WDT Resets and WDT wake-ups.

## TABLE 5-3:STATUS BITS, THEIR SIGNIFICANCE AND THE INITIALIZATION CONDITION FOR<br/>RCON REGISTER

| Condition                                                       | Program                |                  | RCC | DN Reg | jister |     |     | STKPTR | Register |

|-----------------------------------------------------------------|------------------------|------------------|-----|--------|--------|-----|-----|--------|----------|

| Condition                                                       | Counter <sup>(1)</sup> | SBOREN           | RI  | то     | PD     | POR | BOR | STKFUL | STKUNF   |

| Power-on Reset                                                  | 0000h                  | 1                | 1   | 1      | 1      | 0   | 0   | 0      | 0        |

| RESET Instruction                                               | 0000h                  | u <b>(2)</b>     | 0   | u      | u      | u   | u   | u      | u        |

| Brown-out Reset                                                 | 0000h                  | u <b>(2)</b>     | 1   | 1      | 1      | u   | 0   | u      | u        |

| MCLR Reset during<br>Power-Managed Run modes                    | 0000h                  | <sub>ປ</sub> (2) | u   | 1      | u      | u   | u   | u      | u        |

| MCLR Reset during<br>Power-Managed Idle modes and<br>Sleep mode | 0000h                  | u <b>(2)</b>     | u   | 1      | 0      | u   | u   | u      | u        |

| WDT Time-out during Full Power or Power-Managed Run modes       | 0000h                  | u <b>(2)</b>     | u   | 0      | u      | u   | u   | u      | u        |

| MCLR Reset during Full-Power execution                          | 0000h                  | <sub>ປ</sub> (2) | u   | u      | u      | u   | u   | u      | u        |

| Stack Full Reset (STVREN = 1)                                   | 0000h                  | u <b>(2)</b>     | u   | u      | u      | u   | u   | 1      | u        |

| Stack Underflow Reset<br>(STVREN = 1)                           | 0000h                  | <sub>ປ</sub> (2) | u   | u      | u      | u   | u   | u      | 1        |

| Stack Underflow Error (not an actual Reset, STVREN = 0)         | 0000h                  | u <b>(2)</b>     | u   | u      | u      | u   | u   | u      | 1        |

| WDT Time-out during<br>Power-Managed Idle or Sleep<br>modes     | PC + 2                 | ս <b>(2)</b>     | u   | 0      | 0      | u   | u   | u      | u        |

| Interrupt Exit from<br>Power-Managed modes                      | PC + 2                 | u <b>(2)</b>     | u   | u      | 0      | u   | u   | u      | u        |

Legend: u = unchanged

**Note 1:** When the wake-up is due to an interrupt and the GIEH or GIEL bits are set, the PC is loaded with the interrupt vector (008h or 0018h).

2: Reset state is '1' for POR and unchanged for all other Resets when software BOR is enabled (BOREN<1:0> Configuration bits = 01 and SBOREN = 1); otherwise, the Reset state is '0'.

| File Name            | Bit 7                         | Bit 6                         | Bit 5         | Bit 4           | Bit 3                 | Bit 2                 | Bit 1  | Bit 0                  | Value on<br>POR, BOR | Details on<br>Page: |

|----------------------|-------------------------------|-------------------------------|---------------|-----------------|-----------------------|-----------------------|--------|------------------------|----------------------|---------------------|

| SPBRGH               | EUSART Bau                    | d Rate Genera                 | tor High Byte |                 |                       |                       |        |                        | 0000 0000            | 57, 236             |

| SPBRG                | EUSART Bau                    | d Rate Genera                 | itor          |                 |                       |                       |        |                        | 0000 0000            | 57, 236             |

| RCREG                | EUSART Rec                    | eive Register                 |               |                 |                       |                       |        |                        | 0000 0000            | 57, 244             |

| TXREG                | EUSART Trar                   | nsmit Register                |               |                 |                       |                       |        |                        | 0000 0000            | 57, 241             |

| TXSTA                | CSRC                          | TX9                           | TXEN          | SYNC            | SENDB                 | BRGH                  | TRMT   | TX9D                   | 0000 0010            | 57, 243             |

| RCSTA                | SPEN                          | RX9                           | SREN          | CREN            | ADDEN                 | FERR                  | OERR   | RX9D                   | 0000 000x            | 57, 243             |

| EEADR                | EEPROM Add                    | dress Register                |               |                 |                       |                       | •      | •                      | 0000 0000            | 57, 111             |

| EEDATA               | EEPROM Dat                    | a Register                    |               |                 |                       |                       |        |                        | 0000 0000            | 57, 111             |

| EECON2               | EEPROM Cor                    | ntrol Register 2              | (not a physic | al register)    |                       |                       |        |                        | 0000 0000            | 57, 111             |

| EECON1               | EEPGD                         | CFGS                          |               | FREE            | WRERR                 | WREN                  | WR     | RD                     | xx-0 x000            | 57, 111             |

| IPR3<br>Mode 0       | IRXIP                         | WAKIP                         | ERRIP         | TXB2IP          | TXB1IP                | TXB0IP                | RXB1IP | RXB0IP                 | 1111 1111            | 57, 132             |

| IPR3<br>Mode 1, 2    | IRXIP                         | WAKIP                         | ERRIP         | TXBnIP          | TXB1IP <sup>(8)</sup> | TXB0IP <sup>(8)</sup> | RXBnIP | FIFOWMIP               | 1111 1111            | 57, 132             |

| PIR3<br>Mode 0       | IRXIF                         | WAKIF                         | ERRIF         | TXB2IF          | TXB1IF                | TXB0IF                | RXB1IF | RXB0IF                 | 0000 0000            | 57, 126             |

| PIR3<br>Mode 1, 2    | IRXIF                         | WAKIF                         | ERRIF         | TXBnlF          | TXB1IF <sup>(8)</sup> | TXB0IF <sup>(8)</sup> | RXBnIF | FIFOWMIF               | 0000 0000            | 57, 126             |

| PIE3<br>Mode 0       | IRXIE                         | WAKIE                         | ERRIE         | TXB2IE          | TXB1IE                | TXB0IE                | RXB1IE | RXB0IE                 | 0000 0000            | 57, 129             |

| PIE3<br>Mode 1, 2    | IRXIE                         | WAKIE                         | ERRIE         | TXBnIE          | TXB1IE <sup>(8)</sup> | TXB0IE <sup>(8)</sup> | RXBnIE | FIFOMWIE               | 0000 0000            | 57, 129             |

| IPR2                 | OSCFIP                        | CMIP <sup>(9)</sup>           | —             | EEIP            | BCLIP                 | HLVDIP                | TMR3IP | ECCP1IP <sup>(9)</sup> | 11-1 1111            | 57, 131             |

| PIR2                 | OSCFIF                        | CMIF <sup>(9)</sup>           | _             | EEIF            | BCLIF                 | HLVDIF                | TMR3IF | ECCP1IF <sup>(9)</sup> | 00-0 0000            | 58, 125             |

| PIE2                 | OSCFIE                        | CMIE <sup>(9)</sup>           | _             | EEIE            | BCLIE                 | HLVDIE                | TMR3IE | ECCP1IE <sup>(9)</sup> | 00-0 0000            | 58, 128             |

| IPR1                 | PSPIP <sup>(3)</sup>          | ADIP                          | RCIP          | TXIP            | SSPIP                 | CCP1IP                | TMR2IP | TMR1IP                 | 1111 1111            | 58, 130             |

| PIR1                 | PSPIF <sup>(3)</sup>          | ADIF                          | RCIF          | TXIF            | SSPIF                 | CCP1IF                | TMR2IF | TMR1IF                 | 0000 0000            | 58, 124             |

| PIE1                 | PSPIE <sup>(3)</sup>          | ADIE                          | RCIE          | TXIE            | SSPIE                 | CCP1IE                | TMR2IE | TMR1IE                 | 0000 0000            | 58, 127             |

| OSCTUNE              | INTSRC                        | PLLEN <sup>(4)</sup>          | _             | TUN4            | TUN3                  | TUN2                  | TUN1   | TUN0                   | 0q-0 0000            | 33, 58              |

| TRISE <sup>(3)</sup> | IBF                           | OBF                           | IBOV          | PSPMODE         | _                     | TRISE2                | TRISE1 | TRISE0                 | 0000 -111            | 58, 146             |

| TRISD <sup>(3)</sup> | PORTD Data                    | Direction Regi                | ster          |                 |                       |                       |        |                        | 1111 1111            | 58, 143             |

| TRISC                | PORTC Data Direction Register |                               |               |                 |                       |                       |        |                        | 1111 1111            | 58, 141             |

| TRISB                | PORTB Data                    | PORTB Data Direction Register |               |                 |                       |                       |        |                        |                      | 58, 138             |

| TRISA                | TRISA7 <sup>(6)</sup>         | TRISA6 <sup>(6)</sup>         | PORTA Data    | a Direction Reg | ister                 |                       |        |                        | 1111 1111            | 58, 135             |

| LATE <sup>(3)</sup>  | —                             | _                             | —             | _               | _                     | LATE2                 | LATE1  | LATE0                  | xxx                  | 58, 146             |

| LATD <sup>(3)</sup>  | LATD Output                   | Latch Register                |               |                 |                       |                       |        |                        | XXXX XXXX            | 58, 143             |

| LATC                 | LATC Output                   | Latch Register                |               |                 |                       |                       |        |                        | XXXX XXXX            | 58, 141             |

| LATB                 | LATB Output                   | Latch Register                |               |                 |                       |                       |        |                        | XXXX XXXX            | 58, 138             |

| LATA                 | LATA7 <sup>(6)</sup>          | LATA6 <sup>(6)</sup>          | LATA Outpu    | t Latch Registe | r                     |                       |        |                        | XXXX XXXX            | 58, 135             |

| TABLE 6-2: | REGISTER FILE SUMMARY | PIC18F2480/2580/4480/4580) | (CONTINUED) |

|------------|-----------------------|----------------------------|-------------|

|------------|-----------------------|----------------------------|-------------|

**Legend:** x = unknown, u = unchanged, - = unimplemented, q = value depends on condition

Note 1: Bit 21 of the PC is only available in Test mode and Serial Programming modes.

The SBOREN bit is only available when CONFIG2L<1:0> = 01; otherwise, it is disabled and reads as '0'. See Section 5.4 "Brown-out Reset (BOR)".

These registers and/or bits are not implemented on PIC18F2X80 devices and are read as '0'. Reset values are shown for PIC18F4X80 devices; individual unimplemented bits should be interpreted as '-'.

4: The PLLEN bit is only available in specific oscillator configuration; otherwise, it is disabled and reads as '0'. See Section 3.6.4 "PLL in INTOSC Modes".

5: The RE3 bit is only available when Master Clear Reset is disabled (CONFIG3H<7> = 0); otherwise, RE3 reads as '0'. This bit is read-only.

6: RA6/RA7 and their associated latch and direction bits are individually configured as port pins based on various primary oscillator modes. When disabled, these bits read as '0'.

7: CAN bits have multiple functions depending on the selected mode of the CAN module.

8: This register reads all '0's until the ECAN™ technology is set up in Mode 1 or Mode 2.

9: These registers are available on PIC18F4X80 devices only.

## 9.0 8 x 8 HARDWARE MULTIPLIER

### 9.1 Introduction

All PIC18 devices include an 8 x 8 hardware multiplier as part of the ALU. The multiplier performs an unsigned operation and yields a 16-bit result that is stored in the product register pair, PRODH:PRODL. The multiplier's operation does not affect any flags in the STATUS register.

Making multiplication a hardware operation allows it to be completed in a single instruction cycle. This has the advantages of higher computational throughput and reduced code size for multiplication algorithms and allows the PIC18 devices to be used in many applications previously reserved for digital signal processors. A comparison of various hardware and software multiply operations, along with the savings in memory and execution time, is shown in Table 9-1.

## 9.2 Operation

Example 9-1 shows the instruction sequence for an 8 x 8 unsigned multiplication. Only one instruction is required when one of the arguments is already loaded in the WREG register.

Example 9-2 shows the sequence to do an 8 x 8 signed multiplication. To account for the signed bits of the arguments, each argument's Most Significant bit (MSb) is tested and the appropriate subtractions are done.

#### EXAMPLE 9-1: 8 x 8 UNSIGNED MULTIPLY ROUTINE

| MOVF  | ARG1, W | ;                |

|-------|---------|------------------|

| MULWF | ARG2    | ; ARG1 * ARG2 -> |

|       |         | ; PRODH:PRODL    |

|       |         |                  |

## EXAMPLE 9-2: 8 x 8 SIGNED

|       |          | MULTIPLY ROUTINE |  |

|-------|----------|------------------|--|

| MOVF  | ARG1, W  |                  |  |

| MULWF | ARG2     | ; ARG1 * ARG2 -> |  |

|       |          | ; PRODH:PRODL    |  |

| BTFSC | ARG2, SB | ; Test Sign Bit  |  |

| SUBWF | PRODH, F | ; PRODH = PRODH  |  |

|       |          | ; – ARG1         |  |

| MOVF  | ARG2, W  |                  |  |

| BTFSC | ARG1, SB | ; Test Sign Bit  |  |

| SUBWF | PRODH, F | ; PRODH = PRODH  |  |

|       |          | ; – ARG2         |  |

|       |          |                  |  |

|                                 |                           | Program           | Cycles | Time     |          |              |  |

|---------------------------------|---------------------------|-------------------|--------|----------|----------|--------------|--|

| Routine                         | Multiply Method           | Memory<br>(Words) | (Max)  | @ 40 MHz | @ 10 MHz | @ 4 MHz      |  |

| 9 x 9 uppignod                  | Without hardware multiply | 13                | 69     | 6.9 μs   | 27.6 μs  | 69 μs        |  |

| 8 x 8 unsigned                  | Hardware multiply         | 1                 | 1      | 100 ns   | 400 ns   | 1 μs         |  |

| 8 x 8 signed                    | Without hardware multiply | 33                | 91     | 9.1 μs   | 36.4 μs  | 91 μs        |  |

|                                 | Hardware multiply         | 6                 | 6      | 600 ns   | 2.4 μs   | 6 μ <b>s</b> |  |

| 10 × 10 unsigned                | Without hardware multiply | 21                | 242    | 24.2 μs  | 96.8 μs  | 242 μs       |  |

| 16 x 16 unsigned                | Hardware multiply         | 28                | 28     | 2.8 μs   | 11.2 μs  | 28 μs        |  |

| 40 · · · 40 · · · · · · · · · · | Without hardware multiply | 52                | 254    | 25.4 μs  | 102.6 μs | 254 μs       |  |

| 16 x 16 signed                  | Hardware multiply         | 35                | 40     | 4.0 μs   | 16.0 μs  | 40 μs        |  |

### TABLE 9-1: PERFORMANCE COMPARISON FOR VARIOUS MULTIPLY OPERATIONS

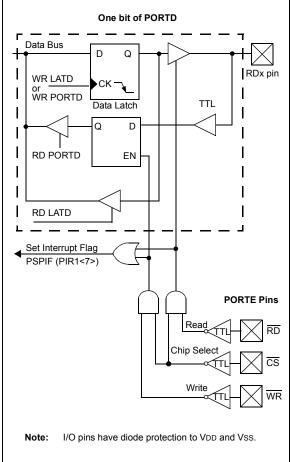

#### 11.6 Parallel Slave Port

| Note: | The Parallel Slave Port is only available on |

|-------|----------------------------------------------|

|       | PIC18F4X80 devices.                          |

In addition to its function as a general I/O port, PORTD can also operate as an 8-bit wide Parallel Slave Port (PSP) or microprocessor port. PSP operation is controlled by the 4 upper bits of the TRISE register (Register 11-1). Setting control bit, PSPMODE (TRISE<4>), enables PSP operation, as long as the Enhanced CCP module is not operating in dual output or quad output PWM mode. In Slave mode, the port is asynchronously readable and writable by the external world.

The PSP can directly interface to an 8-bit microprocessor data bus. The external microprocessor can read or write the PORTD latch as an 8-bit latch. Setting the control bit PSPMODE enables the PORTE I/O pins to become control inputs for the microprocessor port. When set, port pin RE0 is the RD input, RE1 is the WR input and RE2 is the CS (Chip Select) input. For this functionality, the corresponding data direction bits of the TRISE register (TRISE<2:0>) must be configured as inputs (set). The A/D port Configuration bits, PFCG<3:0> (ADCON1<3:0>), must also be set to '1010'.

A write to the PSP occurs when both the  $\overline{CS}$  and  $\overline{WR}$  lines are first detected low and ends when either are detected high. The PSPIF and IBF flag bits are both set when the write ends.

A read from the PSP occurs when both the  $\overline{CS}$  and  $\overline{RD}$  lines are first detected low. The data in PORTD is read out and the OBF bit is set. If the user writes new data to PORTD to set OBF, the data is immediately read out; however, the OBF bit is not set.

When either the  $\overline{CS}$  or  $\overline{RD}$  lines are detected high, the PORTD pins return to the input state and the PSPIF bit is set. User applications should wait for PSPIF to be set before servicing the PSP; when this happens, the IBF and OBF bits can be polled and the appropriate action taken. The timing for the control signals in Write and Read modes is shown in Figure 11-3 and Figure 11-4, respectively.

### FIGURE 11-2: PORTD AND PORTE BLOCK DIAGRAM (PARALLEL SLAVE PORT)

## 12.0 TIMER0 MODULE

The Timer0 module incorporates the following features:

- Software-selectable operation as a timer or counter in both 8-bit or 16-bit modes

- · Readable and writable registers

- Dedicated 8-bit, software programmable

prescaler

- Selectable clock source (internal or external)

- Edge select for external clock

- Interrupt-on-overflow

The T0CON register (Register 12-1) controls all aspects of the module's operation, including the prescale selection. It is both readable and writable.

A simplified block diagram of the Timer0 module in 8-bit mode is shown in Figure 12-1. Figure 12-2 shows a simplified block diagram of the Timer0 module in 16-bit mode.

#### REGISTER 12-1: T0CON: TIMER0 CONTROL REGISTER

| R/W-1  | R/W-1  | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|--------|--------|-------|-------|-------|-------|-------|-------|

| TMR0ON | T08BIT | TOCS  | TOSE  | PSA   | T0PS2 | T0PS1 | T0PS0 |

| bit 7  |        |       |       |       |       |       | bit 0 |

| Legend:          |                                                                                         |                                                                                                                                                                                                                                                                                                               |                                                                   |                    |

|------------------|-----------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|--------------------|

| R = Readable bit |                                                                                         | W = Writable bit                                                                                                                                                                                                                                                                                              | U = Unimplemented bit,                                            | read as '0'        |

| -n = Value       | at POR                                                                                  | '1' = Bit is set                                                                                                                                                                                                                                                                                              | '0' = Bit is cleared                                              | x = Bit is unknown |

| bit 7            |                                                                                         | : Timer0 On/Off Control bit<br>es Timer0<br>Timer0                                                                                                                                                                                                                                                            |                                                                   |                    |

| bit 6            | 1 = Timer                                                                               | imer0 8-Bit/16-Bit Control bi<br>0 is configured as an 8-bit tiı<br>0 is configured as a 16-bit tiı                                                                                                                                                                                                           | mer/counter                                                       |                    |

| bit 5            | 1 = Trans                                                                               | ner0 Clock Source Select bi<br>ition on T0CKI pin input edg<br>al clock (Fosc/4)                                                                                                                                                                                                                              |                                                                   |                    |

| bit 4            | 1 = Increr                                                                              | ner0 Source Edge Select bit<br>nent on high-to-low transition<br>nent on low-to-high transition                                                                                                                                                                                                               | n on T0CKI pin                                                    |                    |

| bit 3            | 1 = TImer                                                                               |                                                                                                                                                                                                                                                                                                               | it<br>Timer0 clock input bypasses<br>er0 clock input comes from p | -                  |

| bit 2-0          | 111 = 1:2<br>110 = 1:1<br>101 = 1:6<br>100 = 1:3<br>011 = 1:1<br>010 = 1:8<br>001 = 1:4 | <ul> <li>&gt;: Timer0 Prescaler Select</li> <li>56 Prescale value</li> <li>28 Prescale value</li> <li>4 Prescale value</li> <li>2 Prescale value</li> <li>6 Prescale value</li> <li>Prescale value</li> <li>Prescale value</li> <li>Prescale value</li> <li>Prescale value</li> <li>Prescale value</li> </ul> | bits                                                              |                    |

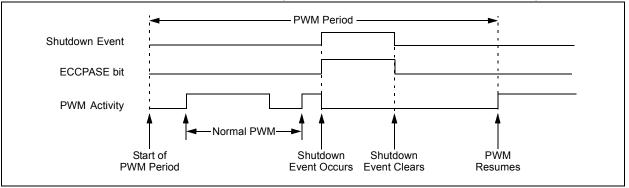

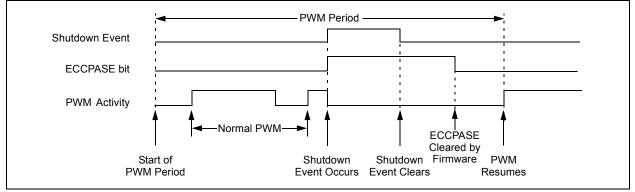

## 17.4.7.1 Auto-Shutdown and Auto-Restart

The auto-shutdown feature can be configured to allow automatic restarts of the module following a shutdown event. This is enabled by setting the PRSEN bit of the ECCP1DEL register (ECCP1DEL<7>).

In Shutdown mode with PRSEN = 1 (Figure 17-10), the ECCPASE bit will remain set for as long as the cause of the shutdown continues. When the shutdown condition clears, the ECCP1ASE bit is cleared. If PRSEN = 0 (Figure 17-11), once a shutdown condition occurs, the ECCPASE bit will remain set until it is cleared by firmware. Once ECCPASE is cleared, the Enhanced PWM will resume at the beginning of the next PWM period.

| Note: | Writing to the ECCPASE bit is disabled |

|-------|----------------------------------------|

|       | while a shutdown condition is active.  |

Independent of the PRSEN bit setting, if the auto-shutdown source is one of the comparators, the shutdown condition is a level. The ECCPASE bit cannot be cleared as long as the cause of the shutdown persists.

The Auto-Shutdown mode can be forced by writing a '1' to the ECCPASE bit.

## 17.4.8 START-UP CONSIDERATIONS

When the ECCP module is used in the PWM mode, the application hardware must use the proper external pull-up and/or pull-down resistors on the PWM output pins. When the microcontroller is released from Reset, all of the I/O pins are in the high-impedance state. The external circuits must keep the power switch devices in the off state until the microcontroller drives the I/O pins with the proper signal levels, or activates the PWM output(s).

The CCP1M<1:0> bits (ECCP1CON<1:0>) allow the user to choose whether the PWM output signals are active-high or active-low for each pair of PWM output pins (P1A/P1C and P1B/P1D). The PWM output polarities must be selected before the PWM pins are configured as outputs. Changing the polarity configuration while the PWM pins are configured as outputs is not recommended, since it may result in damage to the application circuits.

The P1A, P1B, P1C and P1D output latches may not be in the proper states when the PWM module is initialized. Enabling the PWM pins for output at the same time as the ECCP module may cause damage to the application circuit. The ECCP module must be enabled in the proper output mode and complete a full PWM cycle before configuring the PWM pins as outputs. The completion of a full PWM cycle is indicated by the TMR2IF bit being set as the second PWM period begins.

#### FIGURE 17-10: PWM AUTO-SHUTDOWN (PRSEN = 1, AUTO-RESTART ENABLED)

### FIGURE 17-11: PWM AUTO-SHUTDOWN (PRSEN = 0, AUTO-RESTART DISABLED)

#### 18.3.5 MASTER MODE

The master can initiate the data transfer at any time because it controls the SCK. The master determines when the slave (Processor 2, Figure 18-2) is to broadcast data by the software protocol.

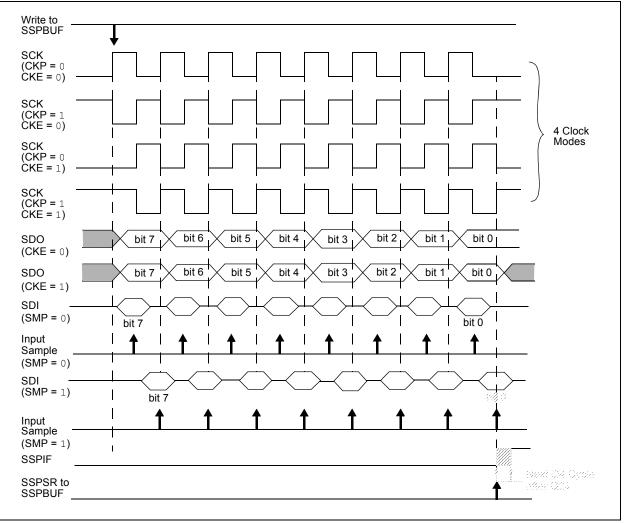

In Master mode, the data is transmitted/received as soon as the SSPBUF register is written to. If the SPI is only going to receive, the SDO output could be disabled (programmed as an input). The SSPSR register will continue to shift in the signal present on the SDI pin at the programmed clock rate. As each byte is received, it will be loaded into the SSPBUF register as if a normal received byte (interrupts and status bits appropriately set). This could be useful in receiver applications as a "Line Activity Monitor" mode. The clock polarity is selected by appropriately programming the CKP bit (SSPCON1<4>). This then, would give waveforms for SPI communication as shown in Figure 18-3, Figure 18-5 and Figure 18-6, where the MSB is transmitted first. In Master mode, the SPI clock rate (bit rate) is user-programmable to be one of the following:

- Fosc/4 (or Tcy)

- Fosc/16 (or 4 Tcy)

- Fosc/64 (or 16 Tcy)

- Timer2 output/2

This allows a maximum data rate (at 40 MHz) of 10.00 Mbps.

Figure 18-3 shows the waveforms for Master mode. When the CKE bit is set, the SDO data is valid before there is a clock edge on SCK. The change of the input sample is shown based on the state of the SMP bit. The time when the SSPBUF is loaded with the received data is shown.

FIGURE 18-3: SPI MODE WAVEFORM (MASTER MODE)

### 18.4.4 CLOCK STRETCHING

Both 7 and 10-Bit Slave modes implement automatic clock stretching during a transmit sequence.

The SEN bit (SSPCON2<0>) allows clock stretching to be enabled during receives. Setting SEN will cause the SCL pin to be held low at the end of each data receive sequence.

#### 18.4.4.1 Clock Stretching for 7-Bit Slave Receive Mode (SEN = 1)

In 7-Bit Slave Receive mode, <u>on the falling edge of the</u> ninth clock at the end of the ACK sequence if the BF bit is set, the CKP bit in the SSPCON1 register is automatically cleared, forcing the SCL output to be held low. The CKP bit being cleared to '0' will assert the SCL line low. The CKP bit must be set in the user's ISR before reception is allowed to continue. By holding the SCL line low, the user has time to service the ISR and read the contents of the SSPBUF before the master device can initiate another receive sequence. This will prevent buffer overruns from occurring (see Figure 18-13).

- Note 1: If the user reads the contents of the SSPBUF before the falling edge of the ninth clock, thus clearing the BF bit, the CKP bit will not be cleared and clock stretching will not occur.

- 2: The CKP bit can be set in software regardless of the state of the BF bit. The user should be careful to clear the BF bit in the ISR before the next receive sequence in order to prevent an overflow condition.

#### 18.4.4.2 Clock Stretching for 10-Bit Slave Receive Mode (SEN = 1)

In 10-Bit Slave Receive mode, during the address sequence, clock stretching automatically takes place but CKP is not cleared. During this time, if the UA bit is set after the ninth clock, clock stretching is initiated. The UA bit is set after receiving the upper byte of the 10-bit address and following the receive of the second byte of the 10-bit address with the R/W bit cleared to '0'. The release of the clock line occurs upon updating SSPADD. Clock stretching will occur on each data receive sequence as described in 7-bit mode.

**Note:** If the user polls the UA bit and clears it by updating the SSPADD register before the falling edge of the ninth clock occurs, and if the user hasn't cleared the BF bit by reading the SSPBUF register before that time, then the CKP bit will still NOT be asserted low. Clock stretching on the basis of the state of the BF bit only occurs during a data sequence, not an address sequence.

#### 18.4.4.3 Clock Stretching for 7-Bit Slave Transmit Mode

7-Bit Slave Transmit mode implements clock stretching by clearing the CKP bit after the falling edge of the ninth clock if the BF bit is clear. This occurs regardless of the state of the SEN bit.

The user's ISR must set the CKP bit before transmission is allowed to continue. By holding the SCL line low, the user has time to service the ISR and load the contents of the SSPBUF before the master device can initiate another transmit sequence (see Figure 18-9).

- Note 1: If the user loads the contents of SSPBUF, setting the BF bit before the falling edge of the ninth clock, the CKP bit will not be cleared and clock stretching will not occur.

- 2: The CKP bit can be set in software regardless of the state of the BF bit.

#### 18.4.4.4 Clock Stretching for 10-Bit Slave Transmit Mode

In 10-Bit Slave Transmit mode, clock stretching is controlled during the first two address sequences by the state of the UA bit, just as it is in 10-Bit Slave Receive mode. The first two addresses are followed by a third address sequence, which contains the high-order bits of the 10-bit address and the R/W bit set to '1'. After the third address sequence is performed, the UA bit is not set, the module is now configured in Transmit mode and clock stretching is controlled by the BF flag as in 7-Bit Slave Transmit mode (see Figure 18-11).

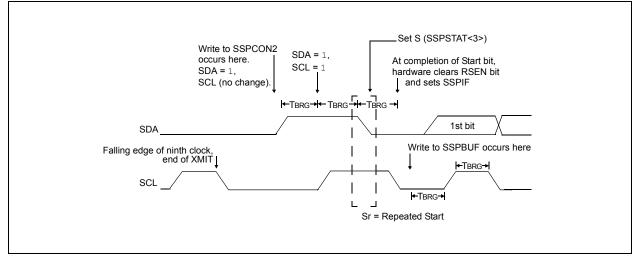

### 18.4.9 I<sup>2</sup>C MASTER MODE REPEATED START CONDITION TIMING

A Repeated Start condition occurs when the RSEN bit (SSPCON2<1>) is programmed high and the I<sup>2</sup>C logic module is in the Idle state. When the RSEN bit is set, the SCL pin is asserted low. When the SCL pin is sampled low, the Baud Rate Generator is loaded with the contents of SSPADD<5:0> and begins counting. The SDA pin is released (brought high) for one Baud Rate Generator count (TBRG). When the Baud Rate Generator times out, and if SDA is sampled high, the SCL pin will be deasserted (brought high). When SCL is sampled high, the Baud Rate Generator is reloaded with the contents of SSPADD<6:0> and begins counting. SDA and SCL must be sampled high for one TBRG. This action is then followed by assertion of the SDA pin (SDA = 0) for one TBRG while SCL is high. Following this, the RSEN bit (SSPCON2<1>) will be automatically cleared and the Baud Rate Generator will not be reloaded, leaving the SDA pin held low. As soon as a Start condition is detected on the SDA and SCL pins, the S bit (SSPSTAT<3>) will be set. The SSPIF bit will not be set until the Baud Rate Generator has timed out.

- Note 1: If RSEN is programmed while any other event is in progress, it will not take effect.

- **2:** A bus collision during the Repeated Start condition occurs if:

- SDA is sampled low when SCL goes from low-to-high.

- SCL goes low before SDA is asserted low. This may indicate that another master is attempting to transmit a data '1'.

Immediately following the SSPIF bit getting set, the user may write the SSPBUF with the 7-bit address in 7-bit mode, or the default first address in 10-bit mode. After the first eight bits are transmitted and an ACK is received, the user may then transmit an additional eight bits of address (10-bit mode) or eight bits of data (7-bit mode).

#### 18.4.9.1 WCOL Status Flag

If the user writes the SSPBUF when a Repeated Start sequence is in progress, the WCOL is set and the contents of the buffer are unchanged (the write doesn't occur).

Note: Because queueing of events is not allowed, writing of the lower 5 bits of SSPCON2 is disabled until the Repeated Start condition is complete.

## FIGURE 18-20: REPEAT START CONDITION WAVEFORM

#### R/W-0 R-0 R/W-0 R/W-0 R/W-0 R/W-0 R-0 R-x SPEN RX9 SREN CREN ADDEN FERR OERR RX9D bit 7 bit 0 Legend: R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' -n = Value at POR '0' = Bit is cleared '1' = Bit is set x = Bit is unknown bit 7 SPEN: Serial Port Enable bit 1 = Serial port enabled (configures RX/DT and TX/CK pins as serial port pins) 0 = Serial port disabled (held in Reset) bit 6 RX9: 9-Bit Receive Enable bit 1 = Selects 9-bit reception 0 = Selects 8-bit reception bit 5 SREN: Single Receive Enable bit Asynchronous mode: Don't care. Synchronous mode - Master: 1 = Enables single receive 0 = Disables single receive This bit is cleared after reception is complete. Synchronous mode - Slave: Don't care. bit 4 **CREN:** Continuous Receive Enable bit Asynchronous mode: 1 = Enables receiver 0 = Disables receiver Synchronous mode: 1 = Enables continuous receive until enable bit CREN is cleared (CREN overrides SREN) 0 = Disables continuous receive bit 3 ADDEN: Address Detect Enable bit Asynchronous mode 9-bit (RX9 = 1): 1 = Enables address detection, enables interrupt and loads the receive buffer when RSR<8> is set 0 = Disables address detection, all bytes are received and ninth bit can be used as parity bit Asynchronous mode 9-bit (RX9 = 0): Don't care. bit 2 FERR: Framing Error bit 1 = Framing error (can be updated by reading RCREG register and receiving next valid byte) 0 = No framing error bit 1 **OERR:** Overrun Error bit 1 = Overrun error (can be cleared by clearing bit CREN) 0 = No overrun error bit 0 RX9D: 9th bit of Received Data This can be an address/data bit or a parity bit and must be calculated by user firmware.

#### REGISTER 19-2: RCSTA: RECEIVE STATUS AND CONTROL REGISTER

| R/W-0         | R/W-0                          | R/W-0            | R/W-0           | R/W-0            | R/W-0            | R/W-0           | R/W-0   |

|---------------|--------------------------------|------------------|-----------------|------------------|------------------|-----------------|---------|

| FIL15_1       | FIL15_0                        | FIL14_1          | FIL14_0         | FIL13_1          | FIL13_0          | FIL12_1         | FIL12_0 |

| bit 7         |                                |                  |                 |                  |                  |                 | bit C   |

|               |                                |                  |                 |                  |                  |                 |         |

| Legend:       |                                |                  |                 |                  |                  |                 |         |

| R = Readable  | e bit                          | W = Writable     | bit             | U = Unimpler     | mented bit, read | l as '0'        |         |

| -n = Value at | POR                            | '1' = Bit is set | t               | '0' = Bit is cle | ared             | x = Bit is unki | nown    |

|               |                                |                  |                 |                  |                  |                 |         |

| bit 7-6       | FIL15_<1:0>:                   | : Filter 15 Sele | ct bits 1 and 0 |                  |                  |                 |         |

|               | 11 = No masl                   | -                |                 |                  |                  |                 |         |

|               | 10 = Filter 15<br>01 = Accepta |                  |                 |                  |                  |                 |         |

|               | 00 = Accepta                   |                  |                 |                  |                  |                 |         |

| bit 5-4       | FIL14_<1:0>:                   | : Filter 14 Sele | ct bits 1 and 0 |                  |                  |                 |         |

|               | 11 = No masl                   | k                |                 |                  |                  |                 |         |

|               | 10 = Filter 15                 |                  |                 |                  |                  |                 |         |

|               | 01 = Accepta<br>00 = Accepta   |                  |                 |                  |                  |                 |         |

| bit 3-2       | •                              | : Filter 13 Sele | ct bits 1 and 0 |                  |                  |                 |         |

|               | 11 = No masl                   |                  |                 |                  |                  |                 |         |

|               | 10 = Filter 15                 |                  |                 |                  |                  |                 |         |

|               | 01 = Accepta                   |                  |                 |                  |                  |                 |         |

| h:4 0         | 00 = Accepta                   |                  |                 |                  |                  |                 |         |

| bit 1-0       | 11 = No mas                    | : Filter 12 Sele | ct bits 1 and 0 |                  |                  |                 |         |

|               | 10 = Filter 15                 | -                |                 |                  |                  |                 |         |

|               | 01 = Accepta                   |                  |                 |                  |                  |                 |         |

|               | 00 = Accepta                   | nce Mask 0       |                 |                  |                  |                 |         |

|               |                                |                  |                 |                  |                  |                 |         |

## REGISTER 24-51: MSEL3: MASK SELECT REGISTER 3<sup>(1)</sup>

**Note 1:** This register is available in Mode 1 and 2 only.

| Address <sup>(1)</sup> | Name                       | Address | Name                       | Address | Name                       | Address | Name |

|------------------------|----------------------------|---------|----------------------------|---------|----------------------------|---------|------|

| E7Fh                   | CANCON_RO4 <sup>(2)</sup>  | E5Fh    | CANCON_RO6 <sup>(2)</sup>  | E3Fh    | CANCON_RO8 <sup>(2)</sup>  | E1Fh    | (4)  |

| E7Eh                   | CANSTAT_RO4 <sup>(2)</sup> | E5Eh    | CANSTAT_RO6 <sup>(2)</sup> | E3Eh    | CANSTAT_RO8 <sup>(2)</sup> | E1Eh    | (4)  |

| E7Dh                   | B5D7                       | E5Dh    | B3D7                       | E3Dh    | B1D7                       | E1Dh    | (4)  |

| E7Ch                   | B5D6                       | E5Ch    | B3D6                       | E3Ch    | B1D6                       | E1Ch    | (4)  |

| E7Bh                   | B5D5                       | E5Bh    | B3D5                       | E3Bh    | B1D5                       | E1Bh    | (4)  |

| E7Ah                   | B5D4                       | E5Ah    | B3D4                       | E3Ah    | B1D4                       | E1Ah    | (4)  |

| E79h                   | B5D3                       | E59h    | B3D3                       | E39h    | B1D3                       | E19h    | (4)  |

| E78h                   | B5D2                       | E58h    | B3D2                       | E38h    | B1D2                       | E18h    | (4)  |

| E77h                   | B5D1                       | E57h    | B3D1                       | E37h    | B1D1                       | E17h    | (4)  |

| E76h                   | B5D0                       | E56h    | B3D0                       | E36h    | B1D0                       | E16h    | (4)  |

| E75h                   | B5DLC                      | E55h    | B3DLC                      | E35h    | B1DLC                      | E15h    | (4)  |

| E74h                   | B5EIDL                     | E54h    | B3EIDL                     | E34h    | B1EIDL                     | E14h    | (4)  |

| E73h                   | B5EIDH                     | E53h    | <b>B3EIDH</b>              | E33h    | B1EIDH                     | E13h    | (4)  |

| E72h                   | B5SIDL                     | E52h    | B3SIDL                     | E32h    | B1SIDL                     | E12h    | (4)  |

| E71h                   | B5SIDH                     | E51h    | B3SIDH                     | E31h    | B1SIDH                     | E11h    | (4)  |

| E70h                   | B5CON                      | E50h    | B3CON                      | E30h    | B1CON                      | E10h    | (4)  |

| E6Fh                   | CANCON_RO5                 | E4Fh    | CANCON_RO7                 | E2Fh    | CANCON_RO9                 | E0Fh    | (4)  |

| E6Eh                   | CANSTAT_RO5                | E4Eh    | CANSTAT_RO7                | E2Eh    | CANSTAT_RO9                | E0Eh    | (4)  |

| E6Dh                   | B4D7                       | E4Dh    | B2D7                       | E2Dh    | B0D7                       | E0Dh    | (4)  |

| E6Ch                   | B4D6                       | E4Ch    | B2D6                       | E2Ch    | B0D6                       | E0Ch    | (4)  |

| E6Bh                   | B4D5                       | E4Bh    | B2D5                       | E2Bh    | B0D5                       | E0Bh    | (4)  |

| E6Ah                   | B4D4                       | E4Ah    | B2D4                       | E2Ah    | B0D4                       | E0Ah    | (4)  |

| E69h                   | B4D3                       | E49h    | B2D3                       | E29h    | B0D3                       | E09h    | (4)  |

| E68h                   | B4D2                       | E48h    | B2D2                       | E28h    | B0D2                       | E08h    | (4)  |

| E67h                   | B4D1                       | E47h    | B2D1                       | E27h    | B0D1                       | E07h    | (4)  |

| E66h                   | B4D0                       | E46h    | B2D0                       | E26h    | B0D0                       | E06h    | (4)  |

| E65h                   | B4DLC                      | E45h    | B2DLC                      | E25h    | B0DLC                      | E05h    | (4)  |

| E64h                   | B4EIDL                     | E44h    | B2EIDL                     | E24h    | <b>B0EIDL</b>              | E04h    | (4)  |

| E63h                   | B4EIDH                     | E43h    | B2EIDH                     | E23h    | B0EIDH                     | E03h    | (4)  |

| E62h                   | B4SIDL                     | E42h    | B2SIDL                     | E22h    | B0SIDL                     | E02h    | (4)  |

| E61h                   | B4SIDH                     | E41h    | B2SIDH                     | E21h    | B0SIDH                     | E01h    | (4)  |

| E60h                   | B4CON                      | E40h    | B2CON                      | E20h    | B0CON                      | E00h    | (4)  |

### TABLE 24-1: CAN CONTROLLER REGISTER MAP (CONTINUED)

Note 1: Shaded registers are available in Access Bank low area, while the rest are available in Bank 15.

2: CANSTAT register is repeated in these locations to simplify application firmware. Unique names are given for each instance of the controller register due to the Microchip header file requirement.

3: These registers are not CAN registers.

4: Unimplemented registers are read as '0'.

| GOTO                    | Uncondit                  | ional Branc            | h                                         | INCF                                  | Incremen                                                    | tf                                                                                                |                                                 |

|-------------------------|---------------------------|------------------------|-------------------------------------------|---------------------------------------|-------------------------------------------------------------|---------------------------------------------------------------------------------------------------|-------------------------------------------------|

| Syntax:                 | GOTO k                    |                        |                                           | Syntax:                               | INCF f{,c                                                   | 1 {,a}}                                                                                           |                                                 |

| Operands:               | $0 \le k \le 104$         | 8575                   |                                           | Operands:                             | $0 \leq f \leq 255$                                         |                                                                                                   |                                                 |

| Operation:              | $k \rightarrow PC<20$     | ):1>                   |                                           |                                       | d ∈ [0,1]                                                   |                                                                                                   |                                                 |

| Status Affected:        | None                      |                        |                                           | Operation:                            | $a \in [0,1]$<br>(f) + 1 $\rightarrow de$                   | act                                                                                               |                                                 |

| Encoding:               |                           |                        |                                           | Status Affected:                      | $(1) \neq 1 \rightarrow 0$<br>C, DC, N, (                   |                                                                                                   |                                                 |

| 1st word (k<7:0>)       | 1110                      | ,                      | kk kkkk <sub>0</sub>                      |                                       | <b></b>                                                     |                                                                                                   |                                                 |

| 2nd word(k<19:8>        | 1111                      | k <sub>19</sub> kkk kk | kk kkkk <sub>8</sub>                      | Encoding:<br>Description:             | 0010                                                        | 10da ff                                                                                           | ff ffff                                         |

| Description:            | anywhere w<br>2-Mbyte me  | two-cycle              |                                           | Decomption.                           | incremente<br>placed in W<br>placed bac<br>lf 'a' is '0', t | d. If 'd' is '0', t<br>/. If 'd' is '1', tf<br>k in register 'f'<br>he Access Ba<br>he BSR is use | the result is<br>ne result is<br>nk is selected |

| Words:                  | 2                         |                        |                                           |                                       |                                                             | nd the extend                                                                                     | ed instruction                                  |

| Cycles:                 | 2                         |                        |                                           |                                       |                                                             | led, this instru                                                                                  |                                                 |

| Q Cycle Activity:       |                           |                        |                                           |                                       |                                                             | Literal Offset                                                                                    | •                                               |

| Q1                      | Q2                        | Q3                     | Q4                                        |                                       |                                                             | never f ≤ 95 (5<br>5. <b>2.3 "Byte-O</b> r                                                        | ,                                               |

| Decode                  | Read literal<br>'k'<7:0>, | No<br>operation        | Read literal<br>'k'<19:8>,<br>Write to PC |                                       | Bit-Oriente                                                 | ed Instruction<br>set Mode" for                                                                   | ns in Indexed                                   |

| No                      | No                        | No                     | No                                        | Words:                                | 1                                                           |                                                                                                   |                                                 |

| operation               | operation                 | operation              | operation                                 | Cycles:                               | 1                                                           |                                                                                                   |                                                 |

|                         |                           |                        |                                           | Q Cycle Activity:                     |                                                             |                                                                                                   |                                                 |

| Example:                | GOTO THE                  | RE                     |                                           | Q1                                    | Q2                                                          | Q3                                                                                                | Q4                                              |

| After Instructi<br>PC = | on<br>Address (T          | HERE)                  |                                           | Decode                                | Read<br>register 'f'                                        | Process<br>Data                                                                                   | Write to destination                            |

|                         |                           |                        |                                           | Example:                              | INCF                                                        | CNT, 1, 0                                                                                         | )                                               |

|                         |                           |                        |                                           | Before Instruc<br>CNT<br>Z<br>C<br>DC | tion<br>= FFh<br>= 0<br>= ?<br>= ?                          |                                                                                                   |                                                 |

After Instruction

CNT Z C DC

= = =

| MULLW             | Multiply                                                               | Multiply Literal with W                                                                                                                                                                                                   |       |                                      |  |  |  |  |

|-------------------|------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|--------------------------------------|--|--|--|--|

| Syntax:           | MULLW                                                                  | MULLW k                                                                                                                                                                                                                   |       |                                      |  |  |  |  |

| Operands:         | $0 \le k \le 258$                                                      | 5                                                                                                                                                                                                                         |       |                                      |  |  |  |  |

| Operation:        | (W) x k $\rightarrow$                                                  | PRODH:                                                                                                                                                                                                                    | PRODL |                                      |  |  |  |  |

| Status Affected:  | None                                                                   |                                                                                                                                                                                                                           |       |                                      |  |  |  |  |

| Encoding:         | 0000                                                                   | 1101                                                                                                                                                                                                                      | kkkk  | kkkk                                 |  |  |  |  |

| Description:      | out betwee<br>8-bit literal<br>placed in t<br>pair. PROI<br>W is uncha | An unsigned multiplication is carried<br>out between the contents of W and the<br>8-bit literal 'k'. The 16-bit result is<br>placed in the PRODH:PRODL register<br>pair. PRODH contains the high byte.<br>W is unchanged. |       |                                      |  |  |  |  |

|                   | Note that r<br>possible in                                             | None of the Status flags are affected.<br>Note that neither overflow nor carry is<br>possible in this operation. A zero result<br>is possible but not detected.                                                           |       |                                      |  |  |  |  |

| Words:            | 1                                                                      |                                                                                                                                                                                                                           |       |                                      |  |  |  |  |

| Cycles:           | 1                                                                      |                                                                                                                                                                                                                           |       |                                      |  |  |  |  |

| Q Cycle Activity: |                                                                        |                                                                                                                                                                                                                           |       |                                      |  |  |  |  |

| Q1                | Q2                                                                     | Q3                                                                                                                                                                                                                        |       | Q4                                   |  |  |  |  |

| Decode            | Read<br>literal 'k'                                                    | Proce<br>Data                                                                                                                                                                                                             | i r   | Write<br>egisters<br>PRODH:<br>PRODL |  |  |  |  |

| Example:          | MIITIM                                                                 | 0C4b                                                                                                                                                                                                                      |       |                                      |  |  |  |  |

| Example:           | MULLW | 0C4h |

|--------------------|-------|------|

| Before Instructior | า     |      |

| W                  | =     | E2h  |

| PRODH              | =     | ?    |

| PRODL              | =     | ?    |

| After Instruction  |       |      |

| W                  | =     | E2h  |

| PRODH              | =     | ADh  |

| PRODL              | =     | 08h  |

|                    |       |      |

| MULWF                                                           |                                                                                                                                                                                                                                                                          | W with f                                                                                                                                                                                                   |                                                                                                                                                                                                      |                                                                                                                                       |

|-----------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                                                         | MULWF                                                                                                                                                                                                                                                                    | f {,a}                                                                                                                                                                                                     |                                                                                                                                                                                                      |                                                                                                                                       |

| Operands:                                                       | 0 ≤ f ≤ 255<br>a ∈ [0,1]                                                                                                                                                                                                                                                 | 5                                                                                                                                                                                                          |                                                                                                                                                                                                      |                                                                                                                                       |

| Operation:                                                      |                                                                                                                                                                                                                                                                          | > PRODH:                                                                                                                                                                                                   | PRODI                                                                                                                                                                                                |                                                                                                                                       |

| Status Affected:                                                | None                                                                                                                                                                                                                                                                     | / I KODII.                                                                                                                                                                                                 | TROBE                                                                                                                                                                                                |                                                                                                                                       |

| Encoding:                                                       | 0000                                                                                                                                                                                                                                                                     | 001a                                                                                                                                                                                                       | ffff                                                                                                                                                                                                 | ffff                                                                                                                                  |

|                                                                 | register fill<br>result is st<br>register pa<br>high byte.<br>unchange<br>None of th<br>Note that i<br>possible in<br>result is po<br>If 'a' is '0',<br>selected. I<br>to select th<br>If 'a' is '0'<br>instruction<br>Offset Add<br>$f \le 95$ (5FH<br><b>"Byte-Ori</b> | e Status fli<br>neither over<br>n this opera<br>ossible but<br>the Access<br>f 'a' is '1', '<br>ne GPR ba<br>and the ex<br>set is ena<br>operates<br>tressing m<br>n). See Sec<br>ented and<br>ns in Indez | f'. The 1<br>PRODE<br>I contair<br>ad 'f' are<br>ags are<br>erflow nc<br>ation. A :<br>not dete<br>s Bank i<br>the BSR<br>ank.<br>tended<br>bled, thi<br>in Index<br>ode whe<br>ction 26<br>Bit-Orie | 6-bit<br>1:PRODI<br>is the<br>affected.<br>or carry is<br>zero<br>ected.<br>s<br>is used<br>s<br>ed Litera<br>enever<br>.2.3<br>ented |

| Words:                                                          | 1                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                            |                                                                                                                                                                                                      |                                                                                                                                       |

| Cycles:                                                         | 1                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                            |                                                                                                                                                                                                      |                                                                                                                                       |