#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 25MHz                                                                     |

| Connectivity               | CANbus, I <sup>2</sup> C, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                               |

| Number of I/O              | 25                                                                        |

| Program Memory Size        | 32KB (16K x 16)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 1.5K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                               |

| Data Converters            | A/D 8x10b                                                                 |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Through Hole                                                              |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                   |

| Supplier Device Package    | 28-SPDIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f2580-e-sp |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Pin Name                                   | Pin Number |     |                  | Pin             | Buffer                       | Description                                                                                    |

|--------------------------------------------|------------|-----|------------------|-----------------|------------------------------|------------------------------------------------------------------------------------------------|

| Pin Name                                   | PDIP       | QFN | TQFP             | Туре            | Туре                         | Description                                                                                    |

|                                            |            |     |                  |                 |                              | PORTC is a bidirectional I/O port.                                                             |

| RC0/T1OSO/T13CKI<br>RC0<br>T1OSO<br>T13CKI | 15         | 34  | 32               | I/O<br>O<br>I   | ST<br>—<br>ST                | Digital I/O.<br>Timer1 oscillator output.<br>Timer1/Timer3 external clock input.               |

| RC1/T1OSI<br>RC1<br>T1OSI                  | 16         | 35  | 35               | I/O<br>I        | ST<br>CMOS                   | Digital I/O.<br>Timer1 oscillator input.                                                       |

| RC2/CCP1<br>RC2<br>CCP1                    | 17         | 36  | 36               | I/O<br>I/O      | ST<br>ST                     | Digital I/O.<br>Capture 1 input/Compare 1 output/PWM1 output.                                  |

| RC3/SCK/SCL<br>RC3<br>SCK                  | 18         | 37  | 37               | I/O<br>I/O      | ST<br>ST                     | Digital I/O.<br>Synchronous serial clock input/output for<br>SPI mode.                         |

| SCL                                        |            |     |                  | I/O             | l <sup>2</sup> C             | Synchronous serial clock input/output for<br>I <sup>2</sup> C™ mode.                           |

| RC4/SDI/SDA<br>RC4<br>SDI<br>SDA           | 23         | 42  | 42               | I/O<br>I<br>I/O | ST<br>ST<br>I <sup>2</sup> C | Digital I/O.<br>SPI data in.<br>I <sup>2</sup> C data I/O.                                     |

| RC5/SDO<br>RC5<br>SDO                      | 24         | 43  | 43               | I/O<br>O        | ST<br>—                      | Digital I/O.<br>SPI data out.                                                                  |

| RC6/TX/CK<br>RC6<br>TX<br>CK               | 25         | 44  | 44               | I/O<br>O<br>I/O | ST<br>—<br>ST                | Digital I/O.<br>EUSART asynchronous transmit.<br>EUSART synchronous clock (see related RX/DT). |

| RC7/RX/DT<br>RC7<br>RX<br>DT               | 26         | 1   | 1                | I/O<br>I<br>I/O | ST<br>ST<br>ST               | Digital I/O.<br>EUSART asynchronous receive.<br>EUSART synchronous data (see related TX/CK).   |

| Legend: TTL = TTL<br>ST = Schr<br>O = Outp | nitt Trig  |     | ut<br>It with Cl | MOS le          |                              | MOS = CMOS compatible input or output<br>= Input                                               |

O = Output  $I^2C$  =  $I^2C^{TM}$ /SMBus input buffer

| TABLE 5-4:         INITIALIZATION CONI           Register         Applicable Devices |      | Power-on Reset,<br>Brown-out Reset | - REGISTERS (CONTIN<br>MCLR Resets,<br>WDT Reset,<br>RESET Instruction,<br>Stack Resets | Wake-up via WDT<br>or Interrupt |           |           |           |

|--------------------------------------------------------------------------------------|------|------------------------------------|-----------------------------------------------------------------------------------------|---------------------------------|-----------|-----------|-----------|

| RXF13EIDL <sup>(6)</sup>                                                             | 2480 | 2580                               | 4480                                                                                    | 4580                            | XXXX XXXX | սսսս սսսս | սսսս սսսս |

| RXF13EIDH <sup>(6)</sup>                                                             | 2480 | 2580                               | 4480                                                                                    | 4580                            | XXXX XXXX | սսսս սսսս | սսսս սսսս |

| RXF13SIDL <sup>(6)</sup>                                                             | 2480 | 2580                               | 4480                                                                                    | 4580                            | xxx- x-xx | uuu- u-uu | uuu- u-uu |

| RXF13SIDH <sup>(6)</sup>                                                             | 2480 | 2580                               | 4480                                                                                    | 4580                            | XXXX XXXX | սսսս սսսս | սսսս սսսս |

| RXF12EIDL <sup>(6)</sup>                                                             | 2480 | 2580                               | 4480                                                                                    | 4580                            | XXXX XXXX | นนนน นนนน | นนนน นนนน |

| RXF12EIDH <sup>(6)</sup>                                                             | 2480 | 2580                               | 4480                                                                                    | 4580                            | XXXX XXXX | սսսս սսսս | սսսս սսսս |

| RXF12SIDL <sup>(6)</sup>                                                             | 2480 | 2580                               | 4480                                                                                    | 4580                            | XXX- X-XX | uuu- u-uu | uuu- u-uu |

| RXF12SIDH <sup>(6)</sup>                                                             | 2480 | 2580                               | 4480                                                                                    | 4580                            | XXXX XXXX | սսսս սսսս | սսսս սսսս |

| RXF11EIDL <sup>(6)</sup>                                                             | 2480 | 2580                               | 4480                                                                                    | 4580                            | XXXX XXXX | սսսս սսսս | uuuu uuuu |

| RXF11EIDH <sup>(6)</sup>                                                             | 2480 | 2580                               | 4480                                                                                    | 4580                            | XXXX XXXX | սսսս սսսս | uuuu uuuu |

| RXF11SIDL <sup>(6)</sup>                                                             | 2480 | 2580                               | 4480                                                                                    | 4580                            | XXX- X-XX | uuu- u-uu | uuu- u-uu |

| RXF11SIDH <sup>(6)</sup>                                                             | 2480 | 2580                               | 4480                                                                                    | 4580                            | XXXX XXXX | սսսս սսսս | սսսս սսսս |

| RXF10EIDL <sup>(6)</sup>                                                             | 2480 | 2580                               | 4480                                                                                    | 4580                            | XXXX XXXX | սսսս սսսս | -uuu uuuu |

| RXF10EIDH <sup>(6)</sup>                                                             | 2480 | 2580                               | 4480                                                                                    | 4580                            | XXXX XXXX | սսսս սսսս | -uuu uuuu |

| RXF10SIDL <sup>(6)</sup>                                                             | 2480 | 2580                               | 4480                                                                                    | 4580                            | XXX- X-XX | uuu- u-uu | -uuu uuuu |

| RXF10SIDH <sup>(6)</sup>                                                             | 2480 | 2580                               | 4480                                                                                    | 4580                            | XXXX XXXX | սսսս սսսս | -uuu uuuu |

| RXF9EIDL <sup>(6)</sup>                                                              | 2480 | 2580                               | 4480                                                                                    | 4580                            | XXXX XXXX | սսսս սսսս | -uuu uuuu |

| RXF9EIDH <sup>(6)</sup>                                                              | 2480 | 2580                               | 4480                                                                                    | 4580                            | XXXX XXXX | սսսս սսսս | -uuu uuuu |

| RXF9SIDL <sup>(6)</sup>                                                              | 2480 | 2580                               | 4480                                                                                    | 4580                            | XXX- X-XX | uuu- u-uu | -uuu uuuu |

| RXF9SIDH <sup>(6)</sup>                                                              | 2480 | 2580                               | 4480                                                                                    | 4580                            | XXXX XXXX | սսսս սսսս | -uuu uuuu |

| RXF8EIDL <sup>(6)</sup>                                                              | 2480 | 2580                               | 4480                                                                                    | 4580                            | XXXX XXXX | սսսս սսսս | -uuu uuuu |

| RXF8EIDH <sup>(6)</sup>                                                              | 2480 | 2580                               | 4480                                                                                    | 4580                            | XXXX XXXX | սսսս սսսս | -uuu uuuu |

| RXF8SIDL <sup>(6)</sup>                                                              | 2480 | 2580                               | 4480                                                                                    | 4580                            | xxx- x-xx | uuu- u-uu | -uuu uuuu |

| RXF8SIDH <sup>(6)</sup>                                                              | 2480 | 2580                               | 4480                                                                                    | 4580                            | XXXX XXXX | սսսս սսսս | -uuu uuuu |

| RXF7EIDL <sup>(6)</sup>                                                              | 2480 | 2580                               | 4480                                                                                    | 4580                            | XXXX XXXX | սսսս սսսս | -uuu uuuu |

| RXF7EIDH <sup>(6)</sup>                                                              | 2480 | 2580                               | 4480                                                                                    | 4580                            | XXXX XXXX | սսսս սսսս | -uuu uuuu |

| RXF7SIDL <sup>(6)</sup>                                                              | 2480 | 2580                               | 4480                                                                                    | 4580                            | xxx- x-xx | uuu- u-uu | -uuu uuuu |

| RXF7SIDH <sup>(6)</sup>                                                              | 2480 | 2580                               | 4480                                                                                    | 4580                            | XXXX XXXX | սսսս սսսս | -uuu uuuu |

| RXF6EIDL <sup>(6)</sup>                                                              | 2480 | 2580                               | 4480                                                                                    | 4580                            | XXXX XXXX | սսսս սսսս | -uuu uuuu |

| RXF6EIDH <sup>(6)</sup>                                                              | 2480 | 2580                               | 4480                                                                                    | 4580                            | XXXX XXXX | սսսս սսսս | -uuu uuuu |

| RXF6SIDL <sup>(6)</sup>                                                              | 2480 | 2580                               | 4480                                                                                    | 4580                            | xxx- x-xx | uuu- u-uu | -uuu uuuu |

| RXF6SIDH <sup>(6)</sup>                                                              | 2480 | 2580                               | 4480                                                                                    | 4580                            | XXXX XXXX | นนนน นนนน | -uuu uuuu |

|                                                                                      |      | l                                  | I                                                                                       |                                 |           |           | I         |

#### TABLE 5-4: INITIALIZATION CONDITIONS FOR ALL REGISTERS (CONTINUED)

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition. Shaded cells indicate conditions do not apply for the designated device.

Note 1: One or more bits in the INTCONx or PIRx registers will be affected (to cause wake-up).

2: When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the PC is loaded with the interrupt vector (0008h or 0018h).

- **3:** When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the TOSU, TOSH and TOSL are updated with the current value of the PC. The STKPTR is modified to point to the next location in the hardware stack.

- 4: See Table 5-3 for Reset value for specific condition.

- **5:** Bits 6 and 7 of PORTA, LATA and TRISA are enabled, depending on the oscillator mode selected. When not enabled as PORTA pins, they are disabled and read '0'.

- 6: This register reads all '0's until ECAN™ technology is set up in Mode 1 or Mode 2.

#### 6.0 MEMORY ORGANIZATION

There are three types of memory in PIC18 Enhanced microcontroller devices:

- Program Memory

- Data RAM

- Data EEPROM

As Harvard architecture devices, the data and program memories use separate busses; this allows for concurrent access of the two memory spaces. The data EEPROM, for practical purposes, can be regarded as a peripheral device, since it is addressed and accessed through a set of control registers.

Additional detailed information on the operation of the Flash program memory is provided in **Section 7.0 "Flash Program Memory"**. Data EEPROM is discussed separately in **Section 8.0 "Data EEPROM Memory"**.

#### 6.1 Program Memory Organization

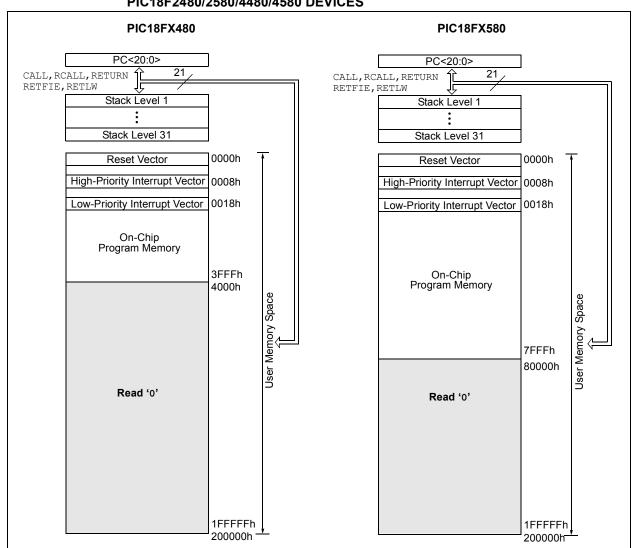

PIC18 microcontrollers implement a 21-bit program counter, which is capable of addressing a 2-Mbyte program memory space. Accessing a location between upper boundary of the physically implemented memory and the 2-Mbyte address will return all '0's (a NOP instruction).

The PIC18F2480 and PIC18F4480 each have 16 Kbytes of Flash memory and can store up to 8,192 single-word instructions. The PIC18F2580 and PIC18F4580 each have 32 Kbytes of Flash memory and can store up to 16,384 single-word instructions.

PIC18 devices have two interrupt vectors. The Reset vector address is at 0000h and the interrupt vector addresses are at 0008h and 0018h.

The program memory maps for PIC18FX480 and PIC18FX580 devices are shown in Figure 6-1.

#### FIGURE 6-1: PROGRAM MEMORY MAP AND STACK FOR PIC18F2480/2580/4480/4580 DEVICES

| Address | Name                     | Address | Name               | Address | Name              | Address | Name |

|---------|--------------------------|---------|--------------------|---------|-------------------|---------|------|

| EFFh    | _                        | EDFh    |                    | EBFh    |                   | E9Fh    |      |

| EFEh    | _                        | EDEh    | _                  | EBEh    | _                 | E9Eh    | _    |

| EFDh    | _                        | EDDh    | _                  | EBDh    | _                 | E9Dh    | _    |

| EFCh    | _                        | EDCh    | _                  | EBCh    | _                 | E9Ch    | _    |

| EFBh    | _                        | EDBh    | _                  | EBBh    | _                 | E9Bh    | _    |

| EFAh    | _                        | EDAh    | _                  | EBAh    | _                 | E9Ah    | _    |

| EF9h    | _                        | ED9h    | _                  | EB9h    | _                 | E99h    | _    |

| EF8h    | _                        | ED8h    | _                  | EB8h    | _                 | E98h    | _    |

| EF7h    | —                        | ED7h    | _                  | EB7h    | _                 | E97h    | _    |

| EF6h    | _                        | ED6h    | _                  | EB6h    | _                 | E96h    | _    |

| EF5h    | _                        | ED5h    | _                  | EB5h    | _                 | E95h    | _    |

| EF4h    | _                        | ED4h    | _                  | EB4h    | _                 | E94h    | _    |

| EF3h    | _                        | ED3h    | _                  | EB3h    | _                 | E93h    | _    |

| EF2h    | _                        | ED2h    | _                  | EB2h    | _                 | E92h    | _    |

| EF1h    | —                        | ED1h    | _                  | EB1h    | _                 | E91h    | _    |

| EF0h    | —                        | ED0h    | _                  | EB0h    | _                 | E90h    | _    |

| EEFh    | _                        | ECFh    | _                  | EAFh    | _                 | E8Fh    | _    |

| EEEh    | —                        | ECEh    | _                  | EAEh    | _                 | E8Eh    | _    |

| EEDh    | —                        | ECDh    | _                  | EADh    | _                 | E8Dh    | _    |

| EECh    | _                        | ECCh    | _                  | EACh    | _                 | E8Ch    | _    |

| EEBh    | —                        | ECBh    | _                  | EABh    | _                 | E8Bh    | _    |

| EEAh    | _                        | ECAh    | _                  | EAAh    | _                 | E8Ah    | _    |

| EE9h    | _                        | EC9h    | _                  | EA9h    | _                 | E89h    | _    |

| EE8h    | —                        | EC8h    | _                  | EA8h    | _                 | E88h    | _    |

| EE7h    | —                        | EC7h    | _                  | EA7h    | _                 | E87h    | _    |

| EE6h    | _                        | EC6h    | _                  | EA6h    | _                 | E86h    | _    |

| EE5h    | _                        | EC5h    | _                  | EA5h    | _                 | E85h    | _    |

| EE4h    | _                        | EC4h    | _                  | EA4h    | _                 | E84h    | _    |

| EE3h    |                          | EC3h    | —                  | EA3h    |                   | E83h    |      |

| EE2h    |                          | EC2h    | _                  | EA2h    |                   | E82h    |      |

| EE1h    | _                        | EC1h    | —                  | EA1h    | _                 | E81h    | _    |

| EE0h    |                          | EC0h    | _                  | EA0h    | _                 | E80h    |      |

|         | Pagiatora available only |         | V90 dovices: other |         | ators road as 'o' |         |      |

### TABLE 6-1:SPECIAL FUNCTION REGISTER MAP FOR<br/>PIC18F2480/2580/4480/4580 DEVICES (CONTINUED)

Note 1: Registers available only on PIC18F4X80 devices; otherwise, the registers read as '0'.

2: When any TX\_ENn bit in RX\_TX\_SELn is set, then the corresponding bit in this register has transmit properties.

3: This is not a physical register.

| EXAMPLE 7-3:   | WRITIN | G TO FLASH PROGRA | AM MEMORY (CONTINUED)           |

|----------------|--------|-------------------|---------------------------------|

| PROGRAM MEMORY |        |                   |                                 |

| _              | BSF    | EECON1, EEPGD     | ; point to Flash program memory |

|                | BCF    | EECON1, CFGS      | ; access Flash program memory   |

|                | BSF    | EECON1, WREN      | ; enable write to memory        |

|                | BCF    | INTCON, GIE       | ; disable interrupts            |

|                | MOVLW  | 55h               |                                 |

| Required       | MOVWF  | EECON2            | ; write 55h                     |

| Sequence       | MOVLW  | 0AAh              |                                 |

|                | MOVWF  | EECON2            | ; write OAAh                    |

|                | BSF    | EECON1, WR        | ; start program (CPU stall)     |

|                | DECFSZ | COUNTER1          |                                 |

|                | BRA    | WRITE BUFFER BACK |                                 |

|                | BSF    | INTCON, GIE       | ; re-enable interrupts          |

|                | BCF    | EECON1, WREN      | ; disable write to memory       |

|                |        |                   |                                 |

#### 7.5.2 WRITE VERIFY

Depending on the application, good programming practice may dictate that the value written to the memory should be verified against the original value. This should be used in applications where excessive writes can stress bits near the specification limit.

### 7.5.3 UNEXPECTED TERMINATION OF WRITE OPERATION

If a write is terminated by an unplanned event, such as loss of power or an unexpected Reset, the memory location just programmed should be verified and reprogrammed if needed. If the write operation is interrupted by a MCLR Reset or a WDT time-out Reset during normal operation, the user can check the WRERR bit and rewrite the location(s) as needed.

### 7.5.4 PROTECTION AGAINST SPURIOUS WRITES

To protect against spurious writes to Flash program memory, the write initiate sequence must also be followed. See **Section 25.0** "**Special Features of the CPU**" for more detail.

#### 7.6 Flash Program Operation During Code Protection

See Section 25.5 "Program Verification and Code Protection" for details on code protection of Flash program memory.

| Name    | Bit 7                                                                        | Bit 6               | Bit 5  | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0                  | Reset<br>Values<br>on Page: |

|---------|------------------------------------------------------------------------------|---------------------|--------|-------|-------|--------|--------|------------------------|-----------------------------|

| TBLPTRU | bit21 <sup>(3)</sup> Program Memory Table Pointer Upper Byte (TBLPTR<20:16>) |                     |        |       |       |        |        |                        | 55                          |

| TBPLTRH | RH Program Memory Table Pointer High Byte (TBLPTR<15:8>)                     |                     |        |       |       |        |        |                        | 55                          |

| TBLPTRL | Program Memory Table Pointer High Byte (TBLPTR<7:0>)                         |                     |        |       |       |        | 55     |                        |                             |

| TABLAT  | Program Memory Table Latch                                                   |                     |        |       |       |        |        | 55                     |                             |

| INTCON  | <b>GIE/GIEH</b>                                                              | PEIE/GIEL           | TMR0IE | INTE  | RBIE  | TMR0IF | INTF   | RBIF                   | 55                          |

| EECON2  | EEPROM Control Register 2 (not a physical register)                          |                     |        |       |       |        |        | 57                     |                             |

| EECON1  | EEPGD                                                                        | CFGS                | _      | FREE  | WRERR | WREN   | WR     | RD                     | 57                          |

| IPR2    | OSCFIP                                                                       | CMIP <sup>(2)</sup> | _      | EEIP  | BCLIP | HLVDIP | TMR3IP | ECCP1IP <sup>(1)</sup> | 57                          |

| PIR2    | OSCFIF                                                                       | CMIF <sup>(2)</sup> | _      | EEIF  | BCLIF | HLVDIF | TMR3IF | ECCP1IF <sup>(1)</sup> | 58                          |

| PIE2    | OSCFIE                                                                       | CMIE <sup>(2)</sup> | _      | EEIE  | BCLIE | HLVDIE | TMR3IE | ECCP1IE <sup>(1)</sup> | 58                          |

TABLE 7-2:

REGISTERS ASSOCIATED WITH PROGRAM FLASH MEMORY

Legend: — = unimplemented, read as '0'. Shaded cells are not used during Flash/EEPROM access.

**Note 1:** These bits are available in PIC18F4X80 devices only.

- 2: These bits are available in PIC18F4X80 devices and reserved in PIC18F2X80 devices.

- **3:** This bit is available only in Test mode and Serial Programming mode.

#### 11.3 PORTC, TRISC and LATC Registers

PORTC is an 8-bit wide, bidirectional port. The corresponding Data Direction register is TRISC. Setting a TRISC bit (= 1) will make the corresponding PORTC pin an input (i.e., put the corresponding output driver in a high-impedance mode). Clearing a TRISC bit (= 0) will make the corresponding PORTC pin an output (i.e., put the contents of the output latch on the selected pin).

The Output Latch register (LATC) is also memory mapped. Read-modify-write operations on the LATC register read and write the latched output value for PORTC.

PORTC is multiplexed with several peripheral functions (Table 11-5). The pins have Schmitt Trigger input buffers.

When enabling peripheral functions, care should be taken in defining TRIS bits for each PORTC pin. Some peripherals override the TRIS bit to make a pin an output, while other peripherals override the TRIS bit to make a pin an input. The user should refer to the corresponding peripheral section for the correct TRIS bit settings.

### Note: On a Power-on Reset, these pins are configured as digital inputs.

The contents of the TRISC register are affected by peripheral overrides. Reading TRISC always returns the current contents, even though a peripheral device may be overriding one or more of the pins.

#### EXAMPLE 11-3: INITIALIZING PORTC

| CLRF  | PORTC | ; Initialize PORTC by ; clearing output |

|-------|-------|-----------------------------------------|

|       |       | ; data latches                          |

| CLRF  | LATC  | ; Alternate method                      |

|       |       | ; to clear output                       |

|       |       | ; data latches                          |

| MOVLW | OCFh  | ; Value used to                         |

|       |       | ; initialize data                       |

|       |       | ; direction                             |

| MOVWF | TRISC | ,                                       |

|       |       | ; RC<5:4> as outputs                    |

|       |       | ; RC<7:6> as inputs                     |

|       |       |                                         |

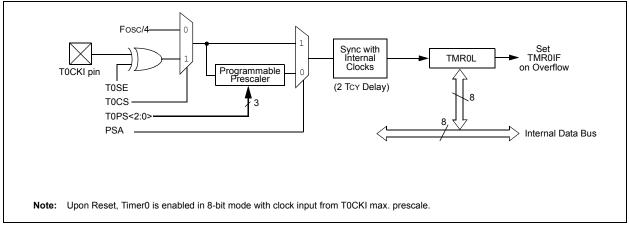

#### 12.1 Timer0 Operation

Timer0 can operate as either a timer or a counter; the mode is selected by clearing the T0CS bit (T0CON<5>). In Timer mode, the module increments on every clock by default unless a different prescaler value is selected (see **Section 12.3 "Prescaler"**). If the TMR0 register is written to, the increment is inhibited for the following two instruction cycles. The user can work around this by writing an adjusted value to the TMR0 register.

The Counter mode is selected by setting the T0CS bit (= 1). In Counter mode, Timer0 increments either on every rising or falling edge of pin, RA4/T0CKI. The incrementing edge is determined by the Timer0 Source Edge Select bit, T0SE (T0CON<4>); clearing this bit selects the rising edge. Restrictions on the external clock input are discussed below.

An external clock source can be used to drive Timer0; however, it must meet certain requirements to ensure that the external clock can be synchronized with the internal phase clock (Tosc). There is a delay between synchronization and the onset of incrementing the timer/counter.

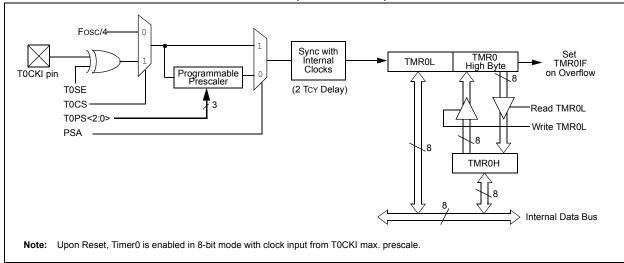

#### 12.2 Timer0 Reads and Writes in 16-Bit Mode

TMR0H is not the actual high byte of Timer0 in 16-bit mode; it is actually a buffered version of the real high byte of Timer0, which is not directly readable nor writable (refer to Figure 12-2). TMR0H is updated with the contents of the high byte of Timer0 during a read of TMR0L. This provides the ability to read all 16 bits of Timer0 without having to verify that the read of the high and low byte were valid, due to a rollover between successive reads of the high and low byte.

Similarly, a write to the high byte of Timer0 must also take place through the TMR0H Buffer register. The high byte is updated with the contents of TMR0H when a write occurs to TMR0L. This allows all 16 bits of Timer0 to be updated at once.

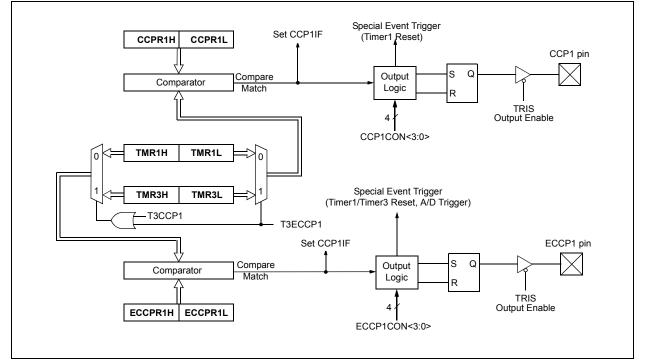

#### 16.3 Compare Mode

In Compare mode, the 16-bit CCPR1 register value is constantly compared against either the TMR1 or TMR3 register pair value. When a match occurs, the CCP1 pin can be:

- driven high

- · driven low

- toggled (high-to-low or low-to-high)

- remain unchanged (that is, reflects the state of the I/O latch)

The action on the pin is based on the value of the mode select bits (ECCP1M<3:0>). At the same time, the interrupt flag bit, ECCP1IF, is set.

#### 16.3.1 CCP PIN CONFIGURATION

The user must configure the CCP1 pin as an output by clearing the appropriate TRIS bit.

| Note: | Clearing the CCP1CON register will force    |

|-------|---------------------------------------------|

|       | the RC2 compare output latch (depending     |

|       | on device configuration) to the default low |

|       | level. This is not the PORTC I/O data       |

|       | latch.                                      |

#### 16.3.2 TIMER1/TIMER3 MODE SELECTION

Timer1 and/or Timer3 must be running in Timer mode or Synchronized Counter mode if the CCP module is using the compare feature. In Asynchronous Counter mode, the compare operation may not work.

#### 16.3.3 SOFTWARE INTERRUPT MODE

When the Generate Software Interrupt mode is chosen (CCP1M<3:0> = 1010), the CCP1 pin is not affected. Only a CCP interrupt is generated, if enabled, and the CCP1IE bit is set.

#### 16.3.4 SPECIAL EVENT TRIGGER

Both CCP modules are equipped with a Special Event Trigger. This is an internal hardware signal generated in Compare mode to trigger actions by other modules. The Special Event Trigger is enabled by selecting the Compare Special Event Trigger mode (CCP1M<3:0> = 1011).

For either CCP module, the Special Event Trigger resets the Timer register pair for whichever timer resource is currently assigned as the module's time base. This allows the CCPR1 registers to serve as a programmable period register for either timer.

#### FIGURE 16-2: COMPARE MODE OPERATION BLOCK DIAGRAM

#### 19.1 Baud Rate Generator (BRG)

The BRG is a dedicated, 8-bit or 16-bit generator that supports both the Asynchronous and Synchronous modes of the EUSART. By default, the BRG operates in 8-bit mode; setting the BRG16 bit (BAUDCON<3>) selects 16-bit mode.

The SPBRGH:SPBRG register pair controls the period of a free running timer. In Asynchronous mode, bits BRGH (TXSTA<2>) and BRG16 (BAUDCON<3>) also control the baud rate. In Synchronous mode, BRGH is ignored. Table 19-1 shows the formula for computation of the baud rate for different EUSART modes which only apply in Master mode (internally generated clock).

Given the desired baud rate and Fosc, the nearest integer value for the SPBRGH:SPBRG registers can be calculated using the formulas in Table 19-1. From this, the error in baud rate can be determined. An example calculation is shown in Example 19-1. Typical baud rates and error values for the various Asynchronous modes are shown in Table 19-2. It may be advantageous to use the high baud rate (BRGH = 1) or the 16-bit BRG to reduce the baud rate error, or achieve a slow baud rate for a fast oscillator frequency.

Writing a new value to the SPBRGH:SPBRG registers causes the BRG timer to be reset (or cleared). This ensures the BRG does not wait for a timer overflow before outputting the new baud rate.

| <b>Note:</b> BRG value of '0' is not supported. |

|-------------------------------------------------|

|                                                 |

#### 19.1.1 OPERATION IN POWER-MANAGED MODES

The device clock is used to generate the desired baud rate. When one of the power-managed modes is entered, the new clock source may be operating at a different frequency. This may require an adjustment to the value in the SPBRG register pair.

#### 19.1.2 SAMPLING

The data on the RX pin is sampled three times by a majority detect circuit to determine if a high or a low level is present at the RX pin when SYNC is clear or when BRG16 and BRGH are both not set. The data on the RX pin is sampled once when SYNC is set or when BRGH16 and BRGH are both set.

| TABLE 13-1. DAGD RATE FORMIGEAS | TABLE 19-1: | BAUD RATE FORMULAS |

|---------------------------------|-------------|--------------------|

|---------------------------------|-------------|--------------------|

| Configuration Bits |       | its  |                     | Doud Data Formula        |  |

|--------------------|-------|------|---------------------|--------------------------|--|

| SYNC               | BRG16 | BRGH | BRG/EUSART Mode     | Baud Rate Formula        |  |

| 0                  | 0     | 0    | 8-bit/Asynchronous  | Fosc/[64 (n + 1)]        |  |

| 0                  | 0     | 1    | 8-bit/Asynchronous  | $\Gamma_{000}/[16(n+1)]$ |  |

| 0                  | 1     | 0    | 16-bit/Asynchronous | Fosc/[16 (n + 1)]        |  |

| 0                  | 1     | 1    | 16-bit/Asynchronous |                          |  |

| 1                  | 0     | х    | 8-bit/Synchronous   | Fosc/[4 (n + 1)]         |  |

| 1                  | 1     | х    | 16-bit/Synchronous  |                          |  |

**Legend:** x = Don't care, n = value of SPBRGH:SPBRG register pair

NOTES:

## $\label{eq:register24-28: BnEIDH: TX/RX BUFFER n EXTENDED IDENTIFIER REGISTERS, \\ HIGH BYTE IN RECEIVE MODE [0 \le n \le 5, TXnEN (BSEL0<n>) = 0]^{(1)}$

| R-x     | R-x   | R-x   | R-x   | R-x   | R-x   | R-x  | R-x   |

|---------|-------|-------|-------|-------|-------|------|-------|

| EID15   | EID14 | EID13 | EID12 | EID11 | EID10 | EID9 | EID8  |

| bit 7   |       |       |       |       |       |      | bit 0 |

|         |       |       |       |       |       |      |       |

| Legend: |       |       |       |       |       |      |       |

| Legenu.           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

bit 7-0 EID<15:8>: Extended Identifier bits

Note 1: These registers are available in Mode 1 and 2 only.

### $\label{eq:register24-29: BnEIDH: TX/RX BUFFER n EXTENDED IDENTIFIER REGISTERS, \\ HIGH BYTE IN TRANSMIT MODE [0 \le n \le 5, TXnEN (BSEL0<n>) = 1]^{(1)}$

| R/W-x |

|-------|-------|-------|-------|-------|-------|-------|-------|

| EID15 | EID14 | EID13 | EID12 | EID11 | EID10 | EID9  | EID8  |

| bit 7 |       |       |       |       |       |       | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | l as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 7-0 **EID<15:8>:** Extended Identifier bits

Note 1: These registers are available in Mode 1 and 2 only.

### $\label{eq:register24-30:BnEIDL: TX/RX BUFFER n EXTENDED IDENTIFIER REGISTERS, \\ LOW BYTE IN RECEIVE MODE [0 \le n \le 5, TXnEN (BSEL<n>) = 0]^{(1)}$

| R-x                                                                        | R-x  | R-x  | R-x  | R-x  | R-x  | R-x  | R-x   |

|----------------------------------------------------------------------------|------|------|------|------|------|------|-------|

| EID7                                                                       | EID6 | EID5 | EID4 | EID3 | EID2 | EID1 | EID0  |

| bit 7                                                                      |      |      |      |      |      |      | bit 0 |

|                                                                            |      |      |      |      |      |      |       |

| Legend:                                                                    |      |      |      |      |      |      |       |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'       |      |      |      |      |      |      |       |

| -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown |      |      |      |      | nown |      |       |

bit 7-0 EID<7:0>: Extended Identifier bits

Note 1: These registers are available in Mode 1 and 2 only.

| ANDWF                                          | AND W wi                                                                           | ith f                                                            |                                                        |                                               |

|------------------------------------------------|------------------------------------------------------------------------------------|------------------------------------------------------------------|--------------------------------------------------------|-----------------------------------------------|

| Syntax:                                        | ANDWF                                                                              | f {,d {,a}                                                       | }                                                      |                                               |

| Operands:                                      | $\begin{array}{l} 0 \leq f \leq 255 \\ d  \in  [0,1] \\ a  \in  [0,1] \end{array}$ |                                                                  |                                                        |                                               |

| Operation:                                     | (W) .AND. (                                                                        | (f) $\rightarrow$ des                                            | t                                                      |                                               |

| Status Affected:                               | N, Z                                                                               |                                                                  |                                                        |                                               |

| Encoding:                                      | 0001                                                                               | 01da                                                             | fff                                                    | f ffff                                        |

| Description:                                   |                                                                                    | f 'd' is '0'<br>5 '1', the r                                     | the re                                                 | D'ed with<br>esult is stored<br>s stored back |

|                                                | ,                                                                                  |                                                                  |                                                        | k is selected.<br>I to select the             |

|                                                | set is enable<br>in Indexed I<br>mode when<br>Section 26.                          | ed, this in<br>_iteral Of<br>ever f ≤ 9<br>.2.3 "Byt<br>d Instru | nstruc<br>fset A<br>95 (5F<br><b>e-Ori</b> c<br>ctions | h). See<br>ented and<br>s in Indexed          |

| Words:                                         | 1                                                                                  |                                                                  |                                                        |                                               |

| Cycles:                                        | 1                                                                                  |                                                                  |                                                        |                                               |

| Q Cycle Activity:                              |                                                                                    |                                                                  |                                                        |                                               |

| Q1                                             | Q2                                                                                 | Q3                                                               |                                                        | Q4                                            |

| Decode                                         | Read<br>register 'f'                                                               | Proce<br>Data                                                    |                                                        | Write to destination                          |

| Example:                                       | ANDWF                                                                              | REG,                                                             | ), 0                                                   |                                               |

| Before Instruc<br>W<br>REG<br>After Instructic | = 17h<br>= C2h                                                                     |                                                                  |                                                        |                                               |

| W<br>REG                                       | = 02h<br>= C2h                                                                     |                                                                  |                                                        |                                               |

| вс                                                                                                                                                                                                                         | BC Branch if Carry    |                           |                                                        |          |               |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|---------------------------|--------------------------------------------------------|----------|---------------|--|--|--|--|

| Synta                                                                                                                                                                                                                      | ax:                   | BC n                      | BC n                                                   |          |               |  |  |  |  |

| Oper                                                                                                                                                                                                                       | ands:                 | -128 ≤ n ≤ 1              | $-128 \le n \le 127$                                   |          |               |  |  |  |  |

| Oper                                                                                                                                                                                                                       | ation:                |                           | if Carry bit is '1',<br>(PC) + 2 + 2n $\rightarrow$ PC |          |               |  |  |  |  |

| Statu                                                                                                                                                                                                                      | s Affected:           | None                      |                                                        |          |               |  |  |  |  |

| Enco                                                                                                                                                                                                                       | ding:                 | 1110                      | 0010                                                   | nnnn     | nnnn          |  |  |  |  |

| Desc                                                                                                                                                                                                                       | ription:              | If the Carry will branch. | bit is '1',                                            | then the | program       |  |  |  |  |

| The 2's complement number '2n' is<br>added to the PC. Since the PC will have<br>incremented to fetch the next<br>instruction, the new address will be<br>PC + 2 + 2n. This instruction is then a<br>two-cycle instruction. |                       |                           |                                                        |          |               |  |  |  |  |

| Word                                                                                                                                                                                                                       | ls:                   | 1                         |                                                        |          |               |  |  |  |  |

| Cycle                                                                                                                                                                                                                      | es:                   | 1(2)                      | 1(2)                                                   |          |               |  |  |  |  |

| Q C<br>If Ju                                                                                                                                                                                                               | ycle Activity:<br>mp: |                           |                                                        |          |               |  |  |  |  |

|                                                                                                                                                                                                                            | Q1                    | Q2                        | Q3                                                     |          | Q4            |  |  |  |  |

|                                                                                                                                                                                                                            | Decode                | Read literal<br>'n'       | Proces<br>Data                                         | s Wr     | te to PC      |  |  |  |  |

|                                                                                                                                                                                                                            | No                    | No                        | No                                                     |          | No            |  |  |  |  |

|                                                                                                                                                                                                                            | operation             | operation                 | operation                                              | on op    | eration       |  |  |  |  |

| lf No                                                                                                                                                                                                                      | o Jump:               |                           |                                                        |          |               |  |  |  |  |

|                                                                                                                                                                                                                            | Q1                    | Q2                        | Q3                                                     |          | Q4            |  |  |  |  |

|                                                                                                                                                                                                                            | Decode                | Read literal<br>'n'       | Proces<br>Data                                         | -        | No<br>eration |  |  |  |  |

|                                                                                                                                                                                                                            |                       |                           | Dala                                                   | l of     |               |  |  |  |  |

| Example: HERE BC 5                                                                                                                                                                                                         |                       |                           |                                                        |          |               |  |  |  |  |

| Before Instruction                                                                                                                                                                                                         |                       |                           |                                                        |          |               |  |  |  |  |

|                                                                                                                                                                                                                            | PC = address (HERE)   |                           |                                                        |          |               |  |  |  |  |

|                                                                                                                                                                                                                            | After Instruction     |                           |                                                        |          |               |  |  |  |  |

| = | address          | (HERE)                    |                                 |                   |

|---|------------------|---------------------------|---------------------------------|-------------------|

|   |                  |                           |                                 |                   |

| = | 1;               |                           |                                 |                   |

| = |                  | (HERE                     | +                               | 12)               |

| = | -,               |                           |                                 |                   |

| = | address          | (HERE                     | +                               | 2)                |

|   | =<br>=<br>=<br>= | = 1;<br>= address<br>= 0; | = 1;<br>= address (HERE<br>= 0; | = address (HERE + |

| DEC         | FSZ                                      | Decrement f, Skip if 0                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                         |  |  |  |  |

|-------------|------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|--|--|--|--|

| Synta       | ax:                                      | DECFSZ f                                                                                                                                                                                                                                                         | {,d {,a}}                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                         |  |  |  |  |

| Oper        | ands:                                    | $\begin{array}{l} 0 \leq f \leq 255 \\ d  \in  [0,1] \\ a  \in  [0,1] \end{array}$                                                                                                                                                                               | d ∈ [0,1]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                         |  |  |  |  |

| Oper        | ation:                                   | (f) – 1 $\rightarrow$ de skip if result                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                         |  |  |  |  |

| Statu       | s Affected:                              | None                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                         |  |  |  |  |

| Enco        | oding:                                   | 0010                                                                                                                                                                                                                                                             | 11da fff                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | f ffff                  |  |  |  |  |

| Desc        | ription:                                 | decremente<br>placed in W<br>placed back<br>If the result<br>which is alra<br>and a NOP i<br>it a two-cyci<br>If 'a' is '0', th<br>If 'a' is '0', th<br>GPR bank.<br>If 'a' is '0' an<br>set is enable<br>in Indexed I<br>mode when<br>Section 26<br>Bit-Oriente | The contents of register 'f' are<br>decremented. If 'd' is '0', the result is<br>placed in W. If 'd' is '1', the result is<br>placed back in register 'f'.<br>If the result is '0', the next instruction<br>which is already fetched is discarded<br>and a NOP is executed instead, making<br>it a two-cycle instruction.<br>If 'a' is '0', the Access Bank is selected.<br>If 'a' is '0', the Access Bank is selected.<br>If 'a' is '1', the BSR is used to select the<br>GPR bank.<br>If 'a' is '0' and the extended instruction<br>set is enabled, this instruction operates<br>in Indexed Literal Offset Addressing<br>mode whenever f $\leq$ 95 (5Fh). See<br>Section 26.2.3 "Byte-Oriented and<br>Bit-Oriented Instructions in Indexed<br>Literal Offset Mode" for details. |                         |  |  |  |  |

| Word        | ls:                                      | 1                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                         |  |  |  |  |

| Cycle       | es:                                      |                                                                                                                                                                                                                                                                  | ycles if skip a<br>a 2-word instr                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                         |  |  |  |  |

| QC          | ycle Activity:                           |                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                         |  |  |  |  |

|             | Q1                                       | Q2                                                                                                                                                                                                                                                               | Q3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Q4                      |  |  |  |  |

|             | Decode                                   | Read<br>register 'f'                                                                                                                                                                                                                                             | Process<br>Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Write to<br>destination |  |  |  |  |

| lf sk       | ip:                                      | register i                                                                                                                                                                                                                                                       | Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | destination             |  |  |  |  |

|             | Q1                                       | Q2                                                                                                                                                                                                                                                               | Q3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Q4                      |  |  |  |  |

|             | No                                       | No                                                                                                                                                                                                                                                               | No                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | No                      |  |  |  |  |

| lf als      | operation                                | operation                                                                                                                                                                                                                                                        | operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | operation               |  |  |  |  |

| II SK       | up and tollowe<br>Q1                     | d by 2-word in:<br>Q2                                                                                                                                                                                                                                            | Q3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Q4                      |  |  |  |  |

|             | No                                       | No                                                                                                                                                                                                                                                               | No                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | No                      |  |  |  |  |