Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 25MHz                                                                     |

| Connectivity               | CANbus, I <sup>2</sup> C, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                               |

| Number of I/O              | 36                                                                        |

| Program Memory Size        | 16KB (8K x 16)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 768 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                               |

| Data Converters            | A/D 11x10b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 44-VQFN Exposed Pad                                                       |

| Supplier Device Package    | 44-QFN (8x8)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f4480-e-ml |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 6.1.2.2 Return Stack Pointer (STKPTR)

The STKPTR register (Register 6-1) contains the Stack Pointer value, the STKFUL (Stack Full) status bit and the STKUNF (Stack Underflow) status bits. The value of the Stack Pointer can be 0 through 31. The Stack Pointer increments before values are pushed onto the stack and decrements after values are popped off the stack. On Reset, the Stack Pointer value will be zero. The user may read and write the Stack Pointer value. This feature can be used by a Real-Time Operating System for return stack maintenance.

After the PC is pushed onto the stack 31 times (without popping any values off the stack), the STKFUL bit is set. The STKFUL bit is cleared by software or by a POR.

The action that takes place when the stack becomes full depends on the state of the STVREN (Stack Overflow Reset Enable) Configuration bit. (Refer to **Section 25.1 "Configuration Bits**" for a description of the device Configuration bits.) If STVREN is set (default), the 31st push will push the (PC + 2) value onto the stack, set the STKFUL bit and reset the device. The STKFUL bit will remain set and the Stack Pointer will be set to zero.

If STVREN is cleared, the STKFUL bit will be set on the 31st push and the Stack Pointer will increment to 31. Any additional pushes will not overwrite the 31st push and STKPTR will remain at 31.

When the stack has been popped enough times to unload the stack, the next pop will return a value of zero to the PC and sets the STKUNF bit, while the Stack Pointer remains at zero. The STKUNF bit will remain set until cleared by software or until a POR occurs.

| Note: | Returning a value of zero to the PC on an |  |  |  |  |  |  |  |  |

|-------|-------------------------------------------|--|--|--|--|--|--|--|--|

|       | underflow has the effect of vectoring the |  |  |  |  |  |  |  |  |

|       | program to the Reset vector, where the    |  |  |  |  |  |  |  |  |

|       | stack conditions can be verified and      |  |  |  |  |  |  |  |  |

|       | appropriate actions can be taken. This is |  |  |  |  |  |  |  |  |

|       | not the same as a Reset, as the contents  |  |  |  |  |  |  |  |  |

|       | of the SFRs are not affected.             |  |  |  |  |  |  |  |  |

### 6.1.2.3 PUSH and POP Instructions

Since the Top-of-Stack is readable and writable, the ability to push values onto the stack and pull values off the stack without disturbing normal program execution is a desirable feature. The PIC18 instruction set includes two instructions, PUSH and POP, that permit the TOS to be manipulated under software control. TOSU, TOSH and TOSL can be modified to place data or a return address on the stack.

The PUSH instruction places the current PC value onto the stack. This increments the Stack Pointer and loads the current PC value onto the stack.

The POP instruction discards the current TOS by decrementing the Stack Pointer. The previous value pushed onto the stack then becomes the TOS value.

## REGISTER 6-1: STKPTR: STACK POINTER REGISTER

| REGISTER 6                                                                                                                                                                                                                                  | -1: SIKPI             | R: STACK P                                                    | OINTER RE | GISTER           |                  |                 |       |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|---------------------------------------------------------------|-----------|------------------|------------------|-----------------|-------|

| R/C-0                                                                                                                                                                                                                                       | R/C-0                 | U-0                                                           | R/W-0     | R/W-0            | R/W-0            | R/W-0           | R/W-0 |

| STKFUL <sup>(1)</sup>                                                                                                                                                                                                                       | STKUNF <sup>(1)</sup> | —                                                             | SP4       | SP3              | SP2              | SP1             | SP0   |

| bit 7                                                                                                                                                                                                                                       |                       |                                                               |           |                  |                  |                 | bit 0 |

|                                                                                                                                                                                                                                             |                       |                                                               |           |                  |                  |                 |       |

| Legend:                                                                                                                                                                                                                                     |                       | C = Clearable                                                 | bit       |                  |                  |                 |       |

| R = Readable                                                                                                                                                                                                                                | bit                   | W = Writable I                                                | bit       | U = Unimpler     | nented bit, read | as '0'          |       |

| -n = Value at P                                                                                                                                                                                                                             | OR                    | '1' = Bit is set                                              |           | '0' = Bit is cle | ared             | x = Bit is unkr | nown  |

| bit 7 <b>STKFUL:</b> Stack Full Flag bit <sup>(1)</sup><br>1 = Stack became full or overflowed<br>0 = Stack has not become full or overflow<br>bit 6 <b>STKUNF:</b> Stack Underflow Flag bit <sup>(1)</sup><br>1 = Stack underflow occurred |                       |                                                               |           | ed               |                  |                 |       |

| bit 5<br>bit 4-0                                                                                                                                                                                                                            | Unimplemen            | erflow did not o<br><b>ted:</b> Read as '(<br>ck Pointer Loca | )'        |                  |                  |                 |       |

**Note 1:** Bit 7 and bit 6 are cleared by user software or by a POR.

| Address | Name                     | Address | Name               | Address | Name              | Address | Name |

|---------|--------------------------|---------|--------------------|---------|-------------------|---------|------|

| EFFh    |                          | EDFh    |                    | EBFh    |                   | E9Fh    |      |

| EFEh    | _                        | EDEh    | _                  | EBEh    | _                 | E9Eh    | _    |

| EFDh    | _                        | EDDh    | _                  | EBDh    | _                 | E9Dh    | _    |

| EFCh    | _                        | EDCh    | _                  | EBCh    | _                 | E9Ch    | _    |

| EFBh    | _                        | EDBh    | _                  | EBBh    | _                 | E9Bh    | _    |

| EFAh    | _                        | EDAh    | _                  | EBAh    | _                 | E9Ah    | _    |

| EF9h    | _                        | ED9h    | _                  | EB9h    | _                 | E99h    | _    |

| EF8h    | _                        | ED8h    | _                  | EB8h    | _                 | E98h    | _    |

| EF7h    | —                        | ED7h    | _                  | EB7h    | _                 | E97h    | _    |

| EF6h    | _                        | ED6h    | _                  | EB6h    | _                 | E96h    | _    |

| EF5h    | _                        | ED5h    | _                  | EB5h    | _                 | E95h    | _    |

| EF4h    | _                        | ED4h    | _                  | EB4h    | _                 | E94h    | _    |

| EF3h    | _                        | ED3h    | _                  | EB3h    | _                 | E93h    | _    |

| EF2h    | _                        | ED2h    | _                  | EB2h    | _                 | E92h    | _    |

| EF1h    | —                        | ED1h    | _                  | EB1h    | _                 | E91h    | _    |

| EF0h    | —                        | ED0h    | _                  | EB0h    | _                 | E90h    | _    |

| EEFh    | _                        | ECFh    | _                  | EAFh    | _                 | E8Fh    | _    |

| EEEh    | —                        | ECEh    | _                  | EAEh    | _                 | E8Eh    | _    |

| EEDh    | —                        | ECDh    | _                  | EADh    | _                 | E8Dh    | _    |

| EECh    | _                        | ECCh    | _                  | EACh    | _                 | E8Ch    | _    |

| EEBh    | —                        | ECBh    | _                  | EABh    | _                 | E8Bh    | _    |

| EEAh    | _                        | ECAh    | _                  | EAAh    | _                 | E8Ah    | _    |

| EE9h    | _                        | EC9h    | _                  | EA9h    | _                 | E89h    | _    |

| EE8h    | —                        | EC8h    | _                  | EA8h    | _                 | E88h    | _    |

| EE7h    | —                        | EC7h    | _                  | EA7h    | _                 | E87h    | _    |

| EE6h    | _                        | EC6h    | _                  | EA6h    | _                 | E86h    | _    |

| EE5h    | _                        | EC5h    | _                  | EA5h    | _                 | E85h    | _    |

| EE4h    | _                        | EC4h    | _                  | EA4h    | _                 | E84h    | _    |

| EE3h    |                          | EC3h    | —                  | EA3h    |                   | E83h    |      |

| EE2h    |                          | EC2h    | _                  | EA2h    |                   | E82h    |      |

| EE1h    | _                        | EC1h    | —                  | EA1h    | _                 | E81h    | _    |

| EE0h    |                          | EC0h    | _                  | EA0h    | _                 | E80h    |      |

|         | Pagiatora available only |         | V90 dovices: other |         | ators road as 'o' |         |      |

# TABLE 6-1:SPECIAL FUNCTION REGISTER MAP FOR<br/>PIC18F2480/2580/4480/4580 DEVICES (CONTINUED)

Note 1: Registers available only on PIC18F4X80 devices; otherwise, the registers read as '0'.

2: When any TX\_ENn bit in RX\_TX\_SELn is set, then the corresponding bit in this register has transmit properties.

3: This is not a physical register.

## 7.2.2 TABLAT – TABLE LATCH REGISTER

The Table Latch (TABLAT) is an 8-bit register mapped into the SFR space. The Table Latch register is used to hold 8-bit data during data transfers between program memory and data RAM.

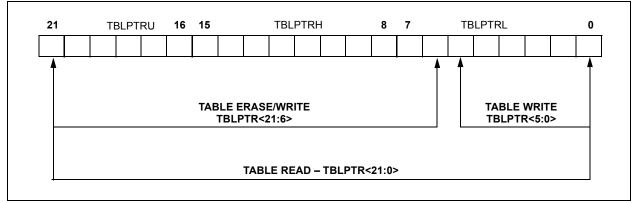

### 7.2.3 TBLPTR – TABLE POINTER REGISTER

The Table Pointer (TBLPTR) register addresses a byte within the program memory. The TBLPTR is comprised of three SFR registers: Table Pointer Upper Byte, Table Pointer High Byte and Table Pointer Low Byte (TBLPTRU:TBLPTRH:TBLPTRL). These three registers join to form a 22-bit wide pointer. The low-order 21 bits allow the device to address up to 2 Mbytes of program memory space. The 22nd bit allows access to the Device ID, the user ID and the Configuration bits.

The Table Pointer, TBLPTR, is used by the TBLRD and TBLWT instructions. These instructions can update the TBLPTR in one of four ways based on the table operation. These operations are shown in Table 7-1. These operations on the TBLPTR only affect the low-order 21 bits.

## 7.2.4 TABLE POINTER BOUNDARIES

TBLPTR is used in reads, writes and erases of the Flash program memory.

When a TBLRD is executed, all 22 bits of the TBLPTR determine which byte is read from program memory into TABLAT.

When a TBLWT is executed, the five LSbs of the Table Pointer register (TBLPTR<4:0>) determine which of the 32 program memory holding registers is written to. When the timed write to program memory begins (via the WR bit), the 16 MSbs of the TBLPTR (TBLPTR<21:6>) determine which program memory block of 32 bytes is written to. For more detail, see **Section 7.5 "Writing to Flash Program Memory"**.

When an erase of program memory is executed, the 16 MSbs of the Table Pointer register (TBLPTR<21:6>) point to the 64-byte block that will be erased. The Least Significant bits (TBLPTR<5:0>) are ignored.

Figure 7-3 describes the relevant boundaries of TBLPTR based on Flash program memory operations.

### TABLE 7-1: TABLE POINTER OPERATIONS WITH TBLRD AND TBLWT INSTRUCTIONS

| Example            | Operation on Table Pointer                  |

|--------------------|---------------------------------------------|

| TBLRD*<br>TBLWT*   | TBLPTR is not modified                      |

| TBLRD*+<br>TBLWT*+ | TBLPTR is incremented after the read/write  |

| TBLRD*-<br>TBLWT*- | TBLPTR is decremented after the read/write  |

| TBLRD+*<br>TBLWT+* | TBLPTR is incremented before the read/write |

#### FIGURE 7-3: TABLE POINTER BOUNDARIES BASED ON OPERATION

Example 9-3 shows the sequence to do a 16 x 16 unsigned multiplication. Equation 9-1 shows the algorithm that is used. The 32-bit result is stored in four registers (RES3:RES0).

#### EQUATION 9-1: 16 x 16 UNSIGNED MULTIPLICATION ALGORITHM

| RES3:RES0 | = | rittorin: ittore - rittozni. ittoze                                            |

|-----------|---|--------------------------------------------------------------------------------|

|           | = | $(ARG1H \bullet ARG2H \bullet 2^{16}) +$                                       |

|           |   |                                                                                |

|           |   | $(ARG1L \bullet ARG2H \bullet 2^8) +$                                          |

|           |   | $(ARG1L \bullet ARG2L)$                                                        |

|           | = | $(ARG1H \bullet ARG2L \bullet 2^8) +$<br>$(ARG1L \bullet ARG2H \bullet 2^8) +$ |

### EXAMPLE 9-3: 1

#### 16 x 16 UNSIGNED MULTIPLY ROUTINE

|   | MOVF   | ARG1L, W    |                   |

|---|--------|-------------|-------------------|

|   | MULWF  |             | ; ARG1L * ARG2L-> |

|   |        |             | ; PRODH:PRODL     |

|   | MOVFF  | PRODH, RES1 | ;                 |

|   | MOVFF  | PRODL, RESO | ;                 |

| ; |        |             |                   |

|   | MOVF   | ARG1H, W    |                   |

|   | MULWF  | ARG2H       | ; ARG1H * ARG2H-> |

|   |        |             | ; PRODH:PRODL     |

|   | MOVFF  | PRODH, RES3 | ;                 |

|   | MOVFF  | PRODL, RES2 | ;                 |

| ; |        |             |                   |

|   | MOVF   | ARG1L, W    |                   |

|   | MULWF  | ARG2H       | ; ARG1L * ARG2H-> |

|   |        |             | ; PRODH:PRODL     |

|   | MOVF   | PRODL, W    | ;                 |

|   | ADDWF  | RES1, F     | ; Add cross       |

|   | MOVF   | PRODH, W    | ; products        |

|   | ADDWFC | RES2, F     | ;                 |

|   | CLRF   | WREG        | ;                 |

|   | ADDWFC | RES3, F     | ;                 |

| ; |        |             |                   |

|   | MOVF   | ARG1H, W    | ;                 |

|   | MULWF  | ARG2L       | ; ARG1H * ARG2L-> |

|   |        |             | ; PRODH:PRODL     |

|   | MOVF   | PRODL, W    | ;                 |

|   | ADDWF  | RES1, F     | ; Add cross       |

|   | MOVF   | PRODH, W    | ; products        |

|   | ADDWFC | RES2, F     | ;                 |

|   | CLRF   | WREG        | ;                 |

|   | ADDWFC | RES3, F     | ;                 |

| L |        |             |                   |

Example 9-4 shows the sequence to do a 16 x 16 signed multiply. Equation 9-2 shows the algorithm used. The 32-bit result is stored in four registers (RES3:RES0). To account for the signed bits of the arguments, the MSb for each argument pair is tested and the appropriate subtractions are done.

#### EQUATION 9-2: 16 x 16 SIGNED MULTIPLICATION ALGORITHM

| RES3:RES0 = ARG1H:ARG1L • ARG2H:ARG2L                            |

|------------------------------------------------------------------|

| $= (ARG1H \bullet ARG2H \bullet 2^{16}) +$                       |

| $(ARG1H \bullet ARG2L \bullet 2^8) +$                            |

| $(ARG1L \bullet ARG2H \bullet 2^8) +$                            |

| $(ARG1L \bullet ARG2L) +$                                        |

| $(-1 \bullet ARG2H < 7 > \bullet ARG1H:ARG1L \bullet 2^{16}) +$  |

| $(-1 \bullet ARG1H < 7 \ge \bullet ARG2H: ARG2L \bullet 2^{16})$ |

|                                                                  |

#### EXAMPLE 9-4: 16 x 16 SIGNED MULTIPLY ROUTINE

|          |         | WOLI          |                    |

|----------|---------|---------------|--------------------|

|          | MOVF    | ARG1L, W      |                    |

|          | MULWF   | ARG2L         | ; ARG1L * ARG2L -> |

|          |         |               | ; PRODH:PRODL      |

|          | MOVFF   | PRODH, RES1   |                    |

|          |         | PRODL, RESO   |                    |

| ;        | 110 1 1 | 110001, 10000 | ,                  |

| <i>'</i> | MOVF    | ARG1H, W      |                    |

|          | MULWF   |               | ; ARG1H * ARG2H -> |

|          | MOLWE   | ARGZI         | ; PRODH:PRODL      |

|          | MOTIDD  |               |                    |

|          | MOVEE   | PRODH, RES3   | ;                  |

|          | MOVEE   | PRODL, RES2   | ;                  |

| ;        |         | 35017 11      |                    |

|          | MOVF    | ARG1L,W       |                    |

|          | MULWF   | ARG2H         | ; ARG1L * ARG2H -> |

|          |         |               | ; PRODH:PRODL      |

|          |         | PRODL, W      | ;                  |

|          | ADDWF   | RES1, F       | ; Add cross        |

|          |         |               | ; products         |

|          | ADDWFC  | RES2, F       | ;                  |

|          | CLRF    | WREG          | ;                  |

|          | ADDWFC  | RES3, F       | ;                  |

| ;        |         |               |                    |

|          | MOVF    | ARG1H, W      | ;                  |

|          | MULWF   | ARG2L         | ; ARG1H * ARG2L -> |

|          |         |               | ; PRODH:PRODL      |

|          | MOVF    | PRODL, W      | ;                  |

|          | ADDWF   | RES1, F       | ; Add cross        |

|          | MOVF    | PRODH, W      | ; products         |

|          |         | RES2, F       | ;                  |

|          | CLRF    |               | ;                  |

|          |         | RES3, F       | ;                  |

| ;        |         |               |                    |

| Ĺ        | BTESS   | ARG2H, 7      | ; ARG2H:ARG2L neg? |

|          | BRA     | SIGN ARG1     | ; no, check ARG1   |

|          | MOVE    | ARG1L, W      | ;                  |

|          | SUBWF   | RES2          | ;                  |

|          | MOVE    | ARG1H, W      | ;                  |

|          | SUBWFB  | -             | ,                  |

|          | SODWED  | INESS         |                    |

| ,<br>etc | N ARG1  |               |                    |

| 510      | _       | ARG1H, 7      | · APC14·APC11 pog2 |

|          |         | CONT_CODE     | ; ARG1H:ARG1L neg? |

|          | BRA     |               |                    |

|          | MOVE    | ARG2L, W      | ;                  |

|          | SUBWF   | RES2          | ;                  |

|          | MOVF    | ARG2H, W      | ;                  |

|          | SUBWFB  | KE23          |                    |

| ;        |         |               |                    |

| CON      | T_CODE  |               |                    |

|          | :       |               |                    |

## **10.0 INTERRUPTS**

The PIC18F2480/2580/4480/4580 devices have multiple interrupt sources and an interrupt priority feature that allows each interrupt source to be assigned a high-priority level or a low-priority level. The high-priority interrupt vector is at 000008h and the low-priority interrupt vector is at 000018h. High-priority interrupts will interrupt any low-priority interrupts that may be in progress.

There are ten registers which are used to control interrupt operation. These registers are:

- RCON

- INTCON

- INTCON2

- INTCON3

- PIR1, PIR2, PIR3

- PIE1, PIE2, PIE3

- IPR1, IPR2, IPR3

It is recommended that the Microchip header files supplied with MPLAB<sup>®</sup> IDE be used for the symbolic bit names in these registers. This allows the assembler/ compiler to automatically take care of the placement of these bits within the specified register.

Each interrupt source has three bits to control its operation. The functions of these bits are:

- Flag bit to indicate that an interrupt event occurred

- Enable bit that allows program execution to branch to the interrupt vector address when the flag bit is set

- Priority bit to select high priority or low priority

The interrupt priority feature is enabled by setting the IPEN bit (RCON<7>). When interrupt priority is enabled, there are two bits which enable interrupts globally. Setting the GIEH bit (INTCON<7>) enables all interrupts that have the priority bit set (high priority). Setting the GIEL bit (INTCON<6>) enables all interrupts that have the priority bit cleared (low priority). When the interrupt flag, enable bit and appropriate global interrupt enable bit are set, the interrupt will vector immediately to address 000008h or 000018h, depending on the priority bit setting. Individual interrupts can be disabled through their corresponding enable bits.

When the IPEN bit is cleared (default state), the interrupt priority feature is disabled and interrupts are compatible with PIC<sup>®</sup> mid-range devices. In Compatibility mode, the interrupt priority bits for each source have no effect. INTCON<6> is the PEIE bit, which enables/disables all peripheral interrupt sources. INT-CON<7> is the GIE bit, which enables/disables all interrupt sources. All interrupts branch to address 000008h in Compatibility mode.

When an interrupt is responded to, the global interrupt enable bit is cleared to disable further interrupts. If the IPEN bit is cleared, this is the GIE bit. If interrupt priority levels are used, this will be either the GIEH or GIEL bit. High-priority interrupt sources can interrupt a lowpriority interrupt. Low-priority interrupts are not processed while high-priority interrupts are in progress.

The return address is pushed onto the stack and the PC is loaded with the interrupt vector address (00008h or 000018h). Once in the Interrupt Service Routine, the source(s) of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bits must be cleared in software before re-enabling interrupts to avoid recursive interrupts.

The "return from interrupt" instruction, RETFIE, exits the interrupt routine and sets the GIE bit (GIEH or GIEL if priority levels are used), which re-enables interrupts.

For external interrupt events, such as the INTx pins or the PORTB input change interrupt, the interrupt latency will be three to four instruction cycles. The exact latency is the same for one or two-cycle instructions. Individual interrupt flag bits are set, regardless of the status of their corresponding enable bit or the GIE bit.

Note: Do not use the MOVFF instruction to modify any of the Interrupt Control registers while any interrupt is enabled. Doing so may cause erratic microcontroller behavior.

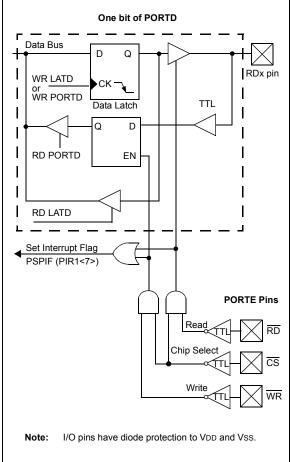

## 11.6 Parallel Slave Port

| Note: | The Parallel Slave Port is only available on |

|-------|----------------------------------------------|

|       | PIC18F4X80 devices.                          |

In addition to its function as a general I/O port, PORTD can also operate as an 8-bit wide Parallel Slave Port (PSP) or microprocessor port. PSP operation is controlled by the 4 upper bits of the TRISE register (Register 11-1). Setting control bit, PSPMODE (TRISE<4>), enables PSP operation, as long as the Enhanced CCP module is not operating in dual output or quad output PWM mode. In Slave mode, the port is asynchronously readable and writable by the external world.

The PSP can directly interface to an 8-bit microprocessor data bus. The external microprocessor can read or write the PORTD latch as an 8-bit latch. Setting the control bit PSPMODE enables the PORTE I/O pins to become control inputs for the microprocessor port. When set, port pin RE0 is the RD input, RE1 is the WR input and RE2 is the CS (Chip Select) input. For this functionality, the corresponding data direction bits of the TRISE register (TRISE<2:0>) must be configured as inputs (set). The A/D port Configuration bits, PFCG<3:0> (ADCON1<3:0>), must also be set to '1010'.

A write to the PSP occurs when both the  $\overline{CS}$  and  $\overline{WR}$  lines are first detected low and ends when either are detected high. The PSPIF and IBF flag bits are both set when the write ends.

A read from the PSP occurs when both the  $\overline{CS}$  and  $\overline{RD}$  lines are first detected low. The data in PORTD is read out and the OBF bit is set. If the user writes new data to PORTD to set OBF, the data is immediately read out; however, the OBF bit is not set.

When either the  $\overline{CS}$  or  $\overline{RD}$  lines are detected high, the PORTD pins return to the input state and the PSPIF bit is set. User applications should wait for PSPIF to be set before servicing the PSP; when this happens, the IBF and OBF bits can be polled and the appropriate action taken. The timing for the control signals in Write and Read modes is shown in Figure 11-3 and Figure 11-4, respectively.

## FIGURE 11-2: PORTD AND PORTE BLOCK DIAGRAM (PARALLEL SLAVE PORT)

## 12.3 Prescaler

An 8-bit counter is available as a prescaler for the Timer0 module. The prescaler is not directly readable or writable; its value is set by the PSA and T0PS<2:0> bits (T0CON<3:0>) which determine the prescaler assignment and prescale ratio.

Clearing the PSA bit assigns the prescaler to the Timer0 module. When it is assigned, prescale values from 1:2 through 1:256 in power-of-2 increments are selectable.

When assigned to the Timer0 module, all instructions writing to the TMR0 register (e.g., CLRF TMR0, MOVWF TMR0, BSF TMR0, etc.) clear the prescaler count.

Note: Writing to TMR0 when the prescaler is assigned to Timer0 will clear the prescaler count but will not change the prescaler assignment.

#### 12.3.1 SWITCHING PRESCALER ASSIGNMENT

The prescaler assignment is fully under software control and can be changed "on-the-fly" during program execution.

## 12.4 Timer0 Interrupt

The TMR0 interrupt is generated when the TMR0 register overflows from FFh to 00h in 8-bit mode, or from FFFFh to 0000h in 16-bit mode. This overflow sets the TMR0IF flag bit. The interrupt can be masked by clearing the TMR0IE bit (INTCON<5>). Before reenabling the interrupt, the TMR0IF bit must be cleared in software by the Interrupt Service Routine.

Since Timer0 is shut down in Sleep mode, the TMR0 interrupt cannot awaken the processor from Sleep.

TABLE 12-1:

REGISTERS ASSOCIATED WITH TIMER0

| Name   | Bit 7                     | Bit 6                 | Bit 5    | Bit 4        | Bit 3    | Bit 2  | Bit 1  | Bit 0 | Reset<br>Values<br>on Page: |

|--------|---------------------------|-----------------------|----------|--------------|----------|--------|--------|-------|-----------------------------|

| TMR0L  | Timer0 Register Low Byte  |                       |          |              |          |        |        |       | 56                          |

| TMR0H  | Timer0 Register High Byte |                       |          |              |          |        |        |       | 56                          |

| INTCON | GIE/GIEH                  | PEIE/GIEL             | TMR0IE   | INT0IE       | RBIE     | TMR0IF | INT0IF | RBIF  | 55                          |

| T0CON  | TMR00N                    | T08BIT                | TOCS     | T0SE         | PSA      | T0PS2  | T0PS1  | T0PS0 | 56                          |

| TRISA  | TRISA7 <sup>(1)</sup>     | TRISA6 <sup>(1)</sup> | PORTA Da | ta Direction | Register |        |        |       | 58                          |

Legend: — = unimplemented locations, read as '0'. Shaded cells are not used by Timer0.

**Note 1:** RA6/RA7 and their associated latch and direction bits are individually configured as port pins based on various primary oscillator modes. When disabled, these bits read as '0'.

NOTES:

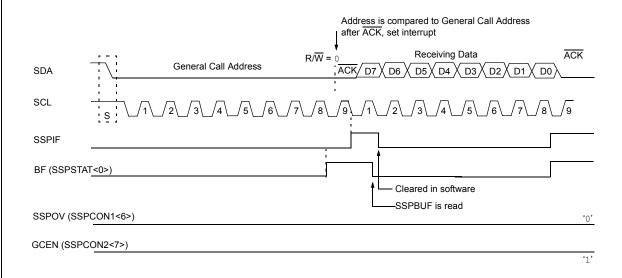

#### 18.4.5 GENERAL CALL ADDRESS SUPPORT

The addressing procedure for the I<sup>2</sup>C bus is such that the first byte after the Start condition usually determines which device will be the slave addressed by the master. The exception is the general call address which can address all devices. When this address is used, all devices should, in theory, respond with an Acknowledge.

The general call address is one of eight addresses reserved for specific purposes by the  $I^2C$  protocol. It consists of all '0's with R/W = 0.

The general call address is recognized when the General Call Enable bit (GCEN) is enabled (SSPCON2<7> set). Following a Start bit detect, 8 bits are shifted into the SSPSR and the address is compared against the SSPADD. It is also compared to the general call address and fixed in hardware.

If the general call address matches, the SSPSR is transferred to the SSPBUF, the BF flag bit is set (eighth bit), and on the falling edge of the ninth bit (ACK bit), the SSPIF interrupt flag bit is set.

When the interrupt is serviced, the source for the interrupt can be checked by reading the contents of the SSPBUF. The value can be used to determine if the address was device-specific or a general call address.

In 10-bit mode, the SSPADD is required to be updated for the second half of the address to match and the UA bit is set (SSPSTAT<1>). If the general call address is sampled when the GCEN bit is set, while the slave is configured in 10-Bit Addressing mode, then the second half of the address is not necessary, the UA bit will not be set and the slave will begin receiving data after the Acknowledge (Figure 18-15).

## 24.2 CAN Module Registers

Note: Not all CAN registers are available in the Access Bank.

There are many control and data registers associated with the CAN module. For convenience, their descriptions have been grouped into the following sections:

- · Control and Status Registers

- Dedicated Transmit Buffer Registers

- · Dedicated Receive Buffer Registers

- · Programmable TX/RX and Auto RTR Buffers

- Baud Rate Control Registers

- I/O Control Register

- · Interrupt Status and Control Registers

Detailed descriptions of each register and their usage are described in the following sections.

#### 24.2.1 CAN CONTROL AND STATUS REGISTERS

The registers described in this section control the overall operation of the CAN module and show its operational status.

### 24.2.4 CAN BAUD RATE REGISTERS

This section describes the CAN Baud Rate registers.

| Note: | These   | registers   | are   | writable | in |

|-------|---------|-------------|-------|----------|----|

|       | Configu | ration mode | only. |          |    |

## REGISTER 24-52: BRGCON1: BAUD RATE CONTROL REGISTER 1

| R/W-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| SJW1  | SJW0  | BRP5  | BRP4  | BRP3  | BRP2  | BRP1  | BRP0  |

| bit 7 |       |       |       |       |       |       | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 7-6 | SJW<1:0>: Synchronized Jump Width bits                |

|---------|-------------------------------------------------------|

|         | 11 = Synchronization jump width time = $4 \times T_Q$ |

|         | 10 = Synchronization jump width time = 3 x TQ         |

|         | 01 = Synchronization jump width time = 2 x TQ         |

|         | 00 = Synchronization jump width time = 1 x TQ         |

| bit 5-0 | BRP<5:0>: Baud Rate Prescaler bits                    |

|         | 111111 = Tq = (2 x 64)/Fosc                           |

|         | 111110 = TQ = (2 x 63)/Fosc                           |

|         | :                                                     |

|         | :                                                     |

|         | 000001 = Tq = (2 x 2)/Fosc                            |

|         | 000000 = Tq = (2 x 1)/Fosc                            |

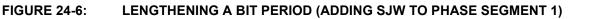

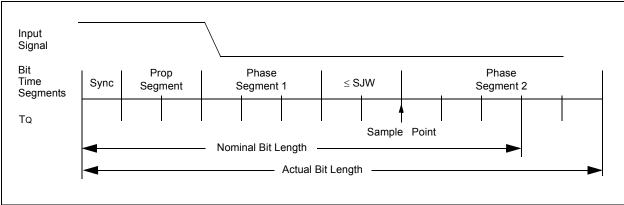

## 24.11 Programming Time Segments

Some requirements for programming of the time segments:

- Prop\_Seg + Phase\_Seg 1  $\geq$  Phase\_Seg 2

- Phase\_Seg  $2 \ge$  Sync Jump Width.

For example, assume that a 125 kHz CAN baud rate is desired, using 20 MHz for Fosc. With a Tosc of 50 ns, a baud rate prescaler value of 04h gives a TQ of 500 ns. To obtain a Nominal Bit Rate of 125 kHz, the Nominal Bit Time must be 8  $\mu$ s or 16 TQ.

Using 1 TQ for the Sync\_Seg, 2 TQ for the Prop\_Seg and 7 TQ for Phase Segment 1 would place the sample point at 10 TQ after the transition. This leaves 6 TQ for Phase Segment 2. By the rules above, the Sync Jump Width could be the maximum of 4 Tq. However, normally a large SJW is only necessary when the clock generation of the different nodes is inaccurate or unstable, such as using ceramic resonators. Typically, an SJW of 1 is enough.

## 24.12 Oscillator Tolerance

As a rule of thumb, the bit timing requirements allow ceramic resonators to be used in applications with transmission rates of up to 125 Kbit/sec. For the full bus speed range of the CAN protocol, a quartz oscillator is required. Refer to ISO11898-1 for oscillator tolerance requirements.

## REGISTER 25-6: CONFIG5L: CONFIGURATION REGISTER 5 LOW (BYTE ADDRESS 300008h)

| U-0   | U-0 | U-0 | U-0 | R/C-1              | R/C-1              | R/C-1 | R/C-1 |

|-------|-----|-----|-----|--------------------|--------------------|-------|-------|

| —     | —   |     | —   | CP3 <sup>(1)</sup> | CP2 <sup>(1)</sup> | CP1   | CP0   |

| bit 7 |     |     |     |                    |                    |       | bit 0 |

|       |     |     |     |                    |                    |       |       |

| Legend:                |                   |                                     |

|------------------------|-------------------|-------------------------------------|

| R = Readable bit       | C = Clearable bit | U = Unimplemented bit, read as '0'  |

| -n = Value when device | is unprogrammed   | u = Unchanged from programmed state |

|                        |                   |                                     |

| bit 7-4 | Unimplemented: Read as '0'                                                                                               |

|---------|--------------------------------------------------------------------------------------------------------------------------|

| bit 3   | CP3: Code Protection bit <sup>(1)</sup>                                                                                  |

|         | <ul> <li>1 = Block 3 (006000-007FFFh) not code-protected</li> <li>0 = Block 3 (006000-007FFFh) code-protected</li> </ul> |

| bit 2   | CP2: Code Protection bit <sup>(1)</sup>                                                                                  |

|         | <ul> <li>1 = Block 2 (004000-005FFFh) not code-protected</li> <li>0 = Block 2 (004000-005FFFh) code-protected</li> </ul> |

| bit 1   | CP1: Code Protection bit                                                                                                 |

|         | <ul> <li>1 = Block 1 (002000-003FFFh) not code-protected</li> <li>0 = Block 1 (002000-003FFFh) code-protected</li> </ul> |

| bit 0   | CP0: Code Protection bit                                                                                                 |

|         | 1 = Block 0 (000800-001FFFh) not code-protected<br>0 = Block 0 (000800-001FFFh) code-protected                           |

|         |                                                                                                                          |

#### Note 1: Unimplemented in PIC18FX480 devices; maintain this bit set.

### REGISTER 25-7: CONFIG5H: CONFIGURATION REGISTER 5 HIGH (BYTE ADDRESS 300009h)

| R/C-1 | R/C-1 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|-------|-------|-----|-----|-----|-----|-----|-------|

| CPD   | CPB   | —   | —   | —   | —   | —   | —     |

| bit 7 |       |     |     |     |     |     | bit 0 |

| Legend:                  |                   |                                     |

|--------------------------|-------------------|-------------------------------------|

| R = Readable bit         | C = Clearable bit | U = Unimplemented bit, read as '0'  |

| -n = Value when device i | s unprogrammed    | u = Unchanged from programmed state |

| bit 7   | CPD: Data EEPROM Code Protection bit               |

|---------|----------------------------------------------------|

|         | 1 = Data EEPROM not code-protected                 |

|         | 0 = Data EEPROM code-protected                     |

| bit 6   | CPB: Boot Block Code Protection bit                |

|         | 1 = Boot Block (000000-0007FFh) not code-protected |

|         | 0 = Boot Block (000000-0007FFh) code-protected     |

| bit 5-0 | Unimplemented: Read as '0'                         |

| Mnemo     | onic,  | Description                     | Cycles | 16-  | Bit Inst | ruction | Word | Status          | Notes |

|-----------|--------|---------------------------------|--------|------|----------|---------|------|-----------------|-------|

| Opera     | nds    | Description                     | Cycles | MSb  |          |         | LSb  | Affected        | Notes |

| LITERAL ( | OPERA  | TIONS                           |        |      |          |         |      |                 |       |

| ADDLW     | k      | Add Literal and WREG            | 1      | 0000 | 1111     | kkkk    | kkkk | C, DC, Z, OV, N |       |

| ANDLW     | k      | AND Literal with WREG           | 1      | 0000 | 1011     | kkkk    | kkkk | Z, N            |       |

| IORLW     | k      | Inclusive OR Literal with WREG  | 1      | 0000 | 1001     | kkkk    | kkkk | Z, N            |       |

| LFSR      | f, k   | Move literal (12-bit) 2nd word  | 2      | 1110 | 1110     | 00ff    | kkkk | None            |       |

|           |        | to FSR(f) 1st word              |        | 1111 | 0000     | kkkk    | kkkk |                 |       |

| MOVLB     | k      | Move Literal to BSR<3:0>        | 1      | 0000 | 0001     | 0000    | kkkk | None            |       |

| MOVLW     | k      | Move Literal to WREG            | 1      | 0000 | 1110     | kkkk    | kkkk | None            |       |

| MULLW     | k      | Multiply Literal with WREG      | 1      | 0000 | 1101     | kkkk    | kkkk | None            |       |

| RETLW     | k      | Return with Literal in WREG     | 2      | 0000 | 1100     | kkkk    | kkkk | None            |       |

| SUBLW     | k      | Subtract WREG from Literal      | 1      | 0000 | 1000     | kkkk    | kkkk | C, DC, Z, OV, N |       |

| XORLW     | k      | Exclusive OR Literal with WREG  | 1      | 0000 | 1010     | kkkk    | kkkk | Z, N            |       |

| DATA MEN  | MORY + |                                 | ONS    |      |          |         |      |                 |       |

| TBLRD*    |        | Table Read                      | 2      | 0000 | 0000     | 0000    | 1000 | None            |       |

| TBLRD*+   |        | Table Read with Post-Increment  |        | 0000 | 0000     | 0000    | 1001 | None            |       |

| TBLRD*-   |        | Table Read with Post-Decrement  |        | 0000 | 0000     | 0000    | 1010 | None            |       |

| TBLRD+*   |        | Table Read with Pre-Increment   |        | 0000 | 0000     | 0000    | 1011 | None            |       |

| TBLWT*    |        | Table Write                     | 2      | 0000 | 0000     | 0000    | 1100 | None            | 5     |

| TBLWT*+   |        | Table Write with Post-Increment |        | 0000 | 0000     | 0000    | 1101 | None            | 5     |

| TBLWT*-   |        | Table Write with Post-Decrement |        | 0000 | 0000     | 0000    | 1110 | None            | 5     |

| TBLWT+*   |        | Table Write with Pre-Increment  |        | 0000 | 0000     | 0000    | 1111 | None            | 5     |

## TABLE 26-2: PIC18FXXXX INSTRUCTION SET (CONTINUED)

**Note 1:** When a PORT register is modified as a function of itself (e.g., MOVF PORTB, 1, 0), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

2: If this instruction is executed on the TMR0 register (and where applicable, 'd' = 1), the prescaler will be cleared if assigned.

**3:** If the Program Counter (PC) is modified or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

4: Some instructions are two-word instructions. The second word of these instructions will be executed as a NOP unless the first word of the instruction retrieves the information embedded in these 16 bits. This ensures that all program memory locations have a valid instruction.

5: If the table write starts the write cycle to internal memory, the write will continue until terminated.

| РОР                               | Рор Тор                                                               | Pop Top of Return Stack                               |                                                                                |  |  |  |  |

|-----------------------------------|-----------------------------------------------------------------------|-------------------------------------------------------|--------------------------------------------------------------------------------|--|--|--|--|

| Syntax:                           | POP                                                                   |                                                       |                                                                                |  |  |  |  |

| Operands:                         | None                                                                  | None                                                  |                                                                                |  |  |  |  |

| Operation:                        | $(TOS) \rightarrow b$                                                 | $(TOS) \rightarrow bit bucket$                        |                                                                                |  |  |  |  |

| Status Affected:                  | None                                                                  | None                                                  |                                                                                |  |  |  |  |

| Encoding:                         | 0000                                                                  | 0000 00                                               | 00 0110                                                                        |  |  |  |  |

| Description:                      | stack and i<br>then becon<br>was pushe<br>This instrue<br>the user to | nes the previo<br>d onto the retu<br>ction is provide | the TOS value<br>us value that<br>urn stack.<br>ed to enable<br>age the return |  |  |  |  |

| Words:                            | 1                                                                     |                                                       |                                                                                |  |  |  |  |

| Cycles:                           | 1                                                                     |                                                       |                                                                                |  |  |  |  |

| Q Cycle Activity:                 |                                                                       |                                                       |                                                                                |  |  |  |  |

| Q1                                | Q2                                                                    | Q3                                                    | Q4                                                                             |  |  |  |  |

| Decode                            | No<br>operation                                                       | POP TOS<br>value                                      | No<br>operation                                                                |  |  |  |  |

| Example:                          | POP<br>GOTO                                                           | NEW                                                   |                                                                                |  |  |  |  |

| Before Instruc<br>TOS<br>Stack (1 | ction<br>level down)                                                  | = 0031/<br>= 01433                                    |                                                                                |  |  |  |  |

| After Instructi<br>TOS<br>PC      | on                                                                    | = 01433<br>= NEW                                      | 32h                                                                            |  |  |  |  |

| -                 | Push Top                                                                                  | of Ret                                        | urn S                                   | tacl                           | (                                   |

|-------------------|-------------------------------------------------------------------------------------------|-----------------------------------------------|-----------------------------------------|--------------------------------|-------------------------------------|

| Syntax:           | PUSH                                                                                      |                                               |                                         |                                |                                     |

| Operands:         | None                                                                                      |                                               |                                         |                                |                                     |

| Operation:        | (PC + 2) $\rightarrow$                                                                    | TOS                                           |                                         |                                |                                     |

| Status Affected:  | None                                                                                      |                                               |                                         |                                |                                     |

| Encoding:         | 0000                                                                                      | 0000                                          | 000                                     | 0                              | 0101                                |

| Description:      | The PC + 2<br>the return s<br>value is pus<br>This instruc<br>software sta<br>then pushin | tack. Th<br>shed dow<br>tion allo<br>ack by m | e prev<br>vn on t<br>ws imp<br>todifyir | ious<br>the s<br>blem<br>ng T( | TOS<br>stack.<br>enting a<br>OS and |

| Words:            | 1                                                                                         |                                               |                                         |                                |                                     |

| Cycles:           | 1                                                                                         |                                               |                                         |                                |                                     |

| Q Cycle Activity: |                                                                                           |                                               |                                         |                                |                                     |

| Q1                | Q2                                                                                        | Q                                             | 3                                       |                                | Q4                                  |

| Decode            | PUSH                                                                                      | No                                            |                                         |                                | No                                  |

| Decode            | PC + 2 onto<br>return stack                                                               | opera                                         | tion                                    | ор                             | eration                             |

| Example:          |                                                                                           | opera                                         | tion                                    | ор                             |                                     |

|                   | return stack                                                                              | = 3                                           | tion<br>345Ah<br>)124h                  | op                             |                                     |

### 26.2.3 BYTE-ORIENTED AND BIT-ORIENTED INSTRUCTIONS IN INDEXED LITERAL OFFSET MODE

| Note: | Enabling                                | the | PIC18     | instruction   | set  |

|-------|-----------------------------------------|-----|-----------|---------------|------|

|       | extension                               | may | cause leg | gacy applicat | ions |

|       | to behave erratically or fail entirely. |     |           |               |      |

In addition to eight new commands in the extended set, enabling the extended instruction set also enables Indexed Literal Offset Addressing mode (Section 6.6.1 "Indexed Addressing with Literal Offset"). This has a significant impact on the way that many commands of the standard PIC18 instruction set are interpreted.

When the extended set is disabled, addresses embedded in opcodes are treated as literal memory locations: either as a location in the Access Bank (a = 0), or in a GPR bank designated by the BSR (a = 1). When the extended instruction set is enabled and a = 0, however, a file register argument of 5Fh or less is interpreted as an offset from the pointer value in FSR2 and not as a literal address. For practical purposes, this means that all instructions that use the Access RAM bit as an argument – that is, all byte-oriented and bit-oriented instructions, or almost half of the core PIC18 instructions – may behave differently when the extended instruction set is enabled.

When the content of FSR2 is 00h, the boundaries of the Access RAM are essentially remapped to their original values. This may be useful in creating backward compatible code. If this technique is used, it may be necessary to save the value of FSR2 and restore it when moving back and forth between 'C' and assembly routines in order to preserve the Stack Pointer. Users must also keep in mind the syntax requirements of the extended instruction set (see Section 26.2.3.1 "Extended Instruction Syntax with Standard PIC18 Commands").

Although the Indexed Literal Offset Addressing mode can be very useful for dynamic stack and pointer manipulation, it can also be very annoying if a simple arithmetic operation is carried out on the wrong register. Users who are accustomed to the PIC18 programming must keep in mind that, when the extended instruction set is enabled, register addresses of 5Fh or less are used for Indexed Literal Offset Addressing.

Representative examples of typical byte-oriented and bit-oriented instructions in the Indexed Literal Offset Addressing mode are provided on the following page to show how execution is affected. The operand conditions shown in the examples are applicable to all instructions of these types.

# 26.2.3.1 Extended Instruction Syntax with Standard PIC18 Commands

When the extended instruction set is enabled, the file register argument, 'f', in the standard byte-oriented and bit-oriented commands is replaced with the literal offset value, 'k'. As already noted, this occurs only when 'f' is less than or equal to 5Fh. When an offset value is used, it must be indicated by square brackets ("[]"). As with the extended instructions, the use of brackets indicates to the compiler that the value is to be interpreted as an index or an offset. Omitting the brackets, or using a value greater than 5Fh within brackets, will generate an error in the MPASM<sup>™</sup> Assembler.

If the index argument is properly bracketed for Indexed Literal Offset Addressing, the Access RAM argument is never specified; it will automatically be assumed to be '0'. This is in contrast to standard operation (extended instruction set disabled) when 'a' is set on the basis of the target address. Declaring the Access RAM bit in this mode will also generate an error in the MPASM Assembler.

The destination argument, 'd', functions as before.

In the latest versions of the MPASM assembler, language support for the extended instruction set must be explicitly invoked. This is done with either the command line option,  $/_{y}$ , or the PE directive in the source listing.

## 26.2.4 CONSIDERATIONS WHEN ENABLING THE EXTENDED INSTRUCTION SET

It is important to note that the extensions to the instruction set may not be beneficial to all users. In particular, users who are not writing code that uses a software stack may not benefit from using the extensions to the instruction set.

Additionally, the Indexed Literal Offset Addressing mode may create issues with legacy applications written to the PIC18 assembler. This is because instructions in the legacy code may attempt to address registers in the Access Bank below 5Fh. Since these addresses are interpreted as literal offsets to FSR2 when the instruction set extension is enabled, the application may read or write to the wrong data addresses.

When porting an application to the PIC18F2480/2580/ 4480/4580, it is very important to consider the type of code. A large, re-entrant application that is written in 'C' and would benefit from efficient compilation will do well when using the instruction set extensions. Legacy applications that heavily use the Access Bank will most likely not benefit from using the extended instruction set.

## 28.0 ELECTRICAL CHARACTERISTICS

## Absolute Maximum Ratings (†)

| Ambient temperature under bias                               | 40°C to +125°C       |

|--------------------------------------------------------------|----------------------|

| Storage temperature                                          | 65°C to +150°C       |

| Voltage on any pin with respect to Vss (except VDD and MCLR) | 0.3V to (VDD + 0.3V) |

| Voltage on VDD with respect to Vss                           | 0.3V to +7.5V        |

| Voltage on MCLR with respect to Vss (Note 2)                 | 0V to +13.25V        |

| Total power dissipation (Note 1)                             | 1.0W                 |

| Maximum current out of Vss pin                               | 300 mA               |

| Maximum current into VDD pin                                 | 250 mA               |

| Input clamp current, Iк (Vi < 0 or Vi > VDD)                 | ±20 mA               |

| Output clamp current, loк (Vo < 0 or Vo > VDD)               | ±20 mA               |

| Maximum output current sunk by any I/O pin                   | 25 mA                |

| Maximum output current sourced by any I/O pin                | 25 mA                |

| Maximum current sunk by all ports                            | 200 mA               |

| Maximum current sourced by all ports                         | 200 mA               |

## Note 1: Power dissipation is calculated as follows:

- $\mathsf{Pdis} = \mathsf{VDD} \times \{\mathsf{IDD} \sum \mathsf{IOH}\} + \sum \{(\mathsf{VDD} \mathsf{VOH}) \times \mathsf{IOH}\} + \sum (\mathsf{VOL} \times \mathsf{IOL})$

- **2:** Voltage spikes below Vss at the MCLR/VPP pin, inducing currents greater than 80 mA, may cause latch-up. Thus, a series resistor of 50-100Ω should be used when applying a "low" level to the MCLR/VPP/RE3 pin, rather than pulling this pin directly to Vss.

**† NOTICE:** Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

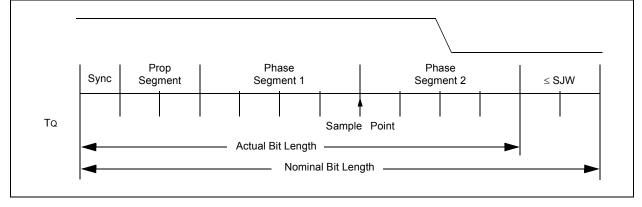

## 40-Lead Plastic Dual In-Line (P) – 600 mil Body [PDIP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | Units    |       | INCHES   |       |

|----------------------------|----------|-------|----------|-------|

| Dimensio                   | n Limits | MIN   | NOM      | MAX   |

| Number of Pins             | Ν        |       | 40       |       |

| Pitch                      | е        |       | .100 BSC |       |

| Top to Seating Plane       | А        | -     | _        | .250  |

| Molded Package Thickness   | A2       | .125  | -        | .195  |

| Base to Seating Plane      | A1       | .015  | -        | -     |

| Shoulder to Shoulder Width | E        | .590  | -        | .625  |

| Molded Package Width       | E1       | .485  | -        | .580  |

| Overall Length             | D        | 1.980 | -        | 2.095 |

| Tip to Seating Plane       | L        | .115  | -        | .200  |

| Lead Thickness             | с        | .008  | -        | .015  |

| Upper Lead Width           | b1       | .030  | -        | .070  |

| Lower Lead Width           | b        | .014  | -        | .023  |

| Overall Row Spacing §      | eB       | -     | -        | .700  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. § Significant Characteristic.

3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" per side.

4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-016B

| STATUS                               |  |

|--------------------------------------|--|

| TXBnEIDH (Transmit Buffer n Extended |  |

| Identifier, High Byte)289            |  |

| TXBnEIDL (Transmit Buffer n Extended |  |

| Identifier, Low Byte)                |  |

| TXBnSIDH (Transmit Buffer n Standard |  |

| Identifier, High Byte)               |  |

| Identifier, Low Byte)                |  |

| TXERRCNT (Transmit Error Count)      |  |

| TXSTA (Transmit Status and Control)  |  |

| WDTCON (Watchdog Timer Control)      |  |

| RESET                                |  |

| Resets                               |  |

| Brown-out Reset (BOR)                |  |

| Oscillator Start-up Timer (OST)      |  |

| Power-on Reset (POR)349              |  |

| Power-up Timer (PWRT)                |  |

| RETFIE                               |  |

| RETLW                                |  |

| RETURN                               |  |

| Return Address Stack                 |  |

| and Associated Registers             |  |

| Return Stack Pointer (STKPTR)        |  |

| Revision History                     |  |

| RLCF                                 |  |

| RRCF                                 |  |

| RRNCF                                |  |

|                                      |  |

| S                                    |  |

|                                      |  |

| SCK                                               | 191     |

|---------------------------------------------------|---------|

| SDI                                               | 191     |

| SDO                                               | 191     |

| SEC_IDLE Mode                                     | 44      |

| SEC_RUN Mode                                      | 40      |

| Serial Clock, SCK                                 | 191     |

| Serial Data In (SDI)                              | 191     |

| Serial Data Out (SDO)                             | 191     |

| Serial Peripheral Interface. See SPI Mode.        |         |

| SETF                                              | 401     |

| Slave Select (SS)                                 | 191     |

| SLEEP                                             | 402     |

| Sleep                                             |         |

| OSC1 and OSC2 Pin States                          | 37      |

| Software Simulator (MPLAB SIM)                    | 419     |

| Special Event Trigger. See Compare (ECCP Mode).   |         |

| Special Event Trigger. See Compare (ECCP Module). |         |

| Special Features of the CPU                       | 349     |

| Special Function Registers                        | 77      |

| Мар                                               | . 77–82 |

| SPI Mode (MSSP)                                   |         |

| Associated Registers                              | 199     |

| Bus Mode Compatibility                            | 199     |

| Effects of a Reset                                | 199     |

|                                                   |         |

| Enabling SPI I/O                 | 195 |

|----------------------------------|-----|

| Master Mode                      | 196 |

| Master/Slave Connection          | 195 |

| Operation                        |     |

| Operation in Power-Managed Modes | 199 |

| Serial Clock                     |     |

| Serial Data In                   | 191 |

| Serial Data Out                  | 191 |

| Slave Mode                       | 197 |

| Slave Select                     | 191 |

| Slave Select Synchronization     | 197 |

| SPI Clock                        | 196 |

| Typical Connection               |     |

| SS                               | 191 |

| SSPOV                            |     |

| SSPOV Status Flag                | 221 |

| SSPSTAT Register                 |     |

| R/W Bit                          |     |

| Stack Full/Underflow Resets      |     |

| STATUS Register                  |     |

| SUBFSR                           |     |

| SUBFWB                           |     |

| SUBLW                            |     |

| SUBULNK                          |     |

| SUBWF                            |     |

| SUBWFB                           |     |

| SWAPF                            | 404 |

## Т

| T0CON Register                           |          |

|------------------------------------------|----------|

| PSA Bit                                  | 153      |

| TOCS Bit                                 | 152      |

| T0PS2:T0PS0 Bits                         | 153      |

| T0SE Bit                                 | 152      |

| Table Pointer Operations (table)         | 104      |

| Table Reads/Table Writes                 | 70       |

| TBLRD                                    | 405      |

| TBLWT                                    | 406      |

| Time-out in Various Situations (table)   | 51       |

| Timer0                                   | 151      |

| 16-Bit Mode Reads and Writes             | 152      |

| Associated Registers                     | 153      |

| Clock Source Edge Select (T0SE Bit)      | 152      |

| Clock Source Select (T0CS Bit)           | 152      |

| Operation                                | 152      |

| Overflow Interrupt                       | 153      |

| Prescaler. See Prescaler, Timer0.        |          |

| Timer1                                   | 155      |

| 16-Bit Read/Write Mode                   | 157      |

| Associated Registers                     | 159      |

| Interrupt                                | 158      |

| Operation                                | 156      |

| Oscillator                               | 155, 157 |

| Oscillator Layout Considerations         | 158      |

| Overflow Interrupt                       | 155      |

| Resetting, Using a Special Event Trigger |          |

| Output (CCP)                             |          |

| Special Event Trigger (ECCP)             | 178      |

| TMR1H Register                           | 155      |

| TMR1L Register                           |          |

| Use as a Real-Time Clock                 | 158      |

| Timer2                                   |          |

| Associated Registers                     | 162      |

| Interrupt                                | 162      |

| Operation                                |          |

| Output                                   | 162      |

|                                          |          |

| 447      |

|----------|

| 448      |

| 449      |

| 450      |

| 440      |

| 437      |

| 452      |

| 454      |

|          |

| 453      |

|          |

| 446      |

| 441      |

|          |

|          |

| 443      |

|          |

| 444      |

|          |

|          |

| 143      |

| 407      |

| 349, 360 |

|          |

| 72       |

|          |

| 235      |

|          |

### ۷

| 436                  |

|----------------------|

|                      |

|                      |

| 349, 358             |

| 359                  |

|                      |

|                      |

|                      |

| . 219, 220, 221, 224 |

| . 219, 220, 221, 224 |

|                      |

| 7                    |

|                      |

|                      |

|                      |

| 408                  |

|                      |