Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 40MHz                                                                    |

| Connectivity               | CANbus, I <sup>2</sup> C, SPI, UART/USART                                |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                              |

| Number of I/O              | 36                                                                       |

| Program Memory Size        | 16KB (8K x 16)                                                           |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 256 x 8                                                                  |

| RAM Size                   | 768 x 8                                                                  |

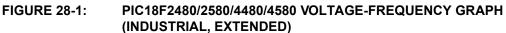

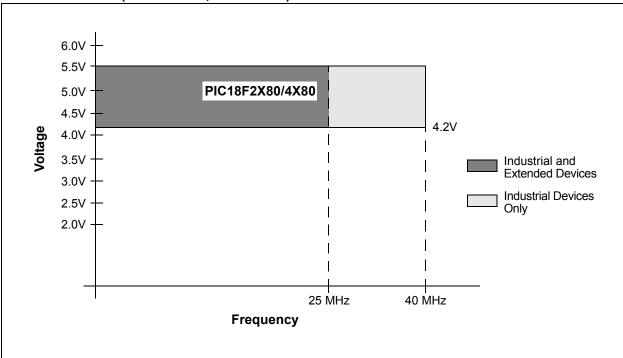

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                              |

| Data Converters            | A/D 11x10b                                                               |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Through Hole                                                             |

| Package / Case             | 40-DIP (0.600", 15.24mm)                                                 |

| Supplier Device Package    | 40-PDIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f4480-i-p |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Table of Contents**

| 1.0  | Device Overview                                              | 9   |

|------|--------------------------------------------------------------|-----|

| 2.0  | Guidelines for Getting Started with PIC18F Microcontrollers  |     |

| 3.0  | Oscillator Configurations                                    |     |

| 4.0  | Power-Managed Modes                                          |     |

| 5.0  | Reset                                                        |     |

| 6.0  | Memory Organization                                          |     |

| 7.0  | Flash Program Memory                                         | 101 |

| 8.0  | Data EEPROM Memory                                           | 111 |

| 9.0  | 8 x 8 Hardware Multiplier                                    | 117 |

| 10.0 | Interrupts                                                   | 119 |

| 11.0 | I/O Ports                                                    | 135 |

| 12.0 | Timer0 Module                                                | 151 |

| 13.0 | Timer1 Module                                                | 155 |

| 14.0 | Timer2 Module                                                |     |

|      | Timer3 Module                                                |     |

|      | Capture/Compare/PWM (CCP) Modules                            |     |

| 17.0 | Enhanced Capture/Compare/PWM (ECCP) Module                   |     |

| 18.0 | Master Synchronous Serial Port (MSSP) Module                 |     |

| 19.0 | Enhanced Universal Synchronous Receiver Transmitter (EUSART) |     |

| 20.0 | 10-Bit Analog-to-Digital Converter (A/D) Module              |     |

| 21.0 | Comparator Module                                            |     |

| 22.0 | Comparator Voltage Reference Module                          |     |

| 23.0 | High/Low-Voltage Detect (HLVD)                               |     |

|      | ECAN Module                                                  |     |

| 25.0 | Special Features of the CPU                                  |     |

| 26.0 |                                                              |     |

| 27.0 | Development Support                                          |     |

|      | Electrical Characteristics                                   |     |

|      | Packaging Information                                        |     |

|      | endix A: Revision History                                    |     |

|      | endix B: Device Differences                                  |     |

| •••  | endix C: Conversion Considerations                           |     |

|      | endix D: Migration from Baseline to Enhanced Devices         |     |

|      | endix E: Migration From Mid-Range to Enhanced Devices        |     |

|      | endix F: Migration From High-End to Enhanced Devices         |     |

|      | Microchip Web Site                                           |     |

|      | omer Change Notification Service                             |     |

|      | omer Support                                                 |     |

|      | ler Response                                                 |     |

| PIC1 | 8F2480/2580/4480/4580 Product Identification System          |     |

# TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@mail.microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

## Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

- The Microchip Corporate Literature Center; U.S. FAX: (480) 792-7277

When contacting a sales office or the literature center, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com/cn to receive the most current information on all of our products.

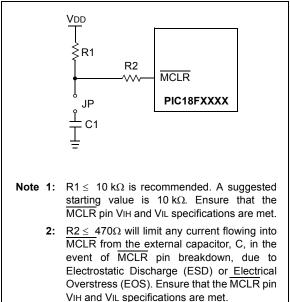

# 2.3 Master Clear (MCLR) Pin

The MCLR pin provides two specific device functions: Device Reset, and Device Programming and Debugging. If programming and debugging are not required in the end application, a direct connection to VDD may be all that is required. The addition of other components, to help increase the application's resistance to spurious Resets from voltage sags, may be beneficial. A typical configuration is shown in Figure 2-1. Other circuit designs may be implemented, depending on the application's requirements.

During programming and debugging, the resistance and capacitance that can be added to the pin must be considered. Device programmers and debuggers drive the MCLR pin. Consequently, specific voltage levels (VIH and VIL) and fast signal transitions must not be adversely affected. Therefore, specific values of R1 and C1 will need to be adjusted based on the application and PCB requirements. For example, it is recommended that the capacitor, C1, be isolated from the MCLR pin during programming and debugging operations by using a jumper (Figure 2-2). The jumper is replaced for normal run-time operations.

Any components associated with the  $\overline{\text{MCLR}}$  pin should be placed within 0.25 inch (6 mm) of the pin.

#### FIGURE 2-2: EXAMPLE OF MCLR PIN CONNECTIONS

# 2.4 ICSP Pins

The PGC and PGD pins are used for In-Circuit Serial Programming<sup>TM</sup> (ICSP<sup>TM</sup>) and debugging purposes. It is recommended to keep the trace length between the ICSP connector and the ICSP pins on the device as short as possible. If the ICSP connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of ohms, not to exceed 100 $\Omega$ .

Pull-up resistors, series diodes, and capacitors on the PGC and PGD pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits and pin input voltage high (VIH) and input low (VIL) requirements.

For device emulation, ensure that the "Communication Channel Select" (i.e., PGCx/PGDx pins) programmed into the device matches the physical connections for the ICSP to the Microchip debugger/emulator tool.

For more information on available Microchip development tools connection requirements, refer to **Section 27.0 "Development Support"**.

# 3.0 OSCILLATOR CONFIGURATIONS

### 3.1 Oscillator Types

PIC18F2480/2580/4480/4580 devices can be operated in ten different oscillator modes. The user can program the Configuration bits, FOSC<3:0>, in Configuration Register 1H to select one of these ten modes:

- 1. LP Low-Power Crystal

- 2. XT Crystal/Resonator

- 3. HS High-Speed Crystal/Resonator

- 4. HSPLL High-Speed Crystal/Resonator with PLL Enabled

- 5. RC External Resistor/Capacitor with Fosc/4 Output on RA6

- 6. RCIO External Resistor/Capacitor with I/O on RA6

- 7. INTIO1 Internal Oscillator with Fosc/4 Output on RA6 and I/O on RA7

- 8. INTIO2 Internal Oscillator with I/O on RA6 and RA7

- 9. EC External Clock with Fosc/4 Output

- 10. ECIO External Clock with I/O on RA6

# 3.2 Crystal Oscillator/Ceramic Resonators

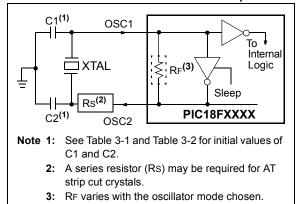

In XT, LP, HS or HSPLL Oscillator modes, a crystal or ceramic resonator is connected to the OSC1 and OSC2 pins to establish oscillation. Figure 3-1 shows the pin connections.

The oscillator design requires the use of a parallel resonant crystal.

Note: Use of a series resonant crystal may give a frequency out of the crystal manufacturer's specifications. FIGURE 3-1:

#### CRYSTAL/CERAMIC RESONATOR OPERATION (XT, LP, HS OR HSPLL CONFIGURATION)

# TABLE 3-1:CAPACITOR SELECTION FOR<br/>CERAMIC RESONATORS

#### **Typical Capacitor Values Used:** Mode OSC1 OSC2 Freq XT 56 pF 455 kHz 56 pF 47 pF 47 pF 2.0 MHz 4.0 MHz 33 pF 33 pF HS 8.0 MHz 27 pF 27 pF 16.0 MHz 22 pF 22 pF

#### Capacitor values are for design guidance only.

These capacitors were tested with the resonators listed below for basic start-up and operation. **These values are not optimized**.

Different capacitor values may be required to produce acceptable oscillator operation. The user should test the performance of the oscillator over the expected VDD and temperature range for the application.

See the notes on page 30 for additional information.

| Resonators Used: |         |  |  |  |  |  |

|------------------|---------|--|--|--|--|--|

| 455 kHz          | 4.0 MHz |  |  |  |  |  |

| 2.0 MHz          | 8.0 MHz |  |  |  |  |  |

| 16.0 MHz         |         |  |  |  |  |  |

Note: When using resonators with frequencies above 3.5 MHz, the use of HS mode, rather than XT mode, is recommended. HS mode may be used at any VDD for which the controller is rated. If HS is selected, it is possible that the gain of the oscillator will overdrive the resonator. Therefore, a series resistor should be placed between the OSC2 pin and the resonator. As a good starting point, the recommended value of Rs is 330Ω.

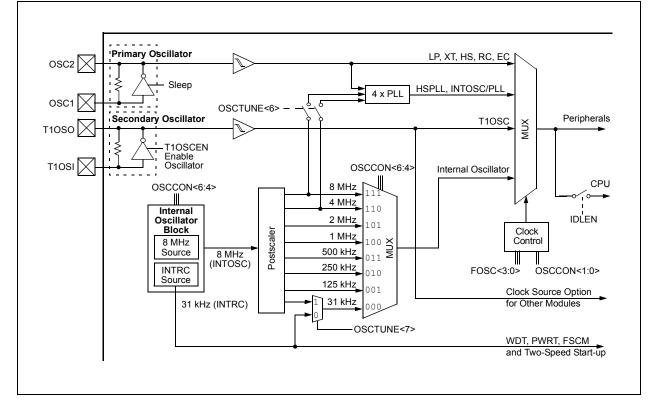

### 3.7 Clock Sources and Oscillator Switching

Like previous PIC18 devices, the PIC18F2480/2580/4480/4580 family includes a feature that allows the device clock source to be switched from the main oscillator to an alternate low-frequency clock source. PIC18F2480/2580/4480/4580 devices offer two alternate clock sources. When an alternate clock source is enabled, the various power-managed operating modes are available.

Essentially, there are three clock sources for these devices:

- Primary oscillators

- · Secondary oscillators

- · Internal oscillator block

The **primary oscillators** include the external crystal and resonator modes, the external RC modes, the external clock modes and the internal oscillator block. The particular mode is defined by the FOSC<3:0> Configuration bits. The details of these modes are covered earlier in this chapter. The **secondary oscillators** are those external sources not connected to the OSC1 or OSC2 pins. These sources may continue to operate even after the controller is placed in a power-managed mode.

PIC18F2480/2580/4480/4580 devices offer the Timer1 oscillator as a secondary oscillator. This oscillator, in all power-managed modes, is often the time base for functions such as a Real-Time Clock (RTC).

Most often, a 32.768 kHz watch crystal is connected between the RC0/T1OSO/T13CKI and RC1/T1OSI pins. Like the LP Oscillator mode circuit, loading capacitors are also connected from each pin to ground.

The Timer1 oscillator is discussed in greater detail in **Section 13.3 "Timer1 Oscillator"**.

In addition to being a primary clock source, the **internal oscillator block** is available as a power-managed mode clock source. The INTRC source is also used as the clock source for several special features, such as the WDT and Fail-Safe Clock Monitor.

The clock sources for the PIC18F2480/2580/4480/4580 devices are shown in Figure 3-8. See **Section 25.0 "Special Features of the CPU"** for Configuration register details.

#### FIGURE 3-8: PIC18F2480/2580/4480/4580 CLOCK DIAGRAM

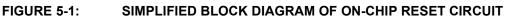

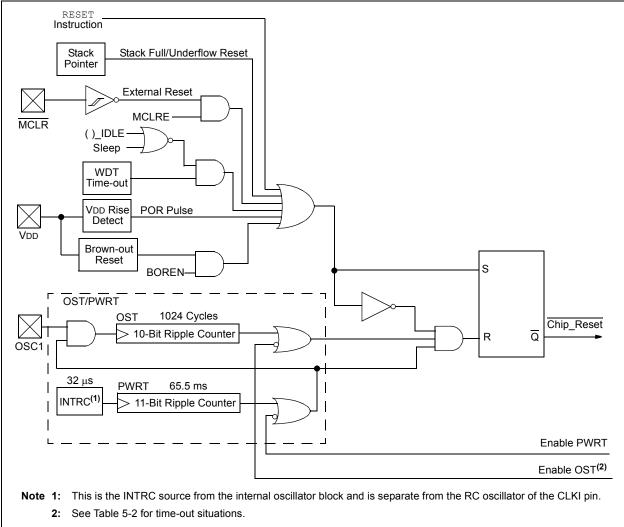

# 5.0 RESET

The PIC18F2480/2580/4480/4580 devices differentiate between various kinds of Reset:

- a) Power-on Reset (POR)

- b) MCLR Reset during normal operation

- c) MCLR Reset during power-managed modes

- d) Watchdog Timer (WDT) Reset (during execution)

- e) Programmable Brown-out Reset (BOR)

- f) RESET Instruction

- g) Stack Full Reset

- h) Stack Underflow Reset

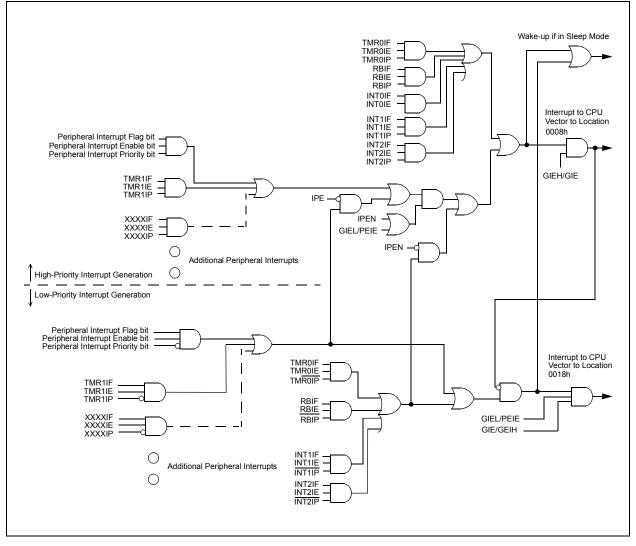

This section discusses Resets generated by MCLR, POR and BOR, and covers the operation of the various start-up timers. Stack Reset events are covered in Section 6.1.2.4 "Stack Full and Underflow Resets". WDT Resets are covered in Section 25.2 "Watchdog Timer (WDT)". A simplified block diagram of the On-Chip Reset Circuit is shown in Figure 5-1.

# 5.1 RCON Register

Device Reset events are tracked through the RCON register (Register 5-1). The lower five bits of the register indicate that a specific Reset event has occurred. In most cases, these bits can only be cleared by the event and must be set by the application after the event. The state of these flag bits, taken together, can be read to indicate the type of Reset that just occurred. This is described in more detail in **Section 5.6 "Reset State of Registers"**.

The RCON register also has control bits for setting interrupt priority (IPEN) and software control of the BOR (SBOREN). Interrupt priority is discussed in Section 10.0 "Interrupts". BOR is covered in Section 5.4 "Brown-out Reset (BOR)".

| TABLE 5-4:            |                             |      |                                    |                               | DITIONS FOR ALL      |                    | •                 | JUED) |      |

|-----------------------|-----------------------------|------|------------------------------------|-------------------------------|----------------------|--------------------|-------------------|-------|------|

| Register              | Register Applicable Devices |      | Power-on Reset,<br>Brown-out Reset | WDT I<br>RESET Ins<br>Stack I | Reset,<br>struction, | Wake-up<br>or Inte | via WDT<br>errupt |       |      |

| RXF3SIDL              | 2480                        | 2580 | 4480                               | 4580                          | XXX- X-XX            | uuu-               | u-uu              | uuu-  | u-uu |

| RXF3SIDH              | 2480                        | 2580 | 4480                               | 4580                          | XXXX XXXX            | սսսս               | uuuu              | սսսս  | uuuu |

| RXF2EIDL              | 2480                        | 2580 | 4480                               | 4580                          | XXXX XXXX            | սսսս               | uuuu              | սսսս  | uuuu |

| RXF2EIDH              | 2480                        | 2580 | 4480                               | 4580                          | XXXX XXXX            | นนนน               | นนนน              | นนนน  | uuuu |

| RXF2SIDL              | 2480                        | 2580 | 4480                               | 4580                          | XXX- X-XX            | uuu-               | u-uu              | uuu-  | u-uu |

| RXF2SIDH              | 2480                        | 2580 | 4480                               | 4580                          | XXXX XXXX            | սսսս               | uuuu              | սսսս  | uuuu |

| RXF1EIDL              | 2480                        | 2580 | 4480                               | 4580                          | XXXX XXXX            | սսսս               | uuuu              | սսսս  | uuuu |

| RXF1EIDH              | 2480                        | 2580 | 4480                               | 4580                          | XXXX XXXX            | นนนน               | นนนน              | սսսս  | uuuu |

| RXF1SIDL              | 2480                        | 2580 | 4480                               | 4580                          | XXX- X-XX            | uuu-               | u-uu              | uuu-  | u-uu |

| RXF1SIDH              | 2480                        | 2580 | 4480                               | 4580                          | XXXX XXXX            | սսսս               | uuuu              | սսսս  | uuuu |

| RXF0EIDL              | 2480                        | 2580 | 4480                               | 4580                          | XXXX XXXX            | սսսս               | uuuu              | սսսս  | uuuu |

| RXF0EIDH              | 2480                        | 2580 | 4480                               | 4580                          | XXXX XXXX            | սսսս               | นนนน              | սսսս  | uuuu |

| RXF0SIDL              | 2480                        | 2580 | 4480                               | 4580                          | XXX- X-XX            | uuu-               | u-uu              | uuu-  | u-uu |

| RXF0SIDH              | 2480                        | 2580 | 4480                               | 4580                          | XXXX XXXX            | uuuu               | uuuu              | uuuu  | uuuu |

| B5D7 <sup>(6)</sup>   | 2480                        | 2580 | 4480                               | 4580                          | XXXX XXXX            | սսսս               | นนนน              | սսսս  | uuuu |

| B5D6 <sup>(6)</sup>   | 2480                        | 2580 | 4480                               | 4580                          | XXXX XXXX            | սսսս               | นนนน              | սսսս  | uuuu |

| B5D5 <sup>(6)</sup>   | 2480                        | 2580 | 4480                               | 4580                          | XXXX XXXX            | uuuu               | uuuu              | uuuu  | uuuu |

| B5D4 <sup>(6)</sup>   | 2480                        | 2580 | 4480                               | 4580                          | XXXX XXXX            | սսսս               | นนนน              | սսսս  | uuuu |

| B5D3 <sup>(6)</sup>   | 2480                        | 2580 | 4480                               | 4580                          | XXXX XXXX            | սսսս               | นนนน              | սսսս  | uuuu |

| B5D2 <sup>(6)</sup>   | 2480                        | 2580 | 4480                               | 4580                          | XXXX XXXX            | uuuu               | uuuu              | uuuu  | uuuu |

| B5D1 <sup>(6)</sup>   | 2480                        | 2580 | 4480                               | 4580                          | XXXX XXXX            | սսսս               | นนนน              | սսսս  | uuuu |

| B5D0 <sup>(6)</sup>   | 2480                        | 2580 | 4480                               | 4580                          | XXXX XXXX            | սսսս               | uuuu              | uuuu  | uuuu |

| B5DLC <sup>(6)</sup>  | 2480                        | 2580 | 4480                               | 4580                          | -xxx xxxx            | -uuu               | uuuu              | -uuu  | uuuu |

| B5EIDL <sup>(6)</sup> | 2480                        | 2580 | 4480                               | 4580                          | XXXX XXXX            | սսսս               | uuuu              | uuuu  | uuuu |

| B5EIDH <sup>(6)</sup> | 2480                        | 2580 | 4480                               | 4580                          | XXXX XXXX            | սսսս               | uuuu              | uuuu  | uuuu |

| B5SIDL <sup>(6)</sup> | 2480                        | 2580 | 4480                               | 4580                          | XXXX X-XX            | սսսս               | u-uu              | սսսս  | u-uu |

| B5SIDH <sup>(6)</sup> | 2480                        | 2580 | 4480                               | 4580                          | XXXX X-XX            | นนนน               | u-uu              | սսսս  | u-uu |

| B5CON <sup>(6)</sup>  | 2480                        | 2580 | 4480                               | 4580                          | 0000 0000            | 0000               | 0000              | սսսս  | uuuu |

| B4D7 <sup>(6)</sup>   | 2480                        | 2580 | 4480                               | 4580                          | XXXX XXXX            | นนนน               | uuuu              | นนนน  | uuuu |

| B4D6 <sup>(6)</sup>   | 2480                        | 2580 | 4480                               | 4580                          | XXXX XXXX            | นนนน               | uuuu              | นนนน  | uuuu |

| B4D5 <sup>(6)</sup>   | 2480                        | 2580 | 4480                               | 4580                          | XXXX XXXX            | սսսս               | uuuu              | սսսս  | uuuu |

### TABLE 5-4: INITIALIZATION CONDITIONS FOR ALL REGISTERS (CONTINUED)

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition. Shaded cells indicate conditions do not apply for the designated device.

Note 1: One or more bits in the INTCONx or PIRx registers will be affected (to cause wake-up).

2: When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the PC is loaded with the interrupt vector (0008h or 0018h).

**3:** When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the TOSU, TOSH and TOSL are updated with the current value of the PC. The STKPTR is modified to point to the next location in the hardware stack.

4: See Table 5-3 for Reset value for specific condition.

**5:** Bits 6 and 7 of PORTA, LATA and TRISA are enabled, depending on the oscillator mode selected. When not enabled as PORTA pins, they are disabled and read '0'.

6: This register reads all '0's until ECAN<sup>™</sup> technology is set up in Mode 1 or Mode 2.

| File Name                              | Bit 7 | Bit 6 | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   | Value on POR, BOR | Details on<br>Page: |

|----------------------------------------|-------|-------|---------|---------|---------|---------|---------|---------|-------------------|---------------------|

| RXF3SIDH                               | SID10 | SID9  | SID8    | SID7    | SID6    | SID5    | SID4    | SID3    | XXXX XXXX         | 62, 308             |

| RXF2EIDL                               | EID7  | EID6  | EID5    | EID4    | EID3    | EID2    | EID1    | EID0    | XXXX XXXX         | 62, 309             |

| RXF2EIDH                               | EID15 | EID14 | EID13   | EID12   | EID11   | EID10   | EID9    | EID8    | XXXX XXXX         | 62, 309             |

| RXF2SIDL                               | SID2  | SID1  | SID0    | _       | EXIDEN  | _       | EID17   | EID16   | xxx- x-xx         | 62, 308             |

| RXF2SIDH                               | SID10 | SID9  | SID8    | SID7    | SID6    | SID5    | SID4    | SID3    | XXXX XXXX         | 62, 308             |

| RXF1EIDL                               | EID7  | EID6  | EID5    | EID4    | EID3    | EID2    | EID1    | EID0    | XXXX XXXX         | 62, 309             |

| RXF1EIDH                               | EID15 | EID14 | EID13   | EID12   | EID11   | EID10   | EID9    | EID8    | XXXX XXXX         | 62, 309             |

| RXF1SIDL                               | SID2  | SID1  | SID0    | _       | EXIDEN  | _       | EID17   | EID16   | xxx- x-xx         | 62, 308             |

| RXF1SIDH                               | SID10 | SID9  | SID8    | SID7    | SID6    | SID5    | SID4    | SID3    | XXXX XXXX         | 62, 308             |

| RXF0EIDL                               | EID7  | EID6  | EID5    | EID4    | EID3    | EID2    | EID1    | EID0    | XXXX XXXX         | 62, 309             |

| RXF0EIDH                               | EID15 | EID14 | EID13   | EID12   | EID11   | EID10   | EID9    | EID8    | XXXX XXXX         | 62, 309             |

| RXF0SIDL                               | SID2  | SID1  | SID0    | _       | EXIDEN  | _       | EID17   | EID16   | xxx- x-xx         | 62, 308             |

| <b>RXF0SIDH</b>                        | SID10 | SID9  | SID8    | SID7    | SID6    | SID5    | SID4    | SID3    | XXXX XXXX         | 62, 308             |

| B5D7 <sup>(8)</sup>                    | B5D77 | B5D76 | B5D75   | B5D74   | B5D73   | B5D72   | B5D71   | B5D70   | XXXX XXXX         | 62, 305             |

| B5D6 <sup>(8)</sup>                    | B5D67 | B5D66 | B5D65   | B5D64   | B5D63   | B5D62   | B5D61   | B5D60   | XXXX XXXX         | 62, 305             |

| B5D5 <sup>(8)</sup>                    | B5D57 | B5D56 | B5D55   | B5D54   | B5D53   | B5D52   | B5D51   | B5D50   | XXXX XXXX         | 62, 305             |

| B5D4 <sup>(8)</sup>                    | B5D47 | B5D46 | B5D45   | B5D44   | B5D43   | B5D42   | B5D41   | B5D40   | XXXX XXXX         | 62, 305             |

| B5D3 <sup>(8)</sup>                    | B5D37 | B5D36 | B5D35   | B5D34   | B5D33   | B5D32   | B5D31   | B5D30   | XXXX XXXX         | 62, 305             |

| B5D2 <sup>(8)</sup>                    | B5D27 | B5D26 | B5D25   | B5D24   | B5D23   | B5D22   | B5D21   | B5D20   | XXXX XXXX         | 62, 305             |

| B5D1 <sup>(8)</sup>                    | B5D17 | B5D16 | B5D15   | B5D14   | B5D13   | B5D12   | B5D11   | B5D10   | XXXX XXXX         | 62, 305             |

| B5D0 <sup>(8)</sup>                    | B5D07 | B5D06 | B5D05   | B5D04   | B5D03   | B5D02   | B5D01   | B5D00   | XXXX XXXX         | 62, 305             |

| B5DLC <sup>(8)</sup><br>Receive mode   | _     | RXRTR | RB1     | RB0     | DLC3    | DLC2    | DLC1    | DLC0    | -xxx xxxx         | 62, 307             |

| B5DLC <sup>(8)</sup><br>Transmit mode  | —     | TXRTR | —       | —       | DLC3    | DLC2    | DLC1    | DLC0    | -x xxxx           | 62, 307             |

| B5EIDL <sup>(8)</sup>                  | EID7  | EID6  | EID5    | EID4    | EID3    | EID2    | EID1    | EID0    | XXXX XXXX         | 62, 305             |

| B5EIDH <sup>(8)</sup>                  | EID15 | EID14 | EID13   | EID12   | EID11   | EID10   | EID9    | EID8    | XXXX XXXX         | 62, 304             |

| B5SIDL <sup>(8)</sup><br>Receive mode  | SID2  | SID1  | SID0    | SRR     | EXID    | _       | EID17   | EID16   | XXXX X-XX         | 62, 303             |

| B5SIDL <sup>(8)</sup><br>Transmit mode | SID2  | SID1  | SID0    | —       | EXIDE   | _       | EID17   | EID16   | xxx- x-xx         | 62, 303             |

| B5SIDH <sup>(8)</sup>                  | SID10 | SID9  | SID8    | SID7    | SID6    | SID5    | SID4    | SID3    | xxxx x-xx         | 62, 302             |

| B5CON <sup>(8)</sup><br>Receive mode   | RXFUL | RXM1  | RXRTRRO | FILHIT4 | FILHIT3 | FILHIT2 | FILHIT1 | FILHIT0 | 0000 0000         | 62, 301             |

| B5CON <sup>(8)</sup><br>Transmit mode  | TXBIF | TXABT | TXLARB  | TXERR   | TXREQ   | RTREN   | TXPRI1  | TXPRI0  | 0000 0000         | 62, 301             |

| B4D7 <sup>(8)</sup>                    | B4D77 | B4D76 | B4D75   | B4D74   | B4D73   | B4D72   | B4D71   | B4D70   | XXXX XXXX         | 62, 305             |

| B4D6 <sup>(8)</sup>                    | B4D67 | B4D66 | B4D65   | B4D64   | B4D63   | B4D62   | B4D61   | B4D60   | XXXX XXXX         | 62, 305             |

| B4D5 <sup>(8)</sup>                    | B4D57 | B4D56 | B4D55   | B4D54   | B4D53   | B4D52   | B4D51   | B4D50   | XXXX XXXX         | 62, 305             |

| B4D4 <sup>(8)</sup>                    | B4D47 | B4D46 | B4D45   | B4D44   | B4D43   | B4D42   | B4D41   | B4D40   | XXXX XXXX         | 63, 305             |

| B4D3 <sup>(8)</sup>                    | B4D37 | B4D36 | B4D35   | B4D34   | B4D33   | B4D32   | B4D31   | B4D30   | XXXX XXXX         | 63, 305             |

| TABLE 6-2: | REGISTER FILE SUMMARY ( | PIC18F2480/2580/4480/4580 | (CONTINUED) |

|------------|-------------------------|---------------------------|-------------|

|------------|-------------------------|---------------------------|-------------|

**Legend:** x = unknown, u = unchanged, - = unimplemented, q = value depends on condition

Note 1: Bit 21 of the PC is only available in Test mode and Serial Programming modes.

The SBOREN bit is only available when CONFIG2L<1:0> = 01; otherwise, it is disabled and reads as '0'. See Section 5.4 "Brown-out Reset (BOR)".

These registers and/or bits are not implemented on PIC18F2X80 devices and are read as '0'. Reset values are shown for PIC18F4X80 devices; individual unimplemented bits should be interpreted as '-'.

4: The PLLEN bit is only available in specific oscillator configuration; otherwise, it is disabled and reads as '0'. See Section 3.6.4 "PLL in INTOSC Modes".

5: The RE3 bit is only available when Master Clear Reset is disabled (CONFIG3H<7> = 0); otherwise, RE3 reads as '0'. This bit is read-only.

6: RA6/RA7 and their associated latch and direction bits are individually configured as port pins based on various primary oscillator modes. When disabled, these bits read as '0'.

7: CAN bits have multiple functions depending on the selected mode of the CAN module.

8: This register reads all '0's until the ECAN™ technology is set up in Mode 1 or Mode 2.

9: These registers are available on PIC18F4X80 devices only.

## 7.2.2 TABLAT – TABLE LATCH REGISTER

The Table Latch (TABLAT) is an 8-bit register mapped into the SFR space. The Table Latch register is used to hold 8-bit data during data transfers between program memory and data RAM.

#### 7.2.3 TBLPTR – TABLE POINTER REGISTER

The Table Pointer (TBLPTR) register addresses a byte within the program memory. The TBLPTR is comprised of three SFR registers: Table Pointer Upper Byte, Table Pointer High Byte and Table Pointer Low Byte (TBLPTRU:TBLPTRH:TBLPTRL). These three registers join to form a 22-bit wide pointer. The low-order 21 bits allow the device to address up to 2 Mbytes of program memory space. The 22nd bit allows access to the Device ID, the user ID and the Configuration bits.

The Table Pointer, TBLPTR, is used by the TBLRD and TBLWT instructions. These instructions can update the TBLPTR in one of four ways based on the table operation. These operations are shown in Table 7-1. These operations on the TBLPTR only affect the low-order 21 bits.

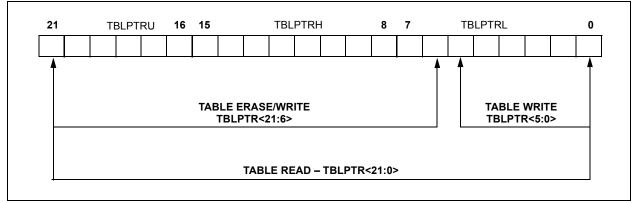

## 7.2.4 TABLE POINTER BOUNDARIES

TBLPTR is used in reads, writes and erases of the Flash program memory.

When a TBLRD is executed, all 22 bits of the TBLPTR determine which byte is read from program memory into TABLAT.

When a TBLWT is executed, the five LSbs of the Table Pointer register (TBLPTR<4:0>) determine which of the 32 program memory holding registers is written to. When the timed write to program memory begins (via the WR bit), the 16 MSbs of the TBLPTR (TBLPTR<21:6>) determine which program memory block of 32 bytes is written to. For more detail, see **Section 7.5 "Writing to Flash Program Memory"**.

When an erase of program memory is executed, the 16 MSbs of the Table Pointer register (TBLPTR<21:6>) point to the 64-byte block that will be erased. The Least Significant bits (TBLPTR<5:0>) are ignored.

Figure 7-3 describes the relevant boundaries of TBLPTR based on Flash program memory operations.

#### TABLE 7-1: TABLE POINTER OPERATIONS WITH TBLRD AND TBLWT INSTRUCTIONS

| Example Operation on Table Pointer |                                             |  |  |  |  |  |

|------------------------------------|---------------------------------------------|--|--|--|--|--|

| TBLRD*<br>TBLWT*                   | TBLPTR is not modified                      |  |  |  |  |  |

| TBLRD*+<br>TBLWT*+                 | TBLPTR is incremented after the read/write  |  |  |  |  |  |

| TBLRD*-<br>TBLWT*-                 | TBLPTR is decremented after the read/write  |  |  |  |  |  |

| TBLRD+*<br>TBLWT+*                 | TBLPTR is incremented before the read/write |  |  |  |  |  |

#### FIGURE 7-3: TABLE POINTER BOUNDARIES BASED ON OPERATION

### 23.6 Operation During Sleep

When enabled, the HLVD circuitry continues to operate during Sleep. If the device voltage crosses the trip point, the HLVDIF bit will be set and the device will wake-up from Sleep. Device execution will continue from the interrupt vector address if interrupts have been globally enabled.

## 23.7 Effects of a Reset

A device Reset forces all registers to their Reset state. This forces the HLVD module to be turned off.

| Name    | Bit 7    | Bit 6     | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0   | Reset<br>Values<br>on Page: |

|---------|----------|-----------|--------|--------|--------|--------|--------|---------|-----------------------------|

| HLVDCON | VDIRMAG  | —         | IRVST  | HLVDEN | HLVDL3 | HLVDL2 | HLVDL1 | HLVDL0  | 56                          |

| INTCON  | GIE/GIEH | PEIE/GIEL | TMR0IE | INT0IE | RBIE   | TMR0IF | INT0IF | RBIF    | 55                          |

| PIR2    | OSCFIF   | CMIF      | —      | EEIF   | BCLIF  | HLVDIF | TMR3IF | ECCP1IF | 58                          |

| PIE2    | OSCFIE   | CMIE      | _      | EEIE   | BCLIE  | HLVDIE | TMR3IE | ECCP1IE | 58                          |

| IPR2    | OSCFIP   | CMIP      | _      | EEIP   | BCLIP  | HLVDIP | TMR3IP | ECCP1IP | 57                          |

#### TABLE 23-1: REGISTERS ASSOCIATED WITH HIGH/LOW-VOLTAGE DETECT MODULE

Legend: — = unimplemented, read as '0'. Shaded cells are unused by the HLVD module.

####

| R/W-x |

|-------|-------|-------|-------|-------|-------|-------|-------|

| EID7  | EID6  | EID5  | EID4  | EID3  | EID2  | EID1  | EID0  |

| bit 7 |       |       |       |       |       |       | bit 0 |

|       |       |       |       |       |       |       |       |

| Legend:           |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

bit 7-0 EID<7:0>: Extended Identifier bits

Note 1: These registers are available in Mode 1 and 2 only.

# REGISTER 24-32: BnDm: TX/RX BUFFER n DATA FIELD BYTE m REGISTERS IN RECEIVE MODE $[0 \le n \le 5, 0 \le m \le 7, TXnEN (BSEL < n >) = 0]^{(1)}$

| R-x   |

|-------|-------|-------|-------|-------|-------|-------|-------|

| BnDm7 | BnDm6 | BnDm5 | BnDm4 | BnDm3 | BnDm2 | BnDm1 | BnDm0 |

| bit 7 |       |       |       |       |       |       | bit 0 |

| Legend:                                                              |                  |                      |                    |  |

|----------------------------------------------------------------------|------------------|----------------------|--------------------|--|

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |                  |                      |                    |  |

| -n = Value at POR                                                    | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |  |

bit 7-0 BnDm<7:0>: Receive Buffer n Data Field Byte m bits (where 0 ≤ n < 3 and 0 < m < 8) Each receive buffer has an array of registers. For example, Receive Buffer 0 has 7 registers: B0D0 to B0D7.

Note 1: These registers are available in Mode 1 and 2 only.

# REGISTER 24-33: BnDm: TX/RX BUFFER n DATA FIELD BYTE m REGISTERS IN TRANSMIT MODE $[0 \le n \le 5, 0 \le m \le 7, TXnEN (BSEL<n>) = 1]^{(1)}$

| R/W-x |

|-------|-------|-------|-------|-------|-------|-------|-------|

| BnDm7 | BnDm6 | BnDm5 | BnDm4 | BnDm3 | BnDm2 | BnDm1 | BnDm0 |

| bit 7 |       |       |       |       |       |       | bit 0 |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 7-0BnDm<7:0>: Transmit Buffer n Data Field Byte m bits (where 0 ≤ n < 3 and 0 < m < 8)</th>Each transmit buffer has an array of registers. For example, Transmit Buffer 0 has 7 registers: TXB0D0 to TXB0D7.

Note 1: These registers are available in Mode 1 and 2 only.

| <b>B</b> # 4 / A                                                  | <b>-</b>                                                                                                     |                                                                                                                                                                        |                                                                                                | <b>B</b> # 4 / A                   |                | <b>-</b>      | <b>-</b> |

|-------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|------------------------------------|----------------|---------------|----------|

| R/W-0                                                             | R/W-0                                                                                                        | R/W-0                                                                                                                                                                  | R/W-0                                                                                          | R/W-0                              | R/W-0          | R/W-0         | R/W-0    |

| SEG2PHTS                                                          | SAM                                                                                                          | SEG1PH2                                                                                                                                                                | SEG1PH1                                                                                        | SEG1PH0                            | PRSEG2         | PRSEG1        | PRSEG0   |

| bit 7                                                             |                                                                                                              |                                                                                                                                                                        |                                                                                                |                                    |                |               | bit 0    |

|                                                                   |                                                                                                              |                                                                                                                                                                        |                                                                                                |                                    |                |               |          |

| Legend:                                                           |                                                                                                              |                                                                                                                                                                        |                                                                                                |                                    |                |               |          |

| R = Readable bitW = Writable bit-n = Value at POR'1' = Bit is set |                                                                                                              | W = Writable                                                                                                                                                           | bit                                                                                            | U = Unimplemented bit, read as '0' |                |               |          |

|                                                                   |                                                                                                              |                                                                                                                                                                        | '0' = Bit is cleared x = Bit is unknown                                                        |                                    | nown           |               |          |

| bit 7                                                             | 1 = Freely pro                                                                                               | 0                                                                                                                                                                      |                                                                                                |                                    | (IPT), whichev | er is greater |          |

| bit 6                                                             | 1 = Bus line is                                                                                              | e of the CAN business of the CAN business of the sampled threases as a sampled once                                                                                    | e times prior to                                                                               | o the sample po<br>e point         | oint           |               |          |

| bit 5-3                                                           | 111 = Phase<br>110 = Phase<br>101 = Phase<br>100 = Phase<br>011 = Phase<br>010 = Phase<br>001 = Phase        | >: Phase Segr<br>Segment 1 tim<br>Segment 1 tim                  | e = 8 x Tq<br>e = 7 x Tq<br>e = 6 x Tq<br>e = 5 x Tq<br>e = 4 x Tq<br>e = 3 x Tq<br>e = 2 x Tq |                                    |                |               |          |

| bit 2-0                                                           | 111 = Propag<br>110 = Propag<br>101 = Propag<br>100 = Propag<br>011 = Propag<br>010 = Propag<br>001 = Propag | •: Propagation<br>gation time = 8<br>gation time = 7<br>gation time = 6<br>gation time = 5<br>gation time = 4<br>gation time = 3<br>gation time = 2<br>gation time = 1 | x TQ<br>x TQ<br>x TQ<br>x TQ<br>x TQ<br>x TQ<br>x TQ<br>x TQ                                   | its                                |                |               |          |

### REGISTER 24-53: BRGCON2: BAUD RATE CONTROL REGISTER 2

## 24.3 CAN Modes of Operation

The PIC18F2480/2580/4480/4580 has six main modes of operation:

- Configuration mode

- · Disable/Sleep mode

- Normal Operation mode

- · Listen Only mode

- · Loopback mode

- · Error Recognition mode

All modes, except Error Recognition, are requested by setting the REQOP bits (CANCON<7:5>). Error Recognition mode is requested through the RXM bits of the Receive Buffer register(s). Entry into a mode is Acknowledged by monitoring the OPMODE bits.

When changing modes, the mode will not actually change until all pending message transmissions are complete. Because of this, the user must verify that the device has actually changed into the requested mode before further operations are executed.

#### 24.3.1 CONFIGURATION MODE

The CAN module has to be initialized before the activation. This is only possible if the module is in the Configuration mode. The Configuration mode is requested by setting the REQOP2 bit. Only when the status bit, OPMODE2, has a high level can the initialization be performed. Afterwards, the Configuration registers, the acceptance mask registers and the acceptance filter registers can be written. The module is activated by setting the REQOP control bits to zero.

The module will protect the user from accidentally violating the CAN protocol through programming errors. All registers which control the configuration of the module can not be modified while the module is online. The CAN module will not be allowed to enter the Configuration mode while a transmission or reception is taking place. The Configuration mode serves as a lock to protect the following registers:

- Configuration Registers

- Functional Mode Selection Registers

- Bit Timing Registers

- Identifier Acceptance Filter Registers

- Identifier Acceptance Mask Registers

- Filter and Mask Control Registers

- Mask Selection Registers

In the Configuration mode, the module will not transmit or receive. The error counters are cleared and the interrupt flags remain unchanged. The programmer will have access to Configuration registers that are access restricted in other modes. I/O pins will revert to normal I/O functions.

#### 24.3.2 DISABLE/SLEEP MODE

In Disable/Sleep mode, the module will not transmit or receive. The module has the ability to set the WAKIF bit due to bus activity; however, any pending interrupts will remain and the error counters will retain their value.

If the REQOP<2:0> bits are set to '001', the module will enter the module Disable/Sleep mode. This mode is similar to disabling other peripheral modules by turning off the module enables. This causes the module internal clock to stop unless the module is active (i.e., receiving or transmitting a message). If the module is active, the module will wait for 11 recessive bits on the CAN bus, detect that condition as an Idle bus, then accept the module Disable/Sleep command. OPMODE<2:0> = 001 indicates whether the module successfully went into the module Disable/Sleep mode.

The WAKIF interrupt is the only module interrupt that is still active in the Disable/Sleep mode. If the WAKDIS is cleared and WAKIE is set, the processor will receive an interrupt whenever the module detects recessive to dominant transition. On wake-up, the module will automatically be set to the previous mode of operation. For example, if the module was switched from Normal to Disable/Sleep mode on bus activity wake-up, the module will automatically enter into Normal mode and the first message that caused the module to wake-up is lost. The module will not generate any error frame. Firmware logic must detect this condition and make sure that retransmission is requested. If the processor receives a wake-up interrupt while it is sleeping, more than one message may get lost. The actual number of messages lost would depend on the processor oscillator start-up time and incoming message bit rate.

The TXCAN pin will stay in the recessive state while the module is in Disable/Sleep mode.

#### 24.3.3 NORMAL MODE

This is the standard operating mode of the PIC18F2480/2580/4480/4580 devices. In this mode, the device actively monitors all bus messages and generates Acknowledge bits, error frames, etc. This is also the only mode in which the PIC18F2480/2580/4480/4580 devices will transmit messages over the CAN bus.

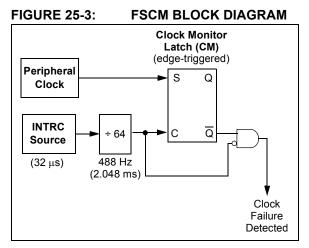

### 25.4 Fail-Safe Clock Monitor

The Fail-Safe Clock Monitor (FSCM) allows the microcontroller to continue operation in the event of an external oscillator failure by automatically switching the device clock to the internal oscillator block. The FSCM function is enabled by setting the FCMEN Configuration bit.

When FSCM is enabled, the INTRC oscillator runs at all times to monitor clocks to peripherals and provide a backup clock in the event of a clock failure. Clock monitoring (shown in Figure 25-3) is accomplished by creating a sample clock signal, which is the INTRC output divided by 64. This allows ample time between FSCM sample clocks for a peripheral clock edge to occur. The peripheral device clock and the sample clock are presented as inputs to the Clock Monitor (CM) latch. The CM is set on the falling edge of the device clock source, but cleared on the rising edge of the sample clock.

Clock failure is tested for on the falling edge of the sample clock. If a sample clock falling edge occurs while CM is still set, a clock failure has been detected (Figure 25-4). This causes the following:

- the FSCM generates an oscillator fail interrupt by setting bit, OSCFIF (PIR2<7>);

- the device clock source is switched to the internal oscillator block (OSCCON is not updated to show the current clock source – this is the Fail-Safe condition); and

- the WDT is reset.

During switchover, the postscaler frequency from the internal oscillator block may not be sufficiently stable for timing-sensitive applications. In these cases, it may be desirable to select another clock configuration and enter an alternate power-managed mode. This can be done to attempt a partial recovery or execute a controlled shutdown. See Section 4.1.4 "Multiple Sleep Commands" and Section 25.3.1 "Special Considerations for Using Two-Speed Start-up" for more details.

To use a higher clock speed on wake-up, the INTOSC or postscaler clock sources can be selected to provide a higher clock speed by setting bits, IRCF<2:0>, immediately after Reset. For wake-ups from Sleep, the INTOSC or postscaler clock sources can be selected by setting the IRCF<2:0> bits prior to entering Sleep mode.

The FSCM will detect failures of the primary or secondary clock sources only. If the internal oscillator block fails, no failure would be detected, nor would any action be possible.

#### 25.4.1 FSCM AND THE WATCHDOG TIMER

Both the FSCM and the WDT are clocked by the INTRC oscillator. Since the WDT operates with a separate divider and counter, disabling the WDT has no effect on the operation of the INTRC oscillator when the FSCM is enabled.

As already noted, the clock source is switched to the INTOSC clock when a clock failure is detected. Depending on the frequency selected by the IRCF<2:0> bits, this may mean a substantial change in the speed of code execution. If the WDT is enabled with a small prescale value, a decrease in clock speed allows a WDT time-out to occur and a subsequent device Reset. For this reason, Fail-Safe Clock events also reset the WDT and postscaler, allowing it to start timing from when execution speed was changed and decreasing the likelihood of an erroneous time-out.

#### 25.4.2 EXITING FAIL-SAFE OPERATION

The Fail-Safe condition is terminated by either a device Reset or by entering a power-managed mode. On Reset, the controller starts the primary clock source specified in Configuration Register 1H (with any required start-up delays that are required for the oscillator mode, such as OST or PLL timer). The INTOSC multiplexer provides the device clock until the primary clock source becomes ready (similar to a Two-Speed Start-up). The clock source is then switched to the primary clock (indicated by the OSTS bit in the OSCCON register becoming set). The Fail-Safe Clock Monitor then resumes monitoring the peripheral clock.

The primary clock source may never become ready during start-up. In this case, operation is clocked by the INTOSC multiplexer. The OSCCON register will remain in its Reset state until a power-managed mode is entered.

| Byte-oriented file register operations                                                                                                                                                                                                                | Example Instruction  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| 15 10 9 8 7 0                                                                                                                                                                                                                                         |                      |

| OPCODE d a f (FILE #)                                                                                                                                                                                                                                 | ADDWF MYREG, W, B    |

| <ul> <li>d = 0 for result destination to be WREG register</li> <li>d = 1 for result destination to be file register (f)</li> <li>a = 0 to force Access Bank</li> <li>a = 1 for BSR to select bank</li> <li>f = 8-bit file register address</li> </ul> |                      |

| Byte to Byte move operations (2-word)                                                                                                                                                                                                                 |                      |

| <u>15 12 11 0</u>                                                                                                                                                                                                                                     |                      |

| OPCODE f (Source FILE #)                                                                                                                                                                                                                              | MOVFF MYREG1, MYREG2 |

| <u>15 12 11 0</u>                                                                                                                                                                                                                                     |                      |

| 1111 f (Destination FILE #)                                                                                                                                                                                                                           |                      |

| f = 12-bit file register address                                                                                                                                                                                                                      |                      |

| Bit-oriented file register operations                                                                                                                                                                                                                 |                      |

| <u>15 12 11 9 8 7 0</u>                                                                                                                                                                                                                               |                      |

| OPCODE b (BIT #) a f (FILE #)                                                                                                                                                                                                                         | BSF MYREG, bit, B    |

| <ul> <li>b = 3-bit position of bit in file register (f)</li> <li>a = 0 to force Access Bank</li> <li>a = 1 for BSR to select bank</li> <li>f = 8-bit file register address</li> </ul>                                                                 |                      |

| Literal operations                                                                                                                                                                                                                                    |                      |

| 15 8 7 0<br>OPCODE k (literal)                                                                                                                                                                                                                        | MOVLW 7Fh            |

| OPCODE     k (literal)       k = 8-bit immediate value                                                                                                                                                                                                |                      |

|                                                                                                                                                                                                                                                       |                      |

| Control operations                                                                                                                                                                                                                                    |                      |

| CALL, GOTO and Branch operations                                                                                                                                                                                                                      |                      |

| 15 8 7 0                                                                                                                                                                                                                                              |                      |

| OPCODE n<7:0> (literal)                                                                                                                                                                                                                               | GOTO Label           |

|                                                                                                                                                                                                                                                       |                      |

| 1111 n<19:8> (literal)                                                                                                                                                                                                                                |                      |

| n = 20-bit immediate value                                                                                                                                                                                                                            |                      |

| <u>15 8 7 0</u>                                                                                                                                                                                                                                       |                      |

| OPCODE S n<7:0> (literal)                                                                                                                                                                                                                             | CALL MYFUNC          |

| 15 12 11 0                                                                                                                                                                                                                                            |                      |

| 1111 n<19:8> (literal)                                                                                                                                                                                                                                |                      |

| S = Fast bit                                                                                                                                                                                                                                          |                      |

| 15 11 10 0                                                                                                                                                                                                                                            |                      |

| OPCODE n<10:0> (literal)                                                                                                                                                                                                                              | BRA MYFUNC           |

|                                                                                                                                                                                                                                                       |                      |

|                                                                                                                                                                                                                                                       |                      |

| 15     8     7     0       OPCODE     n<7:0> (literal)                                                                                                                                                                                                | BC MYFUNC            |

| COMF              | Complement f                                                                                             | CPFSEQ            | Compare f with W, Skip if f = W                                                                                           |

|-------------------|----------------------------------------------------------------------------------------------------------|-------------------|---------------------------------------------------------------------------------------------------------------------------|

| Syntax:           | COMF f {,d {,a}}                                                                                         | Syntax:           | CPFSEQ f {,a}                                                                                                             |

| Operands:         | 0 ≤ f ≤ 255                                                                                              | Operands:         | $0 \le f \le 255$                                                                                                         |

|                   | d ∈ [0,1]                                                                                                |                   | a ∈ [0,1]                                                                                                                 |

|                   | a ∈ [0,1]                                                                                                | Operation:        | (f) – (W),                                                                                                                |

| Operation:        | $(\overline{f}) \rightarrow dest$                                                                        |                   | skip if (f) = (W)                                                                                                         |

| Status Affected:  | N, Z                                                                                                     |                   | (unsigned comparison)                                                                                                     |

| Encoding:         | 0001 11da ffff ffff                                                                                      | Status Affected:  | None                                                                                                                      |

| Description:      | The contents of register 'f' are                                                                         | Encoding:         | 0110 001a ffff ffff                                                                                                       |

| Description.      | complemented. If 'd' is '1', the result is stored in W. If 'd' is '0', the result is                     | Description:      | Compares the contents of data memory<br>location 'f' to the contents of W by<br>performing an unsigned subtraction.       |

|                   | stored back in register 'f'.                                                                             |                   |                                                                                                                           |

|                   | If 'a' is '0', the Access Bank is selected.<br>If 'a' is '1', the BSR is used to select the<br>GPR bank. |                   | If 'f' = W, then the fetched instruction is discarded and a NOP is executed instead, making this a two-cycle instruction. |

|                   | If 'a' is '0' and the extended instruction                                                               |                   | If 'a' is '0', the Access Bank is selected.                                                                               |

|                   | set is enabled, this instruction operates<br>in Indexed Literal Offset Addressing                        |                   | If 'a' is '0', the BSR is used to select the GPR bank.                                                                    |

|                   | mode whenever f $\leq$ 95 (5Fh). See                                                                     |                   | If 'a' is '0' and the extended instruction                                                                                |

|                   | Section 26.2.3 "Byte-Oriented and                                                                        |                   | set is enabled, this instruction operates                                                                                 |

|                   | Bit-Oriented Instructions in Indexed<br>Literal Offset Mode" for details.                                |                   | in Indexed Literal Offset Addressing                                                                                      |

| Words:            |                                                                                                          |                   | mode whenever f ≤ 95 (5Fh). See<br>Section 26.2.3 "Byte-Oriented and                                                      |

|                   |                                                                                                          |                   | Bit-Oriented Instructions in Indexed                                                                                      |

| Cycles:           | 1                                                                                                        |                   | Literal Offset Mode" for details.                                                                                         |

| Q Cycle Activity: |                                                                                                          | Words:            | 1                                                                                                                         |

| Q1                | Q2 Q3 Q4                                                                                                 | Cycles:           | 1(2)                                                                                                                      |

| Decode            | ReadProcessWrite toregister 'f'Datadestination                                                           | ,                 | <b>Note:</b> 3 cycles if skip and followed by a 2-word instruction.                                                       |

|                   |                                                                                                          | Q Cycle Activity: | .,                                                                                                                        |

| Example:          | COMF REG, 0, 0                                                                                           | Q1                | Q2 Q3 Q4                                                                                                                  |

| Before Instruct   | ion                                                                                                      | Decode            | Read Process No                                                                                                           |

| REG               | = 13h                                                                                                    |                   | register 'f' Data operation                                                                                               |

| After Instruction |                                                                                                          | lf skip:          |                                                                                                                           |

| REG<br>W          | = 13h<br>= ECh                                                                                           | Q1                | Q2 Q3 Q4                                                                                                                  |

|                   |                                                                                                          | No                | No No No                                                                                                                  |

|                   |                                                                                                          | operation         | operation operation operation                                                                                             |

|                   |                                                                                                          |                   | d by 2-word instruction:                                                                                                  |

|                   |                                                                                                          | Q1                | Q2 Q3 Q4                                                                                                                  |

|                   |                                                                                                          | No<br>operation   | No No No<br>operation operation                                                                                           |

|                   |                                                                                                          | No                | No No No                                                                                                                  |

|                   |                                                                                                          | operation         | operation operation operation                                                                                             |

|                   |                                                                                                          | Example:          | HERE CPFSEQ REG, 0<br>NEQUAL :                                                                                            |

|                   |                                                                                                          |                   | EQUAL :                                                                                                                   |

|                   |                                                                                                          | Before Instruc    |                                                                                                                           |

|                   |                                                                                                          | PC Addr           |                                                                                                                           |

|                   |                                                                                                          | W<br>REG          | = ?<br>= ?                                                                                                                |

| PC Address        | = | HERE    |          |

|-------------------|---|---------|----------|

| W                 | = | ?       |          |

| REG               | = | ?       |          |

| After Instruction |   |         |          |

| If REG            | = | W;      |          |

| PC                | = | Address | (EQUAL)  |

| If REG            | ≠ | W;      |          |

| PC                | = | Address | (NEQUAL) |

| CPF         | SGT                   | Compare                                                        | f with W, Sk                                                                                   | ip if f > W                                        |

|-------------|-----------------------|----------------------------------------------------------------|------------------------------------------------------------------------------------------------|----------------------------------------------------|

| Synta       | ax:                   | CPFSGT                                                         | f {,a}                                                                                         |                                                    |