Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 40MHz                                                                     |

| Connectivity               | CANbus, I <sup>2</sup> C, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                               |

| Number of I/O              | 36                                                                        |

| Program Memory Size        | 16KB (8K x 16)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 768 × 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                               |

| Data Converters            | A/D 11x10b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 44-TQFP                                                                   |

| Supplier Device Package    | 44-TQFP (10x10)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f4480-i-pt |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Register                 | Applicable Devices |      | Applicable Devices Power-on Reset,<br>Brown-out Reset |      | MCLR Resets,<br>WDT Reset,<br>RESET Instruction,<br>Stack Resets | Wake-up via WDT<br>or Interrupt |           |

|--------------------------|--------------------|------|-------------------------------------------------------|------|------------------------------------------------------------------|---------------------------------|-----------|

| RXF13EIDL <sup>(6)</sup> | 2480               | 2580 | 4480                                                  | 4580 | XXXX XXXX                                                        | սսսս սսսս                       | սսսս սսսս |

| RXF13EIDH <sup>(6)</sup> | 2480               | 2580 | 4480                                                  | 4580 | XXXX XXXX                                                        | սսսս սսսս                       | սսսս սսսս |

| RXF13SIDL <sup>(6)</sup> | 2480               | 2580 | 4480                                                  | 4580 | xxx- x-xx                                                        | uuu- u-uu                       | uuu- u-uu |

| RXF13SIDH <sup>(6)</sup> | 2480               | 2580 | 4480                                                  | 4580 | XXXX XXXX                                                        | սսսս սսսս                       | սսսս սսսս |

| RXF12EIDL <sup>(6)</sup> | 2480               | 2580 | 4480                                                  | 4580 | XXXX XXXX                                                        | นนนน นนนน                       | นนนน นนนน |

| RXF12EIDH <sup>(6)</sup> | 2480               | 2580 | 4480                                                  | 4580 | XXXX XXXX                                                        | սսսս սսսս                       | սսսս սսսս |

| RXF12SIDL <sup>(6)</sup> | 2480               | 2580 | 4480                                                  | 4580 | XXX- X-XX                                                        | uuu- u-uu                       | uuu- u-uu |

| RXF12SIDH <sup>(6)</sup> | 2480               | 2580 | 4480                                                  | 4580 | XXXX XXXX                                                        | սսսս սսսս                       | սսսս սսսս |

| RXF11EIDL <sup>(6)</sup> | 2480               | 2580 | 4480                                                  | 4580 | XXXX XXXX                                                        | սսսս սսսս                       | uuuu uuuu |

| RXF11EIDH <sup>(6)</sup> | 2480               | 2580 | 4480                                                  | 4580 | XXXX XXXX                                                        | սսսս սսսս                       | uuuu uuuu |

| RXF11SIDL <sup>(6)</sup> | 2480               | 2580 | 4480                                                  | 4580 | XXX- X-XX                                                        | uuu- u-uu                       | uuu- u-uu |

| RXF11SIDH <sup>(6)</sup> | 2480               | 2580 | 4480                                                  | 4580 | XXXX XXXX                                                        | սսսս սսսս                       | սսսս սսսս |

| RXF10EIDL <sup>(6)</sup> | 2480               | 2580 | 4480                                                  | 4580 | XXXX XXXX                                                        | սսսս սսսս                       | -uuu uuuu |

| RXF10EIDH <sup>(6)</sup> | 2480               | 2580 | 4480                                                  | 4580 | XXXX XXXX                                                        | սսսս սսսս                       | -uuu uuuu |

| RXF10SIDL <sup>(6)</sup> | 2480               | 2580 | 4480                                                  | 4580 | XXX- X-XX                                                        | uuu- u-uu                       | -uuu uuuu |

| RXF10SIDH <sup>(6)</sup> | 2480               | 2580 | 4480                                                  | 4580 | XXXX XXXX                                                        | սսսս սսսս                       | -uuu uuuu |

| RXF9EIDL <sup>(6)</sup>  | 2480               | 2580 | 4480                                                  | 4580 | XXXX XXXX                                                        | սսսս սսսս                       | -uuu uuuu |

| RXF9EIDH <sup>(6)</sup>  | 2480               | 2580 | 4480                                                  | 4580 | XXXX XXXX                                                        | սսսս սսսս                       | -uuu uuuu |

| RXF9SIDL <sup>(6)</sup>  | 2480               | 2580 | 4480                                                  | 4580 | XXX- X-XX                                                        | uuu- u-uu                       | -uuu uuuu |

| RXF9SIDH <sup>(6)</sup>  | 2480               | 2580 | 4480                                                  | 4580 | XXXX XXXX                                                        | սսսս սսսս                       | -uuu uuuu |

| RXF8EIDL <sup>(6)</sup>  | 2480               | 2580 | 4480                                                  | 4580 | XXXX XXXX                                                        | սսսս սսսս                       | -uuu uuuu |

| RXF8EIDH <sup>(6)</sup>  | 2480               | 2580 | 4480                                                  | 4580 | XXXX XXXX                                                        | սսսս սսսս                       | -uuu uuuu |

| RXF8SIDL <sup>(6)</sup>  | 2480               | 2580 | 4480                                                  | 4580 | xxx- x-xx                                                        | uuu- u-uu                       | -uuu uuuu |

| RXF8SIDH <sup>(6)</sup>  | 2480               | 2580 | 4480                                                  | 4580 | XXXX XXXX                                                        | սսսս սսսս                       | -uuu uuuu |

| RXF7EIDL <sup>(6)</sup>  | 2480               | 2580 | 4480                                                  | 4580 | XXXX XXXX                                                        | սսսս սսսս                       | -uuu uuuu |

| RXF7EIDH <sup>(6)</sup>  | 2480               | 2580 | 4480                                                  | 4580 | XXXX XXXX                                                        | սսսս սսսս                       | -uuu uuuu |

| RXF7SIDL <sup>(6)</sup>  | 2480               | 2580 | 4480                                                  | 4580 | xxx- x-xx                                                        | uuu- u-uu                       | -uuu uuuu |

| RXF7SIDH <sup>(6)</sup>  | 2480               | 2580 | 4480                                                  | 4580 | XXXX XXXX                                                        | սսսս սսսս                       | -uuu uuuu |

| RXF6EIDL <sup>(6)</sup>  | 2480               | 2580 | 4480                                                  | 4580 | XXXX XXXX                                                        | սսսս սսսս                       | -uuu uuuu |

| RXF6EIDH <sup>(6)</sup>  | 2480               | 2580 | 4480                                                  | 4580 | XXXX XXXX                                                        | սսսս սսսս                       | -uuu uuuu |

| RXF6SIDL <sup>(6)</sup>  | 2480               | 2580 | 4480                                                  | 4580 | xxx- x-xx                                                        | uuu- u-uu                       | -uuu uuuu |

| RXF6SIDH <sup>(6)</sup>  | 2480               | 2580 | 4480                                                  | 4580 | XXXX XXXX                                                        | นนนน นนนน                       | -uuu uuuu |

|                          |                    | l    | I                                                     |      |                                                                  |                                 | I         |

### TABLE 5-4: INITIALIZATION CONDITIONS FOR ALL REGISTERS (CONTINUED)

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition. Shaded cells indicate conditions do not apply for the designated device.

Note 1: One or more bits in the INTCONx or PIRx registers will be affected (to cause wake-up).

2: When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the PC is loaded with the interrupt vector (0008h or 0018h).

- **3:** When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the TOSU, TOSH and TOSL are updated with the current value of the PC. The STKPTR is modified to point to the next location in the hardware stack.

- 4: See Table 5-3 for Reset value for specific condition.

- **5:** Bits 6 and 7 of PORTA, LATA and TRISA are enabled, depending on the oscillator mode selected. When not enabled as PORTA pins, they are disabled and read '0'.

- 6: This register reads all '0's until ECAN™ technology is set up in Mode 1 or Mode 2.

## REGISTER 7-1: EECON1: DATA EEPROM CONTROL REGISTER 1

| R/W-x | R/W-x | U-0 | R/W-0 | R/W-x                | R/W-0 | R/S-0 | R/S-0 |

|-------|-------|-----|-------|----------------------|-------|-------|-------|

| EEPGD | CFGS  | —   | FREE  | WRERR <sup>(1)</sup> | WREN  | WR    | RD    |

| bit 7 |       |     |       |                      |       |       | bit 0 |

| Legend:           | S = Settable bit |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| hit 7 | EEDCD: Flack Bragger at Data FERROM Mamary Salast hit                                                                                                                                                                                                                   |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 7 | EEPGD: Flash Program or Data EEPROM Memory Select bit                                                                                                                                                                                                                   |

|       | 1 = Access Flash program memory<br>0 = Access data EEPROM memory                                                                                                                                                                                                        |

| 1.1.0 | -                                                                                                                                                                                                                                                                       |

| bit 6 | CFGS: Flash Program/Data EEPROM or Configuration Select bit                                                                                                                                                                                                             |

|       | 1 = Access Configuration registers                                                                                                                                                                                                                                      |

|       | 0 = Access Flash program or data EEPROM memory                                                                                                                                                                                                                          |

| bit 5 | Unimplemented: Read as '0'                                                                                                                                                                                                                                              |

| bit 4 | FREE: Flash Row Erase Enable bit                                                                                                                                                                                                                                        |

|       | <ul> <li>1 = Erase the program memory row addressed by TBLPTR on the next WR command (cleared by<br/>completion of erase operation)</li> </ul>                                                                                                                          |

|       | 0 = Perform write only                                                                                                                                                                                                                                                  |

| bit 3 | WRERR: Flash Program/Data EEPROM Error Flag bit <sup>(1)</sup>                                                                                                                                                                                                          |

|       | <ul> <li>1 = A write operation is prematurely terminated (any Reset during self-timed programming in normal<br/>operation or an improper write attempt)</li> </ul>                                                                                                      |

|       | 0 = The write operation completed                                                                                                                                                                                                                                       |

| bit 2 | WREN: Flash Program/Data EEPROM Write Enable bit                                                                                                                                                                                                                        |

|       | 1 = Allows write cycles to Flash program/data EEPROM                                                                                                                                                                                                                    |

|       | 0 = Inhibits write cycles to Flash program/data EEPROM                                                                                                                                                                                                                  |

| bit 1 | WR: Write Control bit                                                                                                                                                                                                                                                   |

|       | <ul> <li>1 = Initiates a data EEPROM erase/write cycle or a program memory erase cycle or write cycle<br/>(The operation is self-timed and the bit is cleared by hardware once write is complete.<br/>The WR bit can only be set (not cleared) in software.)</li> </ul> |

|       | 0 = Write cycle to the EEPROM is complete                                                                                                                                                                                                                               |

| bit 0 | RD: Read Control bit                                                                                                                                                                                                                                                    |

|       | 1 = Initiates an EEPROM read (Read takes one cycle. RD is cleared in hardware. The RD bit can only                                                                                                                                                                      |

|       | be set (not cleared) in software. RD bit cannot be set when EEPGD = 1 or CFGS = 1.)<br>0 = Does not initiate an EEPROM read                                                                                                                                             |

|       |                                                                                                                                                                                                                                                                         |

**Note 1:** When a WRERR occurs, the EEPGD and CFGS bits are not cleared. This allows tracing of the error condition.

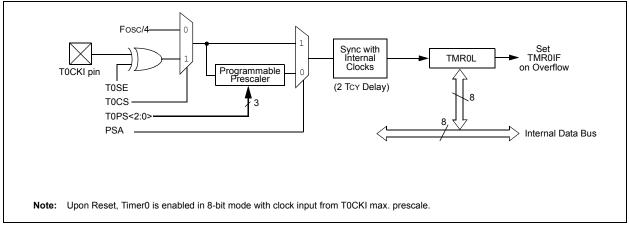

## 12.1 Timer0 Operation

Timer0 can operate as either a timer or a counter; the mode is selected by clearing the T0CS bit (T0CON<5>). In Timer mode, the module increments on every clock by default unless a different prescaler value is selected (see **Section 12.3 "Prescaler"**). If the TMR0 register is written to, the increment is inhibited for the following two instruction cycles. The user can work around this by writing an adjusted value to the TMR0 register.

The Counter mode is selected by setting the T0CS bit (= 1). In Counter mode, Timer0 increments either on every rising or falling edge of pin, RA4/T0CKI. The incrementing edge is determined by the Timer0 Source Edge Select bit, T0SE (T0CON<4>); clearing this bit selects the rising edge. Restrictions on the external clock input are discussed below.

An external clock source can be used to drive Timer0; however, it must meet certain requirements to ensure that the external clock can be synchronized with the internal phase clock (Tosc). There is a delay between synchronization and the onset of incrementing the timer/counter.

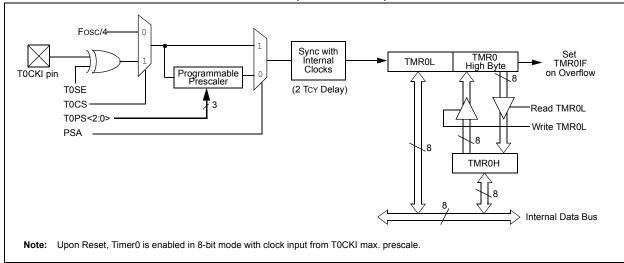

### 12.2 Timer0 Reads and Writes in 16-Bit Mode

TMR0H is not the actual high byte of Timer0 in 16-bit mode; it is actually a buffered version of the real high byte of Timer0, which is not directly readable nor writable (refer to Figure 12-2). TMR0H is updated with the contents of the high byte of Timer0 during a read of TMR0L. This provides the ability to read all 16 bits of Timer0 without having to verify that the read of the high and low byte were valid, due to a rollover between successive reads of the high and low byte.

Similarly, a write to the high byte of Timer0 must also take place through the TMR0H Buffer register. The high byte is updated with the contents of TMR0H when a write occurs to TMR0L. This allows all 16 bits of Timer0 to be updated at once.

## REGISTER 17-2: ECCP1DEL: ECCP PWM DEAD-BAND DELAY REGISTER

| R/W-0 | R/W-0               | R/W-0               | R/W-0               | R/W-0               | R/W-0               | R/W-0               | R/W-0               |

|-------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|

| PRSEN | PDC6 <sup>(1)</sup> | PDC5 <sup>(1)</sup> | PDC4 <sup>(1)</sup> | PDC3 <sup>(1)</sup> | PDC2 <sup>(1)</sup> | PDC1 <sup>(1)</sup> | PDC0 <sup>(1)</sup> |

| bit 7 |                     |                     |                     |                     |                     |                     | bit 0               |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | l as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 7   | PRSEN: PWM Restart Enable bit                                                                                                                          |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <ul> <li>1 = Upon auto-shutdown, the ECCPASE bit clears automatically once the shutdown event goes away;<br/>the PWM restarts automatically</li> </ul> |

|         | 0 = Upon auto-shutdown, ECCPASE must be cleared in software to restart the PWM                                                                         |

| bit 6-0 | PDC<6:0>: PWM Delay Count bits <sup>(1)</sup>                                                                                                          |

|         | Delay time, in number of Fosc/4 (4 * Tosc) cycles, between the scheduled and actual time for a PWM signal to transition to active.                     |

## REGISTER 17-3: ECCP1AS: ECCP AUTO-SHUTDOWN CONTROL REGISTER<sup>(1)</sup>

| R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0  | R/W-0  | R/W-0                 | R/W-0                 |

|---------|---------|---------|---------|--------|--------|-----------------------|-----------------------|

| ECCPASE | ECCPAS2 | ECCPAS1 | ECCPAS0 | PSSAC1 | PSSAC0 | PSSBD1 <sup>(1)</sup> | PSSBD0 <sup>(1)</sup> |

| bit 7   |         |         |         |        |        |                       | bit 0                 |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 7   | ECCPASE: ECCP Auto-Shutdown Event Status bit                                                                                                                                                                                          |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <ul> <li>1 = A shutdown event has occurred; ECCP outputs are in shutdown state</li> <li>0 = ECCP outputs are operating</li> </ul>                                                                                                     |

| bit 6-4 | ECCPAS<2:0>: ECCP Auto-Shutdown Source Select bits                                                                                                                                                                                    |

|         | <pre>111 = RB0 or Comparator 1 or Comparator 2 110 = RB0 or Comparator 2 101 = RB0 or Comparator 1 100 = RB0 011 = Either Comparator 1 or 2 010 = Comparator 2 output 001 = Comparator 1 output 000 = Auto-shutdown is disabled</pre> |

| bit 3-2 | PSSAC<1:0>: Pins, A and C, Shutdown State Control bits                                                                                                                                                                                |

|         | <ul> <li>1x = Pins, A and C, tri-state (PIC18F4X80 devices)</li> <li>01 = Drive Pins, A and C, to '1'</li> <li>00 = Drive Pins, A and C, to '0'</li> </ul>                                                                            |

| bit 1-0 | PSSBD<1:0>: Pins, B and D, Shutdown State Control bits <sup>(1)</sup>                                                                                                                                                                 |

|         | <ul> <li>1x = Pins, B and D, tri-state</li> <li>01 = Drive Pins, B and D, to '1'</li> <li>00 = Drive Pins, B and D, to '0'</li> </ul>                                                                                                 |

| Note 1: | Reserved on PIC18F2X80 devices; maintain these bits clear.                                                                                                                                                                            |

© 2009 Microchip Technology Inc.

### 18.4.3.2 Reception

When the R/W bit of the address byte is clear and an address match occurs, the R/W bit of the SSPSTAT register is cleared. The received address is loaded into the SSPBUF register and the SDA line is held low (ACK).

When the address byte overflow condition exists, then the no Acknowledge (ACK) pulse is given. An overflow condition is defined as either bit, BF (SSPSTAT<0>), is set, or bit, SSPOV (SSPCON1<6>), is set.

An MSSP interrupt is generated for each data transfer byte. Flag bit, SSPIF (PIR1<3>), must be cleared in software. The SSPSTAT register is used to determine the status of the byte.

If SEN is enabled (SSPCON2<0> = 1), RC3/SCK/SCL will be held low (clock stretch) following each data transfer. The clock must be released by setting bit, CKP (SSPCON<4>). See **Section 18.4.4** "Clock **Stretching**" for more details.

### 18.4.3.3 Transmission

When the R/W bit of the incoming address byte is set and an address match occurs, the R/W bit of the SSPSTAT register is set. The received address is loaded into the SSPBUF register. The ACK pulse will be sent on the ninth bit and pin RC3/SCK/SCL is held low regardless of SEN (see Section 18.4.4 "Clock Stretching" for more details). By stretching the clock, the master will be unable to assert another clock pulse until the slave is done preparing the transmit data. The transmit data must be loaded into the SSPBUF register which also loads the SSPSR register. Then, the RC3/ SCK/SCL pin should be enabled by setting bit, CKP (SSPCON1<4>). The eight data bits are shifted out on the falling edge of the SCL input. This ensures that the SDA signal is valid during the SCL high time (Figure 18-9).

The ACK pulse from the master-receiver is latched on the rising edge of the ninth SCL input pulse. If the SDA line is high (not ACK), then the data transfer is complete. In this case, when the ACK is latched by the slave, the slave logic is reset and the slave monitors for another occurrence of the Start bit. If the SDA line was low (ACK), the next transmit data must be loaded into the SSPBUF register. Again, pin, RC3/SCK/SCL, must be enabled by setting bit, CKP.

An MSSP interrupt is generated for each data transfer byte. The SSPIF bit must be cleared in software and the SSPSTAT register is used to determine the status of the byte. The SSPIF bit is set on the falling edge of the ninth clock pulse.

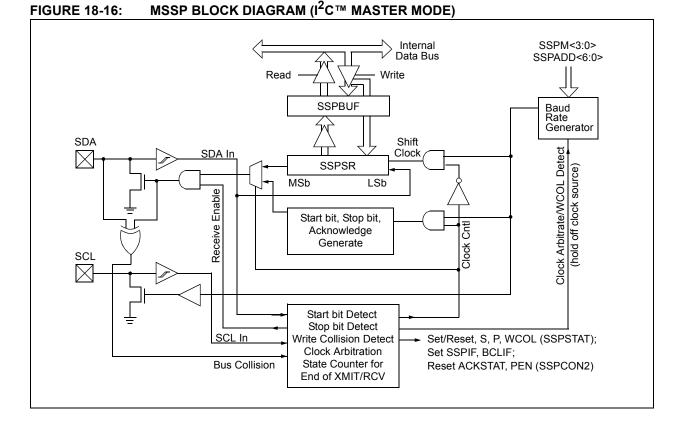

#### 18.4.6 MASTER MODE

Master mode is enabled by setting and clearing the appropriate SSPM bits in SSPCON1 and by setting the SSPEN bit. In Master mode, the SCL and SDA lines are manipulated by the MSSP hardware.

Master mode of operation is supported by interrupt generation on the detection of the Start and Stop conditions. The Stop (P) and Start (S) bits are cleared from a Reset or when the MSSP module is disabled. Control of the  $I^2C$  bus may be taken when the P bit is set or the bus is Idle, with both the S and P bits clear.

In Firmware Controlled Master mode, user code conducts all  $I^2C$  bus operations based on Start and Stop bit conditions.

Once Master mode is enabled, the user has six options.

- 1. Assert a Start condition on SDA and SCL.

- 2. Assert a Repeated Start condition on SDA and SCL.

- 3. Write to the SSPBUF register initiating transmission of data/address.

- 4. Configure the I<sup>2</sup>C port to receive data.

- 5. Generate an Acknowledge condition at the end of a received byte of data.

- 6. Generate a Stop condition on SDA and SCL.

**Note:** The MSSP module, when configured in I<sup>2</sup>C Master mode, does not allow queueing of events. For instance, the user is not allowed to initiate a Start condition and immediately write the SSPBUF register to initiate transmission before the Start condition is complete. In this case, the SSPBUF will not be written to and the WCOL bit will be set, indicating that a write to the SSPBUF did not occur.

The following events will cause the MSSP Interrupt Flag bit, SSPIF, to be set (MSSP interrupt, if enabled):

- · Start condition

- Stop condition

- · Data transfer byte transmitted/received

- · Acknowledge transmitted

- · Repeated Start

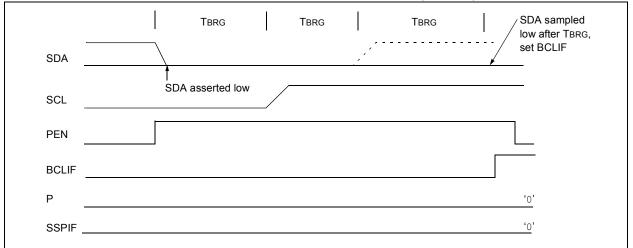

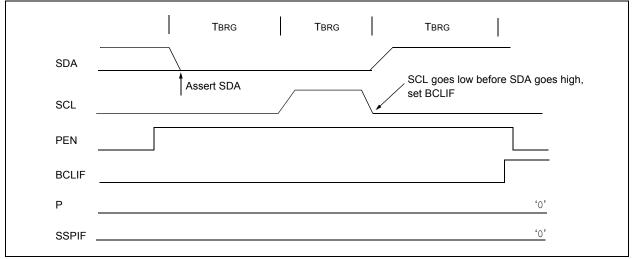

### 18.4.17.3 Bus Collision During a Stop Condition

Bus collision occurs during a Stop condition if:

- a) After the SDA pin has been deasserted and allowed to float high, SDA is sampled low after the BRG has timed out.

- b) After the SCL pin is deasserted, SCL is sampled low before SDA goes high.

The Stop condition begins with SDA asserted low. When SDA is sampled low, the SCL pin is allowed to float. When the pin is sampled high (clock arbitration), the Baud Rate Generator is loaded with SSPADD<6:0> and counts down to 0. After the BRG times out, SDA is sampled. If SDA is sampled low, a bus collision has occurred. This is due to another master attempting to drive a data '0' (Figure 18-31). If the SCL pin is sampled low before SDA is allowed to float high, a bus collision occurs. This is another case of another master attempting to drive a data '0' (Figure 18-32).

#### FIGURE 18-31: BUS COLLISION DURING A STOP CONDITION (CASE 1)

### FIGURE 18-32: BUS COLLISION DURING A STOP CONDITION (CASE 2)

### 19.2.4 AUTO-WAKE-UP ON SYNC BREAK CHARACTER

During Sleep mode, all clocks to the EUSART are suspended. Because of this, the Baud Rate Generator is inactive and a proper byte reception cannot be performed. The auto-wake-up feature allows the controller to wake-up due to activity on the RX/DT line, while the EUSART is operating in Asynchronous mode.

The auto-wake-up feature is enabled by setting the WUE bit (BAUDCON<1>). Once set, the typical receive sequence on RX/DT is disabled and the EUSART remains in an Idle state, monitoring for a wake-up event independent of the CPU mode. A wake-up event consists of a high-to-low transition on the RX/DT line. (This coincides with the start of a Sync Break or a Wake-up Signal character for the LIN/J2602 protocol.)

Following a wake-up event, the module generates an RCIF interrupt. The interrupt is generated synchronously to the Q clocks in normal operating modes (Figure 19-8) and asynchronously, if the device is in Sleep mode (Figure 19-9). The interrupt condition is cleared by reading the RCREG register.

The WUE bit is automatically cleared once a low-to-high transition is observed on the RX line following the wake-up event. At this point, the EUSART module is in Idle mode and returns to normal operation. This signals to the user that the Sync Break event is over.

#### 19.2.4.1 Special Considerations Using Auto-Wake-up

Since auto-wake-up functions by sensing rising edge transitions on RX/DT, information with any state changes before the Stop bit may signal a false

End-of-Character (EOC) and cause data or framing errors. To work properly, therefore, the initial character in the transmission must be all '0's. This can be 00h (8 bits) for standard RS-232 devices or 000h (12 bits) for LIN/J2602 bus.

Oscillator start-up time must also be considered, especially in applications using oscillators with longer start-up intervals (i.e., XT or HS mode). The Sync Break (or Wake-up Signal) character must be of sufficient length and be followed by a sufficient interval to allow enough time for the selected oscillator to start and provide proper initialization of the EUSART.

## 19.2.4.2 Special Considerations Using the WUE Bit

The timing of WUE and RCIF events may cause some confusion when it comes to determining the validity of received data. As noted, setting the WUE bit places the EUSART in an Idle mode. The wake-up event causes a receive interrupt by setting the RCIF bit. The WUE bit is cleared after this when a rising edge is seen on RX/DT. The interrupt condition is then cleared by reading the RCREG register. Ordinarily, the data in RCREG will be dummy data and should be discarded.

The fact that the WUE bit has been cleared (or is still set) and the RCIF flag is set should not be used as an indicator of the integrity of the data in RCREG. Users should consider implementing a parallel method in firmware to verify received data integrity.

To assure that no actual data is lost, check the RCIDL bit to verify that a receive operation is not in process. If a receive operation is not occurring, the WUE bit may then be set just prior to entering the Sleep mode.

## FIGURE 19-8: AUTO-WAKE-UP BIT (WUE) TIMINGS DURING NORMAL OPERATION

| - OSC (               | - MANAL                                                  | NGC AL                                    | UNDALAN (* 1917)        | UNUALAB                                | NYNAIN. | agaan | uaupunun                               | .J.M.D.C                               | 9.9. <u>9</u> .9       | naaqaa         | .: A. I. |

|-----------------------|----------------------------------------------------------|-------------------------------------------|-------------------------|----------------------------------------|---------|-------|----------------------------------------|----------------------------------------|------------------------|----------------|----------|

|                       | ्रे विषे त्वरे                                           | eriese                                    |                         |                                        |         | 3     |                                        |                                        |                        | 200MG 8003     | 385      |

| 898 SE <sup>3</sup> - | - 5                                                      | ·····                                     | ····/                   | ···· · · · · · · · · · · · · · · · · · |         |       | ······································ |                                        | innernen p.<br>5. Spen |                |          |

|                       | - 2-<br>                                                 |                                           |                         |                                        |         |       |                                        |                                        | 1. 1                   | · · ·          |          |

| XAN Ane -             | - 1                                                      | ·····                                     | *********************** |                                        | anna    |       |                                        |                                        | aar i                  | ······         |          |

|                       | 2                                                        | *                                         | ·                       | 3 2                                    | 4.1     | No. 1 |                                        |                                        | e - 4                  | 4              |          |

| SSC38                 | - k<br>- generalen en e | ,<br>,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, |                         | ; ; ;<br>                              |         |       | ······································ | ······································ | ······                 | ······         |          |

|                       |                                                          | -                                         | -                       |                                        |         |       | — Ciperes de                           | e ožeste                               | -86 A.Y.C              | 283 <u>"</u> , |          |

|                       | 100                                                      | 1                                         | 1 A                     |                                        |         |       |                                        |                                        |                        |                |          |

## FIGURE 19-9: AUTO-WAKE-UP BIT (WUE) TIMINGS DURING SLEEP

## 23.0 HIGH/LOW-VOLTAGE DETECT (HLVD)

PIC18F2480/2580/4480/4580 devices have a High/Low-Voltage Detect module (HLVD). This is a programmable circuit that allows the user to specify both a device voltage trip point and the direction of change from that point. If the device experiences an excursion past the trip point in that direction, an interrupt flag is set. If the interrupt is enabled, the program execution will branch to the interrupt vector address and the software can then respond to the interrupt.

The High/Low-Voltage Detect Control register (Register 23-1) completely controls the operation of the HLVD module. This allows the circuitry to be "turned off" by the user under software control, which minimizes the current consumption for the device.

The block diagram for the HLVD module is shown in Figure 23-1.

### REGISTER 23-1: HLVDCON: HIGH/LOW-VOLTAGE DETECT CONTROL REGISTER

| R/W-0         | U-0                                                                    | R-0                                                                                                         | R/W-0         | R/W-0                              | R/W-1                 | R/W-0                 | R/W-1                 |  |  |  |

|---------------|------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|---------------|------------------------------------|-----------------------|-----------------------|-----------------------|--|--|--|

| VDIRMAG       |                                                                        | IRVST                                                                                                       | HLVDEN        | HLVDL3 <sup>(1)</sup>              | HLVDL2 <sup>(1)</sup> | HLVDL1 <sup>(1)</sup> | HLVDL0 <sup>(1)</sup> |  |  |  |

| bit 7         |                                                                        |                                                                                                             |               |                                    |                       |                       | bit 0                 |  |  |  |

|               |                                                                        |                                                                                                             |               |                                    |                       |                       |                       |  |  |  |

| Legend:       |                                                                        |                                                                                                             |               |                                    |                       |                       |                       |  |  |  |

| R = Readable  |                                                                        | W = Writable bit                                                                                            |               | U = Unimplemented bit, read as '0' |                       |                       |                       |  |  |  |

| -n = Value at | POR                                                                    | '1' = Bit is set                                                                                            |               | '0' = Bit is cle                   | ared                  | x = Bit is unknown    |                       |  |  |  |

| bit 7         |                                                                        | oltage Directio                                                                                             | n Magnitude ( | Select hit                         |                       |                       |                       |  |  |  |

| Sit           |                                                                        | •                                                                                                           | •             |                                    | oint (HLVDL<3:0       | )>)                   |                       |  |  |  |

|               |                                                                        |                                                                                                             | •             |                                    | point (HLVDL<         | ,                     |                       |  |  |  |

| bit 6         | Unimplemen                                                             | ted: Read as '                                                                                              | 0'            |                                    |                       |                       |                       |  |  |  |

| bit 5         | IRVST: Intern                                                          | al Reference V                                                                                              | oltage Stable | Flag bit                           |                       |                       |                       |  |  |  |

|               | 1 = Indicates                                                          | 1 = Indicates that the voltage detect logic will generate the interrupt flag at the specified voltage range |               |                                    |                       |                       |                       |  |  |  |

|               |                                                                        |                                                                                                             |               | will not generation of be enabled  | ate the interrup<br>I | t flag at the spe     | ecified voltage       |  |  |  |

| bit 4         | HLVDEN: Hig                                                            | h/Low-Voltage                                                                                               | Detect Powe   | r Enable bit                       |                       |                       |                       |  |  |  |

|               | 1 = HLVD enabled                                                       |                                                                                                             |               |                                    |                       |                       |                       |  |  |  |

|               | 0 = HLVD dis                                                           |                                                                                                             |               |                                    |                       |                       |                       |  |  |  |

| bit 3-0       | HLVDL<3:0>: High/Low-Voltage Detection Limit bits <sup>(1)</sup>       |                                                                                                             |               |                                    |                       |                       |                       |  |  |  |

|               | 1111 = External analog input is used (input comes from the HLVDIN pin) |                                                                                                             |               |                                    |                       |                       |                       |  |  |  |

|               | 1110 = 4.48V-4.69V<br>1101 = 4.23V-4.43V                               |                                                                                                             |               |                                    |                       |                       |                       |  |  |  |

|               | 1101 = 4.23v - 4.43v<br>1100 = 4.01V - 4.20V                           |                                                                                                             |               |                                    |                       |                       |                       |  |  |  |

|               | 1011 <b>= 3.81V</b>                                                    | ′-3.99V                                                                                                     |               |                                    |                       |                       |                       |  |  |  |

|               | 1010 = 3.63V                                                           |                                                                                                             |               |                                    |                       |                       |                       |  |  |  |

|               |                                                                        | 1001 = 3.46V-3.63V<br>1000 = 3.31V-3.47V                                                                    |               |                                    |                       |                       |                       |  |  |  |

|               | 0111 = 3.05V                                                           |                                                                                                             |               |                                    |                       |                       |                       |  |  |  |

|               | 0110 = 2.82V                                                           |                                                                                                             |               |                                    |                       |                       |                       |  |  |  |

|               | 0101 = 2.72V                                                           | ′-2.85V                                                                                                     |               |                                    |                       |                       |                       |  |  |  |

|               | 0100 = 2.54V                                                           |                                                                                                             |               |                                    |                       |                       |                       |  |  |  |

|               | 0011 = 2.38V                                                           |                                                                                                             |               |                                    |                       |                       |                       |  |  |  |

|               | 0010 = 2.31V<br>0001 = 2.18V                                           |                                                                                                             |               |                                    |                       |                       |                       |  |  |  |

|               | 00001 = 2.18V<br>0000 = 2.12V                                          | -                                                                                                           |               |                                    |                       |                       |                       |  |  |  |

**Note 1:** HLVDL<3:0> modes that result in a trip point below the valid operating voltage of the device are not tested.

### 24.2 CAN Module Registers

Note: Not all CAN registers are available in the Access Bank.

There are many control and data registers associated with the CAN module. For convenience, their descriptions have been grouped into the following sections:

- · Control and Status Registers

- Dedicated Transmit Buffer Registers

- · Dedicated Receive Buffer Registers

- · Programmable TX/RX and Auto RTR Buffers

- Baud Rate Control Registers

- I/O Control Register

- · Interrupt Status and Control Registers

Detailed descriptions of each register and their usage are described in the following sections.

#### 24.2.1 CAN CONTROL AND STATUS REGISTERS

The registers described in this section control the overall operation of the CAN module and show its operational status.

## REGISTER 24-13: RXB0CON: RECEIVE BUFFER 0 CONTROL REGISTER (CONTINUED)

| bit 2 | Mode 0:<br><b>RXB0DBEN:</b> Receive Buffer 0 Double-Buffer Enable bit                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul> <li>1 = Receive Buffer 0 overflow will write to Receive Buffer 1</li> <li>0 = No Receive Buffer 0 overflow to Receive Buffer 1</li> </ul>                                                                                                                                                                                                                                                                                                                                                                              |

|       | Mode 1, 2:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|       | <b>FILHIT2:</b> Filter Hit bit 2<br>This bit combines with other bits to form filter acceptance bits<4:0>.                                                                                                                                                                                                                                                                                                                                                                                                                  |

| bit 1 | <u>Mode 0:</u><br>JTOFF: Jump Table Offset bit (read-only copy of RXB0DBEN) <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|       | <ul> <li>1 = Allows jump table offset between 6 and 7</li> <li>0 = Allows jump table offset between 1 and 0</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                      |

|       | Mode 1, 2:<br><b>FILHIT1:</b> Filter Hit bit 1<br>This bit combines with other bits to form filter acceptance bits<4:0>.                                                                                                                                                                                                                                                                                                                                                                                                    |

| bit 0 | Mode 0:         FILHIT0: Filter Hit bit 0         This bit indicates which acceptance filter enabled the message reception into Receive Buffer 0.         1 = Acceptance Filter 1 (RXF1)         0 = Acceptance Filter 0 (RXF0)         Mode 1, 2:         FILHIT0: Filter Hit bit 0         This bit, in combination with FILHIT<4:1>, indicates which acceptance filter enabled the message reception into this receive buffer.         01111 = Acceptance Filter 15 (RXF15)         01110 = Acceptance Filter 14 (RXF14) |

|       | 00000 = Acceptance Filter 0 (RXF0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

- **Note 1:** This bit is set by the CAN module upon receiving a message and must be cleared by software after the buffer is read. As long as RXFUL is set, no new message will be loaded and buffer will be considered full. After clearing the RXFUL flag, the PIR3 bit, RXB0IF, can be cleared. If RXB0IF is cleared, but RXFUL is not cleared, then RXB0IF is set again.

- **2:** This bit allows same filter jump table for both RXB0CON and RXB1CON.

| R/W-0              | R/W-0                                                                                                                                                    | R/W-0                                                           | R/W-0        | R/W-0            | R/W-0            | R/W-0           | R/W-0  |

|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|--------------|------------------|------------------|-----------------|--------|

| FIL11_1            | FIL11_0                                                                                                                                                  | FIL10_1                                                         | FIL10_0      | FIL9_1           | FIL9_0           | FIL8_1          | FIL8_0 |

| bit 7              | ·                                                                                                                                                        |                                                                 |              |                  |                  |                 | bit 0  |

| Legend:            |                                                                                                                                                          |                                                                 |              |                  |                  |                 |        |

| R = Readabl        | e bit                                                                                                                                                    | W = Writable                                                    | bit          | U = Unimpler     | mented bit, read | d as '0'        |        |

| -n = Value at      | POR                                                                                                                                                      | '1' = Bit is set                                                |              | '0' = Bit is cle | eared            | x = Bit is unkr | iown   |

| bit 7-6<br>bit 5-4 | 11 = No mask<br>10 = Filter 15<br>01 = Acceptar<br>00 = Acceptar<br>FIL10_<1:0>:<br>11 = No mask<br>10 = Filter 15<br>01 = Acceptar                      | nce Mask 1<br>nce Mask 0<br>: Filter 10 Sele<br><<br>nce Mask 1 |              |                  |                  |                 |        |

| bit 3-2            | 00 = Acceptance Mask 0<br>FIL9_<1:0>: Filter 9 Select bits 1 and 0<br>11 = No mask<br>10 = Filter 15<br>01 = Acceptance Mask 1<br>00 = Acceptance Mask 0 |                                                                 |              |                  |                  |                 |        |

| bit 1-0            | FIL8_<1:0>: I<br>11 = No mask<br>10 = Filter 15<br>01 = Accepta<br>00 = Accepta                                                                          | nce Mask 1                                                      | bits 1 and 0 |                  |                  |                 |        |

## REGISTER 24-50: MSEL2: MASK SELECT REGISTER 2<sup>(1)</sup>

**Note 1:** This register is available in Mode 1 and 2 only.

## 24.10 Synchronization

To compensate for phase shifts between the oscillator frequencies of each of the nodes on the bus, each CAN controller must be able to synchronize to the relevant signal edge of the incoming signal. When an edge in the transmitted data is detected, the logic will compare the location of the edge to the expected time (Sync\_Seg). The circuit will then adjust the values of Phase Segment 1 and Phase Segment 2 as necessary. There are two mechanisms used for synchronization.

#### 24.10.1 HARD SYNCHRONIZATION

Hard synchronization is only done when there is a recessive to dominant edge during a bus Idle condition, indicating the start of a message. After hard synchronization, the bit time counters are restarted with Sync\_Seg. Hard synchronization forces the edge, which has occurred to lie within the synchronization segment of the restarted bit time. Due to the rules of synchronization, if a hard synchronization occurs, there will not be a resynchronization within that bit time.

#### 24.10.2 RESYNCHRONIZATION

As a result of resynchronization, Phase Segment 1 may be lengthened or Phase Segment 2 may be shortened. The amount of lengthening or shortening of the phase buffer segments has an upper bound given by the Synchronization Jump Width (SJW). The value of the SJW will be added to Phase Segment 1 (see Figure 24-6) or subtracted from Phase Segment 2 (see Figure 24-7). The SJW is programmable between 1 Tq and 4 Tq.

Clocking information will only be derived from recessive to dominant transitions. The property, that only a fixed maximum number of successive bits have the same value, ensures resynchronization to the bit stream during a frame. The phase error of an edge is given by the position of the edge relative to Sync\_Seg, measured in Tq. The phase error is defined in magnitude of Tq as follows:

- e = 0 if the edge lies within Sync\_Seg.

- e > 0 if the edge lies before the sample point.

- e < 0 if the edge lies after the sample point of the previous bit.

If the magnitude of the phase error is less than, or equal to, the programmed value of the Synchronization Jump Width, the effect of a resynchronization is the same as that of a hard synchronization.

If the magnitude of the phase error is larger than the Synchronization Jump Width and if the phase error is positive, then Phase Segment 1 is lengthened by an amount equal to the Synchronization Jump Width.

If the magnitude of the phase error is larger than the resynchronization jump width and if the phase error is negative, then Phase Segment 2 is shortened by an amount equal to the Synchronization Jump Width.

### 24.10.3 SYNCHRONIZATION RULES

- Only one synchronization within one bit time is allowed.

- An edge will be used for synchronization only if the value detected at the previous sample point (previously read bus value) differs from the bus value immediately after the edge.

- All other recessive to dominant edges fulfilling rules 1 and 2 will be used for resynchronization, with the exception that a node transmitting a dominant bit will not perform a resynchronization as a result of a recessive to dominant edge with a positive phase error.

| BNC                                                                                                                                                      | v                                                                    | Branch if                                                                                                                                                                                                                  | Not Overflo                      | w                                                         | BNZ                                                |                                        | Branch if                                                                              | Not Zero                                                    |                                 |                        |

|----------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|-----------------------------------------------------------|----------------------------------------------------|----------------------------------------|----------------------------------------------------------------------------------------|-------------------------------------------------------------|---------------------------------|------------------------|

| Synta                                                                                                                                                    | ax:                                                                  | BNOV n                                                                                                                                                                                                                     |                                  |                                                           | Syntax:                                            |                                        | BNZ n                                                                                  |                                                             |                                 |                        |

| Oper                                                                                                                                                     | ands:                                                                | $-128 \le n \le 127$                                                                                                                                                                                                       |                                  |                                                           | Operands                                           | $Operands: -128 \le n \le 127$         |                                                                                        |                                                             |                                 |                        |

| Oper                                                                                                                                                     | Operation: if Overflow bit is '0',<br>$(PC) + 2 + 2n \rightarrow PC$ |                                                                                                                                                                                                                            | Operation                        | ו:                                                        | if Zero bit is '0', (PC) + 2 + 2n $\rightarrow$ PC |                                        |                                                                                        |                                                             |                                 |                        |

| Statu                                                                                                                                                    | is Affected:                                                         | None                                                                                                                                                                                                                       |                                  |                                                           | Status Aff                                         | Status Affected: None                  |                                                                                        |                                                             |                                 |                        |

| Enco                                                                                                                                                     | oding:                                                               | 1110                                                                                                                                                                                                                       | 0101 nn:                         | nn nnnn                                                   | Encoding                                           | :                                      | 1110                                                                                   | 0001                                                        | nnnn                            | nnnn                   |

| Desc                                                                                                                                                     | cription:                                                            | If the Overf program wi                                                                                                                                                                                                    | low bit is '0', th<br>Il branch. | hen the                                                   | Descriptio                                         | on:                                    | If the Zero will branch.                                                               | -                                                           | en the p                        | orogram                |

|                                                                                                                                                          |                                                                      | The 2's complement number '2n' is<br>added to the PC. Since the PC will have<br>incremented to fetch the next<br>instruction, the new address will be<br>PC + 2 + 2n. This instruction is then a<br>two-cycle instruction. |                                  |                                                           |                                                    |                                        | The 2's cor<br>added to th<br>incremente<br>instruction,<br>PC + 2 + 2<br>two-cycle ir | e PC. Since<br>d to fetch th<br>the new ad<br>n. This instr | e the PO<br>ne next<br>Idress v | C will have<br>will be |

| Word                                                                                                                                                     | ls:                                                                  | 1                                                                                                                                                                                                                          |                                  |                                                           | Words:                                             |                                        | 1                                                                                      |                                                             |                                 |                        |

| Cycle                                                                                                                                                    | es:                                                                  | 1(2)                                                                                                                                                                                                                       |                                  |                                                           | Cycles:                                            |                                        | 1(2)                                                                                   |                                                             |                                 |                        |

|                                                                                                                                                          | ycle Activity:                                                       |                                                                                                                                                                                                                            |                                  |                                                           | Q Cycle                                            | Activity:                              |                                                                                        |                                                             |                                 |                        |

| lf Ju                                                                                                                                                    | Q1                                                                   | Q2                                                                                                                                                                                                                         | Q3                               | Q4                                                        | If Jump:                                           | Q1                                     | Q2                                                                                     | Q3                                                          |                                 | Q4                     |

|                                                                                                                                                          | Decode                                                               | Read literal<br>'n'                                                                                                                                                                                                        | Process<br>Data                  | Write to PC                                               | D                                                  | ecode                                  | Read literal<br>'n'                                                                    | Process<br>Data                                             | Wr                              | ite to PC              |

|                                                                                                                                                          | No                                                                   | No                                                                                                                                                                                                                         | No                               | No                                                        |                                                    | No                                     | No                                                                                     | No                                                          |                                 | No                     |

|                                                                                                                                                          | operation                                                            | operation                                                                                                                                                                                                                  | operation                        | operation                                                 | ор                                                 | eration                                | operation                                                                              | operation                                                   | n op                            | peration               |