Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 25MHz                                                                     |

| Connectivity               | CANbus, I <sup>2</sup> C, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                               |

| Number of I/O              | 36                                                                        |

| Program Memory Size        | 32KB (16K x 16)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 1.5K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                               |

| Data Converters            | A/D 11x10b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 44-VQFN Exposed Pad                                                       |

| Supplier Device Package    | 44-QFN (8x8)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f4580-e-ml |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| TABLE 5-4:               |      |         |        |      |                                    |      |                      |      |                   |  |  |  |

|--------------------------|------|---------|--------|------|------------------------------------|------|----------------------|------|-------------------|--|--|--|

| Register                 | Ар   | olicabl | e Devi | ces  | Power-on Reset,<br>Brown-out Reset |      | Reset,<br>struction, | -    | via WDT<br>errupt |  |  |  |

| B0EIDL <sup>(6)</sup>    | 2480 | 2580    | 4480   | 4580 | XXXX XXXX                          | սսսս | uuuu                 | uuuu | uuuu              |  |  |  |

| B0EIDH <sup>(6)</sup>    | 2480 | 2580    | 4480   | 4580 | XXXX XXXX                          | uuuu | uuuu                 | uuuu | uuuu              |  |  |  |

| B0SIDL <sup>(6)</sup>    | 2480 | 2580    | 4480   | 4580 | XXXX X-XX                          | uuuu | u-uu                 | uuuu | u-uu              |  |  |  |

| B0SIDH <sup>(6)</sup>    | 2480 | 2580    | 4480   | 4580 | XXXX XXXX                          | սսսս | นนนน                 | սսսս | uuuu              |  |  |  |

| B0CON <sup>(6)</sup>     | 2480 | 2580    | 4480   | 4580 | 0000 0000                          | 0000 | 0000                 | սսսս | uuuu              |  |  |  |

| TXBIE <sup>(6)</sup>     | 2480 | 2580    | 4480   | 4580 | 0 00                               | u    | uu                   | u    | uu                |  |  |  |

| BIE0 <sup>(6)</sup>      | 2480 | 2580    | 4480   | 4580 | 0000 0000                          | 0000 | 0000                 | սսսս | uuuu              |  |  |  |

| BSEL0 <sup>(6)</sup>     | 2480 | 2580    | 4480   | 4580 | 0000 00                            | 0000 | 00                   | uuuu | uu                |  |  |  |

| MSEL3 <sup>(6)</sup>     | 2480 | 2580    | 4480   | 4580 | 0000 0000                          | 0000 | 0000                 | uuuu | uuuu              |  |  |  |

| MSEL2 <sup>(6)</sup>     | 2480 | 2580    | 4480   | 4580 | 0000 0000                          | 0000 | 0000                 | uuuu | uuuu              |  |  |  |

| MSEL1 <sup>(6)</sup>     | 2480 | 2580    | 4480   | 4580 | 0000 0101                          | 0000 | 0101                 | սսսս | uuuu              |  |  |  |

| MSEL0 <sup>(6)</sup>     | 2480 | 2580    | 4480   | 4580 | 0101 0000                          | 0101 | 0000                 | սսսս | uuuu              |  |  |  |

| SDFLC <sup>(6)</sup>     | 2480 | 2580    | 4480   | 4580 | 0 0000                             | 0    | 0000                 | -u   | uuuu              |  |  |  |

| RXFCON1 <sup>(6)</sup>   | 2480 | 2580    | 4480   | 4580 | 0000 0000                          | 0000 | 0000                 | սսսս | uuuu              |  |  |  |

| RXFCON0 <sup>(6)</sup>   | 2480 | 2580    | 4480   | 4580 | 0000 0000                          | 0000 | 0000                 | սսսս | uuuu              |  |  |  |

| RXFBCON7 <sup>(6)</sup>  | 2480 | 2580    | 4480   | 4580 | 0000 0000                          | 0000 | 0000                 | սսսս | uuuu              |  |  |  |

| RXFBCON6 <sup>(6)</sup>  | 2480 | 2580    | 4480   | 4580 | 0000 0000                          | 0000 | 0000                 | սսսս | uuuu              |  |  |  |

| RXFBCON5 <sup>(6)</sup>  | 2480 | 2580    | 4480   | 4580 | 0000 0000                          | 0000 | 0000                 | սսսս | uuuu              |  |  |  |

| RXFBCON4 <sup>(6)</sup>  | 2480 | 2580    | 4480   | 4580 | 0000 0000                          | 0000 | 0000                 | սսսս | uuuu              |  |  |  |

| RXFBCON3 <sup>(6)</sup>  | 2480 | 2580    | 4480   | 4580 | 0000 0000                          | 0000 | 0000                 | սսսս | uuuu              |  |  |  |

| RXFBCON2 <sup>(6)</sup>  | 2480 | 2580    | 4480   | 4580 | 0001 0001                          | 0001 | 0001                 | uuuu | uuuu              |  |  |  |

| RXFBCON1 <sup>(6)</sup>  | 2480 | 2580    | 4480   | 4580 | 0001 0001                          | 0001 | 0001                 | սսսս | uuuu              |  |  |  |

| RXFBCON0 <sup>(6)</sup>  | 2480 | 2580    | 4480   | 4580 | 0000 0000                          | 0000 | 0000                 | սսսս | uuuu              |  |  |  |

| RXF15EIDL <sup>(6)</sup> | 2480 | 2580    | 4480   | 4580 | XXXX XXXX                          | սսսս | uuuu                 | uuuu | uuuu              |  |  |  |

| RXF15EIDH <sup>(6)</sup> | 2480 | 2580    | 4480   | 4580 | XXXX XXXX                          | uuuu | นนนน                 | սսսս | uuuu              |  |  |  |

| RXF15SIDL(6)             | 2480 | 2580    | 4480   | 4580 | XXX- X-XX                          | uuu- | u-uu                 | uuu- | u-uu              |  |  |  |

| RXF15SIDH <sup>(6)</sup> | 2480 | 2580    | 4480   | 4580 | XXXX XXXX                          | uuuu | นนนน                 | սսսս | uuuu              |  |  |  |

| RXF14EIDL <sup>(6)</sup> | 2480 | 2580    | 4480   | 4580 | XXXX XXXX                          | uuuu | นนนน                 | սսսս | uuuu              |  |  |  |

| RXF14EIDH <sup>(6)</sup> | 2480 | 2580    | 4480   | 4580 | XXXX XXXX                          | սսսս | uuuu                 | uuuu | uuuu              |  |  |  |

| RXF14SIDL <sup>(6)</sup> | 2480 | 2580    | 4480   | 4580 | xxx- x-xx                          | uuu- | u-uu                 | uuu- | u-uu              |  |  |  |

| RXF14SIDH <sup>(6)</sup> | 2480 | 2580    | 4480   | 4580 | XXXX XXXX                          | սսսս | uuuu                 | uuuu | uuuu              |  |  |  |

### TABLE 5-4: INITIALIZATION CONDITIONS FOR ALL REGISTERS (CONTINUED)

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition. Shaded cells indicate conditions do not apply for the designated device.

Note 1: One or more bits in the INTCONx or PIRx registers will be affected (to cause wake-up).

- 2: When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the PC is loaded with the interrupt vector (0008h or 0018h).

- **3:** When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the TOSU, TOSH and TOSL are updated with the current value of the PC. The STKPTR is modified to point to the next location in the hardware stack.

- 4: See Table 5-3 for Reset value for specific condition.

- **5:** Bits 6 and 7 of PORTA, LATA and TRISA are enabled, depending on the oscillator mode selected. When not enabled as PORTA pins, they are disabled and read '0'.

- 6: This register reads all '0's until ECAN<sup>™</sup> technology is set up in Mode 1 or Mode 2.

## TABLE 6-1:SPECIAL FUNCTION REGISTER MAP FOR<br/>PIC18F2480/2580/4480/4580 DEVICES (CONTINUED)

| ddress | Name     | Address | Name        | Address | Name        | Address | Name            |

|--------|----------|---------|-------------|---------|-------------|---------|-----------------|

| F7Fh   | _        | F5Fh    | CANCON_RO0  | F3Fh    | CANCON_RO2  | F1Fh    | RXM1EIDL        |

| F7Eh   | _        | F5Eh    | CANSTAT_RO0 | F3Eh    | CANSTAT_RO2 | F1Eh    | RXM1EIDH        |

| F7Dh   | _        | F5Dh    | RXB1D7      | F3Dh    | TXB1D7      | F1Dh    | RXM1SIDL        |

| F7Ch   | _        | F5Ch    | RXB1D6      | F3Ch    | TXB1D6      | F1Ch    | RXM1SIDH        |

| F7Bh   | _        | F5Bh    | RXB1D5      | F3Bh    | TXB1D5      | F1Bh    | RXM0EIDL        |

| F7Ah   | _        | F5Ah    | RXB1D4      | F3Ah    | TXB1D4      | F1Ah    | RXM0EIDH        |

| F79h   | _        | F59h    | RXB1D3      | F39h    | TXB1D3      | F19h    | <b>RXM0SIDL</b> |

| F78h   | _        | F58h    | RXB1D2      | F38h    | TXB1D2      | F18h    | RXM0SIDH        |

| F77h   | ECANCON  | F57h    | RXB1D1      | F37h    | TXB1D1      | F17h    | RXF5EIDL        |

| F76h   | TXERRCNT | F56h    | RXB1D0      | F36h    | TXB1D0      | F16h    | RXF5EIDH        |

| F75h   | RXERRCNT | F55h    | RXB1DLC     | F35h    | TXB1DLC     | F15h    | RXF5SIDL        |

| F74h   | COMSTAT  | F54h    | RXB1EIDL    | F34h    | TXB1EIDL    | F14h    | RXF5SIDH        |

| F73h   | CIOCON   | F53h    | RXB1EIDH    | F33h    | TXB1EIDH    | F13h    | RXF4EIDL        |

| F72h   | BRGCON3  | F52h    | RXB1SIDL    | F32h    | TXB1SIDL    | F12h    | RXF4EIDH        |

| F71h   | BRGCON2  | F51h    | RXB1SIDH    | F31h    | TXB1SIDH    | F11h    | RXF4SIDL        |

| F70h   | BRGCON1  | F50h    | RXB1CON     | F30h    | TXB1CON     | F10h    | RXF4SIDH        |

| F6Fh   | CANCON   | F4Fh    | CANCON_RO1  | F2Fh    | CANCON_RO3  | F0Fh    | RXF3EIDL        |

| F6Eh   | CANSTAT  | F4Eh    | CANSTAT_RO1 | F2Eh    | CANSTAT_RO3 | F0Eh    | RXF3EIDH        |

| F6Dh   | RXB0D7   | F4DH    | TXB0D7      | F2Dh    | TXB2D7      | F0Dh    | RXF3SIDL        |

| F6Ch   | RXB0D6   | F4Ch    | TXB0D6      | F2Ch    | TXB2D6      | F0Ch    | RXF3SIDH        |

| F6Bh   | RXB0D5   | F4Bh    | TXB0D5      | F2Bh    | TXB2D5      | F0Bh    | RXF2EIDL        |

| F6Ah   | RXB0D4   | F4Ah    | TXB0D4      | F2Ah    | TXB2D4      | F0Ah    | RXF2EIDH        |

| F69h   | RXB0D3   | F49h    | TXB0D3      | F29h    | TXB2D3      | F09h    | RXF2SIDL        |

| F68h   | RXB0D2   | F48h    | TXB0D2      | F28h    | TXB2D2      | F08h    | RXF2SIDH        |

| F67h   | RXB0D1   | F47h    | TXB0D1      | F27h    | TXB2D1      | F07h    | RXF1EIDL        |

| F66h   | RXB0D0   | F46h    | TXB0D0      | F26h    | TXB2D0      | F06h    | RXF1EIDH        |

| F65h   | RXB0DLC  | F45h    | TXB0DLC     | F25h    | TXB2DLC     | F05h    | RXF1SIDL        |

| F64h   | RXB0EIDL | F44h    | TXB0EIDL    | F24h    | TXB2EIDL    | F04h    | RXF1SIDH        |

| F63h   | RXB0EIDH | F43h    | TXB0EIDH    | F23h    | TXB2EIDH    | F03h    | RXF0EIDL        |

| F62h   | RXB0SIDL | F42h    | TXB0SIDL    | F22h    | TXB2SIDL    | F02h    | RXF0EIDH        |

| F61h   | RXB0SIDH | F41h    | TXB0SIDH    | F21h    | TXB2SIDH    | F01h    | RXF0SIDL        |

| F60h   | RXB0CON  | F40h    | TXB0CON     | F20h    | TXB2CON     | F00h    | RXF0SIDH        |

Note 1: Registers available only on PIC18F4X80 devices; otherwise, the registers read as '0'.

2: When any TX\_ENn bit in RX\_TX\_SELn is set, then the corresponding bit in this register has transmit properties.

3: This is not a physical register.

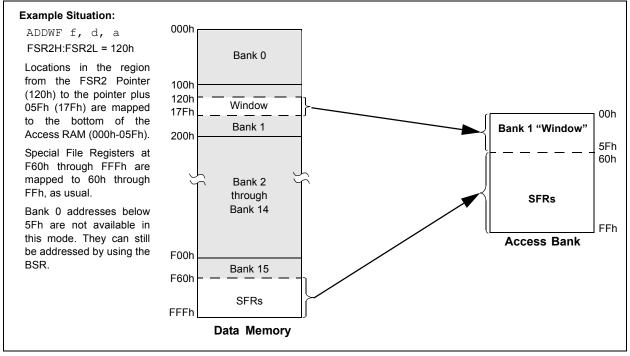

## 6.6.3 MAPPING THE ACCESS BANK IN INDEXED LITERAL OFFSET MODE

The use of Indexed Literal Offset Addressing mode effectively changes how the lower half of Access RAM (00h to 7Fh) is mapped. Rather than containing just the contents of the bottom half of Bank 0, this mode maps the contents from Bank 0 and a user-defined "window" that can be located anywhere in the data memory space. The value of FSR2 establishes the lower boundary of the addresses mapped into the window, while the upper boundary is defined by FSR2 plus 95 (5Fh). Addresses in the Access RAM above 5Fh are mapped as previously described (see **Section 6.3.2 "Access Bank**"). An example of Access Bank remapping in this addressing mode is shown in Figure 6-10.

Remapping of the Access Bank applies *only* to operations using the Indexed Literal Offset mode. Operations that use the BSR (Access RAM bit is '1') will continue to use Direct Addressing as before. Any indirect or indexed operation that explicitly uses any of the indirect file operands (including FSR2) will continue to operate as standard Indirect Addressing. Any instruction that uses the Access Bank, but includes a register address of greater than 05Fh, will use Direct Addressing and the normal Access Bank map.

## 6.6.4 BSR IN INDEXED LITERAL OFFSET MODE

Although the Access Bank is remapped when the extended instruction set is enabled, the operation of the BSR remains unchanged. Direct Addressing using the BSR to select the data memory bank operates in the same manner as previously described.

## FIGURE 6-10: REMAPPING THE ACCESS BANK WITH INDEXED LITERAL OFFSET ADDRESSING

| Mode 0     | R/W-0                                                            | R/W-0                                                             | R/W-0                                                | R/W-0                     | R/W-0                 | R/W-0                 | R/W-0         | R/W-0                  |

|------------|------------------------------------------------------------------|-------------------------------------------------------------------|------------------------------------------------------|---------------------------|-----------------------|-----------------------|---------------|------------------------|

| wode u     | IRXIE                                                            | WAKIE                                                             | ERRIE                                                | TXB2IE                    | TXB1IE <sup>(1)</sup> | TXB0IE <sup>(1)</sup> | RXB1IE        | RXB0IE                 |

|            | DAM 0                                                            | R/W-0                                                             | R/W-0                                                | R/W-0                     | R/W-0                 | R/W-0                 | R/W-0         | R/W-0                  |

| Mode 1,2   | R/W-0                                                            | WAKIE                                                             | ERRIE                                                | TXBnIE                    | TXB1IE <sup>(1)</sup> | TXB0IE <sup>(1)</sup> | R/W-0         | FIFOWMIE <sup>(1</sup> |

|            | bit 7                                                            | WARLE                                                             |                                                      | TADIIL                    | TABILE?               | INDUE: /              | RADIIL        | bit C                  |

|            |                                                                  |                                                                   |                                                      |                           |                       |                       |               |                        |

| Legend:    |                                                                  |                                                                   |                                                      |                           |                       |                       |               |                        |

| R = Reada  |                                                                  |                                                                   | W = Writabl                                          |                           | -                     | emented bit, r        |               |                        |

| -n = Value | at POR                                                           |                                                                   | '1' = Bit is s                                       | et                        | '0' = Bit is cl       | eared                 | x = Bit is ur | hknown                 |

| bit 7      | 1 = Enable i                                                     | invalid messa                                                     | ived Messag<br>age received i<br>age received        | nterrupt                  | nable bit             |                       |               |                        |

| bit 6      | 1 = Enable                                                       | bus activity w                                                    | y Wake-up Int<br>vake-up interre<br>vake-up interre  | upt                       | le bit                |                       |               |                        |

| bit 5      | 1 = Enable                                                       | N bus Error Ir<br>CAN bus erro<br>CAN bus erro                    |                                                      | le bit                    |                       |                       |               |                        |

| bit 4      | <b>TXB2IE:</b> CA<br>1 = Enable<br>0 = Disable                   | Transmit Buff                                                     | Buffer 2 Interr<br>er 2 interrupt<br>fer 2 interrupt | •                         | bit                   |                       |               |                        |

|            | <b>TXBnIE:</b> CA                                                | AN Transmit E<br>transmit buffe                                   | Buffer Interrup                                      | dividual inte             | it<br>rrupt is enable | ed by TXBIE a         | and BIE0      |                        |

| bit 3      | 1 = Enable                                                       | Transmit Buff                                                     | Buffer 1 Interr<br>er 1 interrupt<br>fer 1 interrupt |                           | bit <sup>(1)</sup>    |                       |               |                        |

| bit 2      | 1 = Enable                                                       | Transmit Buff                                                     | Buffer 0 Interr<br>er 0 interrupt<br>fer 0 interrupt |                           | bit <sup>(1)</sup>    |                       |               |                        |

| bit 1      | <b>RXB1IE:</b> CA                                                | Receive Buffe                                                     | Suffer 1 Interru                                     | ıpt Enable b              | it                    |                       |               |                        |

|            | <b>RXBnIE:</b> CA                                                | receive buffer                                                    | Buffer Interrup                                      | lividual inter            | t<br>rupt is enable   | d by BIE0             |               |                        |

| bit 0      | RXB0IE: CA<br>1 = Enable<br>0 = Disable<br>When CAN<br>Unimpleme | Receive Buffe<br>Receive Buff<br>is in Mode 1:<br>ented: Read a   | er 0 interrupt                                       | upt Enable b              | it                    |                       |               |                        |

|            | <b>FIFOWMIE:</b><br>1 = Enable                                   | <u>is in Mode 2:</u><br>FIFO Watern<br>FIFO waterm<br>FIFO waterm | mark Interrup<br>ark interrupt                       | t Enable bit <sup>(</sup> | 1)                    |                       |               |                        |

#### REGISTER 10-9: PIE3: PERIPHERAL INTERRUPT ENABLE REGISTER 3

Note 1: In CAN Mode 1 and 2, these bits are forced to '0'.

| TABLE 11-8: SUMMA | RY OF REGISTERS ASSOCIATED WITH PORTD |

|-------------------|---------------------------------------|

|-------------------|---------------------------------------|

| Name                    | Bit 7                      | Bit 6         | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   | Reset<br>Values<br>on Page: |  |

|-------------------------|----------------------------|---------------|---------|---------|---------|---------|---------|---------|-----------------------------|--|

| PORTD <sup>(1)</sup>    | RD7                        | RD6           | RD5     | RD4     | RD3     | RD2     | RD1     | RD0     | 58                          |  |

| LATD <sup>(1)</sup>     | LATD Output Latch Register |               |         |         |         |         |         |         |                             |  |

| TRISD <sup>(1)</sup>    | PORTD Dat                  | a Direction R | egister |         |         |         |         |         | 58                          |  |

| TRISE <sup>(1)</sup>    | IBF                        | OBF           | IBOV    | PSPMODE | _       | TRISE2  | TRISE1  | TRISE0  | 58                          |  |

| ECCP1CON <sup>(1)</sup> | EPWM1M1                    | EPWM1M0       | EDC1B1  | EDC1B0  | ECCP1M3 | ECCP1M2 | ECCP1M1 | ECCP1M0 | 57                          |  |

Legend: — = unimplemented, read as '0'. Shaded cells are not used by PORTD.

Note 1: These registers are available on PIC18F4X80 devices only.

## 15.2 Timer3 16-Bit Read/Write Mode

Timer3 can be configured for 16-bit reads and writes (see Figure 15-2). When the RD16 control bit (T3CON<7>) is set, the address for TMR3H is mapped to a buffer register for the high byte of Timer3. A read from TMR3L will load the contents of the high byte of Timer3 into the Timer3 High Byte Buffer register. This provides the user with the ability to accurately read all 16 bits of Timer1 without having to determine whether a read of the high byte, followed by a read of the low byte, has become invalid due to a rollover between reads.

A write to the high byte of Timer3 must also take place through the TMR3H Buffer register. The Timer3 high byte is updated with the contents of TMR3H when a write occurs to TMR3L. This allows a user to write all 16 bits to both the high and low bytes of Timer3 at once.

The high byte of Timer3 is not directly readable or writable in this mode. All reads and writes must take place through the Timer3 High Byte Buffer register.

Writes to TMR3H do not clear the Timer3 prescaler. The prescaler is only cleared on writes to TMR3L.

## 15.3 Using the Timer1 Oscillator as the Timer3 Clock Source

The Timer1 internal oscillator may be used as the clock source for Timer3. The Timer1 oscillator is enabled by setting the T1OSCEN (T1CON<3>) bit. To use it as the Timer3 clock source, the TMR3CS bit must also be set. As previously noted, this also configures Timer3 to increment on every rising edge of the oscillator source.

The Timer1 oscillator is described in Section 13.0 "Timer1 Module".

## 15.4 Timer3 Interrupt

The TMR3 register pair (TMR3H:TMR3L) increments from 0000h to FFFFh and overflows to 0000h. The Timer3 interrupt, if enabled, is generated on overflow and is latched in the interrupt flag bit, TMR3IF (PIR2<1>). This interrupt can be enabled or disabled by setting or clearing the Timer3 Interrupt Enable bit, TMR3IE (PIE2<1>).

## 15.5 Resetting Timer3 Using the CCP Special Event Trigger

If the ECCP1 module is configured to generate a special event trigger in Compare mode (ECCP1M<3:0> = 1011), this signal will reset Timer3. It will also start an A/D conversion if the A/D module is enabled (see Section 16.3.4 "Special Event Trigger" for more information.).

The module must be configured as either a timer or synchronous counter to take advantage of this feature. When used this way, the ECCPR2H:ECCPR2L register pair effectively becomes a period register for Timer3.

If Timer3 is running in Asynchronous Counter mode, the Reset operation may not work.

In the event that a write to Timer3 coincides with a Special Event Trigger from a CCP module, the write will take precedence.

Note: The special event triggers from the ECCP1 module will not set the TMR3IF interrupt flag bit (PIR1<0>).

| Name   | Bit 7      | Bit 6                  | Bit 5   | Bit 4   | Bit 3                 | Bit 2  | Bit 1  | Bit 0                  | Reset<br>Values<br>on Page: |

|--------|------------|------------------------|---------|---------|-----------------------|--------|--------|------------------------|-----------------------------|

| INTCON | GIE/GIEH   | PEIE/GIEL              | TMR0IE  | INT0IE  | RBIE                  | TMR0IF | INT0IF | RBIF                   | 55                          |

| PIR2   | OSCFIF     | CMIF <sup>(2)</sup>    | _       | EEIF    | BCLIF                 | HLVDIF | TMR3IF | ECCP1IF <sup>(2)</sup> | 58                          |

| PIE2   | OSCFIE     | CMIE <sup>(2)</sup>    | _       | EEIE    | BCLIE                 | HLVDIE | TMR3IE | ECCP1IE <sup>(2)</sup> | 58                          |

| IPR2   | OSCFIP     | CMIP <sup>(2)</sup>    | _       | EEIP    | BCLIP                 | HLVDIP | TMR3IP | ECCP1IP <sup>(2)</sup> | 57                          |

| TMR3L  | Timer3 Reg | gister Low Byt         | e       |         |                       |        |        |                        | 57                          |

| TMR3H  | Timer3 Reg | gister High By         | te      |         |                       |        |        |                        | 57                          |

| T1CON  | RD16       | T1RUN                  | T1CKPS1 | T1CKPS0 | T1OSCEN               | T1SYNC | TMR1CS | TMR10N                 | 56                          |

| T3CON  | RD16       | T3ECCP1 <sup>(1)</sup> | T3CKPS1 | T3CKPS0 | T3CCP1 <sup>(1)</sup> | T3SYNC | TMR3CS | TMR3ON                 | 57                          |

TABLE 15-1: REGISTERS ASSOCIATED WITH TIMER3 AS A TIMER/COUNTER

Legend: — = unimplemented, read as '0'. Shaded cells are not used by the Timer3 module.

Note 1: These bits are available in PIC18F4X80 devices only.

2: These bits are available in PIC18F4X80 devices and reserved in PIC18F2X80 devices.

#### R/W-0 R-0 R/W-0 R/W-0 R/W-0 R/W-0 R-0 R-x SPEN RX9 SREN CREN ADDEN FERR OERR RX9D bit 7 bit 0 Legend: R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' -n = Value at POR '0' = Bit is cleared '1' = Bit is set x = Bit is unknown bit 7 SPEN: Serial Port Enable bit 1 = Serial port enabled (configures RX/DT and TX/CK pins as serial port pins) 0 = Serial port disabled (held in Reset) bit 6 RX9: 9-Bit Receive Enable bit 1 = Selects 9-bit reception 0 = Selects 8-bit reception bit 5 SREN: Single Receive Enable bit Asynchronous mode: Don't care. Synchronous mode - Master: 1 = Enables single receive 0 = Disables single receive This bit is cleared after reception is complete. Synchronous mode - Slave: Don't care. bit 4 **CREN:** Continuous Receive Enable bit Asynchronous mode: 1 = Enables receiver 0 = Disables receiver Synchronous mode: 1 = Enables continuous receive until enable bit CREN is cleared (CREN overrides SREN) 0 = Disables continuous receive bit 3 ADDEN: Address Detect Enable bit Asynchronous mode 9-bit (RX9 = 1): 1 = Enables address detection, enables interrupt and loads the receive buffer when RSR<8> is set 0 = Disables address detection, all bytes are received and ninth bit can be used as parity bit Asynchronous mode 9-bit (RX9 = 0): Don't care. bit 2 FERR: Framing Error bit 1 = Framing error (can be updated by reading RCREG register and receiving next valid byte) 0 = No framing error bit 1 **OERR:** Overrun Error bit 1 = Overrun error (can be cleared by clearing bit CREN) 0 = No overrun error bit 0 RX9D: 9th bit of Received Data This can be an address/data bit or a parity bit and must be calculated by user firmware.

### REGISTER 19-2: RCSTA: RECEIVE STATUS AND CONTROL REGISTER

## 19.2.5 BREAK CHARACTER SEQUENCE

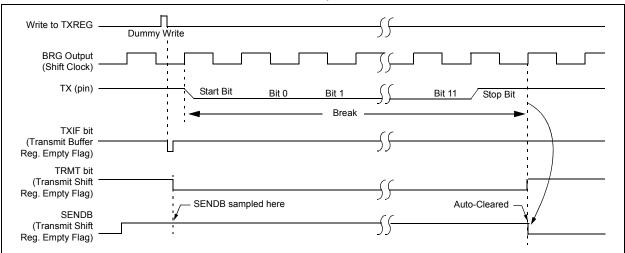

The Enhanced EUSART module has the capability of sending the special Break character sequences that are required by the LIN/J2602 bus standard. The Break character transmit consists of a Start bit, followed by twelve '0' bits and a Stop bit. The Frame Break character is sent whenever the SENDB and TXEN bits (TXSTA<3> and TXSTA<5>) are set while the Transmit Shift register is loaded with data. Note that the value of data written to TXREG will be ignored and all '0's will be transmitted.

The SENDB bit is automatically reset by hardware after the corresponding Stop bit is sent. This allows the user to preload the transmit FIFO with the next transmit byte following the Break character (typically, the Sync character in the LIN/J2602 specification).

Note that the data value written to the TXREG for the Break character is ignored. The write simply serves the purpose of initiating the proper sequence.

The TRMT bit indicates when the transmit operation is active or Idle, just as it does during normal transmission. See Figure 19-10 for the timing of the Break character sequence.

### 19.2.5.1 Break and Sync Transmit Sequence

The following sequence will send a message frame header made up of a Break, followed by an Auto-Baud Sync byte. This sequence is typical of a LIN/J2602 bus master.

- 1. Configure the EUSART for the desired mode.

- 2. Set the TXEN and SENDB bits to set up the Break character.

- 3. Load the TXREG with a dummy character to initiate transmission (the value is ignored).

- 4. Write '55h' to TXREG to load the Sync character into the transmit FIFO buffer.

- 5. After the Break has been sent, the SENDB bit is reset by hardware. The Sync character now transmits in the preconfigured mode.

When the TXREG becomes empty, as indicated by the TXIF, the next data byte can be written to TXREG.

### 19.2.6 RECEIVING A BREAK CHARACTER

The Enhanced USART module can receive a Break character in two ways.

The first method forces configuration of the baud rate at a frequency of 9/13 the typical speed. This allows for the Stop bit transition to be at the correct sampling location (13 bits for Break versus Start bit and 8 data bits for typical data).

The second method uses the auto-wake-up feature described in **Section 19.2.4 "Auto-Wake-up on Sync Break Character"**. By enabling this feature, the EUSART will sample the next two transitions on RX/DT, cause an RCIF interrupt and receive the next data byte followed by another interrupt.

Note that following a Break character, the user will typically want to enable the Auto-Baud Rate Detect feature. For both methods, the user can set the ABD bit once the TXIF interrupt is observed.

#### FIGURE 19-10: SEND BREAK CHARACTER SEQUENCE

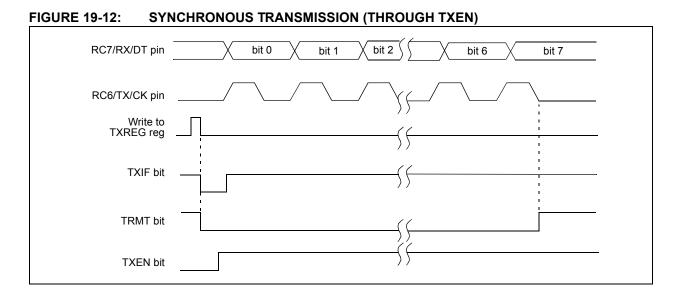

#### TABLE 19-7: REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER TRANSMISSION

| Name    | Bit 7                | Bit 6       | Bit 5       | Bit 4        | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on Page: |

|---------|----------------------|-------------|-------------|--------------|-------|--------|--------|--------|-----------------------------|

| INTCON  | GIE/GIEH             | PEIE/GIEL   | TMR0IE      | INT0IE       | RBIE  | TMR0IF | INT0IF | RBIF   | 55                          |

| PIR1    | PSPIF <sup>(1)</sup> | ADIF        | RCIF        | TXIF         | SSPIF | CCP1IF | TMR2IF | TMR1IF | 58                          |

| PIE1    | PSPIE <sup>(1)</sup> | ADIE        | RCIE        | TXIE         | SSPIE | CCP1IE | TMR2IE | TMR1IE | 58                          |

| IPR1    | PSPIP <sup>(1)</sup> | ADIP        | RCIP        | TXIP         | SSPIP | CCP1IP | TMR2IP | TMR1IP | 58                          |

| RCSTA   | SPEN                 | RX9         | SREN        | CREN         | ADDEN | FERR   | OERR   | RX9D   | 57                          |

| TXREG   | EUSART T             | ransmit Reg | ister       |              |       |        |        |        | 57                          |

| TXSTA   | CSRC                 | TX9         | TXEN        | SYNC         | SENDB | BRGH   | TRMT   | TX9D   | 57                          |

| BAUDCON | ABDOVF               | RCIDL       | _           | SCKP         | BRG16 | —      | WUE    | ABDEN  | 57                          |

| SPBRGH  | EUSART E             | aud Rate G  | enerator Re | gister, High | Byte  |        |        |        | 57                          |

| SPBRG   | EUSART E             | aud Rate G  | enerator Re | gister, Low  | Byte  |        |        |        | 57                          |

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used for synchronous master transmission.

**Note 1:** Reserved in PIC18F2X80 devices; always maintain these bits clear.

### 24.2 CAN Module Registers

Note: Not all CAN registers are available in the Access Bank.

There are many control and data registers associated with the CAN module. For convenience, their descriptions have been grouped into the following sections:

- · Control and Status Registers

- Dedicated Transmit Buffer Registers

- · Dedicated Receive Buffer Registers

- · Programmable TX/RX and Auto RTR Buffers

- Baud Rate Control Registers

- I/O Control Register

- · Interrupt Status and Control Registers

Detailed descriptions of each register and their usage are described in the following sections.

#### 24.2.1 CAN CONTROL AND STATUS REGISTERS

The registers described in this section control the overall operation of the CAN module and show its operational status.

### REGISTER 24-54: BRGCON3: BAUD RATE CONTROL REGISTER 3

| R/W-0                                    | R/W-0              | 11.0                             | U-0              | U-0                       | R/W-0                  | R/W-0                  |                        |

|------------------------------------------|--------------------|----------------------------------|------------------|---------------------------|------------------------|------------------------|------------------------|

|                                          | 1                  | U-0                              | 0-0              | 0-0                       |                        |                        | R/W-0                  |

| WAKDIS                                   | WAKFIL             |                                  |                  |                           | SEG2PH2 <sup>(1)</sup> | SEG2PH1 <sup>(1)</sup> | SEG2PH0 <sup>(1)</sup> |

| bit 7                                    |                    |                                  |                  |                           |                        |                        | bit 0                  |

|                                          |                    |                                  |                  |                           |                        |                        |                        |

| Legend:                                  |                    |                                  |                  |                           |                        |                        |                        |

| R = Readable                             | bit                | W = Writable                     | bit              | U = Unimpler              | nented bit, read       | as '0'                 |                        |

| -n = Value at POR '1' = Bit is set '0' = |                    |                                  |                  |                           | ared                   | x = Bit is unkn        | iown                   |

|                                          |                    |                                  |                  |                           |                        |                        |                        |

| bit 7                                    | WAKDIS: Wa         | ke-up Disable I                  | oit              |                           |                        |                        |                        |

|                                          | 1 = Disable C      | AN bus activity                  | wake-up feat     | ture                      |                        |                        |                        |

|                                          | 0 = Enable C/      | AN bus activity                  | wake-up feat     | ure                       |                        |                        |                        |

| bit 6                                    | WAKFIL: Sele       | ects CAN bus L                   | ine Filter for \ | Wake-up bit               |                        |                        |                        |

|                                          |                    | bus line filter for              |                  |                           |                        |                        |                        |

|                                          | 0 = CAN bus        | line filter is not               | used for wake    | e-up                      |                        |                        |                        |

| bit 5-3                                  | Unimplemen         | ted: Read as '                   | )'               |                           |                        |                        |                        |

| bit 2-0                                  | SEG2PH<2:0         | >: Phase Segn                    | nent 2 Time S    | elect bits <sup>(1)</sup> |                        |                        |                        |

|                                          |                    | Segment 2 time                   |                  |                           |                        |                        |                        |

|                                          |                    | Segment 2 tim                    |                  |                           |                        |                        |                        |

|                                          |                    | Segment 2 time<br>Segment 2 time |                  |                           |                        |                        |                        |

|                                          |                    | Segment 2 tim                    |                  |                           |                        |                        |                        |

|                                          |                    | Segment 2 tim                    |                  |                           |                        |                        |                        |

|                                          |                    | Segment 2 time                   |                  |                           |                        |                        |                        |

|                                          | 000 <b>= Phase</b> | Segment 2 time                   | e = 1 x Tq       |                           |                        |                        |                        |

Note 1: Ignored if SEG2PHTS bit (BRGCON2<7>) is '0'.

#### 24.2.5 CAN MODULE I/O CONTROL REGISTER

This register controls the operation of the CAN module's I/O pins in relation to the rest of the microcontroller.

## REGISTER 24-55: CIOCON: CAN I/O CONTROL REGISTER

| U-0                       | U-0 | R/W-0                 | R/W-0  | U-0          | U-0              | U-0    | U-0   |

|---------------------------|-----|-----------------------|--------|--------------|------------------|--------|-------|

|                           | _   | ENDRHI <sup>(1)</sup> | CANCAP | —            | —                | —      | —     |

| bit 7                     |     |                       |        |              |                  |        | bit 0 |

|                           |     |                       |        |              |                  |        |       |

|                           |     |                       |        |              |                  |        |       |

| Legend:                   |     |                       |        |              |                  |        |       |

| Legend:<br>R = Readable b | bit | W = Writable          | bit    | U = Unimpler | nented bit, read | as '0' |       |

| bit 7-6 | Unimplemented: Read as '0'                                                    |

|---------|-------------------------------------------------------------------------------|

| bit 5   | ENDRHI: Enable Drive High bit <sup>(1)</sup>                                  |

|         | 1 = CANTX pin will drive VDD when recessive                                   |

|         | 0 = CANTX pin will be tri-state when recessive                                |

| bit 4   | CANCAP: CAN Message Receive Capture Enable bit                                |

|         | 1 = Enable CAN capture, CAN message receive signal replaces input on RC2/CCP1 |

|         | 0 = Disable CAN capture, RC2/CCP1 input to CCP1 module                        |

| bit 3-0 | Unimplemented: Read as '0'                                                    |

Note 1: Always set this bit when using a differential bus to avoid signal crosstalk in CANTX from other nearby pins.

## REGISTER 25-4: CONFIG3H: CONFIGURATION REGISTER 3 HIGH (BYTE ADDRESS 300005h)

| R/P-1 | U-0 | U-0 | U-0 | U-0 | R/P-0   | R/P-1  | U-0   |

|-------|-----|-----|-----|-----|---------|--------|-------|

| MCLRE | —   | —   | —   | —   | LPT10SC | PBADEN | —     |

| bit 7 |     |     |     |     |         |        | bit 0 |

|       |     |     |     |     |         |        |       |

| Legend:                                                                                                                                                                                          |                                                                                                                                                            |                                       |                                     |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|-------------------------------------|--|--|

| R = Readable bit P = Programmable bit                                                                                                                                                            |                                                                                                                                                            | P = Programmable bit                  | U = Unimplemented bit, read as '0'  |  |  |

| -n = Value                                                                                                                                                                                       | when device is ι                                                                                                                                           | nprogrammed                           | u = Unchanged from programmed state |  |  |

| bit 7 <b>MCLRE:</b> MCLR Pin Enable bit<br>1 = MCLR pin enabled; RE3 input pin di<br>0 = RE3 input pin enabled; MCLR disab                                                                       |                                                                                                                                                            | pin enabled; RE <u>3 input</u> pin di |                                     |  |  |

| bit 6-3                                                                                                                                                                                          | S-3 Unimplemented: Read as '0'                                                                                                                             |                                       |                                     |  |  |

| bit 2                                                                                                                                                                                            | bit 2 LPT1OSC: Low-Power Timer1 Oscillator Enable bit<br>1 = Timer1 configured for low-power operation<br>0 = Timer1 configured for higher power operation |                                       |                                     |  |  |

| bit 1 <b>PBADEN:</b> PORTB A/D Enable bit<br>(Affects ADCON1 Reset state. ADCON1 controls PORTB<4:0> pin configuration.)<br>1 = PORTB<4:0> pins are configured as analog input channels on Reset |                                                                                                                                                            |                                       |                                     |  |  |

- 0 = PORTB<4:0> pins are configured as digital I/O on Reset

- bit 0 Unimplemented: Read as '0'

## REGISTER 25-5: CONFIG4L: CONFIGURATION REGISTER 4 LOW (BYTE ADDRESS 300006h)

| R/P-1 | R/P-0 | U-0 | R/P-0 | U-0 | R/P-1 | U-0 | R/P-1  |

|-------|-------|-----|-------|-----|-------|-----|--------|

| DEBUG | XINST | —   | BBSIZ | _   | LVP   | —   | STVREN |

| bit 7 |       |     |       |     |       |     | bit 0  |

| Lagandi                               |                                            |                                                |  |  |

|---------------------------------------|--------------------------------------------|------------------------------------------------|--|--|

| Legend:                               |                                            |                                                |  |  |

| R = Readable bit P = Programmable bit |                                            | U = Unimplemented bit, read as '0'             |  |  |

| -n = Value wh                         | en device is unprogrammed                  | u = Unchanged from programmed state            |  |  |

|                                       |                                            |                                                |  |  |

| bit 7                                 | <b>DEBUG:</b> Background Debugger Enable   | bit                                            |  |  |

|                                       |                                            | and RB7 configured as general purpose I/O pins |  |  |

|                                       | 0 = Background debugger enabled, RB6       | and RB7 are dedicated to In-Circuit Debug      |  |  |

| bit 6                                 | XINST: Extended Instruction Set Enable     | bit                                            |  |  |

|                                       | 1 = Instruction set extension and Indexed  |                                                |  |  |

|                                       | 0 = Instruction set extension and Indexed  | d Addressing mode disabled (Legacy mode)       |  |  |

| bit 5                                 | Unimplemented: Read as '0'                 |                                                |  |  |

| bit 4                                 | BBSIZ: Boot Block Size Select Bit 0        |                                                |  |  |

|                                       | 01 = 2K words (4 Kbytes) boot block        |                                                |  |  |

|                                       | 00 = 1K words (2 Kbytes) boot block        |                                                |  |  |

| bit 3                                 | Unimplemented: Read as '0'                 |                                                |  |  |

| bit 2                                 | LVP: Single-Supply ICSP™ Enable bit        |                                                |  |  |

|                                       | 1 = Single-Supply ICSP enabled             |                                                |  |  |

|                                       | 0 = Single-Supply ICSP disabled            |                                                |  |  |

| bit 1                                 | Unimplemented: Read as '0'                 |                                                |  |  |

| bit 0                                 | STVREN: Stack Full/Underflow Reset Er      | nable bit                                      |  |  |

|                                       | 1 = Stack full/underflow will cause Reset  |                                                |  |  |

|                                       | 0 = Stack full/underflow will not cause Re | eset                                           |  |  |

|                                       |                                            |                                                |  |  |

|                                       |                                            |                                                |  |  |

| BCF                         | Bit Clear f                                                                                                                                                                                         | BN                                                                                          | Branch if Negative                                                                                                                                                                                                       |  |  |

|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Syntax:                     | BCF f, b {,a}                                                                                                                                                                                       | Syntax:                                                                                     | BN n                                                                                                                                                                                                                     |  |  |

| Operands:                   | $0 \le f \le 255$                                                                                                                                                                                   | Operands:                                                                                   | $-128 \le n \le 127$                                                                                                                                                                                                     |  |  |

|                             | $0 \le b \le 7$<br>a \equiv [0,1]                                                                                                                                                                   | Operation:                                                                                  | if Negative bit is '1',<br>(PC) + 2 + 2n $\rightarrow$ PC                                                                                                                                                                |  |  |

| Operation:                  | $0 \rightarrow f \le b >$                                                                                                                                                                           | Status Affected:                                                                            | None                                                                                                                                                                                                                     |  |  |

| Status Affected:            | None                                                                                                                                                                                                | Encoding:                                                                                   | 1110 0110 nnnn nnnn                                                                                                                                                                                                      |  |  |

| Encoding:<br>Description:   | 1001 bbba ffff fff<br>Bit 'b' in register 'f' is cleared.                                                                                                                                           | Description:                                                                                | If the Negative bit is '1', then the program will branch.                                                                                                                                                                |  |  |

|                             | If 'a' is '0', the Access Bank is selected.<br>If 'a' is '1', the BSR is used to select the<br>GPR bank.<br>If 'a' is '0' and the extended instruction<br>set is enabled, this instruction operates |                                                                                             | The 2's complement number '2n' is<br>added to the PC. Since the PC will ha<br>incremented to fetch the next<br>instruction, the new address will be<br>PC + 2 + 2n. This instruction is then a<br>two-cycle instruction. |  |  |

|                             | in Indexed Literal Offset Addressing<br>mode whenever f ≤ 95 (5Fh). See                                                                                                                             | Words:                                                                                      | 1                                                                                                                                                                                                                        |  |  |

|                             | Section 26.2.3 "Byte-Oriented and                                                                                                                                                                   | Cycles:                                                                                     | 1(2)                                                                                                                                                                                                                     |  |  |

|                             | Bit-Oriented Instructions in Indexed<br>Literal Offset Mode" for details.                                                                                                                           | Q Cycle Activity:                                                                           |                                                                                                                                                                                                                          |  |  |

| Words:                      | 1                                                                                                                                                                                                   | If Jump:                                                                                    |                                                                                                                                                                                                                          |  |  |

| Cycles:                     | 1                                                                                                                                                                                                   | Q1                                                                                          | Q2 Q3 Q4                                                                                                                                                                                                                 |  |  |

| Q Cycle Activity:           |                                                                                                                                                                                                     | Decode                                                                                      | Read literal Process Write to PC<br>'n' Data                                                                                                                                                                             |  |  |

| Q1                          | Q2 Q3 Q4                                                                                                                                                                                            | No                                                                                          | No No No                                                                                                                                                                                                                 |  |  |

| Decode                      | Read Process Write   register 'f' Data register 'f'                                                                                                                                                 | operation                                                                                   | operation operation operation                                                                                                                                                                                            |  |  |

|                             |                                                                                                                                                                                                     | If No Jump:<br>Q1                                                                           | Q2 Q3 Q4                                                                                                                                                                                                                 |  |  |

| Example:                    | BCF FLAG REG, 7, 0                                                                                                                                                                                  | Decode                                                                                      | Read literal Process No                                                                                                                                                                                                  |  |  |

| Before Instruct             | =                                                                                                                                                                                                   | Decode                                                                                      | 'n' Data operation                                                                                                                                                                                                       |  |  |

| FLAG_RI<br>After Instructio | EG = C7h                                                                                                                                                                                            | Example:                                                                                    |                                                                                                                                                                                                                          |  |  |

| FLAG_RI                     |                                                                                                                                                                                                     | Example:<br>Before Instruct<br>PC<br>After Instructio<br>If Negati<br>PC<br>If Negati<br>PC | = address (HERE)<br>on<br>ve = 1;<br>= address (Jump)                                                                                                                                                                    |  |  |

| MULLW             | Multiply                                                               | Multiply Literal with W                                                                                                                                                                                                   |                         |                                      |  |  |  |

|-------------------|------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|--------------------------------------|--|--|--|

| Syntax:           | MULLW                                                                  | MULLW k                                                                                                                                                                                                                   |                         |                                      |  |  |  |

| Operands:         | $0 \le k \le 258$                                                      | $0 \le k \le 255$                                                                                                                                                                                                         |                         |                                      |  |  |  |

| Operation:        | (W) x k $\rightarrow$                                                  | PRODH:                                                                                                                                                                                                                    | PRODL                   |                                      |  |  |  |

| Status Affected:  | None                                                                   |                                                                                                                                                                                                                           |                         |                                      |  |  |  |

| Encoding:         | 0000                                                                   | 1101                                                                                                                                                                                                                      | kkkk                    | kkkk                                 |  |  |  |

| Description:      | out betwee<br>8-bit literal<br>placed in t<br>pair. PROI<br>W is uncha | An unsigned multiplication is carried<br>out between the contents of W and the<br>8-bit literal 'k'. The 16-bit result is<br>placed in the PRODH:PRODL register<br>pair. PRODH contains the high byte.<br>W is unchanged. |                         |                                      |  |  |  |

|                   | None of th<br>Note that r<br>possible in<br>is possible                | neither ov<br>this oper                                                                                                                                                                                                   | erflow no<br>ation. A a | or carry is                          |  |  |  |

| Words:            | 1                                                                      |                                                                                                                                                                                                                           |                         |                                      |  |  |  |

| Cycles:           | 1                                                                      |                                                                                                                                                                                                                           |                         |                                      |  |  |  |

| Q Cycle Activity: |                                                                        |                                                                                                                                                                                                                           |                         |                                      |  |  |  |

| Q1                | Q2                                                                     | Q3                                                                                                                                                                                                                        |                         | Q4                                   |  |  |  |

| Decode            | Read<br>literal 'k'                                                    | Proce<br>Data                                                                                                                                                                                                             | i r                     | Write<br>egisters<br>PRODH:<br>PRODL |  |  |  |

| Example:          | MIITIM                                                                 | 0C4b                                                                                                                                                                                                                      |                         |                                      |  |  |  |

| Example:           | MULLW | 0C4h |

|--------------------|-------|------|

| Before Instructior | า     |      |

| W                  | =     | E2h  |

| PRODH              | =     | ?    |

| PRODL              | =     | ?    |

| After Instruction  |       |      |

| W                  | =     | E2h  |

| PRODH              | =     | ADh  |

| PRODL              | =     | 08h  |

|                    |       |      |

| MULWF                                                           |                                                                                                                                                                                                                                                                          | W with f                                                                                                                                                                                                   |                                                                                                                                                                                                      |                                                                                                                                       |  |

|-----------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|--|

| Syntax:                                                         | MULWF                                                                                                                                                                                                                                                                    | f {,a}                                                                                                                                                                                                     |                                                                                                                                                                                                      |                                                                                                                                       |  |

| Operands:                                                       | 0 ≤ f ≤ 255<br>a ∈ [0,1]                                                                                                                                                                                                                                                 | $0 \le f \le 255$                                                                                                                                                                                          |                                                                                                                                                                                                      |                                                                                                                                       |  |

| Operation:                                                      |                                                                                                                                                                                                                                                                          | > PRODH:                                                                                                                                                                                                   | PRODI                                                                                                                                                                                                |                                                                                                                                       |  |

| Status Affected:                                                | None                                                                                                                                                                                                                                                                     | / I KODII.                                                                                                                                                                                                 | TROBE                                                                                                                                                                                                |                                                                                                                                       |  |

| Encoding:                                                       | 0000                                                                                                                                                                                                                                                                     | 001a                                                                                                                                                                                                       | ffff                                                                                                                                                                                                 | ffff                                                                                                                                  |  |

|                                                                 | register fill<br>result is st<br>register pa<br>high byte.<br>unchange<br>None of th<br>Note that i<br>possible in<br>result is po<br>If 'a' is '0',<br>selected. I<br>to select th<br>If 'a' is '0'<br>instruction<br>Offset Add<br>$f \le 95$ (5FH<br><b>"Byte-Ori</b> | e Status fli<br>neither over<br>n this opera<br>ossible but<br>the Access<br>f 'a' is '1', '<br>ne GPR ba<br>and the ex<br>set is ena<br>operates<br>dressing m<br>n). See Sec<br>ented and<br>ns in Indez | f'. The 1<br>PRODE<br>I contair<br>ad 'f' are<br>ags are<br>erflow nc<br>ation. A :<br>not dete<br>s Bank i<br>the BSR<br>ank.<br>tended<br>bled, thi<br>in Index<br>ode whe<br>ction 26<br>Bit-Orie | 6-bit<br>1:PRODI<br>is the<br>affected.<br>or carry is<br>zero<br>ected.<br>s<br>is used<br>s<br>ed Litera<br>enever<br>.2.3<br>ented |  |

| Words:                                                          | 1                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                            |                                                                                                                                                                                                      |                                                                                                                                       |  |