#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 25MHz                                                                    |

| Connectivity               | CANbus, I <sup>2</sup> C, SPI, UART/USART                                |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                              |

| Number of I/O              | 36                                                                       |

| Program Memory Size        | 32KB (16K x 16)                                                          |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 256 x 8                                                                  |

| RAM Size                   | 1.5К х 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                              |

| Data Converters            | A/D 11x10b                                                               |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Through Hole                                                             |

| Package / Case             | 40-DIP (0.600", 15.24mm)                                                 |

| Supplier Device Package    | 40-PDIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f4580-e-p |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### **Table of Contents**

| 1.0  | Device Overview                                              | 9   |

|------|--------------------------------------------------------------|-----|

| 2.0  | Guidelines for Getting Started with PIC18F Microcontrollers  |     |

| 3.0  | Oscillator Configurations                                    |     |

| 4.0  | Power-Managed Modes                                          |     |

| 5.0  | Reset                                                        |     |

| 6.0  | Memory Organization                                          |     |

| 7.0  | Flash Program Memory                                         | 101 |

| 8.0  | Data EEPROM Memory                                           | 111 |

| 9.0  | 8 x 8 Hardware Multiplier                                    | 117 |

| 10.0 | Interrupts                                                   | 119 |

| 11.0 | I/O Ports                                                    | 135 |

| 12.0 | Timer0 Module                                                | 151 |

| 13.0 | Timer1 Module                                                | 155 |

| 14.0 | Timer2 Module                                                |     |

|      | Timer3 Module                                                |     |

|      | Capture/Compare/PWM (CCP) Modules                            |     |

| 17.0 | Enhanced Capture/Compare/PWM (ECCP) Module                   |     |

| 18.0 | Master Synchronous Serial Port (MSSP) Module                 |     |

| 19.0 | Enhanced Universal Synchronous Receiver Transmitter (EUSART) |     |

| 20.0 | 10-Bit Analog-to-Digital Converter (A/D) Module              |     |

| 21.0 | Comparator Module                                            |     |

| 22.0 | Comparator Voltage Reference Module                          |     |

| 23.0 | High/Low-Voltage Detect (HLVD)                               |     |

|      | ECAN Module                                                  |     |

| 25.0 | Special Features of the CPU                                  |     |

| 26.0 |                                                              |     |

| 27.0 | Development Support                                          |     |

|      | Electrical Characteristics                                   |     |

|      | Packaging Information                                        |     |

|      | endix A: Revision History                                    |     |

|      | endix B: Device Differences                                  |     |

| •••  | endix C: Conversion Considerations                           |     |

|      | endix D: Migration from Baseline to Enhanced Devices         |     |

|      | endix E: Migration From Mid-Range to Enhanced Devices        |     |

|      | endix F: Migration From High-End to Enhanced Devices         |     |

|      | Microchip Web Site                                           |     |

|      | omer Change Notification Service                             |     |

|      | omer Support                                                 |     |

|      | ler Response                                                 |     |

| PIC1 | 8F2480/2580/4480/4580 Product Identification System          |     |

|                                                            | Pin Number<br>SPDIP,<br>SOIC QFN |    | Pin                | Buffer                         |                                                                                                                            |

|------------------------------------------------------------|----------------------------------|----|--------------------|--------------------------------|----------------------------------------------------------------------------------------------------------------------------|

| Pin Name                                                   |                                  |    |                    |                                | Description                                                                                                                |

|                                                            |                                  |    |                    |                                | PORTA is a bidirectional I/O port.                                                                                         |

| RA0/AN0<br>RA0<br>AN0                                      | 2                                | 27 | I/O<br>I           | TTL<br>Analog                  | Digital I/O.<br>Analog Input 0.                                                                                            |

| RA1/AN1<br>RA1<br>AN1                                      | 3                                | 28 | I/O<br>I           | TTL<br>Analog                  | Digital I/O.<br>Analog Input 1.                                                                                            |

| RA2/AN2/VREF-<br>RA2<br>AN2<br>VREF-                       | 4                                | 1  | I/O<br>I<br>I      | TTL<br>Analog<br>Analog        | Digital I/O.<br>Analog Input 2.<br>A/D reference voltage (low) input.                                                      |

| RA3/AN3/Vref+<br>RA3<br>AN3<br>Vref+                       | 5                                | 2  | I/O<br>I<br>I      | TTL<br>Analog<br>Analog        | Digital I/O.<br>Analog Input 3.<br>A/D reference voltage (high) input.                                                     |

| RA4/T0CKI<br>RA4<br>T0CKI                                  | 6                                | 3  | I/O<br>I           | TTL<br>ST                      | Digital I/O.<br>Timer0 external clock input.                                                                               |

| RA5/AN4/SS/<br>HLVDIN<br>RA5<br>AN4<br>SS<br>HLVDIN<br>RA6 | 7                                | 4  | I/O<br>I<br>I<br>I | TTL<br>Analog<br>TTL<br>Analog | Digital I/O.<br>Analog Input 4.<br>SPI slave select input.<br>High/Low-Voltage Detect input.<br>See the OSC2/CLKO/RA6 pin. |

| RA7                                                        |                                  |    |                    |                                | See the OSC1/CLKI/RA7 pin.                                                                                                 |

| TABLE 1-2: | PIC18F2480/2580 PINOUT I/O DESCRIPTIONS (CONTINUED) |

|------------|-----------------------------------------------------|

|            |                                                     |

ST = Schmitt Trigger input with CMOS levels

$I^2C = I^2C^{TM}/SMBus$  input buffer

L = Input Ρ = Power

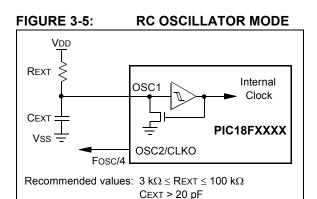

### 3.4 RC Oscillator

For timing insensitive applications, the "RC" and "RCIO" device options offer additional cost savings. The actual oscillator frequency is a function of several factors:

- supply voltage

- values of the external resistor (REXT) and capacitor (CEXT)

- operating temperature

Given the same device, operating voltage and temperature and component values, there will also be unit-to-unit frequency variations. These are due to factors such as:

- normal manufacturing variation

- difference in lead frame capacitance between package types (especially for low CEXT values)

- variations within the tolerance of limits of  $\ensuremath{\mathsf{REXT}}$  and  $\ensuremath{\mathsf{CEXT}}$

In the RC Oscillator mode, the oscillator frequency divided by 4 is available on the OSC2 pin. This signal may be used for test purposes or to synchronize other logic. Figure 3-5 shows how the R/C combination is connected.

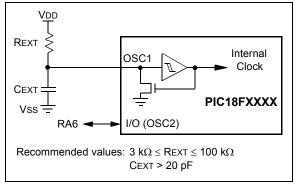

The RCIO Oscillator mode (Figure 3-6) functions like the RC mode, except that the OSC2 pin becomes an additional general purpose I/O pin. The I/O pin becomes bit 6 of PORTA (RA6).

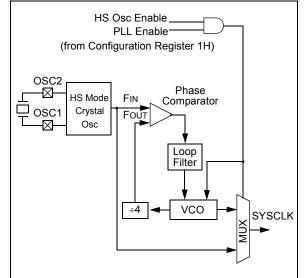

### 3.5 PLL Frequency Multiplier

A Phase Locked Loop (PLL) circuit is provided as an option for users who wish to use a lower frequency oscillator circuit or to clock the device up to its highest rated frequency from a crystal oscillator. This may be useful for customers who are concerned with EMI due to high-frequency crystals or users who require higher clock speeds from an internal oscillator.

#### 3.5.1 HSPLL OSCILLATOR MODE

The HSPLL mode makes use of the HS mode oscillator for frequencies up to 10 MHz. A PLL then multiplies the oscillator output frequency by 4 to produce an internal clock frequency up to 40 MHz.

The PLL is only available to the crystal oscillator when the FOSC<3:0> Configuration bits are programmed for HSPLL mode (= 0110).

#### FIGURE 3-7: PLL BLOCK DIAGRAM (HS MODE)

#### 3.5.2 PLL AND INTOSC

The PLL is also available to the internal oscillator block in selected oscillator modes. In this configuration, the PLL is enabled in software and generates a clock output of up to 32 MHz. The operation of INTOSC with the PLL is described in **Section 3.6.4 "PLL in INTOSC Modes**".

| TABLE 5-4: |                    |      |      |      | DITIONS FOR ALL                    |                    |      |                                 |      |  |  |

|------------|--------------------|------|------|------|------------------------------------|--------------------|------|---------------------------------|------|--|--|

| Register   | Applicable Devices |      |      |      | Power-on Reset,<br>Brown-out Reset | WDT I<br>RESET In: | ,    | Wake-up via WDT<br>or Interrupt |      |  |  |

| RXB1SIDH   | 2480               | 2580 | 4480 | 4580 | XXXX XXXX                          | นนนน               | นนนน | սսսս                            | นนนน |  |  |

| RXB1CON    | 2480               | 2580 | 4480 | 4580 | 000- 0000                          | 000-               | 0000 | uuu-                            | uuuu |  |  |

| TXB0D7     | 2480               | 2580 | 4480 | 4580 | XXXX XXXX                          | սսսս               | uuuu | uuuu                            | uuuu |  |  |

| TXB0D6     | 2480               | 2580 | 4480 | 4580 | XXXX XXXX                          | սսսս               | uuuu | uuuu                            | uuuu |  |  |

| TXB0D5     | 2480               | 2580 | 4480 | 4580 | XXXX XXXX                          | սսսս               | นนนน | սսսս                            | uuuu |  |  |

| TXB0D4     | 2480               | 2580 | 4480 | 4580 | XXXX XXXX                          | սսսս               | uuuu | uuuu                            | uuuu |  |  |

| TXB0D3     | 2480               | 2580 | 4480 | 4580 | XXXX XXXX                          | սսսս               | uuuu | uuuu                            | uuuu |  |  |

| TXB0D2     | 2480               | 2580 | 4480 | 4580 | XXXX XXXX                          | นนนน               | นนนน | սսսս                            | uuuu |  |  |

| TXB0D1     | 2480               | 2580 | 4480 | 4580 | XXXX XXXX                          | սսսս               | uuuu | uuuu                            | uuuu |  |  |

| TXB0D0     | 2480               | 2580 | 4480 | 4580 | XXXX XXXX                          | սսսս               | uuuu | uuuu                            | uuuu |  |  |

| TXB0DLC    | 2480               | 2580 | 4480 | 4580 | -x xxxx                            | -u                 | uuuu | -u                              | uuuu |  |  |

| TXB0EIDL   | 2480               | 2580 | 4480 | 4580 | XXXX XXXX                          | սսսս               | นนนน | սսսս                            | uuuu |  |  |

| TXB0EIDH   | 2480               | 2580 | 4480 | 4580 | XXXX XXXX                          | սսսս               | นนนน | -uuu                            | uuuu |  |  |

| TXB0SIDL   | 2480               | 2580 | 4480 | 4580 | XXX- X-XX                          | uuu-               | u-uu | uuu-                            | u-uu |  |  |

| TXB0SIDH   | 2480               | 2580 | 4480 | 4580 | XXXX XXXX                          | սսսս               | นนนน | սսսս                            | uuuu |  |  |

| TXB0CON    | 2480               | 2580 | 4480 | 4580 | 0000 0-00                          | 0000               | 0-00 | uuuu                            | u-uu |  |  |

| TXB1D7     | 2480               | 2580 | 4480 | 4580 | XXXX XXXX                          | սսսս               | uuuu | սսսս                            | uuuu |  |  |

| TXB1D6     | 2480               | 2580 | 4480 | 4580 | XXXX XXXX                          | սսսս               | นนนน | սսսս                            | uuuu |  |  |

| TXB1D5     | 2480               | 2580 | 4480 | 4580 | XXXX XXXX                          | սսսս               | นนนน | սսսս                            | uuuu |  |  |

| TXB1D4     | 2480               | 2580 | 4480 | 4580 | XXXX XXXX                          | սսսս               | uuuu | uuuu                            | uuuu |  |  |

| TXB1D3     | 2480               | 2580 | 4480 | 4580 | XXXX XXXX                          | սսսս               | นนนน | սսսս                            | uuuu |  |  |

| TXB1D2     | 2480               | 2580 | 4480 | 4580 | XXXX XXXX                          | սսսս               | uuuu | uuuu                            | uuuu |  |  |

| TXB1D1     | 2480               | 2580 | 4480 | 4580 | XXXX XXXX                          | սսսս               | uuuu | սսսս                            | uuuu |  |  |

| TXB1D0     | 2480               | 2580 | 4480 | 4580 | XXXX XXXX                          | սսսս               | uuuu | սսսս                            | uuuu |  |  |

| TXB1DLC    | 2480               | 2580 | 4480 | 4580 | -x xxxx                            | -u                 | นนนน | -u                              | uuuu |  |  |

| TXB1EIDL   | 2480               | 2580 | 4480 | 4580 | XXXX XXXX                          | սսսս               | uuuu | սսսս                            | uuuu |  |  |

| TXB1EIDH   | 2480               | 2580 | 4480 | 4580 | XXXX XXXX                          | սսսս               | uuuu | սսսս                            | uuuu |  |  |

| TXB1SIDL   | 2480               | 2580 | 4480 | 4580 | XXX- X-XX                          | uuu-               | u-uu | uuu-                            | uu-u |  |  |

| TXB1SIDH   | 2480               | 2580 | 4480 | 4580 | XXXX XXXX                          | սսսս               | uuuu | -uuu                            | uuuu |  |  |

| TXB1CON    | 2480               | 2580 | 4480 | 4580 | 0000 0-00                          | 0000               | 0-00 | սսսս                            | u-uu |  |  |

| TXB2D7     | 2480               | 2580 | 4480 | 4580 | XXXX XXXX                          | นนนน               | นนนน | Ouuu                            | uuuu |  |  |

#### TABLE 5-4: INITIALIZATION CONDITIONS FOR ALL REGISTERS (CONTINUED)

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition. Shaded cells indicate conditions do not apply for the designated device.

Note 1: One or more bits in the INTCONx or PIRx registers will be affected (to cause wake-up).

2: When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the PC is loaded with the interrupt vector (0008h or 0018h).

**3:** When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the TOSU, TOSH and TOSL are updated with the current value of the PC. The STKPTR is modified to point to the next location in the hardware stack.

4: See Table 5-3 for Reset value for specific condition.

**5:** Bits 6 and 7 of PORTA, LATA and TRISA are enabled, depending on the oscillator mode selected. When not enabled as PORTA pins, they are disabled and read '0'.

6: This register reads all '0's until ECAN<sup>™</sup> technology is set up in Mode 1 or Mode 2.

## TABLE 6-1:SPECIAL FUNCTION REGISTER MAP FOR<br/>PIC18F2480/2580/4480/4580 DEVICES (CONTINUED)

| Address | Name                  | Address | Name                  | Address | Name                  | Address | Name                  |

|---------|-----------------------|---------|-----------------------|---------|-----------------------|---------|-----------------------|

| E7Fh    | CANCON_RO4            | E6Fh    | CANCON_RO5            | E5Fh    | CANCON_RO6            | E4Fh    | CANCON_RO7            |

| E7Eh    | CANSTAT_RO4           | E6Eh    | CANSTAT_RO5           | E5Eh    | CANSTAT_RO6           | E4Eh    | CANSTAT_R07           |

| E7Dh    | B5D7 <sup>(2)</sup>   | E6Dh    | B4D7 <sup>(2)</sup>   | E5Dh    | B3D7 <sup>(2)</sup>   | E4Dh    | B2D7 <sup>(2)</sup>   |

| E7Ch    | B5D6 <sup>(2)</sup>   | E6Ch    | B4D6 <sup>(2)</sup>   | E5Ch    | B3D6 <sup>(2)</sup>   | E4Ch    | B2D6 <sup>(2)</sup>   |

| E7Bh    | B5D5 <sup>(2)</sup>   | E6Bh    | B4D5 <sup>(2)</sup>   | E5Bh    | B3D5 <sup>(2)</sup>   | E4Bh    | B2D5 <sup>(2)</sup>   |

| E7Ah    | B5D4 <sup>(2)</sup>   | E6Ah    | B4D4 <sup>(2)</sup>   | E5Ah    | B3D4 <sup>(2)</sup>   | E4Ah    | B2D4 <sup>(2)</sup>   |

| E79h    | B5D3 <sup>(2)</sup>   | E69h    | B4D3 <sup>(2)</sup>   | E59h    | B3D3 <sup>(2)</sup>   | E49h    | B2D3 <sup>(2)</sup>   |

| E78h    | B5D2 <sup>(2)</sup>   | E68h    | B4D2 <sup>(2)</sup>   | E58h    | B3D2 <sup>(2)</sup>   | E48h    | B2D2 <sup>(2)</sup>   |

| E77h    | B5D1 <sup>(2)</sup>   | E67h    | B4D1 <sup>(2)</sup>   | E57h    | B3D1 <sup>(2)</sup>   | E47h    | B2D1 <sup>(2)</sup>   |

| E76h    | B5D0 <sup>(2)</sup>   | E66h    | B4D0 <sup>(2)</sup>   | E56h    | B3D0 <sup>(2)</sup>   | E46h    | B2D0 <sup>(2)</sup>   |

| E75h    | B5DLC <sup>(2)</sup>  | E65h    | B4DLC <sup>(2)</sup>  | E55h    | B3DLC <sup>(2)</sup>  | E45h    | B2DLC <sup>(2)</sup>  |

| E74h    | B5EIDL <sup>(2)</sup> | E64h    | B4EIDL <sup>(2)</sup> | E54h    | B3EIDL <sup>(2)</sup> | E44h    | B2EIDL <sup>(2)</sup> |

| E73h    | B5EIDH <sup>(2)</sup> | E63h    | B4EIDH <sup>(2)</sup> | E53h    | B3EIDH <sup>(2)</sup> | E43h    | B2EIDH <sup>(2)</sup> |

| E72h    | B5SIDL <sup>(2)</sup> | E62h    | B4SIDL <sup>(2)</sup> | E52h    | B3SIDL <sup>(2)</sup> | E42h    | B2SIDL <sup>(2)</sup> |

| E71h    | B5SIDH <sup>(2)</sup> | E61h    | B4SIDH <sup>(2)</sup> | E51h    | B3SIDH <sup>(2)</sup> | E41h    | B2SIDH <sup>(2)</sup> |

| E70h    | B5CON <sup>(2)</sup>  | E60h    | B4CON <sup>(2)</sup>  | E50h    | B3CON <sup>(2)</sup>  | E40h    | B2CON <sup>(2)</sup>  |

| E3Fh    | CANCON_RO8            | E2Fh    | CANCON_RO9            | E1Fh    |                       | E0Fh    | —                     |

| E3Eh    | CANSTAT_RO8           | E2Eh    | CANSTAT_RO9           | E1Eh    |                       | E0Eh    | —                     |

| E3Dh    | B1D7 <sup>(2)</sup>   | E2Dh    | B0D7 <sup>(2)</sup>   | E1Dh    |                       | E0Dh    | _                     |

| E3Ch    | B1D6 <sup>(2)</sup>   | E2Ch    | B0D6 <sup>(2)</sup>   | E1Ch    |                       | E0Ch    | _                     |

| E3Bh    | B1D5 <sup>(2)</sup>   | E2Bh    | B0D5 <sup>(2)</sup>   | E1Bh    | _                     | E0Bh    | _                     |

| E3Ah    | B1D4 <sup>(2)</sup>   | E2Ah    | B0D4 <sup>(2)</sup>   | E1Ah    |                       | E0Ah    | _                     |

| E39h    | B1D3 <sup>(2)</sup>   | E29h    | B0D3 <sup>(2)</sup>   | E19h    |                       | E09h    | _                     |

| E38h    | B1D2 <sup>(2)</sup>   | E28h    | B0D2 <sup>(2)</sup>   | E18h    | _                     | E08h    | _                     |

| E37h    | B1D1 <sup>(2)</sup>   | E27h    | B0D1 <sup>(2)</sup>   | E17h    |                       | E07h    | _                     |

| E36h    | B1D0 <sup>(2)</sup>   | E26h    | B0D0 <sup>(2)</sup>   | E16h    |                       | E06h    | _                     |

| E35h    | B1DLC <sup>(2)</sup>  | E25h    | B0DLC <sup>(2)</sup>  | E15h    |                       | E05h    | —                     |

| E34h    | B1EIDL <sup>(2)</sup> | E24h    | B0EIDL <sup>(2)</sup> | E14h    |                       | E04h    | _                     |

| E33h    | B1EIDH <sup>(2)</sup> | E23h    | B0EIDH <sup>(2)</sup> | E13h    | —                     | E03h    | _                     |

| E32h    | B1SIDL <sup>(2)</sup> | E22h    | B0SIDL <sup>(2)</sup> | E12h    | _                     | E02h    | _                     |

| E31h    | B1SIDH <sup>(2)</sup> | E21h    | B0SIDH <sup>(2)</sup> | E11h    | —                     | E01h    | _                     |

| E30h    | B1CON <sup>(2)</sup>  | E20h    | B0CON <sup>(2)</sup>  | E10h    | _                     | E00h    | —                     |

Note 1: Registers available only on PIC18F4X80 devices; otherwise, the registers read as '0'.

2: When any TX\_ENn bit in RX\_TX\_SELn is set, then the corresponding bit in this register has transmit properties.

3: This is not a physical register.

### 6.5 Program Memory and the Extended Instruction Set

The operation of program memory is unaffected by the use of the extended instruction set.

Enabling the extended instruction set adds eight additional two-word commands to the existing PIC18 instruction set: ADDFSR, ADDULNK, CALLW, MOVSF, MOVSS, PUSHL, SUBFSR and SUBULNK. These instructions are executed as described in Section 6.2.4 "Two-Word Instructions".

## 6.6 Data Memory and the Extended Instruction Set

Enabling the PIC18 extended instruction set (XINST Configuration bit = 1) significantly changes certain aspects of data memory and its addressing. Specifically, the use of the Access Bank for many of the core PIC18 instructions is different. This is due to the introduction of a new addressing mode for the data memory space. This mode also alters the behavior of Indirect Addressing using FSR2 and its associated operands.

What does not change is just as important. The size of the data memory space is unchanged, as well as its linear addressing. The SFR map remains the same. Core PIC18 instructions can still operate in both Direct and Indirect Addressing mode; inherent and literal instructions do not change at all. Indirect Addressing with FSR0 and FSR1 also remains unchanged.

#### 6.6.1 INDEXED ADDRESSING WITH LITERAL OFFSET

Enabling the PIC18 extended instruction set changes the behavior of Indirect Addressing using the FSR2 register pair and its associated file operands. Under the proper conditions, instructions that use the Access Bank – that is, most bit-oriented and byte-oriented – instructions – can invoke a form of Indexed Addressing using an offset specified in the instruction. This special addressing mode is known as Indexed Addressing with Literal Offset or Indexed Literal Offset mode. When using the extended instruction set, this addressing mode requires the following:

- The use of the Access Bank is forced ('a' = 0); and

- The file address argument is less than or equal to 5Fh.

Under these conditions, the file address of the instruction is not interpreted as the lower byte of an address (used with the BSR in Direct Addressing), or as an 8-bit address in the Access Bank. Instead, the value is interpreted as an offset value to an Address Pointer, specified by FSR2. The offset and the contents of FSR2 are added to obtain the target address of the operation.

#### 6.6.2 INSTRUCTIONS AFFECTED BY INDEXED LITERAL OFFSET MODE

Any of the core PIC18 instructions that can use Direct Addressing are potentially affected by the Indexed Literal Offset Addressing mode. This includes all byte-oriented and bit-oriented instructions, or almost one-half of the standard PIC18 instruction set. Instructions that only use Inherent or Literal Addressing modes are unaffected.

Additionally, byte-oriented and bit-oriented instructions are not affected if they use the Access Bank (Access RAM bit is '1'), or include a file address of 60h or above. Instructions meeting these criteria will continue to execute as before. A comparison of the different possible addressing modes when the extended instruction set is enabled in shown in Figure 6-9.

Those who desire to use byte-oriented or bit-oriented instructions in the Indexed Literal Offset mode should note the changes to assembler syntax for this mode. This is described in more detail in **Section 26.2.1** "Extended Instruction Syntax".

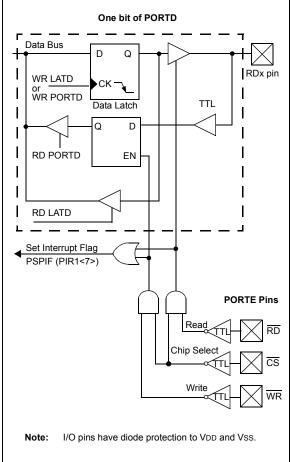

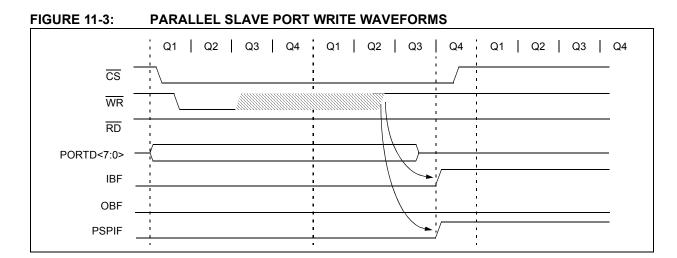

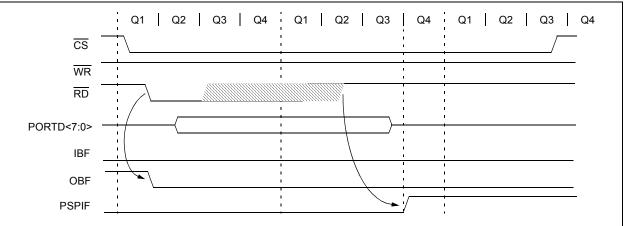

#### 11.6 Parallel Slave Port

| Note: | The Parallel Slave Port is only available on |

|-------|----------------------------------------------|

|       | PIC18F4X80 devices.                          |

In addition to its function as a general I/O port, PORTD can also operate as an 8-bit wide Parallel Slave Port (PSP) or microprocessor port. PSP operation is controlled by the 4 upper bits of the TRISE register (Register 11-1). Setting control bit, PSPMODE (TRISE<4>), enables PSP operation, as long as the Enhanced CCP module is not operating in dual output or quad output PWM mode. In Slave mode, the port is asynchronously readable and writable by the external world.

The PSP can directly interface to an 8-bit microprocessor data bus. The external microprocessor can read or write the PORTD latch as an 8-bit latch. Setting the control bit PSPMODE enables the PORTE I/O pins to become control inputs for the microprocessor port. When set, port pin RE0 is the RD input, RE1 is the WR input and RE2 is the CS (Chip Select) input. For this functionality, the corresponding data direction bits of the TRISE register (TRISE<2:0>) must be configured as inputs (set). The A/D port Configuration bits, PFCG<3:0> (ADCON1<3:0>), must also be set to '1010'.

A write to the PSP occurs when both the  $\overline{CS}$  and  $\overline{WR}$  lines are first detected low and ends when either are detected high. The PSPIF and IBF flag bits are both set when the write ends.

A read from the PSP occurs when both the  $\overline{CS}$  and  $\overline{RD}$  lines are first detected low. The data in PORTD is read out and the OBF bit is set. If the user writes new data to PORTD to set OBF, the data is immediately read out; however, the OBF bit is not set.

When either the  $\overline{CS}$  or  $\overline{RD}$  lines are detected high, the PORTD pins return to the input state and the PSPIF bit is set. User applications should wait for PSPIF to be set before servicing the PSP; when this happens, the IBF and OBF bits can be polled and the appropriate action taken. The timing for the control signals in Write and Read modes is shown in Figure 11-3 and Figure 11-4, respectively.

#### FIGURE 11-2: PORTD AND PORTE BLOCK DIAGRAM (PARALLEL SLAVE PORT)

#### FIGURE 11-4: PARALLEL SLAVE PORT READ WAVEFORMS

#### TABLE 11-11: REGISTERS ASSOCIATED WITH PARALLEL SLAVE PORT

| Name                 | Bit 7       | Bit 6          | Bit 5   | Bit 4   | Bit 3 | Bit 2      | Bit 1        | Bit 0  | Reset<br>Values<br>on Page: |

|----------------------|-------------|----------------|---------|---------|-------|------------|--------------|--------|-----------------------------|

| PORTD <sup>(1)</sup> | RD7         | RD6            | RD5     | RD4     | RD3   | RD2        | RD1          | RD0    | 58                          |

| LATD <sup>(1)</sup>  | LATD Output | ut Latch Regis | ster    |         |       |            |              |        | 58                          |

| TRISD <sup>(1)</sup> | PORTD Da    | ta Direction R | egister |         |       |            |              |        | 58                          |

| PORTE <sup>(1)</sup> | _           |                | _       | _       | RE3   | RE2        | RE1          | RE0    | 58                          |

| LATE <sup>(1)</sup>  | _           | —              | _       | _       | _     | LATE Outpu | ut Latch Reg | 58     |                             |

| TRISE <sup>(1)</sup> | IBF         | OBF            | IBOV    | PSPMODE | _     | TRISE2     | TRISE1       | TRISE0 | 58                          |

| INTCON               | GIE/GIEH    | PEIE/GIEL      | TMR0IE  | INTOIE  | RBIE  | TMR0IF     | INT0IF       | RBIF   | 55                          |

| PIR1                 | PSPIF       | ADIF           | RCIF    | TXIF    | SSPIF | CCP1IF     | TMR2IF       | TMR1IF | 58                          |

| PIE1                 | PSPIE       | ADIE           | RCIE    | TXIE    | SSPIE | CCP1IE     | TMR2IE       | TMR1IE | 58                          |

| IPR1                 | PSPIP       | ADIP           | RCIP    | TXIP    | SSPIP | CCP1IP     | TMR2IP       | TMR1IP | 58                          |

| ADCON1               |             |                | VCFG1   | VCFG0   | PCFG3 | PCFG2      | PCFG1        | PCFG0  | 56                          |

| CMCON <sup>(1)</sup> | C2OUT       | C10UT          | C2INV   | C1INV   | CIS   | CM2        | CM1          | CM0    | 57                          |

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used by the Parallel Slave Port.

Note 1: These registers are available on PIC18F4X80 devices only.

|    | ECCP1CON<br><7:6> | SIGNAL        | 0 Duty<br>Cycle      | <b>→</b>             | PR2 + 1          |

|----|-------------------|---------------|----------------------|----------------------|------------------|

|    | 1.02              |               |                      | Period —             |                  |

| 00 | (Single Output)   | P1A Modulated | Delay <sup>(1)</sup> | Delay <sup>(1)</sup> |                  |

|    |                   | P1A Modulated |                      |                      | -<br>-<br>-<br>- |

| LO | (Half-Bridge)     | P1B Modulated |                      |                      |                  |

|    |                   | P1A Active    | <br>                 |                      |                  |

| )1 | (Full-Bridge,     | P1B Inactive  |                      | 1<br>1<br>1          | -<br>-<br>-<br>- |

| JT | Forward)          | P1C Inactive  |                      |                      | 1<br>            |

|    |                   | P1D Modulated | =                    | <br>                 |                  |

|    |                   | P1A Inactive  | _ !                  |                      |                  |

| 11 | (Full-Bridge,     | P1B Modulated |                      |                      |                  |

| L  | Reverse)          | P1C Active    |                      | i<br>I<br>I          |                  |

|    |                   | P1D Inactive  | _ '<br>_ '           |                      | 1<br>1<br>1      |

#### FIGURE 17-2: PWM OUTPUT RELATIONSHIPS (ACTIVE-HIGH STATE)

#### FIGURE 17-3: PWM OUTPUT RELATIONSHIPS (ACTIVE-LOW STATE)

|    | ECCP1CON<br><7:6>         | SIGNAL        | 0 |                      | -▶                   | PR2 + 1     |

|----|---------------------------|---------------|---|----------------------|----------------------|-------------|

|    | 1.0                       |               |   |                      | – Period ––––        |             |

| 00 | (Single Output)           | P1A Modulated |   | ]<br>'               |                      | I<br><br>   |

|    |                           | P1A Modulated |   | Delay <sup>(1)</sup> | Delay <sup>(1)</sup> | 1<br>1<br>1 |

| 10 | (Half-Bridge)             | P1B Modulated |   |                      |                      |             |

|    |                           | P1A Active    |   | 1<br>1               | 1<br>1<br>1          | 1<br>1<br>1 |

| 01 | (Full-Bridge,<br>Forward) | P1B Inactive  |   | 1<br>1<br>1          | 1<br>1<br>1          | 1<br>1<br>1 |

|    | i orward)                 | P1C Inactive  |   | 1<br>1               |                      |             |

|    |                           | P1D Modulated |   | ļ                    |                      |             |

|    |                           | P1A Inactive  |   | 1<br>1<br>1          |                      |             |

| 11 | (Full-Bridge,<br>Reverse) | P1B Modulated |   | 1                    |                      | I<br><br>   |

|    | Reverse)                  | P1C Active    |   | 1<br>+<br>1          | 1<br>                |             |

|    |                           | P1D Inactive  |   | 1<br>1<br>1          | <br>I<br>I           |             |

#### **Relationships:**

• Period = 4 \* Tosc \* (PR2 + 1) \* (TMR2 Prescale Value)

• Duty Cycle = Tosc \* (ECCPR1L<7:0>:ECCP1CON<5:4>) \* (TMR2 Prescale Value)

• Delay = 4 \* Tosc \* (ECCP1DEL<6:0>)

Note 1: Dead-band delay is programmed using the ECCP1DEL register (Section 17.4.6 "Programmable Dead-Band Delay").

#### 17.4.9 SETUP FOR PWM OPERATION

The following steps should be taken when configuring the ECCP module for PWM operation:

- 1. Configure the PWM pins, P1A and P1B (and P1C and P1D, if used), as inputs by setting the corresponding TRIS bits.

- 2. Set the PWM period by loading the PR2 register.

- Configure the ECCP1 module for the desired PWM mode and configuration by loading the ECCP1CON register with the appropriate values:

- Select one of the available output configurations and direction with the EPWM1M<1:0> bits.

- Select the polarities of the PWM output signals with the ECCP1M<3:0> bits.

- 4. Set the PWM duty cycle by loading the ECCPR1L register and ECCP1CON<5:4> bits.

- 5. For Half-Bridge Output mode, set the dead-band delay by loading ECCP1DEL<6:0> with the appropriate value.

- 6. If auto-shutdown operation is required, load the ECCP1AS register:

- Select the auto-shutdown sources using the ECCPAS<2:0> bits.

- Select the shutdown states of the PWM output pins using PSSAC<1:0> and PSSBD<1:0> bits.

- Set the ECCPASE bit (ECCP1AS<7>).

- Configure the comparators using the CMCON register.

- Configure the comparator inputs as analog inputs.

- 7. If auto-restart operation is required, set the PRSEN bit (ECCP1DEL<7>).

- 8. Configure and start TMR2:

- Clear the TMR2 interrupt flag bit by clearing the TMR2IF bit (PIR1<1>).

- Set the TMR2 prescale value by loading the T2CKPS bits (T2CON<1:0>).

- Enable Timer2 by setting the TMR2ON bit (T2CON<2>).

- 9. Enable PWM outputs after a new PWM cycle has started:

- Wait until TMRn overflows (TMRnIF bit is set).

- Enable the ECCP1/P1A, P1B, P1C and/or P1D pin outputs by clearing the respective TRIS bits.

- Clear the ECCPASE bit (ECCP1AS<7>).

#### 17.4.10 EFFECTS OF A RESET

Both Power-on Reset and subsequent Resets will force all ports to Input mode and the CCP registers to their Reset states.

This forces the Enhanced CCP module to reset to a state compatible with the standard CCP module.

#### EXAMPLE 19-1: CALCULATING BAUD RATE ERROR

| For a device with Fosc | c of | 16 MHz, desired baud rate of 9600, Asynchronous mode, 8-bit BRG:                                                |

|------------------------|------|-----------------------------------------------------------------------------------------------------------------|

| Desired Baud Rate      | =    | Fosc/(64 ([SPBRGH:SPBRG] + 1)                                                                                   |

| Solving for SPBRGH:S   | SPB  | RG:                                                                                                             |

| Х                      | =    | ((Fosc/Desired Baud Rate)/64) – 1                                                                               |

|                        | =    | ((1600000/9600)/64) – 1                                                                                         |

|                        | =    | [25.042] = 25                                                                                                   |

| Calculated Baud Rate   | =    | 16000000/(64 (25 + 1))                                                                                          |

|                        | =    | 9615                                                                                                            |

| Error                  | =    | (Calculated Baud Rate - Desired Baud Rate)/Desired Baud Rate                                                    |

|                        | =    | (9615 - 9600)/9600 = 0.16%                                                                                      |

|                        | = =  | [25.042] = 25<br>16000000/(64 (25 + 1))<br>9615<br>(Calculated Baud Rate – Desired Baud Rate)/Desired Baud Rate |

#### TABLE 19-2: REGISTERS ASSOCIATED WITH BAUD RATE GENERATOR

| Name    | Bit 7                                              | Bit 6                                         | Bit 5 | Bit 4    | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Reset<br>Values<br>on Page: |  |

|---------|----------------------------------------------------|-----------------------------------------------|-------|----------|-------|-------|-------|-------|-----------------------------|--|

| TXSTA   | CSRC                                               | TX9                                           | TXEN  | SYNC     | SENDB | BRGH  | TRMT  | TX9D  | 57                          |  |

| RCSTA   | SPEN                                               | RX9                                           | SREN  | CREN     | ADDEN | FERR  | OERR  | RX9D  | 57                          |  |

| BAUDCON | ABDOVF                                             | RCIDL                                         | _     | SCKP     | BRG16 | _     | WUE   | ABDEN | 57                          |  |

| SPBRGH  | EUSART B                                           | EUSART Baud Rate Generator Register High Byte |       |          |       |       |       |       |                             |  |

| SPBRG   | SPBRG EUSART Baud Rate Generator Register Low Byte |                                               |       |          |       |       |       |       |                             |  |

| SPBRG   |                                                    |                                               |       | <u> </u> | Byte  |       |       |       | 57                          |  |

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used by the BRG.

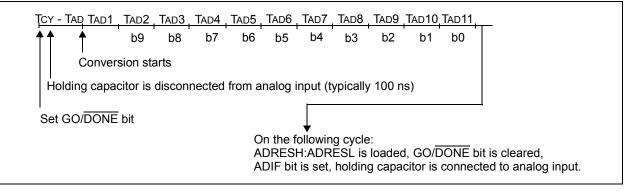

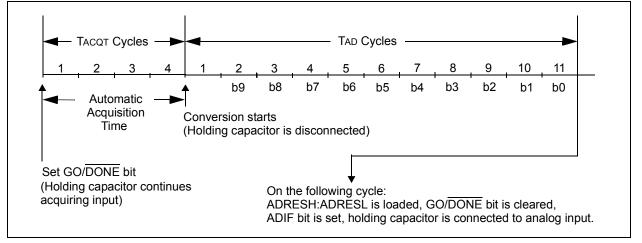

### 20.6 A/D Conversions

Figure 20-3 shows the operation of the A/D Converter after the GO/DONE bit has been set and the ACQT<2:0> bits are cleared. A conversion is started after the following instruction to allow entry into Sleep mode before the conversion begins.

Figure 20-4 shows the operation of the A/D Converter after the GO/DONE bit has been set and the ACQT<2:0> bits are set to '010' and selecting a 4 TAD acquisition time before the conversion starts.

Clearing the GO/DONE bit during a conversion will abort the current conversion. The A/D Result register pair will NOT be updated with the partially completed A/D conversion sample. This means the ADRESH:ADRESL registers will continue to contain the value of the last completed conversion (or the last value written to the ADRESH:ADRESL registers).

After the A/D conversion is completed or aborted, a 2 TAD wait is required before the next acquisition can be started. After this wait, acquisition on the selected channel is automatically started.

**Note:** The GO/DONE bit should **NOT** be set in the same instruction that turns on the A/D.

#### FIGURE 20-3: A/D CONVERSION TAD CYCLES (ACQT<2:0> = 000, TACQ = 0)

#### FIGURE 20-4: A/D CONVERSION TAD CYCLES (ACQT<2:0> = 010, TACQ = 4 TAD)

#### REGISTER 24-21: RXERRCNT: RECEIVE ERROR COUNT REGISTER

| R-0      | R-0  | R-0  | R-0  | R-0  | R-0  | R-0  | R-0   |

|----------|------|------|------|------|------|------|-------|

| REC7     | REC6 | REC5 | REC4 | REC3 | REC2 | REC1 | REC0  |

| bit 7    |      |      |      |      |      |      | bit 0 |

|          |      |      |      |      |      |      |       |

| l egend. |      |      |      |      |      |      |       |

| Legena.                           |                  |                                    |                    |  |

|-----------------------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit W = Writable bit |                  | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR                 | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

bit 7-0 **REC<7:0>:** Receive Error Counter bits

This register contains the receive error value as defined by the CAN specifications. When RXERRCNT > 127, the module will go into an error-passive state. RXERRCNT does not have the ability to put the module in "bus-off" state.

#### EXAMPLE 24-5: READING A CAN MESSAGE

; Need to read a pending message from RXB0 buffer. ; To receive any message, filter, mask and RXM1:RXM0 bits in RXB0CON registers must be ; programmed correctly. ; Make sure that there is a message pending in RXBO. BTFSS RXBOCON, RXFUL ; Does RXB0 contain a message? BRA NoMessage ; No. Handle this situation... ; We have verified that a message is pending in RXBO buffer. ; If this buffer can receive both Standard or Extended Identifier messages, ; identify type of message received. ; Is this Extended Identifier? BTFSS RXBOSIDL, EXID BRA StandardMessage ; No. This is Standard Identifier message. ; Yes. This is Extended Identifier message. ; Read all 29-bits of Extended Identifier message. . . . ; Now read all data bytes MOVFF RXB0DO, MY DATA BYTE1 . . . ; Once entire message is read, mark the RXBO that it is read and no longer FULL. BCF RXB0CON, RXFUL ; This will allow CAN Module to load new messages ; into this buffer. . . .

## $\label{eq:register24-26:BnSIDL: TX/RX BUFFER n STANDARD IDENTIFIER REGISTERS, \\ LOW BYTE IN RECEIVE MODE [0 \le n \le 5, TXnEN (BSEL0<n>) = 0]^{(1)}$

| R-x   | R-x  | R-x  | R-x | R-x  | U-0 | R-x   | R-x   |

|-------|------|------|-----|------|-----|-------|-------|

| SID2  | SID1 | SID0 | SRR | EXID |     | EID17 | EID16 |

| bit 7 |      |      |     |      |     |       | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 7-5 | SID<2:0>: Standard Identifier bits (if EXID = 0)                                                                                                                             |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | Extended Identifier bits, EID<20:18> (if EXID = 1).                                                                                                                          |

| bit 4   | SRR: Substitute Remote Transmission Request bit                                                                                                                              |

|         | This bit is always '1' when EXID = 1 or equal to the value of RXRTRRO (BnCON<5>) when EXID = 0.                                                                              |

| bit 3   | EXID: Extended Identifier Enable bit                                                                                                                                         |

|         | <ul> <li>1 = Received message is an extended identifier frame (SID&lt;10:0&gt; are EID&lt;28:18&gt;)</li> <li>0 = Received message is a standard identifier frame</li> </ul> |

| bit 2   | Unimplemented: Read as '0'                                                                                                                                                   |

| bit 1-0 | EID<17:16>: Extended Identifier bits                                                                                                                                         |

|         |                                                                                                                                                                              |

**Note 1:** These registers are available in Mode 1 and 2 only.

### $\label{eq:register24-27:BnSiDL: TX/RX BUFFER n STANDARD IDENTIFIER REGISTERS, \\ LOW BYTE IN RECEIVE MODE [0 \le n \le 5, TXnEN (BSEL0<n>) = 1]^{(1)}$

| R/W-x | R/W-x | R/W-x | U-0 | R/W-x | U-0 | R/W-x | R/W-x |

|-------|-------|-------|-----|-------|-----|-------|-------|

| SID2  | SID1  | SID0  | —   | EXIDE | —   | EID17 | EID16 |

| bit 7 |       |       |     |       |     |       | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | l as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 7-5 | SID<2:0>: Standard Identifier bits (if EXIDE = 0)                                                                                                                            |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | Extended Identifier bits, EID<20:18> (if EXIDE = 1).                                                                                                                         |

| bit 4   | Unimplemented: Read as '0'                                                                                                                                                   |

| bit 3   | EXIDE: Extended Identifier Enable bit                                                                                                                                        |

|         | <ul> <li>1 = Received message is an extended identifier frame (SID&lt;10:0&gt; are EID&lt;28:18&gt;)</li> <li>0 = Received message is a standard identifier frame</li> </ul> |

| bit 2   | Unimplemented: Read as '0'                                                                                                                                                   |

| bit 1-0 | EID<17:16>: Extended Identifier bits                                                                                                                                         |

Note 1: These registers are available in Mode 1 and 2 only.

| R/W-0         | R/W-0                                            | R/W-0                                      | R/W-0           | R/W-0            | R/W-0            | R/W-0           | R/W-0   |  |  |

|---------------|--------------------------------------------------|--------------------------------------------|-----------------|------------------|------------------|-----------------|---------|--|--|

| FIL15_1       | FIL15_0                                          | FIL14_1                                    | FIL14_0         | FIL13_1          | FIL13_0          | FIL12_1         | FIL12_0 |  |  |

| bit 7         |                                                  |                                            |                 |                  |                  |                 | bit C   |  |  |

|               |                                                  |                                            |                 |                  |                  |                 |         |  |  |

| Legend:       |                                                  |                                            |                 |                  |                  |                 |         |  |  |

| R = Readable  | e bit                                            | W = Writable                               | bit             | U = Unimpler     | mented bit, read | l as '0'        |         |  |  |

| -n = Value at | POR                                              | '1' = Bit is set                           | t               | '0' = Bit is cle | ared             | x = Bit is unki | nown    |  |  |

|               |                                                  |                                            |                 |                  |                  |                 |         |  |  |

| bit 7-6       | FIL15_<1:0>:                                     | : Filter 15 Sele                           | ct bits 1 and 0 |                  |                  |                 |         |  |  |

|               |                                                  | 11 = No mask                               |                 |                  |                  |                 |         |  |  |

|               |                                                  | 10 = Filter 15<br>01 = Acceptance Mask 1   |                 |                  |                  |                 |         |  |  |

|               | 00 = Accepta                                     |                                            |                 |                  |                  |                 |         |  |  |

| bit 5-4       | FIL14_<1:0>:                                     | FIL14_<1:0>: Filter 14 Select bits 1 and 0 |                 |                  |                  |                 |         |  |  |

|               | 11 = No masl                                     | 11 = No mask                               |                 |                  |                  |                 |         |  |  |

|               |                                                  | 10 = Filter 15                             |                 |                  |                  |                 |         |  |  |

|               | 01 = Acceptance Mask 1<br>00 = Acceptance Mask 0 |                                            |                 |                  |                  |                 |         |  |  |

| bit 3-2       | •                                                | : Filter 13 Sele                           | ct bits 1 and 0 |                  |                  |                 |         |  |  |

|               | 11 = No masl                                     |                                            |                 |                  |                  |                 |         |  |  |

|               | 10 = Filter 15                                   |                                            |                 |                  |                  |                 |         |  |  |

|               | 01 = Accepta                                     |                                            |                 |                  |                  |                 |         |  |  |

| h:4 0         | 00 = Accepta                                     |                                            |                 |                  |                  |                 |         |  |  |

| bit 1-0       | 11 = No mas                                      | : Filter 12 Sele                           | ct bits 1 and 0 |                  |                  |                 |         |  |  |

|               | 10 = Filter 15                                   | -                                          |                 |                  |                  |                 |         |  |  |

|               | 01 = Accepta                                     |                                            |                 |                  |                  |                 |         |  |  |

|               | 00 = Accepta                                     | nce Mask 0                                 |                 |                  |                  |                 |         |  |  |

|               |                                                  |                                            |                 |                  |                  |                 |         |  |  |

### REGISTER 24-51: MSEL3: MASK SELECT REGISTER 3<sup>(1)</sup>

**Note 1:** This register is available in Mode 1 and 2 only.

### 24.7 Message Reception

#### 24.7.1 RECEIVING A MESSAGE

Of all receive buffers, the MAB is always committed to receiving the next message from the bus. The MCU can access one buffer while the other buffer is available for message reception or holding a previously received message.

Note: The entire contents of the MAB are moved into the receive buffer once a message is accepted. This means that regardless of the type of identifier (standard or extended) and the number of data bytes received, the entire receive buffer is overwritten with the MAB contents. Therefore, the contents of all registers in the buffer must be assumed to have been modified when any message is received.

When a message is moved into either of the receive buffers, the associated RXFUL bit is set. This bit must be cleared by the MCU when it has completed processing the message in the buffer in order to allow a new message to be received into the buffer. This bit provides a positive lockout to ensure that the firmware has finished with the message before the module attempts to load a new message into the receive buffer. If the receive interrupt is enabled, an interrupt will be generated to indicate that a valid message has been received.

Once a message is loaded into any matching buffer, user firmware may determine exactly what filter caused this reception by checking the filter hit bits in the RXBnCON or BnCON registers. In Mode 0, FILHIT<3:0> of RXBnCON serve as filter hit bits. In Mode 1 and 2, FILHIT<4:0> bits of BnCON serve as filter hit bits. The same registers also indicate whether the current message is an RTR frame or not. A received message is considered a standard identifier message if the EXID bit in the RXBnSIDL or the BnSIDL register is cleared. Conversely, a set EXID bit indicates an extended identifier message. If the received message is a standard identifier message, user firmware needs to read the SIDL and SIDH registers. In the case of an extended identifier message, firmware should read the SIDL, SIDH, EIDL and EIDH registers. If the RXBnDLC or BnDLC register contain non-zero data count, user firmware should also read the corresponding number of data bytes by accessing the RXBnDm or the BnDm registers. When a received message is an RTR and if the current buffer is not configured for automatic RTR handling, user firmware must take appropriate action and respond manually.

Each receive buffer contains RXM bits to set special Receive modes. In Mode 0, RXM<1:0> bits in RXBnCON define a total of four Receive modes. In Mode 1 and 2, RXM1 bit, in combination with the EXID mask and filter bit, define the same four receive modes.

Normally, these bits are set to '00' to enable reception of all valid messages as determined by the appropriate acceptance filters. In this case, the determination of whether or not to receive standard or extended messages is determined by the EXIDE bit in the acceptance filter register. In Mode 0, if the RXM bits are set to '01' or '10', the receiver will accept only messages with standard or extended identifiers, respectively. If an acceptance filter has the EXIDE bit set such that it does not correspond with the RXM mode, that acceptance filter is rendered useless. In Mode 1 and 2, setting EXID in the SIDL Mask register will ensure that only standard or extended identifiers are received. These two modes of RXM bits can be used in systems where it is known that only standard or extended messages will be on the bus. If the RXM bits are set to '11' (RXM1 = 1 in Mode 1 and 2), the buffer will receive all messages regardless of the values of the acceptance filters. Also, if a message has an error before the end of frame, that portion of the message assembled in the MAB before the error frame will be loaded into the buffer. This mode may serve as a valuable debugging tool for a given CAN network. It should not be used in an actual system environment as the actual system will always have some bus errors and all nodes on the bus are expected to ignore them.

In Mode 1 and 2, when a programmable buffer is configured as a transmit buffer and one or more acceptance filters are associated with it, all incoming messages matching this acceptance filter criteria will be discarded. To avoid this scenario, user firmware must make sure that there are no acceptance filters associated with a buffer configured as a transmit buffer.

### 24.7.2 RECEIVE PRIORITY

When in Mode 0, RXB0 is the higher priority buffer and has two message acceptance filters associated with it. RXB1 is the lower priority buffer and has four acceptance filters associated with it. The lower number of acceptance filters makes the match on RXB0 more restrictive and implies a higher priority for that buffer. Additionally, the RXB0CON register can be configured such that if RXB0 contains a valid message and another valid message is received, an overflow error will not occur and the new message will be moved into RXB1 regardless of the acceptance criteria of RXB1. There are also two programmable acceptance filter masks available, one for each receive buffer (see Section 24.5 "CAN Message Buffers").

In Mode 1 and 2, there are a total of 16 acceptance filters available and each can be dynamically assigned to any of the receive buffers. A buffer with a lower number has higher priority. Given this, if an incoming message matches with two or more receive buffer acceptance criteria, the buffer with the lower number will be loaded with that message.

### REGISTER 25-1: CONFIG1H: CONFIGURATION REGISTER 1 HIGH (BYTE ADDRESS 300001h)

| R/P-0        | R/P-0                                                                                                                 | U-0                                                                                                                                 | U-0             | R/P-0        | R/P-1            | R/P-1      | R/P-1 |  |  |  |

|--------------|-----------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|-----------------|--------------|------------------|------------|-------|--|--|--|

| IESO         | FCMEN                                                                                                                 | _                                                                                                                                   |                 | FOSC3        | FOSC2            | FOSC1      | FOSC0 |  |  |  |

| bit 7        |                                                                                                                       |                                                                                                                                     | ·               |              |                  | •          | bit 0 |  |  |  |

| Legend:      |                                                                                                                       |                                                                                                                                     |                 |              |                  |            |       |  |  |  |

| R = Readab   | le bit                                                                                                                | P = Program                                                                                                                         | nable bit       | U = Unimpler | nented bit, read | l as '0'   |       |  |  |  |

| -n = Value w | hen device is unp                                                                                                     | programmed                                                                                                                          |                 | u = Unchange | ed from prograr  | nmed state |       |  |  |  |

|              |                                                                                                                       |                                                                                                                                     |                 |              |                  |            |       |  |  |  |

| bit 7        | IESO: Interna                                                                                                         | I/External Osc                                                                                                                      | illator Switcho | ver bit      |                  |            |       |  |  |  |

|              |                                                                                                                       | Switchover me                                                                                                                       |                 |              |                  |            |       |  |  |  |

|              | 0 = Oscillator                                                                                                        | Switchover me                                                                                                                       | ode disabled    |              |                  |            |       |  |  |  |

| bit 6        | FCMEN: Fail-                                                                                                          | FCMEN: Fail-Safe Clock Monitor Enable bit                                                                                           |                 |              |                  |            |       |  |  |  |

|              | 1 = Fail-Safe Clock Monitor enabled                                                                                   |                                                                                                                                     |                 |              |                  |            |       |  |  |  |

|              |                                                                                                                       | Clock Monitor                                                                                                                       |                 |              |                  |            |       |  |  |  |

| bit 5-4      | Unimplemen                                                                                                            | ted: Read as '                                                                                                                      | 0'              |              |                  |            |       |  |  |  |

| bit 3-0      | FOSC<3:0>:                                                                                                            | Oscillator Sele                                                                                                                     | ction bits      |              |                  |            |       |  |  |  |

|              | 11xx = External RC oscillator, CLKO function on RA6                                                                   |                                                                                                                                     |                 |              |                  |            |       |  |  |  |

|              |                                                                                                                       | 101x = External RC oscillator, CLKO function on RA6<br>1001 = Internal oscillator block, CLKO function on RA6, port function on RA7 |                 |              |                  |            |       |  |  |  |

|              |                                                                                                                       |                                                                                                                                     |                 |              |                  | NRA7       |       |  |  |  |

|              | 1000 = Internal oscillator block, port function on RA6 and RA7<br>0111 = External RC oscillator, port function on RA6 |                                                                                                                                     |                 |              |                  |            |       |  |  |  |

|              | 0111 = External RC oscillator, point initial of RAG0110 = HS oscillator, PLL enabled (Clock Frequency = 4 x FOSC1)    |                                                                                                                                     |                 |              |                  |            |       |  |  |  |

|              | 0101 = EC oscillator, port function on RA6                                                                            |                                                                                                                                     |                 |              |                  |            |       |  |  |  |

|              |                                                                                                                       | scillator, CLKO                                                                                                                     |                 |              |                  |            |       |  |  |  |

|              |                                                                                                                       | nal RC oscillat                                                                                                                     | or, CLKO fund   | tion on RA6  |                  |            |       |  |  |  |

|              | 0010 = HS os<br>0001 = XT os                                                                                          |                                                                                                                                     |                 |              |                  |            |       |  |  |  |

|              | 0001 = XT  os $0000 = LP $ os                                                                                         |                                                                                                                                     |                 |              |                  |            |       |  |  |  |

| IORLW                                 | Inclusive                             | Inclusive OR Literal with W |      |           |  |  |  |

|---------------------------------------|---------------------------------------|-----------------------------|------|-----------|--|--|--|

| Syntax:                               | IORLW k                               |                             |      |           |  |  |  |

| Operands:                             | $0 \le k \le 255$                     | 5                           |      |           |  |  |  |

| Operation: (W) .OR. $k \rightarrow W$ |                                       |                             |      |           |  |  |  |

| Status Affected:                      | N, Z                                  |                             |      |           |  |  |  |

| Encoding:                             | 0000                                  | 1001                        | kkkk | kkkk      |  |  |  |

| Description:                          | The conter<br>eight-bit lite<br>in W. |                             |      |           |  |  |  |

| Words:                                | 1                                     |                             |      |           |  |  |  |

| Cycles:                               | 1                                     | 1                           |      |           |  |  |  |

| Q Cycle Activity:                     |                                       |                             |      |           |  |  |  |

| Q1                                    | Q2                                    | Q3                          | 3    | Q4        |  |  |  |

| Decode                                | Read<br>literal 'k'                   | Proce<br>Data               |      | rite to W |  |  |  |

| Example:                              | IORLW                                 | 35h                         |      |           |  |  |  |

| Before Instruction<br>W = 9Ah         |                                       |                             |      |           |  |  |  |

| IORWF             | ORWF Inclusive OR W with f                          |                 |                      |  |  |  |  |

|-------------------|-----------------------------------------------------|-----------------|----------------------|--|--|--|--|

| Syntax:           | IORWF f                                             | {,d {,a}}       |                      |  |  |  |  |

| Operands:         | $0 \le f \le 255$<br>$d \in [0,1]$<br>$a \in [0,1]$ | d ∈ [0,1]       |                      |  |  |  |  |

| Operation:        | (W) .OR. (f) $\rightarrow$ dest                     |                 |                      |  |  |  |  |

| Status Affected:  | N, Z                                                |                 |                      |  |  |  |  |

| Encoding:         | 0001                                                | 00da ff         | ff ffff              |  |  |  |  |

| Description:      | J                                                   |                 |                      |  |  |  |  |

|                   |                                                     | set Mode" for   | details.             |  |  |  |  |

| Words:            | 1                                                   |                 |                      |  |  |  |  |

| Cycles:           | 1                                                   | 1               |                      |  |  |  |  |

| Q Cycle Activity: |                                                     |                 |                      |  |  |  |  |

| Q1                | Q2                                                  | Q3              | Q4                   |  |  |  |  |

| Decode            | Read<br>register 'f'                                | Process<br>Data | Write to destination |  |  |  |  |

#### Example:

| imple:             | IORWF          | RESULT, | Ο, | 1 |  |  |  |  |  |  |

|--------------------|----------------|---------|----|---|--|--|--|--|--|--|

| Before Instruction | on             |         |    |   |  |  |  |  |  |  |

| RESULT =<br>W =    | = 13h<br>= 91h |         |    |   |  |  |  |  |  |  |

| After Instruction  |                |         |    |   |  |  |  |  |  |  |

| RESULT =<br>W =    | = 13h<br>= 93h |         |    |   |  |  |  |  |  |  |

After Instruction BFh W =

| DC Characteristics |       | $\begin{array}{l} \mbox{Standard Operating Conditions (unless otherwise stated)} \\ \mbox{Operating temperature } -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for industrial} \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for extended} \end{array}$ |      |      |       |       |                                                                  |

|--------------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-------|-------|------------------------------------------------------------------|

| Param<br>No.       | Sym   | Characteristic                                                                                                                                                                                                                                               | Min  | Тур† | Max   | Units | Conditions                                                       |

|                    |       | Internal Program Memory<br>Programming Specifications <sup>(1)</sup>                                                                                                                                                                                         |      |      |       |       |                                                                  |

| D110               | Vpp   | Voltage on MCLR/VPP/RE3 Pin                                                                                                                                                                                                                                  | 9.00 | _    | 13.25 | V     | (Note 3)                                                         |

| D113               | IDDP  | Supply Current during<br>Programming                                                                                                                                                                                                                         | -    | _    | 10    | mA    |                                                                  |

|                    |       | Data EEPROM Memory                                                                                                                                                                                                                                           |      |      |       |       |                                                                  |

| D120               | ED    | Byte Endurance                                                                                                                                                                                                                                               | 100K | 1M   | —     | E/W   | -40°C to +85°C                                                   |