Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2010                       |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 40MHz                                                                     |

| Connectivity               | CANbus, I <sup>2</sup> C, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                               |

| Number of I/O              | 36                                                                        |

| Program Memory Size        | 32KB (16K x 16)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 1.5K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                               |

| Data Converters            | A/D 11x10b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 44-VQFN Exposed Pad                                                       |

| Supplier Device Package    | 44-QFN (8x8)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f4580-i-ml |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION. QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights.

#### Trademarks

The Microchip name and logo, the Microchip logo, dsPIC, KEELOQ, KEELOQ logo, MPLAB, PIC, PICmicro, PICSTART, rfPIC and UNI/O are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

FilterLab, Hampshire, HI-TECH C, Linear Active Thermistor, MXDEV, MXLAB, SEEVAL and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, Application Maestro, CodeGuard, dsPICDEM, dsPICDEM.net, dsPICworks, dsSPEAK, ECAN, ECONOMONITOR, FanSense, HI-TIDE, In-Circuit Serial Programming, ICSP, Mindi, MiWi, MPASM, MPLAB Certified logo, MPLIB, MPLINK, mTouch, Octopus, Omniscient Code Generation, PICC, PICC-18, PICDEM, PICDEM.net, PICkit, PICtail, PIC<sup>32</sup> logo, REAL ICE, rfLAB, Select Mode, Total Endurance, TSHARC, UniWinDriver, WiperLock and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

$\ensuremath{\mathsf{SQTP}}$  is a service mark of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their respective companies.

© 2009, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

# QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV ISO/TS 16949:2002

Microchip received ISO/TS-16949:2002 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEELOQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001:2000 certified.

## **Table of Contents**

| 1.0  | Device Overview                                              | 9   |

|------|--------------------------------------------------------------|-----|

| 2.0  | Guidelines for Getting Started with PIC18F Microcontrollers  |     |

| 3.0  | Oscillator Configurations                                    |     |

| 4.0  | Power-Managed Modes                                          |     |

| 5.0  | Reset                                                        |     |

| 6.0  | Memory Organization                                          |     |

| 7.0  | Flash Program Memory                                         | 101 |

| 8.0  | Data EEPROM Memory                                           | 111 |

| 9.0  | 8 x 8 Hardware Multiplier                                    | 117 |

| 10.0 | Interrupts                                                   | 119 |

| 11.0 | I/O Ports                                                    | 135 |

| 12.0 | Timer0 Module                                                | 151 |

| 13.0 | Timer1 Module                                                | 155 |

| 14.0 | Timer2 Module                                                |     |

|      | Timer3 Module                                                |     |

|      | Capture/Compare/PWM (CCP) Modules                            |     |

| 17.0 | Enhanced Capture/Compare/PWM (ECCP) Module                   |     |

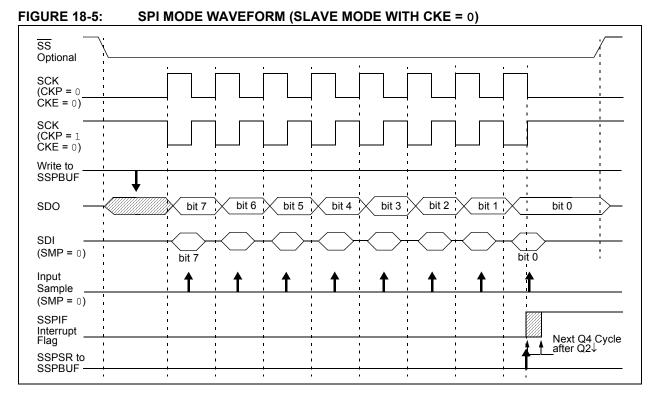

| 18.0 | Master Synchronous Serial Port (MSSP) Module                 |     |

| 19.0 | Enhanced Universal Synchronous Receiver Transmitter (EUSART) |     |

| 20.0 | 10-Bit Analog-to-Digital Converter (A/D) Module              |     |

| 21.0 | Comparator Module                                            |     |

| 22.0 | Comparator Voltage Reference Module                          |     |

| 23.0 | High/Low-Voltage Detect (HLVD)                               |     |

|      | ECAN Module                                                  |     |

| 25.0 | Special Features of the CPU                                  |     |

| 26.0 |                                                              |     |

| 27.0 | Development Support                                          |     |

|      | Electrical Characteristics                                   |     |

|      | Packaging Information                                        |     |

|      | endix A: Revision History                                    |     |

|      | endix B: Device Differences                                  |     |

| •••  | endix C: Conversion Considerations                           |     |

|      | endix D: Migration from Baseline to Enhanced Devices         |     |

|      | endix E: Migration From Mid-Range to Enhanced Devices        |     |

|      | endix F: Migration From High-End to Enhanced Devices         |     |

|      | Microchip Web Site                                           |     |

|      | omer Change Notification Service                             |     |

|      | omer Support                                                 |     |

|      | ler Response                                                 |     |

| PIC1 | 8F2480/2580/4480/4580 Product Identification System          |     |

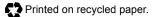

2: OSC1/CLKI and OSC2/CLKO are only available in select oscillator modes and when these pins are not being used as digital I/O. Refer to Section 3.0 "Oscillator Configurations" for additional information.

# TABLE 3-2:CAPACITOR SELECTION FOR<br/>CRYSTAL OSCILLATOR

| Crystal | Typical Capa<br>Tes                                                                                     |                                                                                                                                                                                                                    |

|---------|---------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Fieq    | C1                                                                                                      | C2                                                                                                                                                                                                                 |

| 32 kHz  | 33 pF                                                                                                   | 33 pF                                                                                                                                                                                                              |

| 200 kHz | 15 pF                                                                                                   | 15 pF                                                                                                                                                                                                              |

| 1 MHz   | 33 pF                                                                                                   | 33 pF                                                                                                                                                                                                              |

| 4 MHz   | 27 pF                                                                                                   | 27 pF                                                                                                                                                                                                              |

| 4 MHz   | 27 pF                                                                                                   | 27 pF                                                                                                                                                                                                              |

| 8 MHz   | 22 pF                                                                                                   | 22 pF                                                                                                                                                                                                              |

| 20 MHz  | 15 pF                                                                                                   | 15 pF                                                                                                                                                                                                              |

|         | Freq           32 kHz           200 kHz           1 MHz           4 MHz           4 MHz           8 MHz | Crystal<br>Freq         Tes           32 kHz         33 pF           200 kHz         15 pF           1 MHz         33 pF           4 MHz         27 pF           4 MHz         27 pF           8 MHz         22 pF |

### Capacitor values are for design guidance only.

These capacitors were tested with the crystals listed below for basic start-up and operation. **These values are not optimized.**

Different capacitor values may be required to produce acceptable oscillator operation. The user should test the performance of the oscillator over the expected VDD and temperature range for the application.

See the notes following this table for additional information.

| Crysta  | als Used: |

|---------|-----------|

| 32 kHz  | 4 MHz     |

| 200 kHz | 8 MHz     |

| 1 MHz   | 20 MHz    |

- Note 1: Higher capacitance increases the stability of the oscillator but also increases the start-up time.

- When operating below 3V VDD, or when using certain ceramic resonators at any voltage, it may be necessary to use the HS mode or switch to a crystal oscillator.

- 3: Since each resonator/crystal has its own characteristics, the user should consult the resonator/crystal manufacturer for appropriate values of external components.

- 4: Rs may be required to avoid overdriving crystals with low drive level specification.

- Always verify oscillator performance over the VDD and temperature range that is expected for the application.

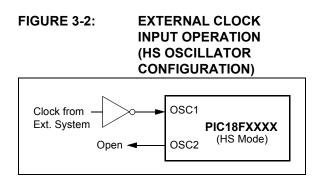

An external clock source may also be connected to the OSC1 pin in the HS mode, as shown in Figure 3-2.

# 3.3 External Clock Input

The EC and ECIO Oscillator modes require an external clock source to be connected to the OSC1 pin. There is no oscillator start-up time required after a Power-on Reset or after an exit from Sleep mode.

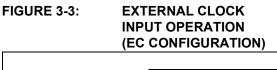

In the EC Oscillator mode, the oscillator frequency divided by 4 is available on the OSC2 pin. This signal may be used for test purposes or to synchronize other logic. Figure 3-3 shows the pin connections for the EC Oscillator mode.

The ECIO Oscillator mode functions like the EC mode, except that the OSC2 pin becomes an additional general purpose I/O pin. The I/O pin becomes bit 6 of PORTA (RA6). Figure 3-4 shows the pin connections for the ECIO Oscillator mode.

# 4.0 POWER-MANAGED MODES

PIC18F2480/2580/4480/4580 devices offer a total of seven operating modes for more efficient power management. These modes provide a variety of options for selective power conservation in applications where resources may be limited (i.e., battery-powered devices).

There are three categories of power-managed modes:

- Run modes

- Idle modes

- Sleep mode

These categories define which portions of the device are clocked, and sometimes, what speed. The Run and Idle modes may use any of the three available clock sources (primary, secondary or internal oscillator block); the Sleep mode does not use a clock source.

The power-managed modes include several power-saving features offered on previous PIC<sup>®</sup> devices. One is the clock switching feature, offered in other PIC18 devices, allowing the controller to use the Timer1 oscillator in place of the primary oscillator. Also included is the Sleep mode, offered by all PIC devices, where all device clocks are stopped.

### 4.1 Selecting Power-Managed Modes

Selecting a power-managed mode requires two decisions: if the CPU is to be clocked or not and the selection of a clock source. The IDLEN bit (OSCCON<7>) controls CPU clocking, while the SCS<1:0> bits (OSCCON<1:0>) select the clock source. The individual modes, bit settings, clock sources and affected modules are summarized in Table 4-1.

### 4.1.1 CLOCK SOURCES

The SCS<1:0> bits allow the selection of one of three clock sources for power-managed modes. They are:

- The primary clock, as defined by the FOSC<3:0> Configuration bits

- The secondary clock (the Timer1 oscillator)

- The internal oscillator block (for RC modes)

### 4.1.2 ENTERING POWER-MANAGED MODES

Switching from one power-managed mode to another begins by loading the OSCCON register. The SCS<1:0> bits select the clock source and determine which Run or Idle mode is to be used. Changing these bits causes an immediate switch to the new clock source, assuming that it is running. The switch may also be subject to clock transition delays. These are discussed in **Section 4.1.3 "Clock Transitions and Status Indicators"** and subsequent sections.

Entry to the power-managed Idle or Sleep modes is triggered by the execution of a SLEEP instruction. The actual mode that results depends on the status of the IDLEN bit.

Depending on the current mode and the mode being switched to, a change to a power-managed mode does not always require setting all of these bits. Many transitions may be done by changing the oscillator select bits, or changing the IDLEN bit, prior to issuing a SLEEP instruction. If the IDLEN bit is already configured correctly, it may only be necessary to perform a SLEEP instruction to switch to the desired mode.

| IADLE 4-1: | POWER                | K-INIANAGED IV | IODE3   |             |                                                                                                              |

|------------|----------------------|----------------|---------|-------------|--------------------------------------------------------------------------------------------------------------|

| Mada       | OSCC                 | ON<7,1:0>      | Modul   | e Clocking  | Augilable Clask and Ossillator Source                                                                        |

| Mode       | IDLEN <sup>(1)</sup> | SCS<1:0>       | CPU     | Peripherals | Available Clock and Oscillator Source                                                                        |

| Sleep      | 0                    | N/A            | Off     | Off         | None – All clocks are disabled                                                                               |

| PRI_RUN    | N/A                  | 00             | Clocked | Clocked     | Primary – LP, XT, HS, HSPLL, RC, EC, INTRC <sup>(2)</sup> :<br>This is the normal full-power execution mode. |

| SEC_RUN    | N/A                  | 01             | Clocked | Clocked     | Secondary – Timer1 Oscillator                                                                                |

| RC_RUN     | N/A                  | 1x             | Clocked | Clocked     | Internal Oscillator Block <sup>(2)</sup>                                                                     |

| PRI_IDLE   | 1                    | 00             | Off     | Clocked     | Primary – LP, XT, HS, HSPLL, RC, EC                                                                          |

| SEC_IDLE   | 1                    | 01             | Off     | Clocked     | Secondary – Timer1 Oscillator                                                                                |

| RC_IDLE    | 1                    | 1x             | Off     | Clocked     | Internal Oscillator Block <sup>(2)</sup>                                                                     |

TABLE 4-1: POWER-MANAGED MODES

Note 1: IDLEN reflects its value when the **SLEEP** instruction is executed.

2: Includes INTOSC and INTOSC postscaler, as well as the INTRC source.

### 4.4.3 RC\_IDLE MODE

In RC\_IDLE mode, the CPU is disabled but the peripherals continue to be clocked from the internal oscillator block using the INTOSC multiplexer. This mode allows for controllable power conservation during Idle periods.

From RC\_RUN, this mode is entered by setting the IDLEN bit and executing a SLEEP instruction. If the device is in another Run mode, first set IDLEN, then set the SCS1 bit and execute SLEEP. Although its value is ignored, it is recommended that SCS0 also be cleared; this is to maintain software compatibility with future devices. The INTOSC multiplexer may be used to select a higher clock frequency, by modifying the IRCF bits, before executing the SLEEP instruction. When the clock source is switched to the INTOSC multiplexer, the primary oscillator is shut down and the OSTS bit is cleared.

If the IRCF bits are set to any non-zero value or the INTSRC bit is set, the INTOSC output is enabled. The IOFS bit becomes set, after the INTOSC output becomes stable, after an interval of TIOBST (parameter 39, Table 28-10). Clocks to the peripherals continue while the INTOSC source stabilizes. If the IRCF bits were previously at a non-zero value, or INTSRC was set before the SLEEP instruction was executed and the INTOSC source was already stable, the IOFS bit will remain set. If the IRCF bits and INTSRC are all clear, the INTOSC output will not be enabled, the IOFS bit will remain clear and there will be no indication of the current clock source.

When a wake event occurs, the peripherals continue to be clocked from the INTOSC multiplexer. After a delay of TCSD following the wake event, the CPU begins executing code being clocked by the INTOSC multiplexer. The IDLEN and SCS bits are not affected by the wake-up. The INTRC source will continue to run if either the WDT or the Fail-Safe Clock Monitor is enabled.

### 4.5 Exiting Idle and Sleep Modes

An exit from Sleep mode or any of the Idle modes is triggered by an interrupt, a Reset or a WDT time-out. This section discusses the triggers that cause exits from power-managed modes. The clocking subsystem actions are discussed in each of the power-managed modes (see Section 4.2 "Run Modes", Section 4.3 "Sleep Mode" and Section 4.4 "Idle Modes").

### 4.5.1 EXIT BY INTERRUPT

Any of the available interrupt sources can cause the device to exit from an Idle mode or the Sleep mode to a Run mode. To enable this functionality, an interrupt source must be enabled by setting its enable bit in one of the INTCON or PIE registers. The exit sequence is initiated when the corresponding interrupt flag bit is set.

On all exits from Idle or Sleep modes by interrupt, code execution branches to the interrupt vector if the GIE/GIEH bit (INTCON<7>) is set. Otherwise, code execution continues or resumes without branching (see Section 10.0 "Interrupts").

A fixed delay of interval, TCSD, following the wake event is required when leaving Sleep and Idle modes. This delay is required for the CPU to prepare for execution. Instruction execution resumes on the first clock cycle following this delay.

### 4.5.2 EXIT BY WDT TIME-OUT

A WDT time-out will cause different actions depending on which power-managed mode the device is in when the time-out occurs.

If the device is not executing code (all Idle modes and Sleep mode), the time-out will result in an exit from the power-managed mode (see Section 4.2 "Run Modes" and Section 4.3 "Sleep Mode"). If the device is executing code (all Run modes), the time-out will result in a WDT Reset (see Section 25.2 "Watchdog Timer (WDT)").

The WDT timer and postscaler are cleared by executing a SLEEP or CLRWDT instruction, the loss of a currently selected clock source (if the Fail-Safe Clock Monitor is enabled) and modifying the IRCF bits in the OSCCON register if the internal oscillator block is the device clock source.

### 4.5.3 EXIT BY RESET

Normally, the device is held in Reset by the Oscillator Start-up Timer (OST) until the primary clock becomes ready. At that time, the OSTS bit is set and the device begins executing code. If the internal oscillator block is the new clock source, the IOFS bit is set instead.

The exit delay time from Reset to the start of code execution depends on both the clock sources before and after the wake-up and the type of oscillator if the new clock source is the primary clock. Exit delays are summarized in Table 4-2.

Code execution can begin before the primary clock becomes ready. If either the Two-Speed Start-up (see **Section 25.3 "Two-Speed Start-up"**) or Fail-Safe Clock Monitor (see **Section 25.4 "Fail-Safe Clock Monitor**") is enabled, the device may begin execution as soon as the Reset source has cleared. Execution is clocked by the INTOSC multiplexer driven by the internal oscillator block. Execution is clocked by the internal oscillator block until either the primary clock becomes ready or a power-managed mode is entered before the primary clock becomes ready; the primary clock is then shut down.

| IABLE 5-4: |      |         |        |      | DITIONS FOR ALL                    |                                                                  |                                 |

|------------|------|---------|--------|------|------------------------------------|------------------------------------------------------------------|---------------------------------|

| Register   | Арг  | olicabl | e Devi | ces  | Power-on Reset,<br>Brown-out Reset | MCLR Resets,<br>WDT Reset,<br>RESET Instruction,<br>Stack Resets | Wake-up via WDT<br>or Interrupt |

| TOSU       | 2480 | 2580    | 4480   | 4580 | 0 0000                             | 0 0000                                                           | 0 uuuu <b>(3)</b>               |

| TOSH       | 2480 | 2580    | 4480   | 4580 | 0000 0000                          | 0000 0000                                                        | uuuu uuuu <b>(3)</b>            |

| TOSL       | 2480 | 2580    | 4480   | 4580 | 0000 0000                          | 0000 0000                                                        | uuuu uuuu <b>(3)</b>            |

| STKPTR     | 2480 | 2580    | 4480   | 4580 | 00-0 0000                          | uu-0 0000                                                        | uu-u uuuu <b>(3)</b>            |

| PCLATU     | 2480 | 2580    | 4480   | 4580 | 0 0000                             | 0 0000                                                           | u uuuu                          |

| PCLATH     | 2480 | 2580    | 4480   | 4580 | 0000 0000                          | 0000 0000                                                        | սսսս սսսս                       |

| PCL        | 2480 | 2580    | 4480   | 4580 | 0000 0000                          | 0000 0000                                                        | PC + 2 <sup>(2)</sup>           |

| TBLPTRU    | 2480 | 2580    | 4480   | 4580 | 00 0000                            | 00 0000                                                          | uu uuuu                         |

| TBLPTRH    | 2480 | 2580    | 4480   | 4580 | 0000 0000                          | 0000 0000                                                        | սսսս սսսս                       |

| TBLPTRL    | 2480 | 2580    | 4480   | 4580 | 0000 0000                          | 0000 0000                                                        | սսսս սսսս                       |

| TABLAT     | 2480 | 2580    | 4480   | 4580 | 0000 0000                          | 0000 0000                                                        | սսսս սսսս                       |

| PRODH      | 2480 | 2580    | 4480   | 4580 | XXXX XXXX                          | uuuu uuuu                                                        | սսսս սսսս                       |

| PRODL      | 2480 | 2580    | 4480   | 4580 | XXXX XXXX                          | นนนน นนนน                                                        | սսսս սսսս                       |

| INTCON     | 2480 | 2580    | 4480   | 4580 | 0000 000x                          | 0000 000u                                                        | uuuu uuuu <b>(1)</b>            |

| INTCON2    | 2480 | 2580    | 4480   | 4580 | 1111 -1-1                          | 1111 -1-1                                                        | uuuu -u-u <b>(1)</b>            |

| INTCON3    | 2480 | 2580    | 4480   | 4580 | 11-0 0-00                          | 11-0 0-00                                                        | uu-u u-uu <b>(1)</b>            |

| INDF0      | 2480 | 2580    | 4480   | 4580 | N/A                                | N/A                                                              | N/A                             |

| POSTINC0   | 2480 | 2580    | 4480   | 4580 | N/A                                | N/A                                                              | N/A                             |

| POSTDEC0   | 2480 | 2580    | 4480   | 4580 | N/A                                | N/A                                                              | N/A                             |

| PREINC0    | 2480 | 2580    | 4480   | 4580 | N/A                                | N/A                                                              | N/A                             |

| PLUSW0     | 2480 | 2580    | 4480   | 4580 | N/A                                | N/A                                                              | N/A                             |

| FSR0H      | 2480 | 2580    | 4480   | 4580 | 0000                               | 0000                                                             | uuuu                            |

| FSR0L      | 2480 | 2580    | 4480   | 4580 | XXXX XXXX                          | นนนน นนนน                                                        | սսսս սսսս                       |

| WREG       | 2480 | 2580    | 4480   | 4580 | XXXX XXXX                          | uuuu uuuu                                                        | սսսս սսսս                       |

| INDF1      | 2480 | 2580    | 4480   | 4580 | N/A                                | N/A                                                              | N/A                             |

| POSTINC1   | 2480 | 2580    | 4480   | 4580 | N/A                                | N/A                                                              | N/A                             |

| POSTDEC1   | 2480 | 2580    | 4480   | 4580 | N/A                                | N/A                                                              | N/A                             |

| PREINC1    | 2480 | 2580    | 4480   | 4580 | N/A                                | N/A                                                              | N/A                             |

| PLUSW1     | 2480 | 2580    | 4480   | 4580 | N/A                                | N/A                                                              | N/A                             |

| FSR1H      | 2480 | 2580    | 4480   | 4580 | 0000                               | 0000                                                             | uuuu                            |

| FSR1L      | 2480 | 2580    | 4480   | 4580 | XXXX XXXX                          | นนนน นนนน                                                        | սսսս սսսս                       |

### TABLE 5-4: INITIALIZATION CONDITIONS FOR ALL REGISTERS

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition. Shaded cells indicate conditions do not apply for the designated device.

Note 1: One or more bits in the INTCONx or PIRx registers will be affected (to cause wake-up).

2: When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the PC is loaded with the interrupt vector (0008h or 0018h).

**3:** When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the TOSU, TOSH and TOSL are updated with the current value of the PC. The STKPTR is modified to point to the next location in the hardware stack.

4: See Table 5-3 for Reset value for specific condition.

**5:** Bits 6 and 7 of PORTA, LATA and TRISA are enabled, depending on the oscillator mode selected. When not enabled as PORTA pins, they are disabled and read '0'.

6: This register reads all '0's until ECAN<sup>™</sup> technology is set up in Mode 1 or Mode 2.

### 6.5 Program Memory and the Extended Instruction Set

The operation of program memory is unaffected by the use of the extended instruction set.

Enabling the extended instruction set adds eight additional two-word commands to the existing PIC18 instruction set: ADDFSR, ADDULNK, CALLW, MOVSF, MOVSS, PUSHL, SUBFSR and SUBULNK. These instructions are executed as described in Section 6.2.4 "Two-Word Instructions".

# 6.6 Data Memory and the Extended Instruction Set

Enabling the PIC18 extended instruction set (XINST Configuration bit = 1) significantly changes certain aspects of data memory and its addressing. Specifically, the use of the Access Bank for many of the core PIC18 instructions is different. This is due to the introduction of a new addressing mode for the data memory space. This mode also alters the behavior of Indirect Addressing using FSR2 and its associated operands.

What does not change is just as important. The size of the data memory space is unchanged, as well as its linear addressing. The SFR map remains the same. Core PIC18 instructions can still operate in both Direct and Indirect Addressing mode; inherent and literal instructions do not change at all. Indirect Addressing with FSR0 and FSR1 also remains unchanged.

### 6.6.1 INDEXED ADDRESSING WITH LITERAL OFFSET

Enabling the PIC18 extended instruction set changes the behavior of Indirect Addressing using the FSR2 register pair and its associated file operands. Under the proper conditions, instructions that use the Access Bank – that is, most bit-oriented and byte-oriented – instructions – can invoke a form of Indexed Addressing using an offset specified in the instruction. This special addressing mode is known as Indexed Addressing with Literal Offset or Indexed Literal Offset mode. When using the extended instruction set, this addressing mode requires the following:

- The use of the Access Bank is forced ('a' = 0); and

- The file address argument is less than or equal to 5Fh.

Under these conditions, the file address of the instruction is not interpreted as the lower byte of an address (used with the BSR in Direct Addressing), or as an 8-bit address in the Access Bank. Instead, the value is interpreted as an offset value to an Address Pointer, specified by FSR2. The offset and the contents of FSR2 are added to obtain the target address of the operation.

### 6.6.2 INSTRUCTIONS AFFECTED BY INDEXED LITERAL OFFSET MODE

Any of the core PIC18 instructions that can use Direct Addressing are potentially affected by the Indexed Literal Offset Addressing mode. This includes all byte-oriented and bit-oriented instructions, or almost one-half of the standard PIC18 instruction set. Instructions that only use Inherent or Literal Addressing modes are unaffected.

Additionally, byte-oriented and bit-oriented instructions are not affected if they use the Access Bank (Access RAM bit is '1'), or include a file address of 60h or above. Instructions meeting these criteria will continue to execute as before. A comparison of the different possible addressing modes when the extended instruction set is enabled in shown in Figure 6-9.

Those who desire to use byte-oriented or bit-oriented instructions in the Indexed Literal Offset mode should note the changes to assembler syntax for this mode. This is described in more detail in **Section 26.2.1** "Extended Instruction Syntax".

# 9.0 8 x 8 HARDWARE MULTIPLIER

### 9.1 Introduction

All PIC18 devices include an 8 x 8 hardware multiplier as part of the ALU. The multiplier performs an unsigned operation and yields a 16-bit result that is stored in the product register pair, PRODH:PRODL. The multiplier's operation does not affect any flags in the STATUS register.

Making multiplication a hardware operation allows it to be completed in a single instruction cycle. This has the advantages of higher computational throughput and reduced code size for multiplication algorithms and allows the PIC18 devices to be used in many applications previously reserved for digital signal processors. A comparison of various hardware and software multiply operations, along with the savings in memory and execution time, is shown in Table 9-1.

### 9.2 Operation

Example 9-1 shows the instruction sequence for an 8 x 8 unsigned multiplication. Only one instruction is required when one of the arguments is already loaded in the WREG register.

Example 9-2 shows the sequence to do an 8 x 8 signed multiplication. To account for the signed bits of the arguments, each argument's Most Significant bit (MSb) is tested and the appropriate subtractions are done.

### EXAMPLE 9-1: 8 x 8 UNSIGNED MULTIPLY ROUTINE

| MOVF  | ARG1, W | ;                |

|-------|---------|------------------|

| MULWF | ARG2    | ; ARG1 * ARG2 -> |

|       |         | ; PRODH:PRODL    |

|       |         |                  |

# EXAMPLE 9-2: 8 x 8 SIGNED

|       |          | MULTIPLY ROUTINE |  |

|-------|----------|------------------|--|

| MOVF  | ARG1, W  |                  |  |

| MULWF | ARG2     | ; ARG1 * ARG2 -> |  |

|       |          | ; PRODH:PRODL    |  |

| BTFSC | ARG2, SB | ; Test Sign Bit  |  |

| SUBWF | PRODH, F | ; PRODH = PRODH  |  |

|       |          | ; – ARG1         |  |

| MOVF  | ARG2, W  |                  |  |

| BTFSC | ARG1, SB | ; Test Sign Bit  |  |

| SUBWF | PRODH, F | ; PRODH = PRODH  |  |

|       |          | ; – ARG2         |  |

|       |          |                  |  |

|                  |                           | Program           | Cycles | Time     |          |              |  |

|------------------|---------------------------|-------------------|--------|----------|----------|--------------|--|

| Routine          | Multiply Method           | Memory<br>(Words) | (Max)  | @ 40 MHz | @ 10 MHz | @ 4 MHz      |  |

| 9 x 9 uppignod   | Without hardware multiply | 13                | 69     | 6.9 μs   | 27.6 μs  | 69 μs        |  |

| 8 x 8 unsigned   | Hardware multiply         | 1                 | 1      | 100 ns   | 400 ns   | 1 μs         |  |

| 9 v 9 signed     | Without hardware multiply | 33                | 91     | 9.1 μs   | 36.4 μs  | 91 μs        |  |

| 8 x 8 signed     | Hardware multiply         | 6                 | 6      | 600 ns   | 2.4 μs   | 6 μ <b>s</b> |  |

| 10 × 10 unsigned | Without hardware multiply | 21                | 242    | 24.2 μs  | 96.8 μs  | 242 μs       |  |

| 16 x 16 unsigned | Hardware multiply         | 28                | 28     | 2.8 μs   | 11.2 μs  | 28 μs        |  |

| 16 v 16 signed   | Without hardware multiply | 52                | 254    | 25.4 μs  | 102.6 μs | 254 μs       |  |

| 16 x 16 signed   | Hardware multiply         | 35                | 40     | 4.0 μs   | 16.0 μs  | 40 μs        |  |

### TABLE 9-1: PERFORMANCE COMPARISON FOR VARIOUS MULTIPLY OPERATIONS

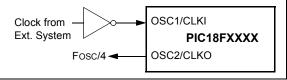

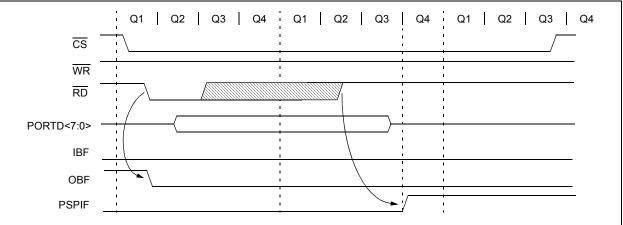

### FIGURE 11-4: PARALLEL SLAVE PORT READ WAVEFORMS

### TABLE 11-11: REGISTERS ASSOCIATED WITH PARALLEL SLAVE PORT

| Name                 | Bit 7       | Bit 6          | Bit 5   | Bit 4   | Bit 3 | Bit 2      | Bit 1        | Bit 0  | Reset<br>Values<br>on Page: |

|----------------------|-------------|----------------|---------|---------|-------|------------|--------------|--------|-----------------------------|

| PORTD <sup>(1)</sup> | RD7         | RD6            | RD5     | RD4     | RD3   | RD2        | RD1          | RD0    | 58                          |

| LATD <sup>(1)</sup>  | LATD Output | ut Latch Regis | ster    |         |       |            |              |        | 58                          |

| TRISD <sup>(1)</sup> | PORTD Da    | ta Direction R | egister |         |       |            |              |        | 58                          |

| PORTE <sup>(1)</sup> | _           |                | _       | —       | RE3   | RE2        | RE1          | RE0    | 58                          |

| LATE <sup>(1)</sup>  | _           | —              | _       | _       | _     | LATE Outpu | ut Latch Reg | ister  | 58                          |

| TRISE <sup>(1)</sup> | IBF         | OBF            | IBOV    | PSPMODE | _     | TRISE2     | TRISE1       | TRISE0 | 58                          |

| INTCON               | GIE/GIEH    | PEIE/GIEL      | TMR0IE  | INTOIE  | RBIE  | TMR0IF     | INT0IF       | RBIF   | 55                          |

| PIR1                 | PSPIF       | ADIF           | RCIF    | TXIF    | SSPIF | CCP1IF     | TMR2IF       | TMR1IF | 58                          |

| PIE1                 | PSPIE       | ADIE           | RCIE    | TXIE    | SSPIE | CCP1IE     | TMR2IE       | TMR1IE | 58                          |

| IPR1                 | PSPIP       | ADIP           | RCIP    | TXIP    | SSPIP | CCP1IP     | TMR2IP       | TMR1IP | 58                          |

| ADCON1               |             |                | VCFG1   | VCFG0   | PCFG3 | PCFG2      | PCFG1        | PCFG0  | 56                          |

| CMCON <sup>(1)</sup> | C2OUT       | C10UT          | C2INV   | C1INV   | CIS   | CM2        | CM1          | CM0    | 57                          |

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used by the Parallel Slave Port.

Note 1: These registers are available on PIC18F4X80 devices only.

# 13.0 TIMER1 MODULE

The Timer1 timer/counter module incorporates these features:

- Software-selectable operation as a 16-bit timer or counter

- Readable and writable 8-bit registers (TMR1H and TMR1L)

- Selectable clock source (internal or external) with device clock or Timer1 oscillator internal options

- Interrupt-on-overflow

- Module Reset on CCP Special Event Trigger

- Device clock status flag (T1RUN)

A simplified block diagram of the Timer1 module is shown in Figure 13-1. A block diagram of the module's operation in Read/Write mode is shown in Figure 13-2.

The module incorporates its own low-power oscillator to provide an additional clocking option. The Timer1 oscillator can also be used as a low-power clock source for the microcontroller in power-managed operation.

Timer1 can also be used to provide Real-Time Clock (RTC) functionality to applications with only a minimal addition of external components and code overhead.

Timer1 is controlled through the T1CON Control register (Register 13-1). It also contains the Timer1 Oscillator Enable bit (T1OSCEN). Timer1 can be enabled or disabled by setting or clearing control bit, TMR1ON (T1CON<0>).

| R/W-0 | R-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0  | R/W-0  | R/W-0  |

|-------|-------|---------|---------|---------|--------|--------|--------|

| RD16  | T1RUN | T1CKPS1 | T1CKPS0 | T1OSCEN | T1SYNC | TMR1CS | TMR10N |

| bit 7 |       |         |         |         |        |        | bit 0  |

### REGISTER 13-1: T1CON: TIMER1 CONTROL REGISTER

| Legend:                               | <b>b</b> :4      | $\lambda = \lambda / \pi + \pi$ | l l – l laimalana arta d bit                                 | read as (0)        |

|---------------------------------------|------------------|---------------------------------------------------------------------------------|--------------------------------------------------------------|--------------------|

| R = Readable bit<br>-n = Value at POR |                  | W = Writable bit                                                                | U = Unimplemented bit,                                       |                    |

| -n = Value at I                       | POR              | '1' = Bit is set                                                                | '0' = Bit is cleared                                         | x = Bit is unknown |

| h:+ 7                                 | <b>DD40</b> , 40 | -Bit Read/Write Mode Enab                                                       |                                                              |                    |

| bit 7                                 |                  |                                                                                 |                                                              |                    |

|                                       |                  |                                                                                 | mer1 in one 16-bit operation<br>mer1 in two 8-bit operations |                    |

| bit 6                                 |                  | Timer1 System Clock Status                                                      | •                                                            |                    |

|                                       |                  | ce clock is derived from Tim                                                    |                                                              |                    |

|                                       |                  | ce clock is derived from and                                                    |                                                              |                    |

| bit 5-4                               | T1CKPS           | <1:0>: Timer1 Input Clock F                                                     | Prescale Select bits                                         |                    |

|                                       | 11 <b>= 1:8</b>  | Prescale value                                                                  |                                                              |                    |

|                                       |                  | Prescale value                                                                  |                                                              |                    |

|                                       |                  | Prescale value                                                                  |                                                              |                    |

|                                       |                  | Prescale value                                                                  |                                                              |                    |

| bit 3                                 |                  | N: Timer1 Oscillator Enable                                                     | bit                                                          |                    |

|                                       |                  | r1 oscillator is enabled                                                        |                                                              |                    |

|                                       |                  | er1 oscillator is shut off                                                      | resistor are turned off to elimin                            | ate power drain    |

| bit 2                                 |                  |                                                                                 | ut Synchronization Select bit                                |                    |

| DIL Z                                 |                  |                                                                                 | at Synchronization Select bit                                |                    |

|                                       |                  | ot synchronize external cloc                                                    | k input                                                      |                    |

|                                       |                  | hronize external clock input                                                    |                                                              |                    |

|                                       |                  | IR1CS = 0:                                                                      |                                                              |                    |

|                                       | This bit is      | ignored. Timer1 uses the in                                                     | nternal clock when TMR1CS =                                  | 0.                 |

| bit 1                                 | TMR1CS           | : Timer1 Clock Source Sele                                                      | ect bit                                                      |                    |

|                                       | 1 = Exte         | rnal clock from pin RC0/T10                                                     | DSO/T13CKI (on the rising edg                                | je)                |

|                                       | 0 = Inter        | nal clock (Fosc/4)                                                              |                                                              |                    |

| bit 0                                 | TMR10N           | I: Timer1 On bit                                                                |                                                              |                    |

|                                       |                  | oles Timer1                                                                     |                                                              |                    |

|                                       | 0 = Stop         | s Timer1                                                                        |                                                              |                    |

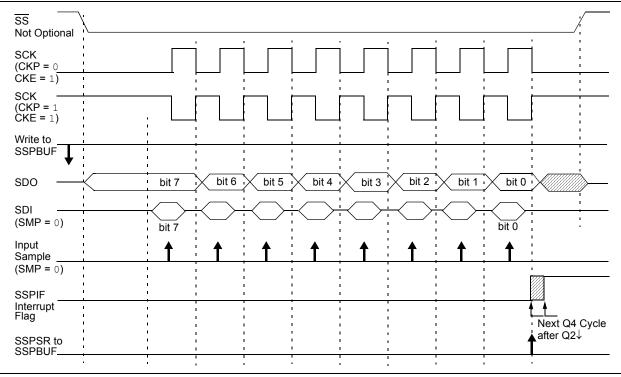

## FIGURE 18-6: SPI MODE WAVEFORM (SLAVE MODE WITH CKE = 1)

### 18.4.10 I<sup>2</sup>C MASTER MODE TRANSMISSION

Transmission of a data byte, a 7-bit address or the other half of a 10-bit address is accomplished by simply writing a value to the SSPBUF register. This action will set the Buffer Full flag bit, BF, and allow the Baud Rate Generator to begin counting and start the next transmission. Each bit of address/data will be shifted out onto the SDA pin after the falling edge of SCL is asserted (see data hold time specification parameter 106). SCL is held low for one Baud Rate Generator rollover count (TBRG). Data should be valid before SCL is released high (see data setup time specification parameter 107). When the SCL pin is released high, it is held that way for TBRG. The data on the SDA pin must remain stable for that duration and some hold time after the next falling edge of SCL. After the eighth bit is shifted out (the falling edge of the eighth clock), the BF flag is cleared and the master releases SDA. This allows the slave device being addressed to respond with an ACK bit during the ninth bit time if an address match occurred, or if data was received properly. The status of ACK is written into the ACKDT bit on the falling edge of the ninth clock. If the master receives an Acknowledge, the Acknowledge status bit, ACKSTAT, is cleared. If not, the bit is set. After the ninth clock, the SSPIF bit is set and the master clock (Baud Rate Generator) is suspended until the next data byte is loaded into the SSPBUF, leaving SCL low and SDA unchanged (Figure 18-21).

After the write to the SSPBUF, each bit of address will be shifted out on the falling edge of SCL until all seven address bits and the R/W bit are completed. On the falling edge of the eighth clock, the master will deassert the SDA pin, allowing the slave to respond with an Acknowledge. On the falling edge of the ninth clock, the master will sample the SDA pin to see if the address was recognized by a slave. The status of the ACK bit is loaded into the ACKSTAT status bit (SSPCON2<6>). Following the falling edge of the ninth clock transmission of the address, the SSPIF flag is set, the BF flag is cleared and the Baud Rate Generator is turned off until another write to the SSPBUF takes place, holding SCL low and allowing SDA to float.

### 18.4.10.1 BF Status Flag

In Transmit mode, the BF bit (SSPSTAT<0>) is set when the CPU writes to SSPBUF and is cleared when all 8 bits are shifted out.

### 18.4.10.2 WCOL Status Flag

If the user writes the SSPBUF when a transmit is already in progress (i.e., SSPSR is still shifting out a data byte), the WCOL is set and the contents of the buffer are unchanged (the write doesn't occur).

WCOL must be cleared in software.

### 18.4.10.3 ACKSTAT Status Flag

In Transmit mode, the ACKSTAT bit (SSPCON2<6>) is cleared when the slave has sent an Acknowledge  $(\overline{ACK} = 0)$  and is set when the slave does not Acknowledge  $(\overline{ACK} = 1)$ . A slave sends an Acknowledge when it has recognized its address (including a general call), or when the slave has properly received its data.

### 18.4.11 I<sup>2</sup>C MASTER MODE RECEPTION

Master mode reception is enabled by programming the Receive Enable bit, RCEN (SSPCON2<3>).

Note: The MSSP module must be in an Idle state before the RCEN bit is set or the RCEN bit will be disregarded.

The Baud Rate Generator begins counting and on each rollover, the state of the SCL pin changes (high-to-low/ low-to-high) and data is shifted into the SSPSR. After the falling edge of the eighth clock, the receive enable flag is automatically cleared, the contents of the SSPSR are loaded into the SSPBUF, the BF flag bit is set, the SSPIF flag bit is set and the Baud Rate Generator is suspended from counting, holding SCL low. The MSSP is now in Idle state awaiting the next command. When the buffer is read by the CPU, the BF flag bit is automatically cleared. The user can then send an Acknowledge bit at the end of reception by setting the Acknowledge sequence enable bit, ACKEN (SSPCON2<4>).

### 18.4.11.1 BF Status Flag

In receive operation, the BF bit is set when an address or data byte is loaded into SSPBUF from SSPSR. It is cleared when the SSPBUF register is read.

### 18.4.11.2 SSPOV Status Flag

In receive operation, the SSPOV bit is set when 8 bits are received into the SSPSR and the BF flag bit is already set from a previous reception.

### 18.4.11.3 WCOL Status Flag

If the user writes the SSPBUF when a receive is already in progress (i.e., SSPSR is still shifting in a data byte), the WCOL bit is set and the contents of the buffer are unchanged (the write doesn't occur).

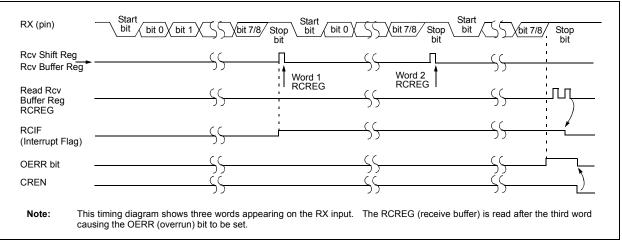

### FIGURE 19-7: ASYNCHRONOUS RECEPTION

#### TABLE 19-6: REGISTERS ASSOCIATED WITH ASYNCHRONOUS RECEPTION

| Name    | Bit 7                                          | Bit 6     | Bit 5  | Bit 4  | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on Page: |

|---------|------------------------------------------------|-----------|--------|--------|-------|--------|--------|--------|-----------------------------|

| INTCON  | GIE/GIEH                                       | PEIE/GIEL | TMR0IE | INT0IE | RBIE  | TMR0IF | INT0IF | RBIF   | 55                          |

| PIR1    | PSPIF <sup>(1)</sup>                           | ADIF      | RCIF   | TXIF   | SSPIF | CCP1IF | TMR2IF | TMR1IF | 58                          |

| PIE1    | PSPIE <sup>(1)</sup>                           | ADIE      | RCIE   | TXIE   | SSPIE | CCP1IE | TMR2IE | TMR1IE | 58                          |

| IPR1    | PSPIP <sup>(1)</sup>                           | ADIP      | RCIP   | TXIP   | SSPIP | CCP1IP | TMR2IP | TMR1IP | 58                          |

| RCSTA   | SPEN                                           | RX9       | SREN   | CREN   | ADDEN | FERR   | OERR   | RX9D   | 57                          |

| RCREG   | EUSART Receive Register                        |           |        |        |       |        |        |        | 57                          |

| TXSTA   | CSRC                                           | TX9       | TXEN   | SYNC   | SENDB | BRGH   | TRMT   | TX9D   | 57                          |

| BAUDCON | ABDOVF                                         | RCIDL     | _      | SCKP   | BRG16 | _      | WUE    | ABDEN  | 57                          |

| SPBRGH  | EUSART Baud Rate Generator Register, High Byte |           |        |        |       |        |        |        | 57                          |

| SPBRG   | EUSART Baud Rate Generator Register, Low Byte  |           |        |        |       |        |        |        | 57                          |

**Legend:** — = unimplemented locations read as '0'. Shaded cells are not used for asynchronous reception.

**Note 1:** Reserved in PIC18F2X80 devices; always maintain these bits clear.

### 19.4.2 EUSART SYNCHRONOUS SLAVE RECEPTION

The operation of the Synchronous Master and Slave modes is identical, except in the case of Sleep or any Idle mode and bit, SREN, which is a "don't care" in Slave mode.

If receive is enabled by setting the CREN bit prior to entering Sleep or any Idle mode, then a word may be received while in this low-power mode. Once the word is received, the RSR register will transfer the data to the RCREG register. If the RCIE enable bit is set, the interrupt generated will wake the chip from the low-power mode. If the global interrupt is enabled, the program will branch to the interrupt vector. To set up a Synchronous Slave Reception:

- 1. Enable the synchronous master serial port by setting bits, SYNC and SPEN, and clearing bit, CSRC.

- 2. If interrupts are desired, set enable bit, RCIE.

- 3. If 9-bit reception is desired, set bit, RX9.

- 4. To enable reception, set enable bit, CREN.

- 5. Flag bit, RCIF, will be set when reception is complete. An interrupt will be generated if enable bit, RCIE, was set.

- Read the RCSTA register to get the 9th bit (if enabled) and determine if any error occurred during reception.

- 7. Read the 8-bit received data by reading the RCREG register.

- 8. If any error occurred, clear the error by clearing bit, CREN.

- If using interrupts, ensure that the GIE and PEIE bits in the INTCON register (INTCON<7:6>) are set.

| Name    | Bit 7                                         | Bit 6       | Bit 5       | Bit 4        | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on Page: |

|---------|-----------------------------------------------|-------------|-------------|--------------|-------|--------|--------|--------|-----------------------------|

| INTCON  | GIE/GIEH                                      | PEIE/GIEL   | TMR0IE      | INT0IE       | RBIE  | TMR0IF | INT0IF | RBIF   | 55                          |

| PIR1    | PSPIF <sup>(1)</sup>                          | ADIF        | RCIF        | TXIF         | SSPIF | CCP1IF | TMR2IF | TMR1IF | 58                          |

| PIE1    | PSPIE <sup>(1)</sup>                          | ADIE        | RCIE        | TXIE         | SSPIE | CCP1IE | TMR2IE | TMR1IE | 58                          |

| IPR1    | PSPIP <sup>(1)</sup>                          | ADIP        | RCIP        | TXIP         | SSPIP | CCP1IP | TMR2IP | TMR1IP | 58                          |

| RCSTA   | SPEN                                          | RX9         | SREN        | CREN         | ADDEN | FERR   | OERR   | RX9D   | 57                          |

| RCREG   | EUSART Receive Register                       |             |             |              |       |        |        |        | 57                          |

| TXSTA   | CSRC                                          | TX9         | TXEN        | SYNC         | SENDB | BRGH   | TRMT   | TX9D   | 57                          |

| BAUDCON | ABDOVF                                        | RCIDL       |             | SCKP         | BRG16 | —      | WUE    | ABDEN  | 57                          |

| SPBRGH  | EUSART Baud Rate Generator Register High Byte |             |             |              |       |        |        |        | 57                          |

| SPBRG   | EUSART B                                      | aud Rate Ge | enerator Re | gister Low I | Byte  |        |        |        | 57                          |

TABLE 19-10: REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE RECEPTION

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used for synchronous slave reception.

Note 1: Reserved in PIC18F2X80 devices; always maintain these bits clear.

| R/W-0         | R/W-0                                            | R/W-0            | R/W-0           | R/W-0                              | R/W-0   | R/W-0           | R/W-0   |  |  |  |

|---------------|--------------------------------------------------|------------------|-----------------|------------------------------------|---------|-----------------|---------|--|--|--|

| FIL15_1       | FIL15_0                                          | FIL14_1          | FIL14_0         | FIL13_1                            | FIL13_0 | FIL12_1         | FIL12_0 |  |  |  |

| bit 7         |                                                  |                  |                 |                                    |         |                 | bit C   |  |  |  |

|               |                                                  |                  |                 |                                    |         |                 |         |  |  |  |

| Legend:       |                                                  |                  |                 |                                    |         |                 |         |  |  |  |

| R = Readable  | e bit                                            | W = Writable     | bit             | U = Unimplemented bit, read as '0' |         |                 |         |  |  |  |

| -n = Value at | POR                                              | '1' = Bit is set | t               | '0' = Bit is cle                   | ared    | x = Bit is unki | nown    |  |  |  |

|               |                                                  |                  |                 |                                    |         |                 |         |  |  |  |

| bit 7-6       | FIL15_<1:0>:                                     | : Filter 15 Sele | ct bits 1 and 0 |                                    |         |                 |         |  |  |  |

|               | 11 = No masl                                     |                  |                 |                                    |         |                 |         |  |  |  |

|               | 10 = Filter 15                                   |                  |                 |                                    |         |                 |         |  |  |  |

|               | 01 = Acceptance Mask 1<br>00 = Acceptance Mask 0 |                  |                 |                                    |         |                 |         |  |  |  |

| bit 5-4       | FIL14_<1:0>:                                     | : Filter 14 Sele | ct bits 1 and 0 |                                    |         |                 |         |  |  |  |

|               | 11 = No mask                                     |                  |                 |                                    |         |                 |         |  |  |  |

|               | 10 = Filter 15                                   |                  |                 |                                    |         |                 |         |  |  |  |

|               | 01 = Accepta<br>00 = Accepta                     |                  |                 |                                    |         |                 |         |  |  |  |

| bit 3-2       | •                                                | : Filter 13 Sele | ct bits 1 and 0 |                                    |         |                 |         |  |  |  |

|               | 11 = No masl                                     |                  |                 |                                    |         |                 |         |  |  |  |

|               | 10 = Filter 15                                   |                  |                 |                                    |         |                 |         |  |  |  |

|               | 01 = Accepta                                     |                  |                 |                                    |         |                 |         |  |  |  |

| h:+ 1 0       | 00 = Accepta                                     |                  | at hits 1 and 0 |                                    |         |                 |         |  |  |  |

| bit 1-0       | 11 = No mas                                      | : Filter 12 Sele | ct bits T and U |                                    |         |                 |         |  |  |  |

|               | 10 = Filter 15                                   | -                |                 |                                    |         |                 |         |  |  |  |

|               | 01 = Accepta                                     |                  |                 |                                    |         |                 |         |  |  |  |

|               | 00 = Accepta                                     | nce Mask 0       |                 |                                    |         |                 |         |  |  |  |

|               |                                                  |                  |                 |                                    |         |                 |         |  |  |  |

# REGISTER 24-51: MSEL3: MASK SELECT REGISTER 3<sup>(1)</sup>

**Note 1:** This register is available in Mode 1 and 2 only.

| Mnemonic,<br>Operands |         | Description                     | Cycles | 16-Bit Instruction Word |      |      |      | Status          |       |

|-----------------------|---------|---------------------------------|--------|-------------------------|------|------|------|-----------------|-------|

|                       |         | Description                     | Cycles | MSb                     |      |      | LSb  | Affected        | Notes |

| LITERAL (             | OPERA   | TIONS                           |        |                         |      |      |      |                 |       |

| ADDLW                 | k       | Add Literal and WREG            | 1      | 0000                    | 1111 | kkkk | kkkk | C, DC, Z, OV, N |       |

| ANDLW                 | k       | AND Literal with WREG           | 1      | 0000                    | 1011 | kkkk | kkkk | Z, N            |       |

| IORLW                 | k       | Inclusive OR Literal with WREG  | 1      | 0000                    | 1001 | kkkk | kkkk | Z, N            |       |

| LFSR                  | f, k    | Move literal (12-bit) 2nd word  | 2      | 1110                    | 1110 | 00ff | kkkk | None            |       |

|                       |         | to FSR(f) 1st word              |        | 1111                    | 0000 | kkkk | kkkk |                 |       |

| MOVLB                 | k       | Move Literal to BSR<3:0>        | 1      | 0000                    | 0001 | 0000 | kkkk | None            |       |

| MOVLW                 | k       | Move Literal to WREG            | 1      | 0000                    | 1110 | kkkk | kkkk | None            |       |

| MULLW                 | k       | Multiply Literal with WREG      | 1      | 0000                    | 1101 | kkkk | kkkk | None            |       |

| RETLW                 | k       | Return with Literal in WREG     | 2      | 0000                    | 1100 | kkkk | kkkk | None            |       |

| SUBLW                 | k       | Subtract WREG from Literal      | 1      | 0000                    | 1000 | kkkk | kkkk | C, DC, Z, OV, N |       |

| XORLW                 | k       | Exclusive OR Literal with WREG  | 1      | 0000                    | 1010 | kkkk | kkkk | Z, N            |       |

| DATA MEN              | /IORY + |                                 | ONS    |                         |      |      |      |                 |       |

| TBLRD*                |         | Table Read                      | 2      | 0000                    | 0000 | 0000 | 1000 | None            |       |

| TBLRD*+               |         | Table Read with Post-Increment  |        | 0000                    | 0000 | 0000 | 1001 | None            |       |

| TBLRD*-               |         | Table Read with Post-Decrement  |        | 0000                    | 0000 | 0000 | 1010 | None            |       |

| TBLRD+*               |         | Table Read with Pre-Increment   |        | 0000                    | 0000 | 0000 | 1011 | None            |       |

| TBLWT*                |         | Table Write                     | 2      | 0000                    | 0000 | 0000 | 1100 | None            | 5     |

| TBLWT*+               |         | Table Write with Post-Increment |        | 0000                    | 0000 | 0000 | 1101 | None            | 5     |

| TBLWT*-               |         | Table Write with Post-Decrement |        | 0000                    | 0000 | 0000 | 1110 | None            | 5     |

| TBLWT+*               |         | Table Write with Pre-Increment  |        | 0000                    | 0000 | 0000 | 1111 | None            | 5     |

### TABLE 26-2: PIC18FXXXX INSTRUCTION SET (CONTINUED)

**Note 1:** When a PORT register is modified as a function of itself (e.g., MOVF PORTB, 1, 0), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

2: If this instruction is executed on the TMR0 register (and where applicable, 'd' = 1), the prescaler will be cleared if assigned.

**3:** If the Program Counter (PC) is modified or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

4: Some instructions are two-word instructions. The second word of these instructions will be executed as a NOP unless the first word of the instruction retrieves the information embedded in these 16 bits. This ensures that all program memory locations have a valid instruction.

5: If the table write starts the write cycle to internal memory, the write will continue until terminated.

# 28.4 AC (Timing) Characteristics

### 28.4.1 TIMING PARAMETER SYMBOLOGY

The timing parameter symbols have been created using one of the following formats:

| 1. TppS2ppS                | 3                               | 3. Tcc:st | (I <sup>2</sup> C specifications only) |

|----------------------------|---------------------------------|-----------|----------------------------------------|

| 2. TppS                    |                                 | 4. Ts     | (I <sup>2</sup> C specifications only) |

| Т                          |                                 |           |                                        |

| F                          | Frequency                       | Т         | Time                                   |

| Lowercase le               | etters (pp) and their meanings: |           |                                        |

| рр                         |                                 |           |                                        |

| сс                         | CCP1                            | osc       | OSC1                                   |

| ck                         | CLKO                            | rd        | RD                                     |

| cs                         | CS                              | rw        | RD or WR                               |

| di                         | SDI                             | sc        | SCK                                    |

| do                         | SDO                             | SS        | SS                                     |

| dt                         | Data in                         | tO        | TOCKI                                  |

| io                         | I/O port                        | t1        | T13CKI                                 |

| mc                         | MCLR                            | wr        | WR                                     |

| Uppercase le               | etters and their meanings:      | •         |                                        |

| S                          |                                 |           |                                        |

| F                          | Fall                            | Р         | Period                                 |

| н                          | High                            | R         | Rise                                   |

| I                          | Invalid (High-impedance)        | V         | Valid                                  |

| L                          | Low                             | Z         | High-impedance                         |

| I <sup>2</sup> C only      |                                 |           |                                        |

| AA                         | output access                   | High      | High                                   |

| BUF                        | Bus free                        | Low       | Low                                    |

| TCC:ST (I <sup>2</sup> C s | specifications only)            | ·         |                                        |

| CC                         |                                 |           |                                        |

| HD                         | Hold                            | SU        | Setup                                  |

| ST                         |                                 |           |                                        |

| DAT                        | DATA input hold                 | STO       | Stop condition                         |

| STA                        | Start condition                 |           |                                        |

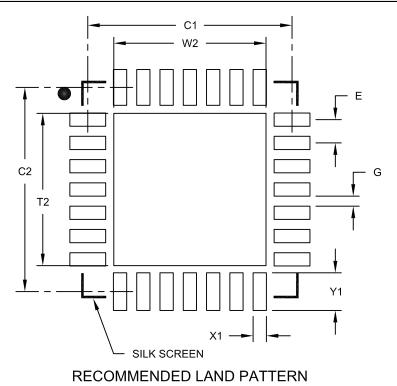

# 28-Lead Plastic Quad Flat, No Lead Package (ML) – 6x6 mm Body [QFN] with 0.55 mm Contact Length

|                            | MILLIMETERS |          |      |      |  |  |

|----------------------------|-------------|----------|------|------|--|--|

| Dimensio                   | MIN         | NOM      | MAX  |      |  |  |

| Contact Pitch              | E           | 0.65 BSC |      |      |  |  |

| Optional Center Pad Width  | W2          |          |      | 4.25 |  |  |

| Optional Center Pad Length | T2          |          |      | 4.25 |  |  |

| Contact Pad Spacing        | C1          |          | 5.70 |      |  |  |

| Contact Pad Spacing        | C2          |          | 5.70 |      |  |  |

| Contact Pad Width (X28)    | X1          |          |      | 0.37 |  |  |

| Contact Pad Length (X28)   | Y1          |          |      | 1.00 |  |  |

| Distance Between Pads      | G           | 0.20     |      |      |  |  |

#### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2105A

NOTES: