#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 40MHz                                                                    |

| Connectivity               | CANbus, I <sup>2</sup> C, SPI, UART/USART                                |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                              |

| Number of I/O              | 36                                                                       |

| Program Memory Size        | 32KB (16K x 16)                                                          |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 256 x 8                                                                  |

| RAM Size                   | 1.5K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                              |

| Data Converters            | A/D 11x10b                                                               |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Through Hole                                                             |

| Package / Case             | 40-DIP (0.600", 15.24mm)                                                 |

| Supplier Device Package    | 40-PDIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f4580-i-p |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

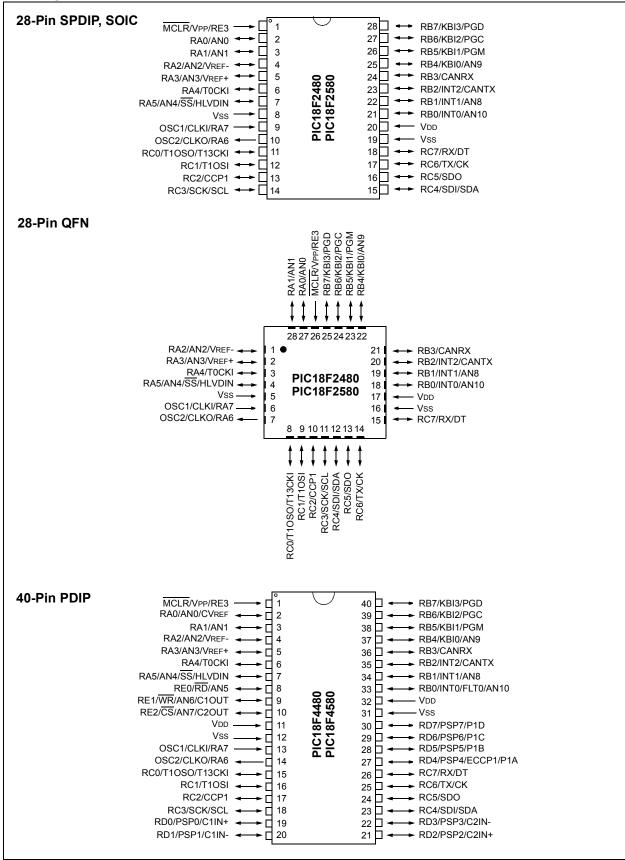

### **Pin Diagrams**

|                  | Pin Nu         | mber | Pin  | Buffer |                                                          |  |  |  |  |

|------------------|----------------|------|------|--------|----------------------------------------------------------|--|--|--|--|

| Pin Name         | SPDIP,<br>SOIC | QFN  | Туре | Туре   | Description                                              |  |  |  |  |

|                  |                |      |      |        | PORTB is a bidirectional I/O port. PORTB can be software |  |  |  |  |

|                  |                |      |      |        | programmed for internal weak pull-ups on all inputs.     |  |  |  |  |

| RB0/INT0/ AN10   | 21             | 18   |      |        |                                                          |  |  |  |  |

| RB0              |                |      | I/O  | TTL    | Digital I/O.                                             |  |  |  |  |

| INT0             |                |      | I    | ST     | External Interrupt 0.                                    |  |  |  |  |

| AN10             |                |      | I    | Analog | Analog Input 10.                                         |  |  |  |  |

| RB1/INT1/AN8     | 22             | 19   |      |        |                                                          |  |  |  |  |

| RB1              |                |      | I/O  | TTL    | Digital I/O.                                             |  |  |  |  |

| INT1             |                |      | I    | ST     | External Interrupt 1.                                    |  |  |  |  |

| AN8              |                |      | I    | Analog | Analog Input 8.                                          |  |  |  |  |

| RB2/INT2/CANTX   | 23             | 20   |      |        |                                                          |  |  |  |  |

| RB2              |                |      | I/O  | TTL    | Digital I/O.                                             |  |  |  |  |

| INT2             |                |      | I    | ST     | External Interrupt 2.                                    |  |  |  |  |

| CANTX            |                |      | 0    | TTL    | CAN bus TX.                                              |  |  |  |  |

| RB3/CANRX        | 24             | 21   |      |        |                                                          |  |  |  |  |

| RB3              |                |      | I/O  | TTL    | Digital I/O.                                             |  |  |  |  |

| CANRX            |                |      | I    | TTL    | CAN bus RX.                                              |  |  |  |  |

| RB4/KBI0/AN9     | 25             | 22   |      |        |                                                          |  |  |  |  |

| RB4              | 20             | 22   | I/O  | TTL    | Digital I/O.                                             |  |  |  |  |

| KBI0             |                |      |      | TTL    | Interrupt-on-change pin.                                 |  |  |  |  |

| AN9              |                |      | i    | Analog | Analog Input 9.                                          |  |  |  |  |

| RB5/KBI1/PGM     | 26             | 23   |      | - 5    |                                                          |  |  |  |  |

| RB5              | 20             | 20   | I/O  | TTL    | Digital I/O.                                             |  |  |  |  |

| KBI1             | 1              |      | "U   | TTL    | Interrupt-on-change pin.                                 |  |  |  |  |

| PGM              |                |      | Ι/Ο  | ST     | Low-Voltage ICSP™ Programming enable pin.                |  |  |  |  |

| RB6/KBI2/PGC     | 27             | 24   | -    |        |                                                          |  |  |  |  |

| RB6              | 21             | 27   | I/O  | TTL    | Digital I/O.                                             |  |  |  |  |

| KBI2             |                |      | "O   | TTL    | Interrupt-on-change pin.                                 |  |  |  |  |

| PGC              |                |      | I/O  | ST     | In-Circuit Debugger and ICSP programming clock pin.      |  |  |  |  |

| RB7/KBI3/PGD     | 28             | 25   |      | 01     |                                                          |  |  |  |  |

| RB7              | 20             | 20   | I/O  | TTL    | Digital I/O.                                             |  |  |  |  |

| KBI3             |                |      | 1/0  | TTL    | Interrupt-on-change pin.                                 |  |  |  |  |

| PGD              |                |      | I/O  | ST     | In-Circuit Debugger and ICSP programming data pin.       |  |  |  |  |

| Legend: TTL = TT | <u> </u>       |      |      | 01     | CMOS = CMOS compatible input or output                   |  |  |  |  |

#### **TABLE 1-2**: PIC18F2480/2580 PINOUT I/O DESCRIPTIONS (CONTINUED)

ST = Schmitt Trigger input with CMOS levels I

Р

= Input

= Power

$\begin{array}{l} O \\ O \\ |^2C \\ |^2C \\ = |^2C^{TM}/SMBus input buffer \end{array}$

# 5.4 Brown-out Reset (BOR)

PIC18F2480/2580/4480/4580 devices implement a BOR circuit that provides the user with a number of configuration and power-saving options. The BOR is controlled by the BORV<1:0> and BOREN<1:0> Configuration bits. There are a total of four BOR configurations which are summarized in Table 5-1.

The BOR threshold is set by the BORV<1:0> bits. If BOR is enabled (any values of BOREN<1:0>, except '00'), any drop of VDD below VBOR (parameter D005) for greater than TBOR (parameter 35) will reset the device. A Reset may or may not occur if VDD falls below VBOR for less than TBOR. The chip will remain in Brown-out Reset until VDD rises above VBOR.

If the Power-up Timer is enabled, it will be invoked after VDD rises above VBOR; it then will keep the chip in Reset for an additional time delay, TPWRT (parameter 33). If VDD drops below VBOR while the Power-up Timer is running, the chip will go back into a Brown-out Reset and the Power-up Timer will be initialized. Once VDD rises above VBOR, the Power-up Timer will execute the additional time delay.

BOR and the Power-on Timer (PWRT) are independently configured. Enabling a Brown-out Reset does not automatically enable the PWRT.

#### 5.4.1 SOFTWARE ENABLED BOR

When BOREN<1:0> = 01, the BOR can be enabled or disabled by the user in software. This is done with the control bit, SBOREN (RCON<6>). Setting SBOREN enables the BOR to function as previously described. Clearing SBOREN disables the BOR entirely. The SBOREN bit operates only in this mode; otherwise it is read as '0'.

Placing the BOR under software control gives the user the additional flexibility of tailoring the application to its environment without having to reprogram the device to change BOR configuration. It also allows the user to tailor device power consumption in software by eliminating the incremental current that the BOR consumes. While the BOR current is typically very small, it may have some impact in low-power applications.

| Note: | Even when BOR is under software control,<br>the Brown-out Reset voltage level is still |

|-------|----------------------------------------------------------------------------------------|

|       | set by the BORV<1:0> Configuration bits.<br>It cannot be changed in software.          |

# 5.4.2 DETECTING BOR

When Brown-out Reset is enabled, the BOR bit always resets to '0' on any Brown-out Reset or Power-on Reset event. This makes it difficult to determine if a Brown-out Reset event has occurred just by reading the state of BOR alone. A more reliable method is to simultaneously check the state of both POR and BOR. This assumes that the POR bit is reset to '1' in software immediately after any Power-on Reset event. IF BOR is '0' while POR is '1', it can be reliably assumed that a Brown-out Reset event has occurred.

# 5.4.3 DISABLING BOR IN SLEEP MODE

When BOREN<1:0> = 10, the BOR remains under hardware control and operates as previously described. Whenever the device enters Sleep mode, however, the BOR is automatically disabled. When the device returns to any other operating mode, BOR is automatically re-enabled.

This mode allows for applications to recover from brown-out situations, while actively executing code, when the device requires BOR protection the most. At the same time, it saves additional power in Sleep mode by eliminating the small incremental BOR current.

| BOR Con | BOR Configuration |                     |                                                                                    |

|---------|-------------------|---------------------|------------------------------------------------------------------------------------|

| BOREN1  | BOREN0            | SBOREN<br>(RCON<6>) | BOR Operation                                                                      |

| 0       | 0                 | Unavailable         | BOR disabled; must be enabled by reprogramming the Configuration bits.             |

| 0       | 1                 | Available           | BOR enabled in software; operation controlled by SBOREN.                           |

| 1       | 0                 | Unavailable         | BOR enabled in hardware in Run and Idle modes, disabled during Sleep mode.         |

| 1       | 1                 | Unavailable         | BOR enabled in hardware; must be disabled by reprogramming the Configuration bits. |

TABLE 5-1: BOR CONFIGURATIONS

| File Name                              | Bit 7 | Bit 6 | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   | Value on POR, BOR | Details on<br>Page: |

|----------------------------------------|-------|-------|---------|---------|---------|---------|---------|---------|-------------------|---------------------|

| RXF3SIDH                               | SID10 | SID9  | SID8    | SID7    | SID6    | SID5    | SID4    | SID3    | XXXX XXXX         | 62, 308             |

| RXF2EIDL                               | EID7  | EID6  | EID5    | EID4    | EID3    | EID2    | EID1    | EID0    | XXXX XXXX         | 62, 309             |

| RXF2EIDH                               | EID15 | EID14 | EID13   | EID12   | EID11   | EID10   | EID9    | EID8    | XXXX XXXX         | 62, 309             |

| RXF2SIDL                               | SID2  | SID1  | SID0    | _       | EXIDEN  | _       | EID17   | EID16   | xxx- x-xx         | 62, 308             |

| RXF2SIDH                               | SID10 | SID9  | SID8    | SID7    | SID6    | SID5    | SID4    | SID3    | XXXX XXXX         | 62, 308             |

| RXF1EIDL                               | EID7  | EID6  | EID5    | EID4    | EID3    | EID2    | EID1    | EID0    | XXXX XXXX         | 62, 309             |

| RXF1EIDH                               | EID15 | EID14 | EID13   | EID12   | EID11   | EID10   | EID9    | EID8    | XXXX XXXX         | 62, 309             |

| RXF1SIDL                               | SID2  | SID1  | SID0    | _       | EXIDEN  | _       | EID17   | EID16   | xxx- x-xx         | 62, 308             |

| RXF1SIDH                               | SID10 | SID9  | SID8    | SID7    | SID6    | SID5    | SID4    | SID3    | XXXX XXXX         | 62, 308             |

| RXF0EIDL                               | EID7  | EID6  | EID5    | EID4    | EID3    | EID2    | EID1    | EID0    | XXXX XXXX         | 62, 309             |

| RXF0EIDH                               | EID15 | EID14 | EID13   | EID12   | EID11   | EID10   | EID9    | EID8    | XXXX XXXX         | 62, 309             |

| RXF0SIDL                               | SID2  | SID1  | SID0    | _       | EXIDEN  | _       | EID17   | EID16   | xxx- x-xx         | 62, 308             |

| <b>RXF0SIDH</b>                        | SID10 | SID9  | SID8    | SID7    | SID6    | SID5    | SID4    | SID3    | XXXX XXXX         | 62, 308             |

| B5D7 <sup>(8)</sup>                    | B5D77 | B5D76 | B5D75   | B5D74   | B5D73   | B5D72   | B5D71   | B5D70   | XXXX XXXX         | 62, 305             |

| B5D6 <sup>(8)</sup>                    | B5D67 | B5D66 | B5D65   | B5D64   | B5D63   | B5D62   | B5D61   | B5D60   | XXXX XXXX         | 62, 305             |

| B5D5 <sup>(8)</sup>                    | B5D57 | B5D56 | B5D55   | B5D54   | B5D53   | B5D52   | B5D51   | B5D50   | XXXX XXXX         | 62, 305             |

| B5D4 <sup>(8)</sup>                    | B5D47 | B5D46 | B5D45   | B5D44   | B5D43   | B5D42   | B5D41   | B5D40   | XXXX XXXX         | 62, 305             |

| B5D3 <sup>(8)</sup>                    | B5D37 | B5D36 | B5D35   | B5D34   | B5D33   | B5D32   | B5D31   | B5D30   | XXXX XXXX         | 62, 305             |

| B5D2 <sup>(8)</sup>                    | B5D27 | B5D26 | B5D25   | B5D24   | B5D23   | B5D22   | B5D21   | B5D20   | XXXX XXXX         | 62, 305             |

| B5D1 <sup>(8)</sup>                    | B5D17 | B5D16 | B5D15   | B5D14   | B5D13   | B5D12   | B5D11   | B5D10   | XXXX XXXX         | 62, 305             |

| B5D0 <sup>(8)</sup>                    | B5D07 | B5D06 | B5D05   | B5D04   | B5D03   | B5D02   | B5D01   | B5D00   | XXXX XXXX         | 62, 305             |

| B5DLC <sup>(8)</sup><br>Receive mode   | _     | RXRTR | RB1     | RB0     | DLC3    | DLC2    | DLC1    | DLC0    | -xxx xxxx         | 62, 307             |

| B5DLC <sup>(8)</sup><br>Transmit mode  | —     | TXRTR | —       | —       | DLC3    | DLC2    | DLC1    | DLC0    | -x xxxx           | 62, 307             |

| B5EIDL <sup>(8)</sup>                  | EID7  | EID6  | EID5    | EID4    | EID3    | EID2    | EID1    | EID0    | XXXX XXXX         | 62, 305             |

| B5EIDH <sup>(8)</sup>                  | EID15 | EID14 | EID13   | EID12   | EID11   | EID10   | EID9    | EID8    | XXXX XXXX         | 62, 304             |

| B5SIDL <sup>(8)</sup><br>Receive mode  | SID2  | SID1  | SID0    | SRR     | EXID    | _       | EID17   | EID16   | XXXX X-XX         | 62, 303             |

| B5SIDL <sup>(8)</sup><br>Transmit mode | SID2  | SID1  | SID0    | —       | EXIDE   | _       | EID17   | EID16   | xxx- x-xx         | 62, 303             |

| B5SIDH <sup>(8)</sup>                  | SID10 | SID9  | SID8    | SID7    | SID6    | SID5    | SID4    | SID3    | xxxx x-xx         | 62, 302             |

| B5CON <sup>(8)</sup><br>Receive mode   | RXFUL | RXM1  | RXRTRRO | FILHIT4 | FILHIT3 | FILHIT2 | FILHIT1 | FILHIT0 | 0000 0000         | 62, 301             |

| B5CON <sup>(8)</sup><br>Transmit mode  | TXBIF | TXABT | TXLARB  | TXERR   | TXREQ   | RTREN   | TXPRI1  | TXPRI0  | 0000 0000         | 62, 301             |

| B4D7 <sup>(8)</sup>                    | B4D77 | B4D76 | B4D75   | B4D74   | B4D73   | B4D72   | B4D71   | B4D70   | XXXX XXXX         | 62, 305             |

| B4D6 <sup>(8)</sup>                    | B4D67 | B4D66 | B4D65   | B4D64   | B4D63   | B4D62   | B4D61   | B4D60   | XXXX XXXX         | 62, 305             |

| B4D5 <sup>(8)</sup>                    | B4D57 | B4D56 | B4D55   | B4D54   | B4D53   | B4D52   | B4D51   | B4D50   | XXXX XXXX         | 62, 305             |

| B4D4 <sup>(8)</sup>                    | B4D47 | B4D46 | B4D45   | B4D44   | B4D43   | B4D42   | B4D41   | B4D40   | XXXX XXXX         | 63, 305             |

| B4D3 <sup>(8)</sup>                    | B4D37 | B4D36 | B4D35   | B4D34   | B4D33   | B4D32   | B4D31   | B4D30   | XXXX XXXX         | 63, 305             |

| TABLE 6-2: | REGISTER FILE SUMMARY ( | PIC18F2480/2580/4480/4580 | (CONTINUED) |

|------------|-------------------------|---------------------------|-------------|

|------------|-------------------------|---------------------------|-------------|

**Legend:** x = unknown, u = unchanged, - = unimplemented, q = value depends on condition

Note 1: Bit 21 of the PC is only available in Test mode and Serial Programming modes.

The SBOREN bit is only available when CONFIG2L<1:0> = 01; otherwise, it is disabled and reads as '0'. See Section 5.4 "Brown-out Reset (BOR)".

These registers and/or bits are not implemented on PIC18F2X80 devices and are read as '0'. Reset values are shown for PIC18F4X80 devices; individual unimplemented bits should be interpreted as '-'.

4: The PLLEN bit is only available in specific oscillator configuration; otherwise, it is disabled and reads as '0'. See Section 3.6.4 "PLL in INTOSC Modes".

5: The RE3 bit is only available when Master Clear Reset is disabled (CONFIG3H<7> = 0); otherwise, RE3 reads as '0'. This bit is read-only.

6: RA6/RA7 and their associated latch and direction bits are individually configured as port pins based on various primary oscillator modes. When disabled, these bits read as '0'.

7: CAN bits have multiple functions depending on the selected mode of the CAN module.

8: This register reads all '0's until the ECAN™ technology is set up in Mode 1 or Mode 2.

9: These registers are available on PIC18F4X80 devices only.

| R-0           | R-0                                                          | R/W-0                                                                                                                                                   | R/W-0           | U-0              | R/W-1            | R/W-1           | R/W-1  |  |  |  |  |  |

|---------------|--------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|------------------|------------------|-----------------|--------|--|--|--|--|--|

| IBF           | OBF                                                          | IBOV                                                                                                                                                    | PSPMODE         |                  | TRISE2           | TRISE1          | TRISE0 |  |  |  |  |  |

| bit 7         |                                                              |                                                                                                                                                         |                 |                  |                  |                 | bit 0  |  |  |  |  |  |

| <del></del>   |                                                              |                                                                                                                                                         |                 |                  |                  |                 |        |  |  |  |  |  |

| Legend:       |                                                              |                                                                                                                                                         |                 |                  |                  |                 |        |  |  |  |  |  |

| R = Readabl   |                                                              | W = Writable                                                                                                                                            |                 | -                | mented bit, read |                 |        |  |  |  |  |  |

| -n = Value at | POR                                                          | '1' = Bit is s€                                                                                                                                         | et              | '0' = Bit is cle | eared            | x = Bit is unkr | nown   |  |  |  |  |  |

| bit 7         | IBF: Input Bu                                                | ffer Full Statu                                                                                                                                         | s hit           |                  |                  |                 |        |  |  |  |  |  |

|               | •                                                            |                                                                                                                                                         | ed and waiting  | to be read by    | the CPU          |                 |        |  |  |  |  |  |

|               | 0 = No word h                                                |                                                                                                                                                         | •               |                  |                  |                 |        |  |  |  |  |  |

| bit 6         | OBF: Output                                                  | Buffer Full Sta                                                                                                                                         | atus bit        |                  |                  |                 |        |  |  |  |  |  |

|               |                                                              |                                                                                                                                                         | olds a previous | ly written word  | d                |                 |        |  |  |  |  |  |

|               | 0 = The outpu                                                | ut buffer has b                                                                                                                                         | een read        |                  |                  |                 |        |  |  |  |  |  |

| bit 5         |                                                              | IBOV: Input Buffer Overflow Detect bit (in Microprocessor mode)                                                                                         |                 |                  |                  |                 |        |  |  |  |  |  |

|               |                                                              | <ul> <li>1 = A write occurred when a previously input word has not been read (must be cleared in software)</li> <li>0 = No overflow occurred</li> </ul> |                 |                  |                  |                 |        |  |  |  |  |  |

| L 11 A        |                                                              |                                                                                                                                                         |                 |                  |                  |                 |        |  |  |  |  |  |

| bit 4         | PSPMODE: Parallel Slave Port Mode Select bit                 |                                                                                                                                                         |                 |                  |                  |                 |        |  |  |  |  |  |

|               | 1 = Parallel Slave Port mode<br>0 = General purpose I/O mode |                                                                                                                                                         |                 |                  |                  |                 |        |  |  |  |  |  |

| bit 3         | Unimplemen                                                   | -                                                                                                                                                       |                 |                  |                  |                 |        |  |  |  |  |  |

| bit 2         | TRISE2: RE2                                                  | 2 Direction Co                                                                                                                                          | ntrol bit       |                  |                  |                 |        |  |  |  |  |  |

|               | 1 = Input                                                    |                                                                                                                                                         |                 |                  |                  |                 |        |  |  |  |  |  |

|               | 0 = Output                                                   |                                                                                                                                                         |                 |                  |                  |                 |        |  |  |  |  |  |

| bit 1         | TRISE1: RE1 Direction Control bit                            |                                                                                                                                                         |                 |                  |                  |                 |        |  |  |  |  |  |

|               | 1 = Input                                                    |                                                                                                                                                         |                 |                  |                  |                 |        |  |  |  |  |  |

|               | 0 = Output                                                   |                                                                                                                                                         |                 |                  |                  |                 |        |  |  |  |  |  |

| bit 0         | TRISE0: RE0                                                  | Direction Co                                                                                                                                            | ntrol bit       |                  |                  |                 |        |  |  |  |  |  |

|               | 1 = Input                                                    |                                                                                                                                                         |                 |                  |                  |                 |        |  |  |  |  |  |

|               | 0 = Output                                                   |                                                                                                                                                         |                 |                  |                  |                 |        |  |  |  |  |  |

# REGISTER 11-1: TRISE REGISTER (PIC18F4X80 DEVICES ONLY)

NOTES:

| Name                    | Bit 7                         | Bit 6                                            | Bit 5        | Bit 4         | Bit 3    | Bit 2   | Bit 1   | Bit 0   | Reset<br>Values<br>on Page: |  |

|-------------------------|-------------------------------|--------------------------------------------------|--------------|---------------|----------|---------|---------|---------|-----------------------------|--|

| INTCON                  | GIE/GIEH                      | PEIE/GIEL                                        | TMR0IE       | INT0IE        | RBIE     | TMR0IF  | INT0IF  | RBIF    | 55                          |  |

| RCON                    | IPEN                          | SBOREN <sup>(2)</sup>                            |              | RI            | TO       | PD      | POR     | BOR     | 56                          |  |

| PIR1                    | PSPIF                         | ADIF                                             | RCIF         | TXIF          | SSPIF    | CCP1IF  | TMR2IF  | TMR1IF  | 58                          |  |

| PIE1                    | PSPIE                         | ADIE                                             | RCIE         | TXIE          | SSPIE    | CCP1IE  | TMR2IE  | TMR1IE  | 58                          |  |

| IPR1                    | PSPIP                         | ADIP                                             | RCIP         | TXIP          | SSPIP    | CCP1IP  | TMR2IP  | TMR1IP  | 58                          |  |

| TRISB                   | PORTB Data Direction Register |                                                  |              |               |          |         |         |         |                             |  |

| TRISC                   | PORTC Da                      | PORTC Data Direction Register                    |              |               |          |         |         |         |                             |  |

| TMR2                    | Timer2 Reg                    | ister                                            |              |               |          |         |         |         | 56                          |  |

| PR2                     | Timer2 Peri                   | od Register                                      |              |               |          |         |         |         | 56                          |  |

| T2CON                   | —                             | T2OUTPS3                                         | T2OUTPS2     | T2OUTPS1      | T2OUTPS0 | TMR2ON  | T2CKPS1 | T2CKPS0 | 56                          |  |

| CCPR1L                  | Capture/Co                    | mpare/PWM                                        | Register 1 L | ow Byte       |          |         |         |         | 57                          |  |

| CCPR1H                  | Capture/Co                    | mpare/PWM                                        | Register 1 H | igh Byte      |          |         |         |         | 57                          |  |

| CCP1CON                 | —                             | _                                                | DC1B1        | DC1B0         | CCP1M3   | CCP1M2  | CCP1M1  | CCP1M0  | 57                          |  |

| ECCPR1L <sup>(1)</sup>  | Enhanced (                    | Enhanced Capture/Compare/PWM Register 1 Low Byte |              |               |          |         |         |         |                             |  |

| ECCPR1H <sup>(1)</sup>  | Enhanced (                    | Capture/Comp                                     | oare/PWM R   | egister 1 Hig | h Byte   |         |         |         | 57                          |  |

| ECCP1CON <sup>(1)</sup> | EPWM1M1                       | EPWM1M0                                          | EDC1B1       | EDC1B0        | ECCP1M3  | ECCP1M2 | ECCP1M1 | ECCP1M0 | 57                          |  |

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used by PWM or Timer2.

Note 1: These registers are unimplemented on PIC18F2X80 devices.

2: The SBOREN bit is only available when CONFIG2L<1:0> = 01; otherwise, it is disabled and reads as '0'. See Section 5.4 "Brown-out Reset (BOR)".

# 18.3.2 OPERATION

When initializing the SPI, several options need to be specified. This is done by programming the appropriate control bits (SSPCON1<5:0> and SSPSTAT<7:6>). These control bits allow the following to be specified:

- Master mode (SCK is the clock output)

- Slave mode (SCK is the clock input)

- Clock Polarity (Idle state of SCK)

- Data Input Sample Phase (middle or end of data output time)

- Clock Edge (output data on rising/falling edge of SCK)

- Clock Rate (Master mode only)

- · Slave Select mode (Slave mode only)

The MSSP consists of a Transmit/Receive Shift register (SSPSR) and a Buffer register (SSPBUF). The SSPSR shifts the data in and out of the device, MSb first. The SSPBUF holds the data that was written to the SSPSR until the received data is ready. Once the 8 bits of data have been received, that byte is moved to the SSPBUF register. Then, the Buffer Full detect bit, BF (SSPSTAT<0>), and the interrupt flag bit, SSPIF, are set. This double-buffering of the received data (SSPBUF) allows the next byte to start reception before reading the data that was just received. Any write to the SSPBUF register during transmission/reception of data will be ignored and the write collision detect bit, WCOL (SSPCON1<7>), will be set. User software must clear the WCOL bit so that it can be determined if the following write(s) to the SSPBUF register completed successfully.

When the application software is expecting to receive valid data, the SSPBUF should be read before the next byte of data to transfer is written to the SSPBUF. The Buffer Full bit, BF (SSPSTAT<0>), indicates when SSPBUF has been loaded with the received data (transmission is complete). When the SSPBUF is read, the BF bit is cleared. This data may be irrelevant if the SPI is only a transmitter. Generally, the MSSP interrupt is used to determine when the transmission/reception has completed. The SSPBUF must be read and/or written. If the interrupt method is not going to be used, then software polling can be done to ensure that a write collision does not occur. Example 18-1 shows the loading of the SSPBUF (SSPSR) for data transmission.

The SSPSR is not directly readable or writable and can only be accessed by addressing the SSPBUF register. Additionally, the MSSP Status register (SSPSTAT) indicates the various status conditions.

| Note: | The SSPBUF regis          | ster cannot be | used v | vith |  |  |  |  |  |

|-------|---------------------------|----------------|--------|------|--|--|--|--|--|

|       | read-modify-write         | instructions   | such   | as   |  |  |  |  |  |

|       | BCF, BTFSC and COMF, etc. |                |        |      |  |  |  |  |  |

Note: To avoid lost data in Master mode, a read of the SSPBUF must be performed to clear the Buffer Full (BF) detect bit (SSPSTAT<0>) between each transmission.

#### EXAMPLE 18-1: LOADING THE SSPBUF (SSPSR) REGISTER

| LOOP | BTFSS | SSPSTAT, BF | ;Has data been received (transmit complete)? |

|------|-------|-------------|----------------------------------------------|

|      | BRA   | LOOP        | ;No                                          |

|      | MOVF  | SSPBUF, W   | ;WREG reg = contents of SSPBUF               |

|      | MOVWF | RXDATA      | ;Save in user RAM, if data is meaningful     |

|      | MOVF  | TXDATA, W   | ;W reg = contents of TXDATA                  |

|      | MOVWF | SSPBUF      | ;New data to xmit                            |

|                     | SYNC = 0, BRGH = 0, BRG16 = 0 |            |                             |                       |            |                             |                       |            |                             |                       |                  |                             |  |

|---------------------|-------------------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------------|-----------------------------|--|

| BAUD<br>RATE<br>(K) | Fosc = 40.000 MHz             |            |                             | Fosc = 20.000 MHz     |            |                             | Fosc = 10.000 MHz     |            |                             | Fos                   | Fosc = 8.000 MHz |                             |  |

|                     | Actual<br>Rate<br>(K)         | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error       | SPBRG<br>value<br>(decimal) |  |

| 0.3                 | _                             |            |                             | _                     | _          | _                           | _                     |            | _                           | _                     | _                | _                           |  |

| 1.2                 | —                             | —          | —                           | 1.221                 | 1.73       | 255                         | 1.202                 | 0.16       | 129                         | 1.201                 | -0.16            | 103                         |  |

| 2.4                 | 2.441                         | 1.73       | 255                         | 2.404                 | 0.16       | 129                         | 2.404                 | 0.16       | 64                          | 2.403                 | -0.16            | 51                          |  |

| 9.6                 | 9.615                         | 0.16       | 64                          | 9.766                 | 1.73       | 31                          | 9.766                 | 1.73       | 15                          | 9.615                 | -0.16            | 12                          |  |

| 19.2                | 19.531                        | 1.73       | 31                          | 19.531                | 1.73       | 15                          | 19.531                | 1.73       | 7                           | _                     | _                | _                           |  |

| 57.6                | 56.818                        | -1.36      | 10                          | 62.500                | 8.51       | 4                           | 52.083                | -9.58      | 2                           | —                     | _                | _                           |  |

| 115.2               | 125.000                       | 8.51       | 4                           | 104.167               | -9.58      | 2                           | 78.125                | -32.18     | 1                           | _                     | _                | —                           |  |

#### TABLE 19-3: BAUD RATES FOR ASYNCHRONOUS MODES

|              | SYNC = 0, BRGH = 0, BRG16 = 0 |            |                             |                       |            |                             |                       |            |                             |  |  |  |

|--------------|-------------------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|--|--|--|

| BAUD<br>RATE | Fos                           | c = 4.000  | MHz                         | Fos                   | c = 2.000  | MHz                         | Fosc = 1.000 MHz      |            |                             |  |  |  |

| (K)          | Actual<br>Rate<br>(K)         | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) |  |  |  |

| 0.3          | 0.300                         | 0.16       | 207                         | 0.300                 | -0.16      | 103                         | 0.300                 | -0.16      | 51                          |  |  |  |

| 1.2          | 1.202                         | 0.16       | 51                          | 1.201                 | -0.16      | 25                          | 1.201                 | -0.16      | 12                          |  |  |  |

| 2.4          | 2.404                         | 0.16       | 25                          | 2.403                 | -0.16      | 12                          | _                     | _          | _                           |  |  |  |

| 9.6          | 8.929                         | -6.99      | 6                           | _                     | _          | _                           | _                     | _          | _                           |  |  |  |

| 19.2         | 20.833                        | 8.51       | 2                           | —                     | _          | _                           | —                     | _          | _                           |  |  |  |

| 57.6         | 62.500                        | 8.51       | 0                           | —                     | _          | _                           | —                     | _          | _                           |  |  |  |

| 115.2        | 62.500                        | -45.75     | 0                           | _                     | _          | —                           | _                     |            |                             |  |  |  |

|             |                       | SYNC = 0, BRGH = 1, BRG16 = 0 |                             |                       |            |                             |                       |            |                             |                       |            |                             |  |  |

|-------------|-----------------------|-------------------------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|--|--|

| BAUD        | Fosc = 40.000 MHz     |                               |                             | Fosc = 20.000 MHz     |            |                             | Fosc = 10.000 MHz     |            |                             | Fosc = 8.000 MHz      |            |                             |  |  |

| RATE<br>(K) | Actual<br>Rate<br>(K) | %<br>Error                    | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) |  |  |

| 0.3         |                       |                               |                             | _                     |            |                             | _                     |            | _                           | _                     |            | _                           |  |  |

| 1.2         | —                     | _                             | —                           | —                     | _          | _                           | —                     | _          | —                           | —                     | _          | —                           |  |  |

| 2.4         | —                     | _                             | _                           | —                     | _          | _                           | 2.441                 | 1.73       | 255                         | 2.403                 | -0.16      | 207                         |  |  |

| 9.6         | 9.766                 | 1.73                          | 255                         | 9.615                 | 0.16       | 129                         | 9.615                 | 0.16       | 64                          | 9.615                 | -0.16      | 51                          |  |  |

| 19.2        | 19.231                | 0.16                          | 129                         | 19.231                | 0.16       | 64                          | 19.531                | 1.73       | 31                          | 19.230                | -0.16      | 25                          |  |  |

| 57.6        | 58.140                | 0.94                          | 42                          | 56.818                | -1.36      | 21                          | 56.818                | -1.36      | 10                          | 55.555                | 3.55       | 8                           |  |  |

| 115.2       | 113.636               | -1.36                         | 21                          | 113.636               | -1.36      | 10                          | 125.000               | 8.51       | 4                           | —                     | _          | _                           |  |  |

|              |                       | SYNC = 0, BRGH = 1, BRG16 = 0 |                             |                       |            |                             |                       |            |                             |  |  |  |  |

|--------------|-----------------------|-------------------------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|--|--|--|--|

| BAUD<br>RATE | Foso                  | = 4.000                       | MHz                         | Fos                   | c = 2.000  | MHz                         | Fosc = 1.000 MHz      |            |                             |  |  |  |  |

| (K)          | Actual<br>Rate<br>(K) | %<br>Error                    | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) |  |  |  |  |

| 0.3          |                       |                               | _                           |                       |            | _                           | 0.300                 | -0.16      | 207                         |  |  |  |  |

| 1.2          | 1.202                 | 0.16                          | 207                         | 1.201                 | -0.16      | 103                         | 1.201                 | -0.16      | 51                          |  |  |  |  |

| 2.4          | 2.404                 | 0.16                          | 103                         | 2.403                 | -0.16      | 51                          | 2.403                 | -0.16      | 25                          |  |  |  |  |

| 9.6          | 9.615                 | 0.16                          | 25                          | 9.615                 | -0.16      | 12                          | _                     | _          | _                           |  |  |  |  |

| 19.2         | 19.231                | 0.16                          | 12                          | _                     | _          | _                           | _                     | _          | _                           |  |  |  |  |

| 57.6         | 62.500                | 8.51                          | 3                           | —                     | _          | _                           | —                     | _          | _                           |  |  |  |  |

| 115.2        | 125.000               | 8.51                          | 1                           | _                     | —          | —                           | _                     |            | —                           |  |  |  |  |

© 2009 Microchip Technology Inc.

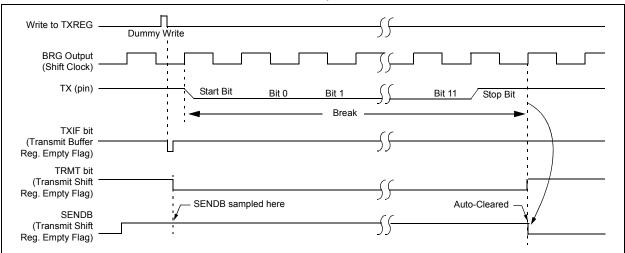

# 19.2.5 BREAK CHARACTER SEQUENCE

The Enhanced EUSART module has the capability of sending the special Break character sequences that are required by the LIN/J2602 bus standard. The Break character transmit consists of a Start bit, followed by twelve '0' bits and a Stop bit. The Frame Break character is sent whenever the SENDB and TXEN bits (TXSTA<3> and TXSTA<5>) are set while the Transmit Shift register is loaded with data. Note that the value of data written to TXREG will be ignored and all '0's will be transmitted.

The SENDB bit is automatically reset by hardware after the corresponding Stop bit is sent. This allows the user to preload the transmit FIFO with the next transmit byte following the Break character (typically, the Sync character in the LIN/J2602 specification).

Note that the data value written to the TXREG for the Break character is ignored. The write simply serves the purpose of initiating the proper sequence.

The TRMT bit indicates when the transmit operation is active or Idle, just as it does during normal transmission. See Figure 19-10 for the timing of the Break character sequence.

#### 19.2.5.1 Break and Sync Transmit Sequence

The following sequence will send a message frame header made up of a Break, followed by an Auto-Baud Sync byte. This sequence is typical of a LIN/J2602 bus master.

- 1. Configure the EUSART for the desired mode.

- 2. Set the TXEN and SENDB bits to set up the Break character.

- 3. Load the TXREG with a dummy character to initiate transmission (the value is ignored).

- 4. Write '55h' to TXREG to load the Sync character into the transmit FIFO buffer.

- 5. After the Break has been sent, the SENDB bit is reset by hardware. The Sync character now transmits in the preconfigured mode.

When the TXREG becomes empty, as indicated by the TXIF, the next data byte can be written to TXREG.

#### 19.2.6 RECEIVING A BREAK CHARACTER

The Enhanced USART module can receive a Break character in two ways.

The first method forces configuration of the baud rate at a frequency of 9/13 the typical speed. This allows for the Stop bit transition to be at the correct sampling location (13 bits for Break versus Start bit and 8 data bits for typical data).

The second method uses the auto-wake-up feature described in **Section 19.2.4 "Auto-Wake-up on Sync Break Character"**. By enabling this feature, the EUSART will sample the next two transitions on RX/DT, cause an RCIF interrupt and receive the next data byte followed by another interrupt.

Note that following a Break character, the user will typically want to enable the Auto-Baud Rate Detect feature. For both methods, the user can set the ABD bit once the TXIF interrupt is observed.

#### FIGURE 19-10: SEND BREAK CHARACTER SEQUENCE

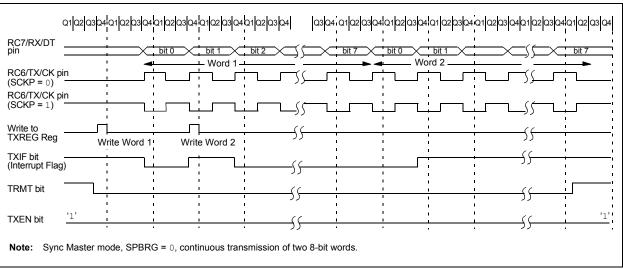

# 19.3 EUSART Synchronous Master Mode

The Master mode indicates that the processor transmits the master clock on the CK line. The Synchronous Master mode is entered by setting the CSRC bit (TXSTA<7>). In this mode, the data is transmitted in a half-duplex manner (i.e., transmission and reception do not occur at the same time). When transmitting data, the reception is inhibited and vice versa. Synchronous mode is entered by setting bit, SYNC (TXSTA<4>). In addition, enable bit, SPEN (RCSTA<7>), is set in order to configure the TX and RX pins to CK (clock) and DT (data) lines, respectively.

The Master mode indicates that the processor transmits the master clock on the CK line. Clock polarity is selected with the SCKP bit (BAUDCON<4>). Setting SCKP sets the Idle state on CK as high, while clearing the bit sets the Idle state as low. This option is provided to support Microwire devices with this module.

#### 19.3.1 EUSART SYNCHRONOUS MASTER TRANSMISSION

The EUSART transmitter block diagram is shown in Figure 19-3. The heart of the transmitter is the Transmit (Serial) Shift Register (TSR). The Shift register obtains its data from the Read/Write Transmit Buffer register, TXREG. The TXREG register is loaded with data in software. The TSR register is not loaded until the last bit has been transmitted from the previous load. As soon as the last bit is transmitted, the TSR is loaded with new data from the TXREG (if available).

Once the TXREG register transfers the data to the TSR register (occurs in one TCYCLE), the TXREG is empty and the TXIF flag bit (PIR1<4>) is set. The interrupt can be enabled or disabled by setting or clearing the interrupt enable bit, TXIE (PIE1<4>). TXIF is set regardless of the state of enable bit TXIE; it cannot be cleared in software. It will reset only when new data is loaded into the TXREG register.

While flag bit, TXIF, indicates the status of the TXREG register, another bit, TRMT (TXSTA<1>), shows the status of the TSR register. TRMT is a read-only bit which is set when the TSR is empty. No interrupt logic is tied to this bit so the user has to poll this bit in order to determine if the TSR register is empty. The TSR is not mapped in data memory so it is not available to the user.

To set up a Synchronous Master Transmission:

- 1. Initialize the SPBRGH:SPBRG registers for the appropriate baud rate. Set or clear the BRG16 bit, as required, to achieve the desired baud rate.

- 2. Enable the synchronous master serial port by setting bits, SYNC, SPEN and CSRC.

- 3. If interrupts are desired, set enable bit, TXIE.

- 4. If 9-bit transmission is desired, set bit, TX9.

- 5. Enable the transmission by setting bit, TXEN.

- 6. If 9-bit transmission is selected, the ninth bit should be loaded in bit, TX9D.

- 7. Start transmission by loading data to the TXREG register.

- If using interrupts, ensure that the GIE and PEIE bits in the INTCON register (INTCON<7:6>) are set.

### FIGURE 19-11: SYNCHRONOUS TRANSMISSION

| R/W-0        | U-0                                                                                                                                                 | R/W-0                                                               | R/W-0         | R/W-0                     | R/W-0           | R/W-0           | R/W-0 |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|---------------|---------------------------|-----------------|-----------------|-------|

| ADFM         |                                                                                                                                                     | ACQT2                                                               | ACQT1         | ACQT0                     | ADCS2           | ADCS1           | ADCS0 |

| bit 7        |                                                                                                                                                     |                                                                     |               |                           |                 |                 | bit C |

| Legend:      |                                                                                                                                                     |                                                                     |               |                           |                 |                 |       |

| R = Readab   | ole bit                                                                                                                                             | W = Writable                                                        | bit           | U = Unimpler              | nented bit, rea | d as '0'        |       |

| -n = Value a | at POR                                                                                                                                              | '1' = Bit is set                                                    |               | ʻ0' = Bit is cle          |                 | x = Bit is unki | nown  |

| bit 7        | <b>ADFM:</b> A/D R<br>1 = Right justi<br>0 = Left justifi                                                                                           |                                                                     | Select bit    |                           |                 |                 |       |

| bit 6        | Unimplemen                                                                                                                                          | ted: Read as '                                                      | 0'            |                           |                 |                 |       |

| bit 5-3      | ACQT<2:0>:<br>111 = 20 TAD<br>110 = 16 TAD<br>101 = 12 TAD<br>100 = 8 TAD<br>011 = 6 TAD<br>010 = 4 TAD<br>001 = 2 TAD<br>000 = 0 TAD <sup>(1</sup> |                                                                     | n Time Select | bits                      |                 |                 |       |

| bit 2-0      | ADCS<2:0>:<br>111 = FRC (d<br>110 = Fosc/6<br>101 = Fosc/1<br>100 = Fosc/4                                                                          | A/D Conversion<br>ock derived fro<br>4<br>6<br>ock derived fro<br>2 | om A/D RC os  | scillator) <sup>(1)</sup> |                 |                 |       |

# REGISTER 20-3: ADCON2: A/D CONTROL REGISTER 2

**Note 1:** If the A/D FRC clock source is selected, a delay of one TCY (instruction cycle) is added before the A/D clock starts. This allows the SLEEP instruction to be executed before starting a conversion.

# 21.0 COMPARATOR MODULE

The analog comparator module contains two comparators that can be configured in a variety of ways. The inputs can be selected from the analog inputs multiplexed with pins, RA0 through RA5, as well as the on-chip voltage reference (see Section 22.0 "Comparator Voltage Reference Module"). The digital outputs (normal or inverted) are available at the pin level and can also be read through the control register.

The CMCON register (Register 21-1) selects the comparator input and output configuration. Block diagrams of the various comparator configurations are shown in Figure 21-1.

### REGISTER 21-1: CMCON: COMPARATOR CONTROL REGISTER

| R-0           | R-0                                             | R/W-0                                   | R/W-0          | R/W-0            | R/W-0            | R/W-0           | R/W-0 |

|---------------|-------------------------------------------------|-----------------------------------------|----------------|------------------|------------------|-----------------|-------|

| C2OUT         | C1OUT                                           | C2INV                                   | C1INV          | CIS              | CM2              | CM1             | CM0   |

| bit 7         |                                                 |                                         |                |                  |                  |                 | bit 0 |

|               |                                                 |                                         |                |                  |                  |                 |       |

| Legend:       |                                                 |                                         |                |                  |                  |                 |       |

| R = Readabl   |                                                 | W = Writable                            |                | •                | mented bit, rea  |                 |       |

| -n = Value at | POR                                             | '1' = Bit is set                        |                | '0' = Bit is cle | ared             | x = Bit is unkr | nown  |

| h:+ <b>7</b>  |                                                 |                                         |                |                  |                  |                 |       |

| bit 7         | When C2INV                                      | nparator 2 Outp                         |                |                  |                  |                 |       |

|               | 1 = C2 VIN+3                                    |                                         |                |                  |                  |                 |       |

|               | 0 = C2 VIN+                                     | -                                       |                |                  |                  |                 |       |

|               | When C2INV                                      | <u>/ = 1:</u>                           |                |                  |                  |                 |       |

|               | 1 = C2 VIN+                                     | < C2 VIN-                               |                |                  |                  |                 |       |

|               | 0 = C2 VIN+                                     | > C2 VIN-                               |                |                  |                  |                 |       |

| bit 6         | C1OUT: Com                                      | parator 1 Outp                          | ut bit         |                  |                  |                 |       |

|               | When C1INV                                      |                                         |                |                  |                  |                 |       |

|               | 1 = C1 VIN+<br>0 = C1 VIN+                      |                                         |                |                  |                  |                 |       |

|               | When C1INV                                      |                                         |                |                  |                  |                 |       |

|               | 1 = C1 VIN+                                     |                                         |                |                  |                  |                 |       |

|               | 0 = C1 VIN+                                     | > C1 VIN-                               |                |                  |                  |                 |       |

| bit 5         | C2INV: Com                                      | parator 2 Outpu                         | t Inversion bi | t                |                  |                 |       |

|               | 1 <b>= C2 outpu</b>                             |                                         |                |                  |                  |                 |       |

|               | •                                               | it not inverted                         |                |                  |                  |                 |       |

| bit 4         |                                                 | parator 1 Outpu                         | t Inversion bi | t                |                  |                 |       |

|               | 1 = C1 outpu                                    |                                         |                |                  |                  |                 |       |

|               | •                                               | it not inverted                         |                |                  |                  |                 |       |

| bit 3         | -                                               | ator Input Switc                        | h bit          |                  |                  |                 |       |

|               | $\frac{\text{When CM} < 2}{1 - C1 \text{ Vis}}$ | : <u>0&gt; = 110:</u><br>connects to RD |                | LL.              |                  |                 |       |

|               |                                                 | connects to RD                          |                |                  |                  |                 |       |

|               | -                                               | connects to RD                          |                |                  |                  |                 |       |

|               | C2 VIN-                                         | connects to RD                          | 3/PSP3/C2IN    | -                |                  |                 |       |

| bit 2-0       | CM<2:0>: Co                                     | omparator Mode                          | e bits         |                  |                  |                 |       |

|               | Figure 21-1                                     | shows the Com                           | parator mode   | s and the CM<    | 2:0> bit setting | S.              |       |

|               |                                                 |                                         |                |                  |                  |                 |       |

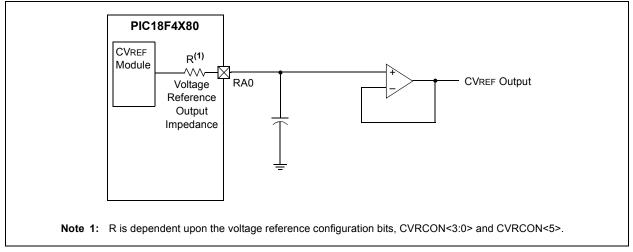

### FIGURE 22-2: COMPARATOR VOLTAGE REFERENCE OUTPUT BUFFER EXAMPLE

#### TABLE 22-1: REGISTERS ASSOCIATED WITH COMPARATOR VOLTAGE REFERENCE

| Name                  | Bit 7                 | Bit 6                 | Bit 5   | Bit 4                        | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Reset<br>Values<br>on Page: |  |

|-----------------------|-----------------------|-----------------------|---------|------------------------------|-------|-------|-------|-------|-----------------------------|--|

| CVRCON <sup>(2)</sup> | CVREN                 | CVROE                 | CVRR    | CVRSS                        | CVR3  | CVR2  | CVR1  | CVR0  | 57                          |  |

| CMCON <sup>(2)</sup>  | C2OUT                 | C10UT                 | C2INV   | C1INV                        | CIS   | CM2   | CM1   | CM0   | 57                          |  |

| TRISA                 | TRISA7 <sup>(1)</sup> | TRISA6 <sup>(1)</sup> | PORTA D | ORTA Data Direction Register |       |       |       |       |                             |  |

**Legend:** Shaded cells are not used with the comparator voltage reference.

**Note 1:** PORTA pins are enabled based on oscillator configuration.

2: These registers are unimplemented on PIC18F2X80 devices.

# 23.2 HLVD Setup

The following steps are needed to set up the HLVD module:

- 1. Disable the module by clearing the HLVDEN bit (HLVDCON<4>).

- 2. Write the value to the HLVDL<3:0> bits that select the desired HLVD trip point.

- Set the VDIRMAG bit to detect high voltage (VDIRMAG = 1) or low voltage (VDIRMAG = 0).

- 4. Enable the HLVD module by setting the HLVDEN bit.

- 5. Clear the HLVD interrupt flag (PIR2<2>), which may have been set from a previous interrupt.

- Enable the HLVD interrupt if interrupts are desired by setting the HLVDIE and GIE bits (PIE<2> and INTCON<7>). An interrupt will not be generated until the IRVST bit is set.

# 23.3 Current Consumption

When the module is enabled, the HLVD comparator and voltage divider are enabled and will consume static current. The total current consumption, when enabled, is specified in electrical specification parameter D022B. Depending on the application, the HLVD module does not need to be operating constantly. To decrease the current requirements, the HLVD circuitry may only need to be enabled for short periods where the voltage is checked. After doing the check, the HLVD module may be disabled.

# 23.4 HLVD Start-up Time

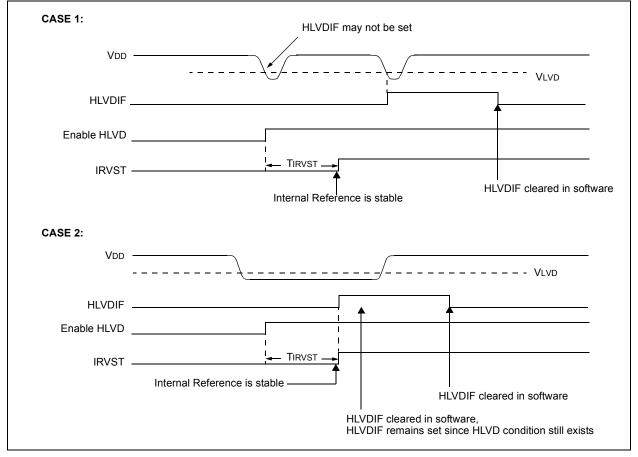

The internal reference voltage of the HLVD module, specified in electrical specification parameter D420, may be used by other internal circuitry, such as the Programmable Brown-out Reset. If the HLVD or other circuits using the voltage reference are disabled to lower the device's current consumption, the reference voltage circuit will require time to become stable before a low or high-voltage condition can be reliably detected. This start-up time, TIRVST, is an interval that is independent of device clock speed. It is specified in electrical specification parameter 36.

The HLVD interrupt flag is not enabled until TIRVST has expired and a stable reference voltage is reached. For this reason, brief excursions beyond the set point may not be detected during this interval. Refer to Figure 23-2 or Figure 23-3.

#### 24.2.6 CAN INTERRUPT REGISTERS

The registers in this section are the same as described in **Section 10.0 "Interrupts"**. They are duplicated here for convenience.

| Made A     | R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Mode 0     | IRXIF WAKIF ERRIF TXB2IF TXB1IF <sup>(1)</sup> TXB0IF <sup>(1)</sup> RXB1IF RXB0IF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Mode 1,2   | R/W-0         R/W-0 <th< td=""></th<> |

|            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|            | bit 7 bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |