Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

|                            | Antina                                                                    |

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 40MHz                                                                     |

| Connectivity               | CANbus, I <sup>2</sup> C, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                               |

| Number of I/O              | 36                                                                        |

| Program Memory Size        | 32KB (16K x 16)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 1.5K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                               |

| Data Converters            | A/D 11x10b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

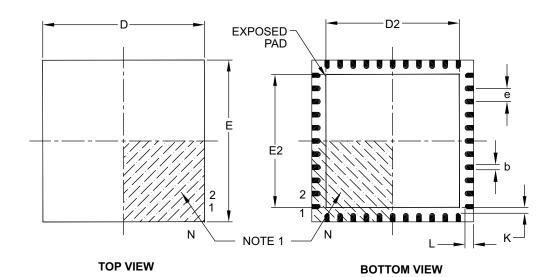

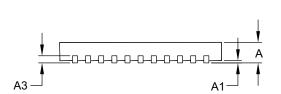

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 44-TQFP                                                                   |

| Supplier Device Package    | 44-TQFP (10x10)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f4580-i-pt |

#### TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@mail.microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

#### **Most Current Data Sheet**

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

#### **Frrata**

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- · Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

- The Microchip Corporate Literature Center; U.S. FAX: (480) 792-7277

When contacting a sales office or the literature center, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com/cn to receive the most current information on all of our products.

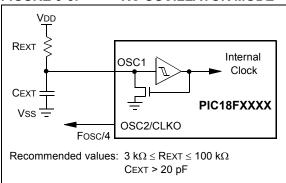

#### 3.4 RC Oscillator

For timing insensitive applications, the "RC" and "RCIO" device options offer additional cost savings. The actual oscillator frequency is a function of several factors:

- · supply voltage

- values of the external resistor (REXT) and capacitor (CEXT)

- · operating temperature

Given the same device, operating voltage and temperature and component values, there will also be unit-to-unit frequency variations. These are due to factors such as:

- · normal manufacturing variation

- difference in lead frame capacitance between package types (especially for low CEXT values)

- variations within the tolerance of limits of REXT and CEXT

In the RC Oscillator mode, the oscillator frequency divided by 4 is available on the OSC2 pin. This signal may be used for test purposes or to synchronize other logic. Figure 3-5 shows how the R/C combination is connected.

FIGURE 3-5: RC OSCILLATOR MODE

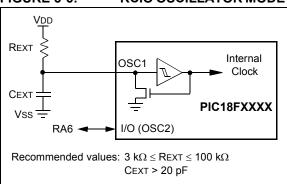

The RCIO Oscillator mode (Figure 3-6) functions like the RC mode, except that the OSC2 pin becomes an additional general purpose I/O pin. The I/O pin becomes bit 6 of PORTA (RA6).

FIGURE 3-6: RCIO OSCILLATOR MODE

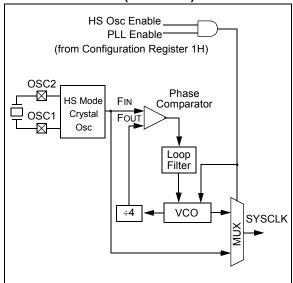

#### 3.5 PLL Frequency Multiplier

A Phase Locked Loop (PLL) circuit is provided as an option for users who wish to use a lower frequency oscillator circuit or to clock the device up to its highest rated frequency from a crystal oscillator. This may be useful for customers who are concerned with EMI due to high-frequency crystals or users who require higher clock speeds from an internal oscillator.

#### 3.5.1 HSPLL OSCILLATOR MODE

The HSPLL mode makes use of the HS mode oscillator for frequencies up to 10 MHz. A PLL then multiplies the oscillator output frequency by 4 to produce an internal clock frequency up to 40 MHz.

The PLL is only available to the crystal oscillator when the FOSC<3:0> Configuration bits are programmed for HSPLL mode (= 0110).

FIGURE 3-7: PLL BLOCK DIAGRAM (HS MODE)

#### 3.5.2 PLL AND INTOSC

The PLL is also available to the internal oscillator block in selected oscillator modes. In this configuration, the PLL is enabled in software and generates a clock output of up to 32 MHz. The operation of INTOSC with the PLL is described in **Section 3.6.4** "PLL in INTOSC **Modes**".

TABLE 5-4: INITIALIZATION CONDITIONS FOR ALL REGISTERS (CONTINUED)

| Register | Applicable Devices |      |      | Power-or<br>Brown-or | ,    | WDT<br>RESET In | Resets,<br>Reset,<br>struction,<br>Resets | Wake-up<br>or Into | via WDT<br>errupt |      |

|----------|--------------------|------|------|----------------------|------|-----------------|-------------------------------------------|--------------------|-------------------|------|

| RXB1SIDH | 2480               | 2580 | 4480 | 4580                 | XXXX | XXXX            | uuuu                                      | uuuu               | uuuu              | uuuu |

| RXB1CON  | 2480               | 2580 | 4480 | 4580                 | 000- | 0000            | 000-                                      | 0000               | uuu-              | uuuu |

| TXB0D7   | 2480               | 2580 | 4480 | 4580                 | XXXX | XXXX            | uuuu                                      | uuuu               | uuuu              | uuuu |

| TXB0D6   | 2480               | 2580 | 4480 | 4580                 | XXXX | XXXX            | uuuu                                      | uuuu               | uuuu              | uuuu |

| TXB0D5   | 2480               | 2580 | 4480 | 4580                 | XXXX | XXXX            | uuuu                                      | uuuu               | uuuu              | uuuu |

| TXB0D4   | 2480               | 2580 | 4480 | 4580                 | XXXX | XXXX            | uuuu                                      | uuuu               | uuuu              | uuuu |

| TXB0D3   | 2480               | 2580 | 4480 | 4580                 | XXXX | XXXX            | uuuu                                      | uuuu               | uuuu              | uuuu |

| TXB0D2   | 2480               | 2580 | 4480 | 4580                 | XXXX | XXXX            | uuuu                                      | uuuu               | uuuu              | uuuu |

| TXB0D1   | 2480               | 2580 | 4480 | 4580                 | XXXX | xxxx            | uuuu                                      | uuuu               | uuuu              | uuuu |

| TXB0D0   | 2480               | 2580 | 4480 | 4580                 | XXXX | XXXX            | uuuu                                      | uuuu               | uuuu              | uuuu |

| TXB0DLC  | 2480               | 2580 | 4480 | 4580                 | -X   | XXXX            | -u                                        | uuuu               | -u                | uuuu |

| TXB0EIDL | 2480               | 2580 | 4480 | 4580                 | XXXX | XXXX            | uuuu                                      | uuuu               | uuuu              | uuuu |

| TXB0EIDH | 2480               | 2580 | 4480 | 4580                 | XXXX | XXXX            | uuuu                                      | uuuu               | -uuu              | uuuu |

| TXB0SIDL | 2480               | 2580 | 4480 | 4580                 | XXX- | x-xx            | uuu-                                      | u-uu               | uuu-              | u-uu |

| TXB0SIDH | 2480               | 2580 | 4480 | 4580                 | XXXX | XXXX            | uuuu                                      | uuuu               | uuuu              | uuuu |

| TXB0CON  | 2480               | 2580 | 4480 | 4580                 | 0000 | 0-00            | 0000                                      | 0-00               | uuuu              | u-uu |

| TXB1D7   | 2480               | 2580 | 4480 | 4580                 | XXXX | XXXX            | uuuu                                      | uuuu               | uuuu              | uuuu |

| TXB1D6   | 2480               | 2580 | 4480 | 4580                 | XXXX | XXXX            | uuuu                                      | uuuu               | uuuu              | uuuu |

| TXB1D5   | 2480               | 2580 | 4480 | 4580                 | XXXX | XXXX            | uuuu                                      | uuuu               | uuuu              | uuuu |

| TXB1D4   | 2480               | 2580 | 4480 | 4580                 | XXXX | XXXX            | uuuu                                      | uuuu               | uuuu              | uuuu |

| TXB1D3   | 2480               | 2580 | 4480 | 4580                 | XXXX | XXXX            | uuuu                                      | uuuu               | uuuu              | uuuu |

| TXB1D2   | 2480               | 2580 | 4480 | 4580                 | XXXX | xxxx            | uuuu                                      | uuuu               | uuuu              | uuuu |

| TXB1D1   | 2480               | 2580 | 4480 | 4580                 | XXXX | xxxx            | uuuu                                      | uuuu               | uuuu              | uuuu |

| TXB1D0   | 2480               | 2580 | 4480 | 4580                 | XXXX | xxxx            | uuuu                                      | uuuu               | uuuu              | uuuu |

| TXB1DLC  | 2480               | 2580 | 4480 | 4580                 | -X   | xxxx            | -u                                        | uuuu               | -u                | uuuu |

| TXB1EIDL | 2480               | 2580 | 4480 | 4580                 | XXXX | xxxx            | uuuu                                      | uuuu               | uuuu              | uuuu |

| TXB1EIDH | 2480               | 2580 | 4480 | 4580                 | XXXX | xxxx            | uuuu                                      | uuuu               | uuuu              | uuuu |

| TXB1SIDL | 2480               | 2580 | 4480 | 4580                 | XXX- | x-xx            | uuu-                                      | u-uu               | uuu-              | uu-u |

| TXB1SIDH | 2480               | 2580 | 4480 | 4580                 | XXXX | xxxx            | uuuu                                      | uuuu               | -uuu              | uuuu |

| TXB1CON  | 2480               | 2580 | 4480 | 4580                 | 0000 | 0-00            | 0000                                      | 0-00               | uuuu              | u-uu |

| TXB2D7   | 2480               | 2580 | 4480 | 4580                 | XXXX |                 | uuuu                                      | uuuu               | 0uuu              | uuuu |

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, read as '0', <math>q = value depends on condition. Shaded cells indicate conditions do not apply for the designated device.

- Note 1: One or more bits in the INTCONx or PIRx registers will be affected (to cause wake-up).

- 2: When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the PC is loaded with the interrupt vector (0008h or 0018h).

- **3:** When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the TOSU, TOSH and TOSL are updated with the current value of the PC. The STKPTR is modified to point to the next location in the hardware stack.

- **4:** See Table 5-3 for Reset value for specific condition.

- **5:** Bits 6 and 7 of PORTA, LATA and TRISA are enabled, depending on the oscillator mode selected. When not enabled as PORTA pins, they are disabled and read '0'.

- **6:** This register reads all '0's until ECAN™ technology is set up in Mode 1 or Mode 2.

TABLE 6-2: REGISTER FILE SUMMARY (PIC18F2480/2580/4480/4580) (CONTINUED)

| File Name | Bit 7   | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   | Value on POR, BOR | Details on Page: |

|-----------|---------|---------|---------|---------|---------|---------|---------|---------|-------------------|------------------|

| TXB1D1    | TXB1D17 | TXB1D16 | TXB1D15 | TXB1D14 | TXB1D13 | TXB1D12 | TXB1D11 | TXB1D10 | xxxx xxxx         | 60, 290          |

| TXB1D0    | TXB1D07 | TXB1D06 | TXB1D05 | TXB1D04 | TXB1D03 | TXB1D02 | TXB1D01 | TXB1D00 | xxxx xxxx         | 60, 290          |

| TXB1DLC   | _       | TXRTR   | _       | _       | DLC3    | DLC2    | DLC1    | DLC0    | -x xxxx           | 60, 291          |

| TXB1EIDL  | EID7    | EID6    | EID5    | EID4    | EID3    | EID2    | EID1    | EID0    | xxxx xxxx         | 60, 290          |

| TXB1EIDH  | EID15   | EID14   | EID13   | EID12   | EID11   | EID10   | EID9    | EID8    | xxxx xxxx         | 60, 289          |

| TXB1SIDL  | SID2    | SID1    | SID0    | -       | EXIDE   | ı       | EID17   | EID16   | xxx- x-xx         | 60, 289          |

| TXB1SIDH  | SID10   | SID9    | SID8    | SID7    | SID6    | SID5    | SID4    | SID3    | xxxx xxxx         | 60, 289          |

| TXB1CON   | TXBIF   | TXABT   | TXLARB  | TXERR   | TXREQ   | 1       | TXPRI1  | TXPRI0  | 0000 0-00         | 60, 288          |

| TXB2D7    | TXB2D77 | TXB2D76 | TXB2D75 | TXB2D74 | TXB2D73 | TXB2D72 | TXB2D71 | TXB2D70 | xxxx xxxx         | 60, 290          |

| TXB2D6    | TXB2D67 | TXB2D66 | TXB2D65 | TXB2D64 | TXB2D63 | TXB2D62 | TXB2D61 | TXB2D60 | xxxx xxxx         | 61, 290          |

| TXB2D5    | TXB2D57 | TXB2D56 | TXB2D55 | TXB2D54 | TXB2D53 | TXB2D52 | TXB2D51 | TXB2D50 | xxxx xxxx         | 61, 290          |

| TXB2D4    | TXB2D47 | TXB2D46 | TXB2D45 | TXB2D44 | TXB2D43 | TXB2D42 | TXB2D41 | TXB2D40 | xxxx xxxx         | 61, 290          |

| TXB2D3    | TXB2D37 | TXB2D36 | TXB2D35 | TXB2D34 | TXB2D33 | TXB2D32 | TXB2D31 | TXB2D30 | xxxx xxxx         | 61, 290          |

| TXB2D2    | TXB2D27 | TXB2D26 | TXB2D25 | TXB2D24 | TXB2D23 | TXB2D22 | TXB2D21 | TXB2D20 | xxxx xxxx         | 61, 290          |

| TXB2D1    | TXB2D17 | TXB2D16 | TXB2D15 | TXB2D14 | TXB2D13 | TXB2D12 | TXB2D11 | TXB2D10 | xxxx xxxx         | 61, 290          |

| TXB2D0    | TXB2D07 | TXB2D06 | TXB2D05 | TXB2D04 | TXB2D03 | TXB2D02 | TXB2D01 | TXB2D00 | xxxx xxxx         | 61, 290          |

| TXB2DLC   | _       | TXRTR   | _       | _       | DLC3    | DLC2    | DLC1    | DLC0    | -x xxxx           | 61, 291          |

| TXB2EIDL  | EID7    | EID6    | EID5    | EID4    | EID3    | EID2    | EID1    | EID0    | xxxx xxxx         | 61, 290          |

| TXB2EIDH  | EID15   | EID14   | EID13   | EID12   | EID11   | EID10   | EID9    | EID8    | xxxx xxxx         | 61, 289          |

| TXB2SIDL  | SID2    | SID1    | SID0    | _       | EXIDE   | _       | EID17   | EID16   | xxxx x-xx         | 61, 289          |

| TXB2SIDH  | SID10   | SID9    | SID8    | SID7    | SID6    | SID5    | SID4    | SID3    | xxx- x-xx         | 61, 289          |

| TXB2CON   | TXBIF   | TXABT   | TXLARB  | TXERR   | TXREQ   | _       | TXPRI1  | TXPRI0  | 0000 0-00         | 61, 288          |

| RXM1EIDL  | EID7    | EID6    | EID5    | EID4    | EID3    | EID2    | EID1    | EID0    | xxxx xxxx         | 61, 310          |

| RXM1EIDH  | EID15   | EID14   | EID13   | EID12   | EID11   | EID10   | EID9    | EID8    | xxxx xxxx         | 61, 310          |

| RXM1SIDL  | SID2    | SID1    | SID0    | _       | EXIDEN  | _       | EID17   | EID16   | xxx- x-xx         | 61, 310          |

| RXM1SIDH  | SID10   | SID9    | SID8    | SID7    | SID6    | SID5    | SID4    | SID3    | xxxx xxxx         | 61, 310          |

| RXM0EIDL  | EID7    | EID6    | EID5    | EID4    | EID3    | EID2    | EID1    | EID0    | xxxx xxxx         | 61, 310          |

| RXM0EIDH  | EID15   | EID14   | EID13   | EID12   | EID11   | EID10   | EID9    | EID8    | xxxx xxxx         | 61, 310          |

| RXM0SIDL  | SID2    | SID1    | SID0    | _       | EXIDEN  | _       | EID17   | EID16   | xxx- x-xx         | 61, 310          |

| RXM0SIDH  | SID10   | SID9    | SID8    | SID7    | SID6    | SID5    | SID4    | SID3    | xxxx xxxx         | 61, 309          |

| RXF5EIDL  | EID7    | EID6    | EID5    | EID4    | EID3    | EID2    | EID1    | EID0    | xxxx xxxx         | 61, 309          |

| RXF5EIDH  | EID15   | EID14   | EID13   | EID12   | EID11   | EID10   | EID9    | EID8    | xxxx xxxx         | 61, 309          |

| RXF5SIDL  | SID2    | SID1    | SID0    | _       | EXIDEN  | _       | EID17   | EID16   | xxx- x-xx         | 61, 308          |

| RXF5SIDH  | SID10   | SID9    | SID8    | SID7    | SID6    | SID5    | SID4    | SID3    | xxxx xxxx         | 61, 308          |

| RXF4EIDL  | EID7    | EID6    | EID5    | EID4    | EID3    | EID2    | EID1    | EID0    | xxxx xxxx         | 61, 309          |

| RXF4EIDH  | EID15   | EID14   | EID13   | EID12   | EID11   | EID10   | EID9    | EID8    | xxxx xxxx         | 61, 309          |

| RXF4SIDL  | SID2    | SID1    | SID0    | _       | EXIDEN  | _       | EID17   | EID16   | xxx- x-xx         | 61, 308          |

| RXF4SIDH  | SID10   | SID9    | SID8    | SID7    | SID6    | SID5    | SID4    | SID3    | xxxx xxxx         | 61, 308          |

| RXF3EIDL  | EID7    | EID6    | EID5    | EID4    | EID3    | EID2    | EID1    | EID0    | xxxx xxxx         | 61, 309          |

| RXF3EIDH  | EID15   | EID14   | EID13   | EID12   | EID11   | EID10   | EID9    | EID8    | xxxx xxxx         | 61, 309          |

| RXF3SIDL  | SID2    | SID1    | SID0    |         | EXIDEN  | _       | EID17   | EID16   | xxx- x-xx         | 62, 308          |

$\textbf{Legend:} \quad x = \text{unknown}, \ u = \text{unchanged}, \ - = \text{unimplemented}, \ q = \text{value depends on condition}$

- Note 1: Bit 21 of the PC is only available in Test mode and Serial Programming modes.

- 2: The SBOREN bit is only available when CONFIG2L<1:0> = 01; otherwise, it is disabled and reads as '0'. See Section 5.4 "Brown-out Reset (BOR)".

- 3: These registers and/or bits are not implemented on PIC18F2X80 devices and are read as '0'. Reset values are shown for PIC18F4X80 devices; individual unimplemented bits should be interpreted as '—'.

- 4: The PLLEN bit is only available in specific oscillator configuration; otherwise, it is disabled and reads as '0'. See Section 3.6.4 "PLL in INTOSC Modes".

- 5: The RE3 bit is only available when Master Clear Reset is disabled (CONFIG3H<7> = 0); otherwise, RE3 reads as '0'. This bit is read-only.

- **6:** RA6/RA7 and their associated latch and direction bits are individually configured as port pins based on various primary oscillator modes. When disabled, these bits read as '0'.

- 7: CAN bits have multiple functions depending on the selected mode of the CAN module.

- 8: This register reads all '0's until the ECAN™ technology is set up in Mode 1 or Mode 2.

- 9: These registers are available on PIC18F4X80 devices only.

#### 7.0 FLASH PROGRAM MEMORY

The Flash program memory is readable, writable and erasable, during normal operation over the entire VDD range.

A read from program memory is executed on one byte at a time. A write to program memory is executed on blocks of 8 bytes at a time. Program memory is erased in blocks of 64 bytes at a time. A bulk erase operation may not be issued from user code.

Writing or erasing program memory will cease instruction fetches until the operation is complete. The program memory cannot be accessed during the write or erase, therefore, code cannot execute. An internal programming timer terminates program memory writes and erases.

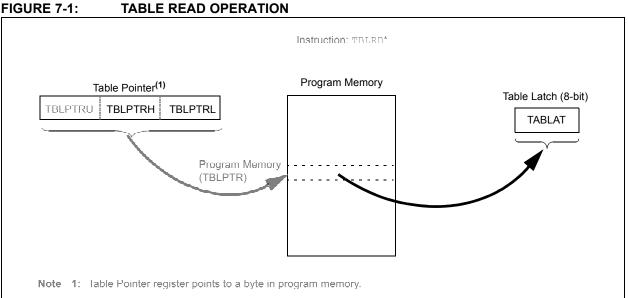

#### 7.1 **Table Reads and Table Writes**

In order to read and write program memory, there are two operations that allow the processor to move bytes between the program memory space and the data RAM:

- Table Read (TBLRD)

- Table Write (TBLWT)

The program memory space is 16 bits wide, while the data RAM space is 8 bits wide. Table reads and table writes move data between these two memory spaces through an 8-bit register (TABLAT).

Table read operations retrieve data from program memory and place it into the data RAM space. Figure 7-1 shows the operation of a table read with program memory and data RAM.

Table write operations store data from the data memory space into holding registers in program memory. The procedure to write the contents of the holding registers into program memory is detailed in Section 7.5 "Writing to Flash Program Memory". Figure 7-2 shows the operation of a table write with program memory and data RAM.

Table operations work with byte entities. A table block containing data, rather than program instructions, is not required to be word aligned. Therefore, a table block can start and end at any byte address. If a table write is being used to write executable code into program memory, program instructions will need to be word aligned.

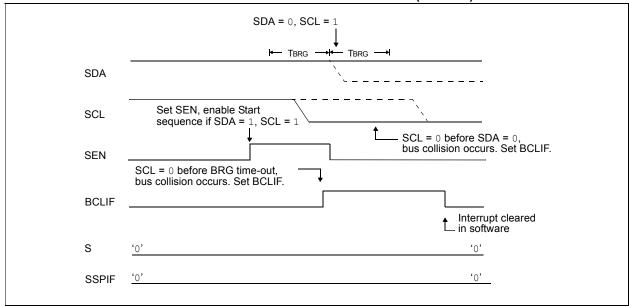

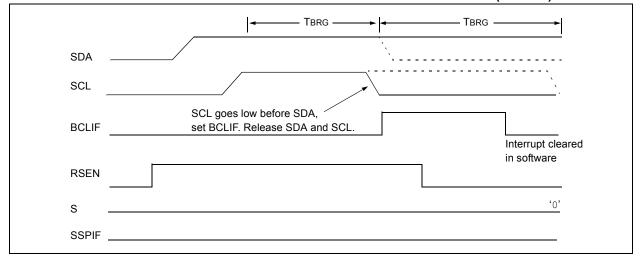

FIGURE 18-27: BUS COLLISION DURING START CONDITION (SCL = 0)

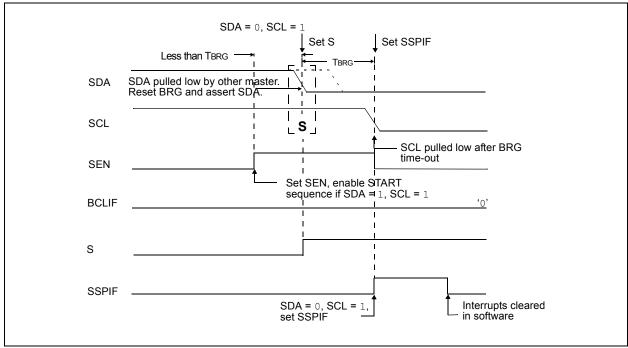

FIGURE 18-28: BRG RESET DUE TO SDA ARBITRATION DURING START CONDITION

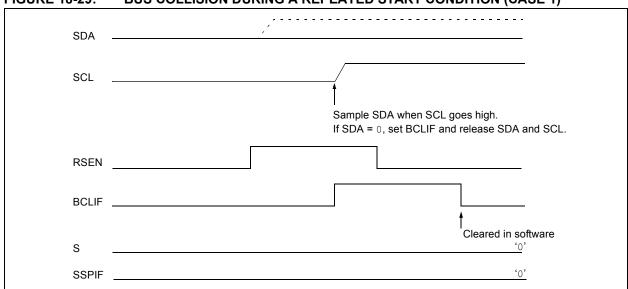

## 18.4.17.2 Bus Collision During a Repeated Start Condition

During a Repeated Start condition, a bus collision occurs if:

- A low level is sampled on SDA when SCL goes from a low level to a high level.

- b) SCL goes low before SDA is asserted low, indicating that another master is attempting to transmit a data '1'.

When the user deasserts SDA and the pin is allowed to float high, the BRG is loaded with SSPADD<6:0> and counts down to 0. The SCL pin is then deasserted and when sampled high, the SDA pin is sampled.

If SDA is low, a bus collision has occurred (i.e., another master is attempting to transmit a data '0', see Figure 18-29). If SDA is sampled high, the BRG is reloaded and begins counting. If SDA goes from high-to-low before the BRG times out, no bus collision occurs because no two masters can assert SDA at exactly the same time.

If SCL goes from high-to-low before the BRG times out, and SDA has not already been asserted, a bus collision occurs. In this case, another master is attempting to transmit a data '1' during the Repeated Start condition, see Figure 18-30.

If, at the end of the BRG time-out, both SCL and SDA are still high, the SDA pin is driven low and the BRG is reloaded and begins counting. At the end of the count regardless of the status of the SCL pin, the SCL pin is driven low and the Repeated Start condition is complete.

FIGURE 18-29: BUS COLLISION DURING A REPEATED START CONDITION (CASE 1)

FIGURE 18-30: BUS COLLISION DURING REPEATED START CONDITION (CASE 2)

#### 19.1.3 AUTO-BAUD RATE DETECT

The Enhanced USART module supports the automatic detection and calibration of baud rate. This feature is active only in Asynchronous mode and while the WUE bit is clear.

The automatic baud rate measurement sequence (Figure 19-1) begins whenever a Start bit is received and the ABDEN bit is set. The calculation is self-averaging.

In the Auto-Baud Rate Detect (ABD) mode, the clock to the BRG is reversed. Rather than the BRG clocking the incoming RX signal, the RX signal is timing the BRG. In ABD mode, the internal Baud Rate Generator is used as a counter to time the bit period of the incoming serial byte stream.

Once the ABDEN bit is set, the state machine will clear the BRG and look for a Start bit. The Auto-Baud Rate Detection must receive a byte with the value 55h (ASCII "U", which is also the LIN/J2602 bus Sync character) in order to calculate the proper bit rate. The measurement is taken over both a low and a high bit time in order to minimize any effects caused by asymmetry of the incoming signal. After a Start bit, the SPBRG begins counting up, using the preselected clock source on the first rising edge of RX. After eight bits on the RX pin or the fifth rising edge, an accumulated value totalling the proper BRG period is left in the SPBRGH:SPBRG register pair. Once the 5th edge is seen (this should correspond to the Stop bit), the ABDEN bit is automatically cleared.

If a rollover of the BRG occurs (an overflow from FFFFh to 0000h), the event is trapped by the ABDOVF status bit (BAUDCON<7>). It is set in hardware by BRG rollovers and can be set or cleared by the user in software. ABD mode remains active after rollover events and the ABDEN bit remains set (Figure 19-2).

While calibrating the baud rate period, the BRG registers are clocked at 1/8th the preconfigured clock rate. Note that the BRG clock can be configured by the BRG16 and BRGH bits. The BRG16 bit must be set to use both SPBRG1 and SPBRGH1 as a 16-bit counter. This allows the user to verify that no carry occurred for 8-bit modes by checking for 00h in the SPBRGH register. Refer to Table 19-4 for counter clock rates to the BRG.

While the ABD sequence takes place, the EUSART state machine is held in Idle. The RCIF interrupt is set once the fifth rising edge on RX is detected. The value in the RCREG needs to be read to clear the RCIF interrupt. The contents of RCREG should be discarded.

- **Note 1:** If the WUE bit is set with the ABDEN bit, Auto-Baud Rate Detection will occur on the byte *following* the Break character.

- 2: It is up to the user to determine that the incoming character baud rate is within the range of the selected BRG clock source. Some combinations of oscillator frequency and EUSART baud rates are not possible due to bit error rates. Overall system timing and communication baud rates must be taken into consideration when using the Auto-Baud Rate Detection feature.

- **3:** To maximize baud rate range, it is recommended to set the BRG16 bit if the auto-baud feature is used.

TABLE 19-4: BRG COUNTER CLOCK RATES

| BRG16 | BRGH | BRG Counter Clock |  |  |  |  |  |

|-------|------|-------------------|--|--|--|--|--|

| 0     | 0    | Fosc/512          |  |  |  |  |  |

| 0     | 1    | Fosc/128          |  |  |  |  |  |

| 1     | 0    | Fosc/128          |  |  |  |  |  |

| 1     | 1    | Fosc/32           |  |  |  |  |  |

#### 19.1.3.1 ABD and EUSART Transmission

Since the BRG clock is reversed during ABD acquisition, the EUSART transmitter cannot be used during ABD. This means that whenever the ABDEN bit is set, TXREG cannot be written to. Users should also ensure that ABDEN does not become set during a transmit sequence. Failing to do this may result in unpredictable EUSART operation.

## 20.4 Operation in Power-Managed Modes

The selection of the automatic acquisition time and A/D conversion clock is determined in part, by the clock source and frequency while in a power-managed mode

If the A/D is expected to operate while the device is in a power-managed mode, the ACQT<2:0> and ADCS<2:0> bits in ADCON2 should be updated in accordance with the clock source to be used in that mode. After entering the mode, an A/D acquisition or conversion may be started. Once started, the device should continue to be clocked by the same clock source until the conversion has been completed.

If desired, the device may be placed into the corresponding Idle mode during the conversion. If the device clock frequency is less than 1 MHz, the A/D RC clock source should be selected.

Operation in the Sleep mode requires the A/D FRC clock to be selected. If bits, ACQT<2:0>, are set to '000' and a conversion is started, the conversion will be delayed one instruction cycle to allow execution of the SLEEP instruction and entry to Sleep mode. The IDLEN bit (OSCCON<7>) must have already been cleared prior to starting the conversion.

#### 20.5 Configuring Analog Port Pins

The ADCON1, TRISA, TRISB and TRISE registers all configure the A/D port pins. The port pins needed as analog inputs must have their corresponding TRIS bits set (input). If the TRIS bit is cleared (output), the digital output level (VOH or VOL) will be converted.

The A/D operation is independent of the state of the CHS<3:0> bits and the TRIS bits.

- Note 1: When reading the PORT register, all pins configured as analog input channels will read as cleared (a low level). Pins configured as digital inputs will convert an analog input. Analog levels on a digitally configured input will be accurately converted.

- 2: Analog levels on any pin defined as a digital input may cause the digital input buffer to consume current out of the device's specification limits.

- **3:** The PBADEN bit in Configuration Register 3H configures PORTB pins to reset as analog or digital pins by controlling how the PCFG bits in ADCON1 are reset.

## 24.2.2 DEDICATED CAN TRANSMIT BUFFER REGISTERS

This section describes the dedicated CAN Transmit Buffer registers and their associated control registers.

#### REGISTER 24-5: TXBnCON: TRANSMIT BUFFER n CONTROL REGISTERS $[0 \le n \le 2]$

| Mada 0 | U-0 | R-0                  | R-0                   | R-0                  | R/W-0                | U-0 | R/W-0                 | R/W-0                 |

|--------|-----|----------------------|-----------------------|----------------------|----------------------|-----|-----------------------|-----------------------|

| Mode 0 | _   | TXABT <sup>(1)</sup> | TXLARB <sup>(1)</sup> | TXERR <sup>(1)</sup> | TXREQ <sup>(2)</sup> | _   | TXPRI1 <sup>(3)</sup> | TXPRI0 <sup>(3)</sup> |

| Mode 1,2  | R/C-0 | R-0                  | R-0                   | R-0                  | R/W-0                | U-0 | R/W-0                 | R/W-0                 |

|-----------|-------|----------------------|-----------------------|----------------------|----------------------|-----|-----------------------|-----------------------|

| Wiode 1,2 | TXBIF | TXABT <sup>(1)</sup> | TXLARB <sup>(1)</sup> | TXERR <sup>(1)</sup> | TXREQ <sup>(2)</sup> | _   | TXPRI1 <sup>(3)</sup> | TXPRI0 <sup>(3)</sup> |

|           | bit 7 |                      |                       |                      |                      |     |                       | bit 0                 |

| Legend:           | C = Clearable bit |                        |                    |

|-------------------|-------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set  | '0' = Bit is cleared   | x = Bit is unknown |

bit 7 Mode 0:

Unimplemented: Read as '0'

Mode 1, 2:

TXBIF: Transmit Buffer Interrupt Flag bit

1 = Transmit buffer has completed transmission of message and may be reloaded

0 = Transmit buffer has not completed transmission of a message

bit 6 TXABT: Transmission Aborted Status bit<sup>(1)</sup>

1 = Message was aborted

0 = Message was not aborted

bit 5 **TXLARB:** Transmission Lost Arbitration Status bit<sup>(1)</sup>

1 = Message lost arbitration while being sent

0 = Message did not lose arbitration while being sent

bit 4 **TXERR:** Transmission Error Detected Status bit<sup>(1)</sup>

1 = A bus error occurred while the message was being sent

0 = A bus error did not occur while the message was being sent

bit 3 **TXREQ:** Transmit Request Status bit<sup>(2)</sup>

1 = Requests sending a message. Clears the TXABT, TXLARB and TXERR bits.

0 = Automatically cleared when the message is successfully sent

bit 2 Unimplemented: Read as '0'

bit 1-0 **TXPRI<1:0>:** Transmit Priority bits<sup>(3)</sup>

11 = Priority Level 3 (highest priority)

10 = Priority Level 2

01 = Priority Level 1

00 = Priority Level 0 (lowest priority)

Note 1: This bit is automatically cleared when TXREQ is set.

2: While TXREQ is set, Transmit Buffer registers remain read-only. Clearing this bit in software while the bit is set will request a message abort.

**3:** These bits define the order in which transmit buffers will be transferred. They do not alter the CAN message identifier.

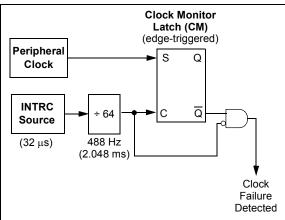

#### 25.4 Fail-Safe Clock Monitor

The Fail-Safe Clock Monitor (FSCM) allows the microcontroller to continue operation in the event of an external oscillator failure by automatically switching the device clock to the internal oscillator block. The FSCM function is enabled by setting the FCMEN Configuration bit

When FSCM is enabled, the INTRC oscillator runs at all times to monitor clocks to peripherals and provide a backup clock in the event of a clock failure. Clock monitoring (shown in Figure 25-3) is accomplished by creating a sample clock signal, which is the INTRC output divided by 64. This allows ample time between FSCM sample clocks for a peripheral clock edge to occur. The peripheral device clock and the sample clock are presented as inputs to the Clock Monitor (CM) latch. The CM is set on the falling edge of the device clock source, but cleared on the rising edge of the sample clock.

FIGURE 25-3: FSCM BLOCK DIAGRAM

Clock failure is tested for on the falling edge of the sample clock. If a sample clock falling edge occurs while CM is still set, a clock failure has been detected (Figure 25-4). This causes the following:

- the FSCM generates an oscillator fail interrupt by setting bit, OSCFIF (PIR2<7>);

- the device clock source is switched to the internal oscillator block (OSCCON is not updated to show the current clock source – this is the Fail-Safe condition); and

- · the WDT is reset.

During switchover, the postscaler frequency from the internal oscillator block may not be sufficiently stable for timing-sensitive applications. In these cases, it may be desirable to select another clock configuration and enter an alternate power-managed mode. This can be done to attempt a partial recovery or execute a controlled shutdown. See Section 4.1.4 "Multiple Sleep Commands" and Section 25.3.1 "Special Considerations for Using Two-Speed Start-up" for more details.

To use a higher clock speed on wake-up, the INTOSC or postscaler clock sources can be selected to provide a higher clock speed by setting bits, IRCF<2:0>, immediately after Reset. For wake-ups from Sleep, the INTOSC or postscaler clock sources can be selected by setting the IRCF<2:0> bits prior to entering Sleep mode.

The FSCM will detect failures of the primary or secondary clock sources only. If the internal oscillator block fails, no failure would be detected, nor would any action be possible.

#### 25.4.1 FSCM AND THE WATCHDOG TIMER

Both the FSCM and the WDT are clocked by the INTRC oscillator. Since the WDT operates with a separate divider and counter, disabling the WDT has no effect on the operation of the INTRC oscillator when the FSCM is enabled.

As already noted, the clock source is switched to the INTOSC clock when a clock failure is detected. Depending on the frequency selected by the IRCF<2:0> bits, this may mean a substantial change in the speed of code execution. If the WDT is enabled with a small prescale value, a decrease in clock speed allows a WDT time-out to occur and a subsequent device Reset. For this reason, Fail-Safe Clock events also reset the WDT and postscaler, allowing it to start timing from when execution speed was changed and decreasing the likelihood of an erroneous time-out.

#### 25.4.2 EXITING FAIL-SAFE OPERATION

The Fail-Safe condition is terminated by either a device Reset or by entering a power-managed mode. On Reset, the controller starts the primary clock source specified in Configuration Register 1H (with any required start-up delays that are required for the oscillator mode, such as OST or PLL timer). The INTOSC multiplexer provides the device clock until the primary clock source becomes ready (similar to a Two-Speed Start-up). The clock source is then switched to the primary clock (indicated by the OSTS bit in the OSCCON register becoming set). The Fail-Safe Clock Monitor then resumes monitoring the peripheral clock.

The primary clock source may never become ready during start-up. In this case, operation is clocked by the INTOSC multiplexer. The OSCCON register will remain in its Reset state until a power-managed mode is entered.

| ADDWFC            | ADD W and Carry bit to f                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                             |      |      |  |  |  |  |  |  |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|------|------|--|--|--|--|--|--|

| Syntax:           | ADDWFC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | f {,d {,                    | a}}  |      |  |  |  |  |  |  |

| Operands:         | $0 \le f \le 258$<br>$d \in [0,1]$<br>$a \in [0,1]$                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 5                           |      |      |  |  |  |  |  |  |

| Operation:        | (W) + (f) +                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | $(C) \rightarrow d\epsilon$ | est  |      |  |  |  |  |  |  |

| Status Affected:  | N,OV, C, DC, Z                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                             |      |      |  |  |  |  |  |  |

| Encoding:         | 0010                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 00da                        | ffff | ffff |  |  |  |  |  |  |

| Description:      | Add W, the Carry flag and data memory location 'f'. If 'd' is '0', the result is placed in W. If 'd' is '1', the result is placed in data memory location 'f'.  If 'a' is '0', the Access Bank is selected. If 'a' is '1', the BSR is used to select the GPR bank.  If 'a' is '0' and the extended instruction set is enabled, this instruction operates in Indexed Literal Offset Addressing mode whenever f ≤ 95 (5Fh). See Section 26.2.3 "Byte-Oriented and Bit-Oriented Instructions in Indexed |                             |      |      |  |  |  |  |  |  |

| Words:            | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                             |      |      |  |  |  |  |  |  |

| Cycles:           | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                             |      |      |  |  |  |  |  |  |

| Q Cycle Activity: |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                             |      |      |  |  |  |  |  |  |

| Q1                | Q2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Q3                          | 1    | Q4   |  |  |  |  |  |  |

Process

Data

REG, 0, 1

Write to

destination

| AND   | LW             | AND Lite            | AND Literal with W                                                                 |      |          |  |  |  |  |  |  |

|-------|----------------|---------------------|------------------------------------------------------------------------------------|------|----------|--|--|--|--|--|--|

| Synta | ax:            | ANDLW               | k                                                                                  |      |          |  |  |  |  |  |  |

| Oper  | ands:          | $0 \le k \le 255$   | 5                                                                                  |      |          |  |  |  |  |  |  |

| Oper  | ation:         | (W) .AND.           | $k\toW$                                                                            |      |          |  |  |  |  |  |  |

| Statu | s Affected:    | N, Z                | N, Z                                                                               |      |          |  |  |  |  |  |  |

| Enco  | ding:          | 0000                | 1011                                                                               | kkkk | kkkk     |  |  |  |  |  |  |

| Desc  | ription:       |                     | The contents of W are ANDed with the 8-bit literal 'k'. The result is placed in W. |      |          |  |  |  |  |  |  |

| Word  | ls:            | 1                   | 1                                                                                  |      |          |  |  |  |  |  |  |

| Cycle | es:            | 1                   |                                                                                    |      |          |  |  |  |  |  |  |

| QC    | ycle Activity: |                     |                                                                                    |      |          |  |  |  |  |  |  |

| Q1    |                | Q2                  | Q3                                                                                 | 3    | Q4       |  |  |  |  |  |  |

|       | Decode         | Read literal<br>'k' | Proce<br>Data                                                                      |      | ite to W |  |  |  |  |  |  |

|       |                | •                   |                                                                                    |      |          |  |  |  |  |  |  |

05Fh

Example: ANDLW

Before Instruction

W = A3h

After Instruction

W = 03h

Example:

Decode

Carry bit = 1 REG = 02h W = 4Dh

Read register 'f'

ADDWFC

After Instruction

Before Instruction

$\begin{array}{ccc} \text{Carry bit} & = & 0 \\ \text{REG} & = & 02h \\ \text{W} & = & 50h \end{array}$

| INC   | sz                                            | Incremen                  | t f, Skip if 0                            |                                  | INF   | SNZ                     | Incremen                                                               | t f, Skip if n                                                                       | ot 0            |  |  |

|-------|-----------------------------------------------|---------------------------|-------------------------------------------|----------------------------------|-------|-------------------------|------------------------------------------------------------------------|--------------------------------------------------------------------------------------|-----------------|--|--|

| Synta | ax:                                           | INCFSZ f                  | {,d {,a}}                                 |                                  | Synt  | ax:                     | INFSNZ f                                                               | {,d {,a}}                                                                            |                 |  |  |

| Oper  | ands:                                         | $0 \le f \le 255$         |                                           |                                  | Ope   | rands:                  | $0 \leq f \leq 255$                                                    |                                                                                      |                 |  |  |

| •     |                                               | $d \in \left[0,1\right]$  |                                           |                                  |       |                         | $d \in [0,1]$                                                          |                                                                                      |                 |  |  |

|       |                                               | a ∈ [0,1]                 |                                           |                                  | 0     |                         | a ∈ [0,1]                                                              |                                                                                      |                 |  |  |

| Oper  | ation:                                        | $(f) + 1 \rightarrow de$  |                                           |                                  | Ope   | ration:                 | (f) + 1 → de<br>skip if resul                                          | •                                                                                    |                 |  |  |

|       |                                               | skip if resul             | <b>t =</b> 0                              |                                  | Stati | us Affected:            | None                                                                   | 0                                                                                    |                 |  |  |

| Statu | s Affected:                                   | None                      |                                           |                                  |       | oding:                  |                                                                        |                                                                                      |                 |  |  |

| Enco  | ding:                                         | 0011                      | 11da ff                                   | ff ffff                          |       | cription:               |                                                                        | ts of register "                                                                     |                 |  |  |

| Desc  | ription:                                      |                           | ts of register "                          |                                  | DCS   | onpuon.                 |                                                                        | d. If 'd' is '0', t                                                                  |                 |  |  |

|       |                                               |                           | d. If 'd' is '0', t                       |                                  |       |                         | placed in W                                                            | /. If 'd' is '1', th                                                                 | ne result is    |  |  |

|       |                                               | •                         | /. If 'd' is '1', th<br>k in register 'f' |                                  |       |                         | •                                                                      | k in register 'f'                                                                    |                 |  |  |

|       |                                               | •                         | is '0', the nex                           |                                  |       |                         |                                                                        | is not '0', the which is alread                                                      |                 |  |  |

|       |                                               |                           | eady fetched i                            |                                  |       |                         |                                                                        | and a NOP is e                                                                       | •               |  |  |

|       |                                               |                           | is executed in:<br>le instruction.        | stead, making                    |       |                         | instead, ma                                                            | iking it a two-d                                                                     | cycle           |  |  |

|       |                                               | ,                         |                                           | nk is selected.                  |       |                         |                                                                        | he Access Ba                                                                         | nk is selected. |  |  |

|       |                                               | •                         |                                           | d to select the                  |       |                         | ,                                                                      |                                                                                      | d to select the |  |  |

|       |                                               | GPR bank.                 |                                           |                                  |       |                         | GPR bank.                                                              |                                                                                      |                 |  |  |

|       |                                               |                           | nd the extend                             | ed instruction<br>ction operates |       |                         |                                                                        | If 'a' is '0' and the extended instruction set is enabled, this instruction operates |                 |  |  |

|       |                                               |                           | Literal Offset A                          | •                                |       |                         |                                                                        | ed, this instru<br>Literal Offset <i>I</i>                                           |                 |  |  |

|       |                                               | mode when                 | never $f \le 95$ (5                       | Fh). See                         |       |                         |                                                                        | ever f ≤ 95 (5                                                                       |                 |  |  |

|       |                                               |                           | .2.3 "Byte-Or<br>ed Instruction           |                                  |       |                         | Section 26.2.3 "Byte-Oriented and Bit-Oriented Instructions in Indexed |                                                                                      |                 |  |  |

|       |                                               |                           | set Mode" for                             |                                  |       |                         |                                                                        | ed Instruction<br>set Mode" for                                                      |                 |  |  |

| Word  | s:                                            | 1                         |                                           |                                  | Word  | ds:                     | 1                                                                      |                                                                                      |                 |  |  |

| Cycle | es:                                           | 1(2)                      |                                           |                                  | Cycl  | es:                     | 1(2)                                                                   |                                                                                      |                 |  |  |

|       |                                               |                           | cycles if skip a                          |                                  |       |                         | Note: 3 d                                                              | cycles if skip a                                                                     | nd followed     |  |  |

|       |                                               | by                        | a 2-word instr                            | uction.                          |       |                         | by                                                                     | a 2-word instr                                                                       | ruction.        |  |  |

| Q C   | ycle Activity:                                |                           |                                           |                                  | QC    | cycle Activity:         |                                                                        |                                                                                      |                 |  |  |

| i     | Q1                                            | Q2                        | Q3                                        | Q4                               |       | Q1                      | Q2                                                                     | Q3                                                                                   | Q4              |  |  |

|       | Decode                                        | Read                      | Process                                   | Write to                         |       | Decode                  | Read                                                                   | Process                                                                              | Write to        |  |  |

| lf sk | in·                                           | register 'f'              | Data                                      | destination                      | lf ol | L                       | register 'f'                                                           | Data                                                                                 | destination     |  |  |

| 11 31 | ιρ.<br>Q1                                     | Q2                        | Q3                                        | Q4                               | If sk | •                       | 00                                                                     | 02                                                                                   | 04              |  |  |

|       | No                                            | No                        | No                                        | No                               |       | Q1<br>No                | Q2<br>No                                                               | Q3<br>No                                                                             | Q4<br>No        |  |  |

|       | operation                                     | operation                 | operation                                 | operation                        |       | operation               | operation                                                              | operation                                                                            | operation       |  |  |

| lf sk | ip and followe                                | d by 2-word in:           | struction:                                |                                  | If sk | <u> </u>                | d by 2-word in                                                         |                                                                                      |                 |  |  |

|       | Q1                                            | Q2                        | Q3                                        | Q4                               |       | Q1                      | Q2                                                                     | Q3                                                                                   | Q4              |  |  |

|       | No                                            | No                        | No                                        | No                               |       | No                      | No                                                                     | No                                                                                   | No              |  |  |

|       | operation                                     | operation                 | operation                                 | operation                        |       | operation               | operation                                                              | operation                                                                            | operation       |  |  |

|       | No<br>operation                               | No operation              | No operation                              | No operation                     |       | No operation            | No operation                                                           | No operation                                                                         | No operation    |  |  |

| Exam  | Example: HERE INCFSZ CNT, 1, 0 NZERO : ZERO : |                           | <u>Exar</u>                               |                                  |       | G, 1, 0                 |                                                                        |                                                                                      |                 |  |  |

|       | Before Instruc                                |                           |                                           |                                  |       | Before Instruc          |                                                                        |                                                                                      |                 |  |  |

|       | PC                                            |                           | (HERE)                                    |                                  |       | PC<br>After Instruction |                                                                        | (HERE)                                                                               |                 |  |  |

|       | After Instruction                             | on<br>= CNT+ <sup>-</sup> | 1                                         |                                  |       | REG                     | = REG +                                                                | 1                                                                                    |                 |  |  |

|       | If CNT                                        | = 0;                      |                                           |                                  |       | If REG                  | <b>≠</b> 0;                                                            |                                                                                      |                 |  |  |

|       | PC<br>If CNT                                  | = Address<br>≠ 0;         | S (ZERO)                                  |                                  |       | PC<br>If REG            | = Address<br>= 0;                                                      | (NZERO)                                                                              |                 |  |  |

|       | PC                                            |                           | S (NZERO)                                 |                                  |       | PC                      | = Address                                                              | S (ZERO)                                                                             |                 |  |  |

#### 28.2 DC Characteristics: Power-Down and Supply Current

PIC18F2480/2580/4480/4580 (Industrial, Extended) PIC18LF2480/2580/4480/4580 (Industrial) (Continued)

| PIC18LF      | <b>2480/2580/4480/4580</b><br>strial)          | Standard Operating Conditions (unless otherwise stated)  Operating temperature -40°C ≤ TA ≤ +85°C for industrial |                    |       |            |                                                                                                      |                                        |  |  |  |

|--------------|------------------------------------------------|------------------------------------------------------------------------------------------------------------------|--------------------|-------|------------|------------------------------------------------------------------------------------------------------|----------------------------------------|--|--|--|

|              | <b>480/2580/4480/4580</b><br>strial, Extended) |                                                                                                                  | rd Oper<br>ng temp |       | -40°C ≤ TA | s otherwise stated $A \le +85^{\circ}\text{C}$ for indust $A \le +125^{\circ}\text{C}$ for extending | rial                                   |  |  |  |

| Param<br>No. | Device                                         | Тур                                                                                                              | Max                | Units | Conditions |                                                                                                      |                                        |  |  |  |

|              | Supply Current (IDD) <sup>(2,3)</sup>          |                                                                                                                  |                    |       |            |                                                                                                      |                                        |  |  |  |

|              | PIC18LF2X80/4X80                               | 300                                                                                                              | 390                | μΑ    | -40°C      |                                                                                                      |                                        |  |  |  |

|              |                                                | 320                                                                                                              | 390                | μΑ    | +25°C      | VDD = 2.0V                                                                                           |                                        |  |  |  |

|              |                                                | 330                                                                                                              | 390                | μΑ    | +85°C      |                                                                                                      |                                        |  |  |  |

|              | PIC18LF2X80/4X80                               | 450                                                                                                              | 550                | μΑ    | -40°C      |                                                                                                      |                                        |  |  |  |

|              |                                                | 470                                                                                                              | 550                | μΑ    | +25°C      | VDD = 3.0V                                                                                           | Fosc = 1 MHz<br>( <b>RC_IDLE</b> mode, |  |  |  |

|              |                                                | 490                                                                                                              | 550                | μА    | +85°C      |                                                                                                      | Internal oscillator source)            |  |  |  |

|              | All devices                                    | 840                                                                                                              | 1030               | μА    | -40°C      |                                                                                                      | ,                                      |  |  |  |

|              |                                                | 880                                                                                                              | 1030               | μΑ    | +25°C      | VDD = 5.0V                                                                                           |                                        |  |  |  |

|              |                                                | 900                                                                                                              | 1030               | μА    | +85°C      | VDD = 5.0 V                                                                                          |                                        |  |  |  |

|              | Extended devices only                          | 2.8                                                                                                              | 3.2                | mA    | +125°C     |                                                                                                      |                                        |  |  |  |

|              | PIC18LF2X80/4X80                               | 760                                                                                                              | 1050               | μΑ    | -40°C      |                                                                                                      |                                        |  |  |  |

|              |                                                | 790                                                                                                              | 1050               | μΑ    | +25°C      | VDD = 2.0V                                                                                           |                                        |  |  |  |

|              |                                                | 810                                                                                                              | 1050               | μΑ    | +85°C      |                                                                                                      |                                        |  |  |  |

|              | PIC18LF2X80/4X80                               | 1.2                                                                                                              | 1.5                | mA    | -40°C      |                                                                                                      |                                        |  |  |  |

|              |                                                | 1.2                                                                                                              | 1.5                | mA    | +25°C      | VDD = 3.0V                                                                                           | Fosc = 4 MHz<br>( <b>RC IDLE</b> mode, |  |  |  |

|              |                                                | 1.3                                                                                                              | 1.5                | mA    | +85°C      |                                                                                                      | Internal oscillator source)            |  |  |  |

|              | All devices                                    | 2.2                                                                                                              | 2.7                | mA    | -40°C      |                                                                                                      |                                        |  |  |  |

|              |                                                | 2.3                                                                                                              | 2.7                | mA    | +25°C      | VDD = 5.0V                                                                                           |                                        |  |  |  |

|              |                                                | 2.3                                                                                                              | 2.7                | mA    | +85°C      | 133 0.01                                                                                             |                                        |  |  |  |

|              | Extended devices only                          | 4.7                                                                                                              | 5.5                | mA    | +125°C     |                                                                                                      |                                        |  |  |  |

|              | PIC18LF2X80/4X80                               | 410                                                                                                              | 550                | μА    | -40°C      |                                                                                                      |                                        |  |  |  |

|              |                                                | 420                                                                                                              | 550                | μА    | +25°C      | VDD = 2.0V                                                                                           |                                        |  |  |  |

|              |                                                | 420                                                                                                              | 550                | μΑ    | +85°C      |                                                                                                      |                                        |  |  |  |

|              | PIC18LF2X80/4X80                               | 870                                                                                                              | 830                | μΑ    | -40°C      | 4                                                                                                    | Fosc = 1 MHz                           |  |  |  |

|              |                                                | 770                                                                                                              | 830                | μΑ    | +25°C      | VDD = 3.0V                                                                                           | (PRI RUN,                              |  |  |  |

|              |                                                | 720                                                                                                              | 830                | μΑ    | +85°C      |                                                                                                      | EC oscillator)                         |  |  |  |