Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 40MHz                                                                      |

| Connectivity               | CANbus, I <sup>2</sup> C, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                |

| Number of I/O              | 36                                                                         |

| Program Memory Size        | 32KB (16K x 16)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 1.5K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                                |

| Data Converters            | A/D 11x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-TQFP                                                                    |

| Supplier Device Package    | 44-TQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f4580t-i-pt |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

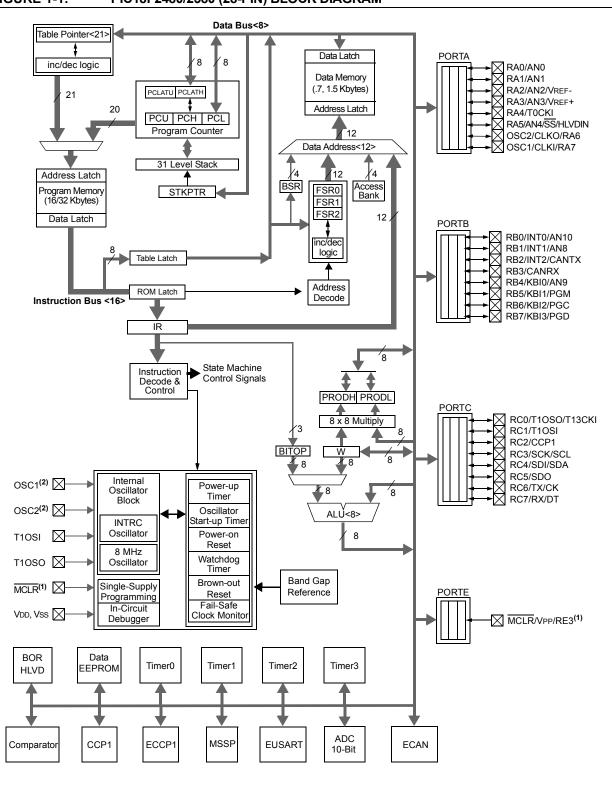

### FIGURE 1-1: PIC18F2480/2580 (28-PIN) BLOCK DIAGRAM

Note 1: RE3 is multiplexed with MCLR and is only available when the MCLR Resets are disabled.

2: OSC1/CLKI and OSC2/CLKO are only available in select oscillator modes and when these pins are not being used as digital I/O. Refer to Section 3.0 "Oscillator Configurations" for additional information.

|                  | Pin Nu         | mber | Pin  | Buffer |                                                          |  |  |  |

|------------------|----------------|------|------|--------|----------------------------------------------------------|--|--|--|

| Pin Name         | SPDIP,<br>SOIC | QFN  | Туре | Туре   | Description                                              |  |  |  |

|                  |                |      |      |        | PORTB is a bidirectional I/O port. PORTB can be software |  |  |  |

|                  |                |      |      |        | programmed for internal weak pull-ups on all inputs.     |  |  |  |

| RB0/INT0/ AN10   | 21             | 18   |      |        |                                                          |  |  |  |

| RB0              |                |      | I/O  | TTL    | Digital I/O.                                             |  |  |  |

| INT0             |                |      | I    | ST     | External Interrupt 0.                                    |  |  |  |

| AN10             |                |      | I    | Analog | Analog Input 10.                                         |  |  |  |

| RB1/INT1/AN8     | 22             | 19   |      |        |                                                          |  |  |  |

| RB1              |                |      | I/O  | TTL    | Digital I/O.                                             |  |  |  |

| INT1             |                |      | I    | ST     | External Interrupt 1.                                    |  |  |  |

| AN8              |                |      | I    | Analog | Analog Input 8.                                          |  |  |  |

| RB2/INT2/CANTX   | 23             | 20   |      |        |                                                          |  |  |  |

| RB2              |                |      | I/O  | TTL    | Digital I/O.                                             |  |  |  |

| INT2             |                |      | I    | ST     | External Interrupt 2.                                    |  |  |  |

| CANTX            |                |      | 0    | TTL    | CAN bus TX.                                              |  |  |  |

| RB3/CANRX        | 24             | 21   |      |        |                                                          |  |  |  |

| RB3              |                |      | I/O  | TTL    | Digital I/O.                                             |  |  |  |

| CANRX            |                |      | I    | TTL    | CAN bus RX.                                              |  |  |  |

| RB4/KBI0/AN9     | 25             | 22   |      |        |                                                          |  |  |  |

| RB4              | 20             | 22   | I/O  | TTL    | Digital I/O.                                             |  |  |  |

| KBI0             |                |      |      | TTL    | Interrupt-on-change pin.                                 |  |  |  |

| AN9              |                |      | i    | Analog | Analog Input 9.                                          |  |  |  |

| RB5/KBI1/PGM     | 26             | 23   |      | - 5    |                                                          |  |  |  |

| RB5              | 20             | 20   | I/O  | TTL    | Digital I/O.                                             |  |  |  |

| KBI1             | 1              |      | "U   | TTL    | Interrupt-on-change pin.                                 |  |  |  |

| PGM              |                |      | I/O  | ST     | Low-Voltage ICSP™ Programming enable pin.                |  |  |  |

| RB6/KBI2/PGC     | 27             | 24   | -    |        |                                                          |  |  |  |

| RB6              | 21             | 27   | I/O  | TTL    | Digital I/O.                                             |  |  |  |

| KBI2             |                |      | "O   | TTL    | Interrupt-on-change pin.                                 |  |  |  |

| PGC              |                |      | I/O  | ST     | In-Circuit Debugger and ICSP programming clock pin.      |  |  |  |

| RB7/KBI3/PGD     | 28             | 25   |      |        |                                                          |  |  |  |

| RB7              | 20             | 20   | I/O  | TTL    | Digital I/O.                                             |  |  |  |

| KBI3             |                |      | 1/0  | TTL    | Interrupt-on-change pin.                                 |  |  |  |

| PGD              |                |      | I/O  | ST     | In-Circuit Debugger and ICSP programming data pin.       |  |  |  |

| Legend: TTL = TT | <u> </u>       |      |      | 01     | CMOS = CMOS compatible input or output                   |  |  |  |

#### **TABLE 1-2:** PIC18F2480/2580 PINOUT I/O DESCRIPTIONS (CONTINUED)

ST = Schmitt Trigger input with CMOS levels I

Р

= Input

= Power

$\begin{array}{l} O \\ O \\ |^2C \\ |^2C \\ = |^2C^{TM}/SMBus \text{ input buffer} \end{array}$

| IABLE 5-4:      |      |                   |      |      | DITIONS FOR ALL                    |                                                                  |                                 |  |

|-----------------|------|-------------------|------|------|------------------------------------|------------------------------------------------------------------|---------------------------------|--|

| Register Applic |      | pplicable Devices |      |      | Power-on Reset,<br>Brown-out Reset | MCLR Resets,<br>WDT Reset,<br>RESET Instruction,<br>Stack Resets | Wake-up via WDT<br>or Interrupt |  |

| TOSU            | 2480 | 2580              | 4480 | 4580 | 0 0000                             | 0 0000                                                           | 0 uuuu <b>(3)</b>               |  |

| TOSH            | 2480 | 2580              | 4480 | 4580 | 0000 0000                          | 0000 0000                                                        | uuuu uuuu <b>(3)</b>            |  |

| TOSL            | 2480 | 2580              | 4480 | 4580 | 0000 0000                          | 0000 0000                                                        | uuuu uuuu <b>(3)</b>            |  |

| STKPTR          | 2480 | 2580              | 4480 | 4580 | 00-0 0000                          | uu-0 0000                                                        | uu-u uuuu <b>(3)</b>            |  |

| PCLATU          | 2480 | 2580              | 4480 | 4580 | 0 0000                             | 0 0000                                                           | u uuuu                          |  |

| PCLATH          | 2480 | 2580              | 4480 | 4580 | 0000 0000                          | 0000 0000                                                        | սսսս սսսս                       |  |

| PCL             | 2480 | 2580              | 4480 | 4580 | 0000 0000                          | 0000 0000                                                        | PC + 2 <sup>(2)</sup>           |  |

| TBLPTRU         | 2480 | 2580              | 4480 | 4580 | 00 0000                            | 00 0000                                                          | uu uuuu                         |  |

| TBLPTRH         | 2480 | 2580              | 4480 | 4580 | 0000 0000                          | 0000 0000                                                        | սսսս սսսս                       |  |

| TBLPTRL         | 2480 | 2580              | 4480 | 4580 | 0000 0000                          | 0000 0000                                                        | սսսս սսսս                       |  |

| TABLAT          | 2480 | 2580              | 4480 | 4580 | 0000 0000                          | 0000 0000                                                        | սսսս սսսս                       |  |

| PRODH           | 2480 | 2580              | 4480 | 4580 | XXXX XXXX                          | uuuu uuuu                                                        | սսսս սսսս                       |  |

| PRODL           | 2480 | 2580              | 4480 | 4580 | XXXX XXXX                          | นนนน นนนน                                                        | սսսս սսսս                       |  |

| INTCON          | 2480 | 2580              | 4480 | 4580 | 0000 000x                          | 0000 000u                                                        | uuuu uuuu <b>(1)</b>            |  |

| INTCON2         | 2480 | 2580              | 4480 | 4580 | 1111 -1-1                          | 1111 -1-1                                                        | uuuu -u-u <b>(1)</b>            |  |

| INTCON3         | 2480 | 2580              | 4480 | 4580 | 11-0 0-00                          | 11-0 0-00                                                        | uu-u u-uu <b>(1)</b>            |  |

| INDF0           | 2480 | 2580              | 4480 | 4580 | N/A                                | N/A                                                              | N/A                             |  |

| POSTINC0        | 2480 | 2580              | 4480 | 4580 | N/A                                | N/A                                                              | N/A                             |  |

| POSTDEC0        | 2480 | 2580              | 4480 | 4580 | N/A                                | N/A                                                              | N/A                             |  |

| PREINC0         | 2480 | 2580              | 4480 | 4580 | N/A                                | N/A                                                              | N/A                             |  |

| PLUSW0          | 2480 | 2580              | 4480 | 4580 | N/A                                | N/A                                                              | N/A                             |  |

| FSR0H           | 2480 | 2580              | 4480 | 4580 | 0000                               | 0000                                                             | uuuu                            |  |

| FSR0L           | 2480 | 2580              | 4480 | 4580 | XXXX XXXX                          | นนนน นนนน                                                        | սսսս սսսս                       |  |

| WREG            | 2480 | 2580              | 4480 | 4580 | XXXX XXXX                          | uuuu uuuu                                                        | սսսս սսսս                       |  |

| INDF1           | 2480 | 2580              | 4480 | 4580 | N/A                                | N/A                                                              | N/A                             |  |

| POSTINC1        | 2480 | 2580              | 4480 | 4580 | N/A                                | N/A                                                              | N/A                             |  |

| POSTDEC1        | 2480 | 2580              | 4480 | 4580 | N/A                                | N/A                                                              | N/A                             |  |

| PREINC1         | 2480 | 2580              | 4480 | 4580 | N/A                                | N/A                                                              | N/A                             |  |

| PLUSW1          | 2480 | 2580              | 4480 | 4580 | N/A                                | N/A                                                              | N/A                             |  |

| FSR1H           | 2480 | 2580              | 4480 | 4580 | 0000                               | 0000                                                             | uuuu                            |  |

| FSR1L           | 2480 | 2580              | 4480 | 4580 | XXXX XXXX                          | นนนน นนนน                                                        | սսսս սսսս                       |  |

#### TABLE 5-4: INITIALIZATION CONDITIONS FOR ALL REGISTERS

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition. Shaded cells indicate conditions do not apply for the designated device.

Note 1: One or more bits in the INTCONx or PIRx registers will be affected (to cause wake-up).

2: When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the PC is loaded with the interrupt vector (0008h or 0018h).

**3:** When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the TOSU, TOSH and TOSL are updated with the current value of the PC. The STKPTR is modified to point to the next location in the hardware stack.

4: See Table 5-3 for Reset value for specific condition.

**5:** Bits 6 and 7 of PORTA, LATA and TRISA are enabled, depending on the oscillator mode selected. When not enabled as PORTA pins, they are disabled and read '0'.

6: This register reads all '0's until ECAN<sup>™</sup> technology is set up in Mode 1 or Mode 2.

### 6.1.2.4 Stack Full and Underflow Resets

Device Resets on stack overflow and stack underflow conditions are enabled by setting the STVREN bit in Configuration Register 4L. When STVREN is set, a full or underflow will set the appropriate STKFUL or STKUNF bit and then cause a device Reset. When STVREN is cleared, a full or underflow condition will set the appropriate STKFUL or STKUNF bit but not cause a device Reset. The STKFUL or STKUNF bits are cleared by the user software or a Power-on Reset.

### 6.1.3 FAST REGISTER STACK

A Fast Register Stack is provided for the STATUS, WREG and BSR registers, to provide a "fast return" option for interrupts. Each stack is only one level deep and is neither readable nor writable. It is loaded with the current value of the corresponding register when the processor vectors for an interrupt. All interrupt sources will push values into the stack registers. The values in the registers are then loaded back into their associated registers, if the RETFIE, FAST instruction is used to return from the interrupt.

If both low and high-priority interrupts are enabled, the stack registers cannot be used reliably to return from low-priority interrupts. If a high-priority interrupt occurs while servicing a low-priority interrupt, the stack register values stored by the low-priority interrupt will be overwritten. In these cases, users must save the key registers in software during a low-priority interrupt.

If interrupt priority is not used, all interrupts may use the Fast Register Stack for returns from interrupt. If no interrupts are used, the Fast Register Stack can be used to restore the STATUS, WREG and BSR registers at the end of a subroutine call. To use the Fast Register Stack for a subroutine call, a CALL label, FAST instruction must be executed to save the STATUS, WREG and BSR registers to the Fast Register Stack. A RETURN, FAST instruction is then executed to restore these registers from the Fast Register Stack.

Example 6-1 shows a source code example that uses the Fast Register Stack during a subroutine call and return.

### EXAMPLE 6-1: FAST REGISTER STACK CODE EXAMPLE

|        |                   | -                                                       |

|--------|-------------------|---------------------------------------------------------|

| CALL   | SUB1, FAST        | ;STATUS, WREG, BSR<br>;SAVED IN FAST REGISTER<br>;STACK |

| 0110-1 | •                 |                                                         |

| SUB1   | •<br>RETURN, FAST | RESTORE VALUES SAVED                                    |

|        |                   | ;IN FAST REGISTER STACK                                 |

### 6.1.4 LOOK-UP TABLES IN PROGRAM MEMORY

There may be programming situations that require the creation of data structures, or look-up tables, in program memory. For PIC18 devices, look-up tables can be implemented in two ways:

- Computed GOTO

- Table Reads

### 6.1.4.1 Computed GOTO

A computed GOTO is accomplished by adding an offset to the program counter. An example is shown in Example 6-2.

A look-up table can be formed with an ADDWF PCL instruction and a group of RETLW nn instructions. The W register is loaded with an offset into the table before executing a call to that table. The first instruction of the called routine is the ADDWF PCL instruction. The next instruction executed will be one of the RETLW nn instructions, that returns the value 'nn' to the calling function.

The offset value (in WREG) specifies the number of bytes that the program counter should advance and should be multiples of 2 (LSb = 0).

In this method, only one data byte may be stored in each instruction location and room on the return address stack is required.

#### EXAMPLE 6-2: COMPUTED GOTO USING AN OFFSET VALUE

|       | MOVF<br>CALL | OFFSET,<br>TABLE | W |

|-------|--------------|------------------|---|

|       | CALL         | IADLL            |   |

| ORG   | nn00h        |                  |   |

| TABLE | ADDWF        | PCL              |   |

|       | RETLW        | nnh              |   |

|       | RETLW        | nnh              |   |

|       | RETLW        | nnh              |   |

|       | •            |                  |   |

|       | •            |                  |   |

|       | •            |                  |   |

|       |              |                  |   |

### 6.1.4.2 Table Reads and Table Writes

A better method of storing data in program memory allows two bytes of data to be stored in each instruction location.

Look-up table data may be stored two bytes per program word by using table reads and writes. The Table Pointer (TBLPTR) register specifies the byte address and the Table Latch (TABLAT) register contains the data that is read from or written to program memory. Data is transferred to or from program memory one byte at a time.

Table read and table write operations are discussed further in Section 7.1 "Table Reads and Table Writes".

| File Name | Bit 7                                                                                                   | Bit 6           | Bit 5                 | Bit 4         | Bit 3           | Bit 2            | Bit 1            | Bit 0          | Value on POR, BOR | Details on<br>Page: |

|-----------|---------------------------------------------------------------------------------------------------------|-----------------|-----------------------|---------------|-----------------|------------------|------------------|----------------|-------------------|---------------------|

| TOSU      | _                                                                                                       | _               |                       | Top-of-Stack  | Upper Byte (To  | DS<20:16>)       |                  |                | 0 0000            | 55, 68              |

| TOSH      | Top-of-Stack High Byte (TOS<15:8>)                                                                      |                 |                       |               |                 |                  |                  |                | 0000 0000         | 55, 68              |

| TOSL      | Top-of-Stack L                                                                                          | ow Byte (TOS    | <7:0>)                |               |                 |                  |                  |                | 0000 0000         | 55, 68              |

| STKPTR    | STKFUL                                                                                                  | STKUNF          | —                     | Return Stack  | Pointer         |                  |                  |                | 00-0 0000         | 55, 69              |

| PCLATU    | _                                                                                                       | —               | bit 21 <sup>(1)</sup> | Holding Regi  | ister for PC<20 | :16>             |                  |                | 0 0000            | 55, 68              |

| PCLATH    | Holding Regist                                                                                          | ter for PC<15:8 | }>                    |               |                 |                  |                  |                | 0000 0000         | 55, 68              |

| PCL       | PC Low Byte (                                                                                           | (PC<7:0>)       |                       |               |                 |                  |                  |                | 0000 0000         | 55, 68              |

| TBLPTRU   | —                                                                                                       | _               | bit 21                | Program Mer   | mory Table Poi  | nter Upper Byte  | (TBLPTR<20:10    | 6>)            | 00 0000           | 55, 109             |

| TBLPTRH   | Program Mem                                                                                             | ory Table Poin  | ter High Byte         | (TBLPTR<15    | :8>)            |                  |                  |                | 0000 0000         | 55, 109             |

| TBLPTRL   | Program Mem                                                                                             | ory Table Poin  | ter Low Byte          | (TBLPTR<7:0   | >)              |                  |                  |                | 0000 0000         | 55, 109             |

| TABLAT    | Program Mem                                                                                             | ory Table Latcl | า                     |               |                 |                  |                  |                | 0000 0000         | 55, 109             |

| PRODH     | Product Regis                                                                                           | ter High Byte   |                       |               |                 |                  |                  |                | XXXX XXXX         | 55, 117             |

| PRODL     | Product Regis                                                                                           | ter Low Byte    |                       |               |                 |                  |                  |                | XXXX XXXX         | 55, 117             |

| INTCON    | GIE/GIEH                                                                                                | PEIE/GIEL       | TMR0IE                | INT0IE        | RBIE            | TMR0IF           | INTOIF           | RBIF           | 0000 000x         | 55, 121             |

| INTCON2   | RBPU                                                                                                    | INTEDG0         | INTEDG1               | INTEDG2       | _               | TMR0IP           | _                | RBIP           | 1111 -1-1         | 55, 122             |

| INTCON3   | INT2IP                                                                                                  | INT1IP          | _                     | INT2IE        | INT1IE          | —                | INT2IF           | INT1IF         | 11-0 0-00         | 55, 123             |

| INDF0     | Uses contents of FSR0 to address data memory – value of FSR0 not changed (not a physical register)      |                 |                       |               |                 |                  |                  | N/A            | 55, 96            |                     |

| POSTINC0  | Uses contents of FSR0 to address data memory – value of FSR0 post-incremented (not a physical register) |                 |                       |               |                 |                  |                  | ster)          | N/A               | 55, 97              |

| POSTDEC0  | Uses contents of FSR0 to address data memory – value of FSR0 post-decremented (not a physical register) |                 |                       |               |                 |                  |                  | ister)         | N/A               | 55, 97              |

| PREINC0   | Uses contents of FSR0 to address data memory – value of FSR0 pre-incremented (not a physical register)  |                 |                       |               |                 |                  |                  | ter)           | N/A               | 55, 97              |

| PLUSW0    | Uses contents<br>FSR0 offset by                                                                         |                 | dress data m          | emory – value | of FSR0 pre-ir  | cremented (not a | a physical regis | ter), value of | N/A               | 55, 97              |

| FSR0H     | -                                                                                                       | -               |                       | —             | Indirect Data I | Memory Address   | Pointer 0 High   |                | xxxx              | 55, 96              |

| FSR0L     | Indirect Data N                                                                                         | Memory Addres   | ss Pointer 0 L        | ow Byte       |                 |                  |                  |                | XXXX XXXX         | 55, 96              |

| WREG      | Working Regis                                                                                           | ster            |                       |               |                 |                  |                  |                | XXXX XXXX         | 55                  |

| INDF1     | Uses contents                                                                                           | of FSR1 to ad   | dress data m          | emory – value | of FSR1 not ch  | nanged (not a ph | ysical register) |                | N/A               | 55, 96              |

| POSTINC1  | Uses contents                                                                                           | of FSR1 to ad   | dress data m          | emory – value | of FSR1 post-i  | ncremented (not  | a physical regi  | ster)          | N/A               | 55, 97              |

| POSTDEC1  | Uses contents                                                                                           | of FSR1 to ad   | dress data m          | emory – value | of FSR1 post-   | decremented (no  | t a physical reg | jister)        | N/A               | 55, 97              |

| PREINC1   | Uses contents                                                                                           | of FSR1 to ad   | dress data m          | emory – value | of FSR1 pre-in  | cremented (not   | a physical regis | ter)           | N/A               | 55, 97              |

| PLUSW1    | Uses contents<br>FSR1 offset by                                                                         |                 | dress data m          | emory – value | of FSR1 pre-ir  | cremented (not a | a physical regis | ter), value of | N/A               | 55, 97              |

| FSR1H     | _                                                                                                       | _               | _                     | _             | Indirect Data I | Memory Address   | Pointer 1 High   |                | xxxx              | 55, 96              |

| FSR1L     | Indirect Data N                                                                                         | Memory Addres   | s Pointer 1 L         | ow Byte       |                 |                  |                  |                | XXXX XXXX         | 55, 96              |

| BSR       | _                                                                                                       | _               | _                     | _             | Bank Select R   | legister         |                  |                | 0000              | 56, 73              |

| INDF2     | Uses contents                                                                                           | of FSR2 to ad   | dress data m          | emory – value | of FSR2 not cl  | nanged (not a ph | ysical register) |                | N/A               | 56, 96              |

| POSTINC2  | Uses contents                                                                                           | of FSR2 to ad   | dress data m          | emory – value | of FSR2 post-i  | ncremented (not  | a physical regi  | ster)          | N/A               | 56, 97              |

| POSTDEC2  | Uses contents                                                                                           | of FSR2 to ad   | dress data m          | emory – value | of FSR2 post-   | decremented (no  | t a physical reg | ister)         | N/A               | 56, 97              |

| PREINC2   | Uses contents                                                                                           | of FSR2 to ad   | dress data m          | emory – value | of FSR2 pre-in  | cremented (not   | a physical regis | ter)           | N/A               | 56, 97              |

| PLUSW2    | Uses contents<br>FSR2 offset by                                                                         |                 | dress data m          | emory – value | of FSR2 pre-ir  | cremented (not a | a physical regis | ter), value of | N/A               | 56, 97              |

**Legend:** x = unknown, u = unchanged, – = unimplemented, q = value depends on condition

Note 1: Bit 21 of the PC is only available in Test mode and Serial Programming modes.

2: The SBOREN bit is only available when CONFIG2L<1:0> = 01; otherwise, it is disabled and reads as '0'. See Section 5.4 "Brown-out Reset (BOR)".

3: These registers and/or bits are not implemented on PIC18F2X80 devices and are read as '0'. Reset values are shown for PIC18F4X80 devices; individual unimplemented bits should be interpreted as '--'.

4: The PLLEN bit is only available in specific oscillator configuration; otherwise, it is disabled and reads as '0'. See Section 3.6.4 "PLL in INTOSC Modes".

5: The RE3 bit is only available when Master Clear Reset is disabled (CONFIG3H<7> = 0); otherwise, RE3 reads as '0'. This bit is read-only.

6: RA6/RA7 and their associated latch and direction bits are individually configured as port pins based on various primary oscillator modes. When disabled, these bits read as '0'.

7: CAN bits have multiple functions depending on the selected mode of the CAN module.

8: This register reads all '0's until the ECAN™ technology is set up in Mode 1 or Mode 2.

9: These registers are available on PIC18F4X80 devices only.

| Mode 0       | R/W-0                                                                                                        | R/W-0                                                                                                                            | R/W-0                                                                                                | R/W-0                                                                | R/W-0                                  | R/W-0                          | R/W-0          | R/W-0      |

|--------------|--------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|----------------------------------------|--------------------------------|----------------|------------|

| Mode U       | IRXIF                                                                                                        | WAKIF                                                                                                                            | ERRIF                                                                                                | TXB2IF                                                               | TXB1IF <sup>(1)</sup>                  | TXB0IF <sup>(1)</sup>          | RXB1IF         | RXB0IF     |

|              | DAVA                                                                                                         | DAMA                                                                                                                             | <b>D</b> 444 0                                                                                       | <b>DAAAA</b>                                                         | <b>D</b> 444 0                         | <b>D</b> /// 0                 | <b>D</b> /// 0 | DAMA       |

| Mode 1,2     | R/W-0                                                                                                        | R/W-0                                                                                                                            | R/W-0                                                                                                | R/W-0                                                                | R/W-0<br>TXB1IF <sup>(1)</sup>         | R/W-0<br>TXB0IF <sup>(1)</sup> | R/W-0          | R/W-0      |

|              | IRXIF<br>bit 7                                                                                               | WAKIF                                                                                                                            | ERRIF                                                                                                | TXBnlF                                                               | 1XB1IF(7)                              | I XBUIF(1)                     | RXBnlF         | bit        |

|              | Dit 1                                                                                                        |                                                                                                                                  |                                                                                                      |                                                                      |                                        |                                |                | Dit        |

| Legend:      |                                                                                                              |                                                                                                                                  |                                                                                                      |                                                                      |                                        |                                |                |            |

| R = Readal   | ole bit                                                                                                      |                                                                                                                                  | W = Writabl                                                                                          | e bit                                                                | U = Unimple                            | emented bit, r                 | ead as '0'     |            |

| -n = Value a | at POR                                                                                                       |                                                                                                                                  | '1' = Bit is s                                                                                       | et                                                                   | ʻ0' = Bit is cl                        | eared                          | x = Bit is ur  | nknown     |

| bit 7        | 1 = An inval                                                                                                 | Invalid Rece<br>lid message h<br>lid message c                                                                                   | nas occurred                                                                                         |                                                                      | -                                      |                                |                |            |

| bit 6        | 1 = Activity                                                                                                 | N bus Activity<br>on CAN bus I<br>vity on CAN b                                                                                  | has occurred                                                                                         | terrupt Flag                                                         | bit                                    |                                |                |            |

| bit 5        | 1 = An error                                                                                                 | N bus Error Ir<br>r has occurre<br>I module erro                                                                                 | d in the CAN                                                                                         |                                                                      | ltiple sources)                        | )                              |                |            |

| bit 4        | <b>TXB2IF:</b> CA1 = Transm0 = TransmWhen CAN                                                                |                                                                                                                                  | s completed <sup>-</sup><br>s not comple<br>or 2:                                                    | transmission<br>ted transmis                                         | n of a messag<br>ssion of a mes        |                                | reloaded       |            |

| bit 3        | 1 = One or<br>0 = No tran                                                                                    |                                                                                                                                  | it buffers hav<br>ready for relo                                                                     | e completed                                                          | I transmission                         | of a message                   | e and may b    | e reloaded |

| bit 5        | 1 = Transmi                                                                                                  | it Buffer 1 has                                                                                                                  | s completed t                                                                                        | ransmission                                                          | of a message<br>sion of a mess         |                                | reloaded       |            |

| bit 2        | 1 = Transmi                                                                                                  |                                                                                                                                  | s completed t                                                                                        | ransmission                                                          | 1)<br>I of a message<br>sion of a mess |                                | reloaded       |            |

| bit 1        | When CAN<br><b>RXB1IF:</b> CA<br>1 = Receive<br>0 = Receive<br>When CAN<br><b>RXBnIF:</b> An<br>1 = One or a | is in Mode 0:<br>AN Receive B<br>Buffer 1 has<br>Buffer 1 has<br>is in Mode 1<br>Ny Receive Bu<br>more receive<br>ive buffer has | uffer 1 Interru<br>received a n<br>not received<br>o <u>r 2:</u><br>uffer Interrupt<br>buffers has r | upt Flag bit<br>ew message<br>a new mess<br>Flag bit<br>eceived a ne | e<br>sage<br>ew message                |                                |                |            |

| bit 0        | RXB0IF: CA<br>1 = Receive<br>0 = Receive<br>When CAN                                                         | is in Mode 0:<br>AN Receive B<br>Buffer 0 has<br>Buffer 0 has<br>is in Mode 1:<br>ented: Read a                                  | received a n<br>not received                                                                         | ew message                                                           |                                        |                                |                |            |

### REGISTER 10-6: PIR3: PERIPHERAL INTERRUPT REQUEST (FLAG) REGISTER 3

Note 1: In CAN Mode 1 and 2, these bits are forced to '0'.

| Pin Name           | Function            | I/O | TRIS | Buffer | Description                                                                                                      |

|--------------------|---------------------|-----|------|--------|------------------------------------------------------------------------------------------------------------------|

| RB0/INT0/FLT0/AN10 | RB0                 | OUT | 0    | DIG    | LATB<0> data output.                                                                                             |

|                    |                     | IN  | 1    | TTL    | PORTB<0> data input. Weak pull-up available only in this mode.                                                   |

|                    | INT0                | IN  | 1    | ST     | External Interrupt 0 input.                                                                                      |

|                    | FLT0 <sup>(1)</sup> | IN  | 1    | ST     | Enhanced PWM Fault input.                                                                                        |

|                    | AN10                | IN  | 1    | ANA    | A/D Input Channel 10. Enabled on POR, this analog input overrides the digital input (read as clear – low level). |

| RB1/INT1/AN8       | RB1                 | OUT | 0    | DIG    | LATB<1> data output.                                                                                             |

|                    |                     | IN  | 1    | TTL    | PORTB<1> data input. Weak pull-up available only in this mode.                                                   |

|                    | INT1                | IN  | 1    | ST     | External Interrupt 1 input.                                                                                      |

|                    | AN8                 | IN  | 1    | ANA    | A/D Input Channel 8. Enabled on POR; this analog input overrides the digital input (read as clear – low level).  |

| RB2/INT2/CANTX     | RB2                 | OUT | х    | DIG    | LATB<2> data output.                                                                                             |

|                    |                     | IN  | 1    | TTL    | PORTB<2> data input. Weak pull-up available only in this mode.                                                   |

|                    | INT2                | IN  | 1    | ST     | External Interrupt 2 input.                                                                                      |

|                    | CANTX               | OUT | 1    | DIG    | CAN transmit signal output. The CAN interface overrides the TRIS<2> control when enabled.                        |

| RB3/CANRX          | RB3                 | OUT | 0    | DIG    | LATB<3> data output.                                                                                             |

|                    |                     | IN  | 1    | TTL    | PORTB<3> data input. Weak pull-up available only in this mode.                                                   |

|                    | CANRX               | IN  | 1    | ST     | CAN receive signal input. Pin must be configured as a digital input b setting TRISB<3>.                          |

| RB4/KBI0/AN9       | RB4                 | OUT | 0    | DIG    | LATB<4> data output.                                                                                             |

|                    |                     | IN  | 1    | TTL    | PORTB<4> data input. Weak pull-up available only in this mode.                                                   |

|                    | KBI0                | IN  | 1    | TTL    | Interrupt-on-pin change.                                                                                         |

|                    | AN9                 | IN  | 1    | ANA    | A/D Input Channel 9. Enabled on POR; this analog input overrides the digital input (read as clear – low level).  |

| RB5/KBI1/PGM       | RB5                 | OUT | 0    | DIG    | LATB<5> data output.                                                                                             |

|                    |                     | IN  | 1    | TTL    | PORTB<5> data input. Weak pull-up available only in this mode.                                                   |

|                    | KBI1                | IN  | 1    | TTL    | Interrupt-on-pin change.                                                                                         |

|                    | PGM                 | IN  | х    | ST     | Low-Voltage Programming mode entry (ICSP™). Enabling this function overrides digital output.                     |

| RB6/KBI2/PGC       | RB6                 | OUT | 0    | DIG    | LATB<6> data output.                                                                                             |

|                    |                     | IN  | 1    | TTL    | PORTB<6> data input. Weak pull-up available only in this mode.                                                   |

|                    | KBI2                | IN  | 1    | TTL    | Interrupt-on-pin change.                                                                                         |

|                    | PGC                 | IN  | Х    | ST     | Low-Voltage Programming mode entry (ICSP) clock input.                                                           |

| RB7/KBI3/PGD       | RB7                 | OUT | 0    | DIG    | LATB<7> data output.                                                                                             |

|                    |                     | IN  | 1    | TTL    | PORTB<7> data input. Weak pull-up available only in this mode.                                                   |

|                    | KBI3                | IN  | 1    | TTL    | Interrupt-on-pin change.                                                                                         |

|                    | PGD                 | OUT | х    | DIG    | Low-Voltage Programming mode entry (ICSP) clock output.                                                          |

|                    |                     | IN  | х    | ST     | Low-Voltage Programming mode entry (ICSP) clock input.                                                           |

TABLE 11-3: PORTB I/O SUMMARY

Legend: OUT = Output, IN = Input, ANA = Analog Signal, DIG = Digital Output, ST = Schmitt Buffer Input, TTL = TTL Buffer Input Note 1: Available on 40/44-pin devices only.

### 18.4.3.2 Reception

When the R/W bit of the address byte is clear and an address match occurs, the R/W bit of the SSPSTAT register is cleared. The received address is loaded into the SSPBUF register and the SDA line is held low (ACK).

When the address byte overflow condition exists, then the no Acknowledge (ACK) pulse is given. An overflow condition is defined as either bit, BF (SSPSTAT<0>), is set, or bit, SSPOV (SSPCON1<6>), is set.

An MSSP interrupt is generated for each data transfer byte. Flag bit, SSPIF (PIR1<3>), must be cleared in software. The SSPSTAT register is used to determine the status of the byte.

If SEN is enabled (SSPCON2<0> = 1), RC3/SCK/SCL will be held low (clock stretch) following each data transfer. The clock must be released by setting bit, CKP (SSPCON<4>). See **Section 18.4.4** "Clock **Stretching**" for more details.

### 18.4.3.3 Transmission

When the R/W bit of the incoming address byte is set and an address match occurs, the R/W bit of the SSPSTAT register is set. The received address is loaded into the SSPBUF register. The ACK pulse will be sent on the ninth bit and pin RC3/SCK/SCL is held low regardless of SEN (see Section 18.4.4 "Clock Stretching" for more details). By stretching the clock, the master will be unable to assert another clock pulse until the slave is done preparing the transmit data. The transmit data must be loaded into the SSPBUF register which also loads the SSPSR register. Then, the RC3/ SCK/SCL pin should be enabled by setting bit, CKP (SSPCON1<4>). The eight data bits are shifted out on the falling edge of the SCL input. This ensures that the SDA signal is valid during the SCL high time (Figure 18-9).

The ACK pulse from the master-receiver is latched on the rising edge of the ninth SCL input pulse. If the SDA line is high (not ACK), then the data transfer is complete. In this case, when the ACK is latched by the slave, the slave logic is reset and the slave monitors for another occurrence of the Start bit. If the SDA line was low (ACK), the next transmit data must be loaded into the SSPBUF register. Again, pin, RC3/SCK/SCL, must be enabled by setting bit, CKP.

An MSSP interrupt is generated for each data transfer byte. The SSPIF bit must be cleared in software and the SSPSTAT register is used to determine the status of the byte. The SSPIF bit is set on the falling edge of the ninth clock pulse.

### REGISTER 24-9: TXBnEIDL: TRANSMIT BUFFER n EXTENDED IDENTIFIER REGISTERS, LOW BYTE $[0 \le n \le 2]$

|         | -     | •     | •     |       |       |       |       |

|---------|-------|-------|-------|-------|-------|-------|-------|

| R/W-x   | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x |

| EID7    | EID6  | EID5  | EID4  | EID3  | EID2  | EID1  | EID0  |

| bit 7   |       |       |       |       |       |       | bit 0 |

|         |       |       |       |       |       |       |       |

| Legend: |       |       |       |       |       |       |       |

|         |       |       |       |       |       |       |       |

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

|-------------------|------------------|------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 7-0 **EID<7:0>:** Extended Identifier bits (not used when transmitting standard identifier message)

### REGISTER 24-10: TXBnDm: TRANSMIT BUFFER n DATA FIELD BYTE m REGISTERS [0 $\leq$ n $\leq$ 2, 0 $\leq$ m $\leq$ 7]

| R/W-x   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| TXBnDm7 | TXBnDm6 | TXBnDm5 | TXBnDm4 | TXBnDm3 | TXBnDm2 | TXBnDm1 | TXBnDm0 |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

### bit 7-0 **TXBnDm<7:0>:** Transmit Buffer n Data Field Byte m bits (where 0 ≤ n < 3 and 0 ≤ m < 8) Each transmit buffer has an array of registers. For example, Transmit Buffer 0 has 7 registers: TXB0D0 to TXB0D7.

| R/W-0              | R/W-0                                                                                                              | R/W-0                                      | R/W-0        | R/W-0            | R/W-0            | R/W-0           | R/W-0  |

|--------------------|--------------------------------------------------------------------------------------------------------------------|--------------------------------------------|--------------|------------------|------------------|-----------------|--------|

| FIL11_1            | FIL11_0                                                                                                            | FIL10_1                                    | FIL10_0      | FIL9_1           | FIL9_0           | FIL8_1          | FIL8_0 |

| bit 7              |                                                                                                                    |                                            |              |                  |                  |                 | bit 0  |

| Legend:            |                                                                                                                    |                                            |              |                  |                  |                 |        |

| R = Readabl        | e bit                                                                                                              | W = Writable                               | bit          | U = Unimpler     | mented bit, read | d as '0'        |        |

| -n = Value at      | POR                                                                                                                | '1' = Bit is set                           |              | '0' = Bit is cle | eared            | x = Bit is unkr | iown   |

| bit 7-6<br>bit 5-4 | 11 = No mask<br>10 = Filter 15<br>01 = Acceptar<br>00 = Acceptar<br>FIL10_<1:0>:<br>11 = No mask<br>10 = Filter 15 | nce Mask 1<br>nce Mask 0<br>Filter 10 Sele |              |                  |                  |                 |        |

| bit 3-2            | 01 = Acceptar<br>00 = Acceptar<br>FIL9_<1:0>: F<br>11 = No mask<br>10 = Filter 15<br>01 = Acceptar                 | nce Mask 0<br>Filter 9 Select  <br><       | oits 1 and 0 |                  |                  |                 |        |

| bit 1-0            | 00 = Acceptar<br>FIL8_<1:0>: F<br>11 = No mask<br>10 = Filter 15<br>01 = Acceptar<br>00 = Acceptar                 | Filter 8 Select  <br><<br>nce Mask 1       | bits 1 and 0 |                  |                  |                 |        |

### REGISTER 24-50: MSEL2: MASK SELECT REGISTER 2<sup>(1)</sup>

**Note 1:** This register is available in Mode 1 and 2 only.

### REGISTER 24-59: TXBIE: TRANSMIT BUFFERS INTERRUPT ENABLE REGISTER<sup>(1)</sup>

| U-0   | U-0 | U-0 | R/W-0                 | R/W-0                 | R/W-0                 | U-0 | U-0   |

|-------|-----|-----|-----------------------|-----------------------|-----------------------|-----|-------|

| —     | —   |     | TXB2IE <sup>(2)</sup> | TXB1IE <sup>(2)</sup> | TXB0IE <sup>(2)</sup> | _   | —     |

| bit 7 |     |     |                       |                       |                       |     | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | l as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 7-5 | Unimplemented: Read as '0'                                              |

|---------|-------------------------------------------------------------------------|

| bit 4-2 | TXB2IE:TXB0IE: Transmit Buffer 2-0 Interrupt Enable bits <sup>(2)</sup> |

|         | 1 = Transmit buffer interrupt is enabled                                |

|         | 0 = Transmit buffer interrupt is disabled                               |

| bit 1-0 | Unimplemented: Read as '0'                                              |

Note 1: This register is available in Mode 1 and 2 only.

2: TXBnIE in PIE3 register must be set to get an interrupt.

### REGISTER 24-60: BIE0: BUFFER INTERRUPT ENABLE REGISTER 0<sup>(1)</sup>

| R/W-0                 | R/W-0                 |

|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|-----------------------|-----------------------|

| B5IE <sup>(2)</sup> | B4IE <sup>(2)</sup> | B3IE <sup>(2)</sup> | B2IE <sup>(2)</sup> | B1IE <sup>(2)</sup> | B0IE <sup>(2)</sup> | RXB1IE <sup>(2)</sup> | RXB0IE <sup>(2)</sup> |

| bit 7               |                     |                     |                     |                     |                     |                       | bit 0                 |

| Legend:                           |                  |                        |                    |

|-----------------------------------|------------------|------------------------|--------------------|

| R = Readable bit                  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| n = Value at POR (1' = Bit is set |                  | '0' = Bit is cleared   | x = Bit is unknown |

bit 7-2 B5IE:B0IE: Programmable Transmit/Receive Buffer 5-0 Interrupt Enable bits<sup>(2)</sup> 1 = Interrupt is enabled 0 = Interrupt is disabled bit 1-0 RXB1IE:RXB0IE: Dedicated Receive Buffer 1-0 Interrupt Enable bits<sup>(2)</sup> 1 = Interrupt is enabled

0 = Interrupt is disabled

Note 1: This register is available in Mode 1 and 2 only.

2: Either TXBnIE or RXBnIE in the PIE3 register must be set to get an interrupt.

### TABLE 24-1: CAN CONTROLLER REGISTER MAP

| Address <sup>(1)</sup> | Name                    | Address | Name                       | Address | Name                       | Address | Name     |

|------------------------|-------------------------|---------|----------------------------|---------|----------------------------|---------|----------|

| F7Fh                   | SPBRGH <sup>(3)</sup>   | F5Fh    | CANCON_RO0                 | F3Fh    | CANCON_RO2                 | F1Fh    | RXM1EIDL |

| F7Eh                   | BAUDCON <sup>(3)</sup>  | F5Eh    | CANSTAT_RO0                | F3Eh    | CANSTAT_RO2                | F1Eh    | RXM1EIDH |

| F7Dh                   | (4)                     | F5Dh    | RXB1D7                     | F3Dh    | TXB1D7                     | F1Dh    | RXM1SIDL |

| F7Ch                   | (4)                     | F5Ch    | RXB1D6                     | F3Ch    | TXB1D6                     | F1Ch    | RXM1SIDH |

| F7Bh                   | (4)                     | F5Bh    | RXB1D5                     | F3Bh    | TXB1D5                     | F1Bh    | RXM0EIDL |

| F7Ah                   | (4)                     | F5Ah    | RXB1D4                     | F3Ah    | TXB1D4                     | F1Ah    | RXM0EIDH |

| F79h                   | ECCP1DEL <sup>(3)</sup> | F59h    | RXB1D3                     | F39h    | TXB1D3                     | F19h    | RXM0SIDL |

| F78h                   | (4)                     | F58h    | RXB1D2                     | F38h    | TXB1D2                     | F18h    | RXM0SIDH |

| F77h                   | ECANCON                 | F57h    | RXB1D1                     | F37h    | TXB1D1                     | F17h    | RXF5EIDL |

| F76h                   | TXERRCNT                | F56h    | RXB1D0                     | F36h    | TXB1D0                     | F16h    | RXF5EIDH |

| F75h                   | RXERRCNT                | F55h    | RXB1DLC                    | F35h    | TXB1DLC                    | F15h    | RXF5SIDL |

| F74h                   | COMSTAT                 | F54h    | RXB1EIDL                   | F34h    | TXB1EIDL                   | F14h    | RXF5SIDH |

| F73h                   | CIOCON                  | F53h    | RXB1EIDH                   | F33h    | TXB1EIDH                   | F13h    | RXF4EIDL |

| F72h                   | BRGCON3                 | F52h    | RXB1SIDL                   | F32h    | TXB1SIDL                   | F12h    | RXF4EIDH |

| F71h                   | BRGCON2                 | F51h    | RXB1SIDH                   | F31h    | TXB1SIDH                   | F11h    | RXF4SIDL |

| F70h                   | BRGCON1                 | F50h    | RXB1CON                    | F30h    | TXB1CON                    | F10h    | RXF4SIDH |

| F6Fh                   | CANCON                  | F4Fh    | CANCON_RO1 <sup>(2)</sup>  | F2Fh    | CANCON_RO3 <sup>(2)</sup>  | F0Fh    | RXF3EIDL |

| F6Eh                   | CANSTAT                 | F4Eh    | CANSTAT_RO1 <sup>(2)</sup> | F2Eh    | CANSTAT_RO3 <sup>(2)</sup> | F0Eh    | RXF3EIDH |

| F6Dh                   | RXB0D7                  | F4Dh    | TXB0D7                     | F2Dh    | TXB2D7                     | F0Dh    | RXF3SIDL |

| F6Ch                   | RXB0D6                  | F4Ch    | TXB0D6                     | F2Ch    | TXB2D6                     | F0Ch    | RXF3SIDH |

| F6Bh                   | RXB0D5                  | F4Bh    | TXB0D5                     | F2Bh    | TXB2D5                     | F0Bh    | RXF2EIDL |

| F6Ah                   | RXB0D4                  | F4Ah    | TXB0D4                     | F2Ah    | TXB2D4                     | F0Ah    | RXF2EIDH |

| F69h                   | RXB0D3                  | F49h    | TXB0D3                     | F29h    | TXB2D3                     | F09h    | RXF2SIDL |

| F68h                   | RXB0D2                  | F48h    | TXB0D2                     | F28h    | TXB2D2                     | F08h    | RXF2SIDH |

| F67h                   | RXB0D1                  | F47h    | TXB0D1                     | F27h    | TXB2D1                     | F07h    | RXF1EIDL |

| F66h                   | RXB0D0                  | F46h    | TXB0D0                     | F26h    | TXB2D0                     | F06h    | RXF1EIDH |

| F65h                   | RXB0DLC                 | F45h    | TXB0DLC                    | F25h    | TXB2DLC                    | F05h    | RXF1SIDL |

| F64h                   | RXB0EIDL                | F44h    | TXB0EIDL                   | F24h    | TXB2EIDL                   | F04h    | RXF1SIDH |

| F63h                   | RXB0EIDH                | F43h    | TXB0EIDH                   | F23h    | TXB2EIDH                   | F03h    | RXF0EIDL |

| F62h                   | RXB0SIDL                | F42h    | TXB0SIDL                   | F22h    | TXB2SIDL                   | F02h    | RXF0EIDH |

| F61h                   | RXB0SIDH                | F41h    | TXB0SIDH                   | F21h    | TXB2SIDH                   | F01h    | RXF0SIDL |

| F60h                   | RXB0CON                 | F40h    | TXB0CON                    | F20h    | TXB2CON                    | F00h    | RXF0SIDH |

**Note 1:** Shaded registers are available in Access Bank low area, while the rest are available in Bank 15.

2: CANSTAT register is repeated in these locations to simplify application firmware. Unique names are given for each instance of the controller register due to the Microchip header file requirement.

**3:** These registers are not CAN registers.

**4:** Unimplemented registers are read as '0'.

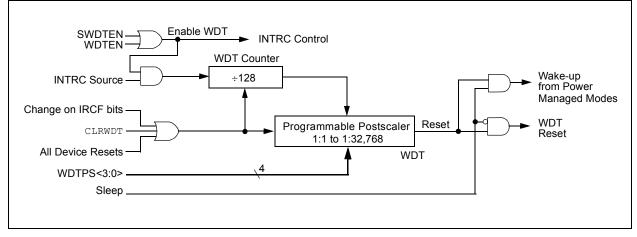

### 25.2 Watchdog Timer (WDT)

For PIC18F2480/2580/4480/4580 devices, the WDT is driven by the INTRC source. When the WDT is enabled, the clock source is also enabled. The nominal WDT period is 4 ms and has the same stability as the INTRC oscillator.

The 4 ms period of the WDT is multiplied by a 16-bit postscaler. Any output of the WDT postscaler is selected by a multiplexer, controlled by bits in Configuration Register 2H. Available periods range from 4 ms to 131.072 seconds (2.18 minutes). The WDT and postscaler are cleared when any of the following events occur: a SLEEP or CLRWDT instruction is executed, the IRCF bits (OSCCON<6:4>) are changed or a clock failure has occurred.

- Note 1: The CLRWDT and SLEEP instructions clear the WDT and postscaler counts when executed.

- 2: Changing the setting of the IRCF bits (OSCCON<6:4>) clears the WDT and postscaler counts.

- **3:** When a CLRWDT instruction is executed, the postscaler count will be cleared.

### 25.2.1 CONTROL REGISTER

Register 25-14 shows the WDTCON register. This is a readable and writable register which contains a control bit that allows software to override the WDT enable Configuration bit, but only if the Configuration bit has disabled the WDT.

#### FIGURE 25-1: WDT BLOCK DIAGRAM

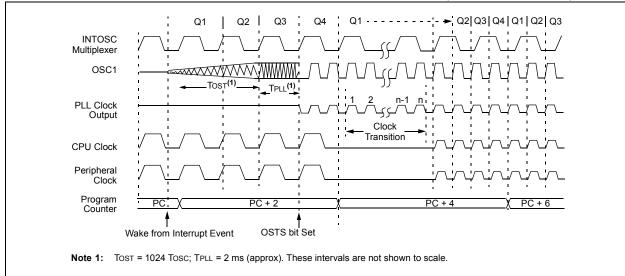

### 25.3 Two-Speed Start-up

The Two-Speed Start-up feature helps to minimize the latency period from oscillator start-up to code execution by allowing the microcontroller to use the INTRC oscillator as a clock source until the primary clock source is available. It is enabled by setting the IESO Configuration bit.

Two-Speed Start-up should be enabled only if the primary oscillator mode is LP, XT, HS or HSPLL (Crystal-Based modes). Other sources do not require an Oscillator Start-up Timer delay; for these, Two-Speed Start-up should be disabled.

When enabled, Resets and wake-ups from Sleep mode cause the device to configure itself to run from the internal oscillator block as the clock source, following the time-out of the Power-up Timer after a Power-on Reset is enabled. This allows almost immediate code execution while the primary oscillator starts and the OST is running. Once the OST times out, the device automatically switches to PRI\_RUN mode.

Because the OSCCON register is cleared on Reset events, the INTOSC (or postscaler) clock source is not initially available after a Reset event; the INTRC clock is used directly at its base frequency. To use a higher clock speed on wake-up, the INTOSC or postscaler clock sources can be selected to provide a higher clock speed by setting bits, IRCF<2:0>, immediately after Reset. For wake-ups from Sleep, the INTOSC or postscaler clock sources can be selected by setting the IRCF2:IRCF0 bits prior to entering Sleep mode.

In all other power-managed modes, Two-Speed Start-up is not used. The device will be clocked by the currently selected clock source until the primary clock source becomes available. The setting of the IESO bit is ignored.

#### 25.3.1 SPECIAL CONSIDERATIONS FOR USING TWO-SPEED START-UP

While using the INTRC oscillator in Two-Speed Start-up, the device still obeys the normal command sequences for entering power-managed modes, including serial SLEEP instructions (refer to **Section 4.1.4 "Multiple Sleep Commands"**). In practice, this means that user code can change the SCS<1:0> bit settings or issue SLEEP instructions before the OST times out. This would allow an application to briefly wake-up, perform routine "housekeeping" tasks and return to Sleep before the device starts to operate from the primary oscillator.

User code can also check if the primary clock source is currently providing the device clocking by checking the status of the OSTS bit (OSCCON<3>). If the bit is set, the primary oscillator is providing the clock. Otherwise, the internal oscillator block is providing the clock during wake-up from Reset or Sleep mode.

### FIGURE 25-2: TIMING TRANSITION FOR TWO-SPEED START-UP (INTOSC TO HSPLL)

| SLEEP               | Enter Sle                                                                                                                               | eep mode                             |              | SUBFWB                                                    | Subtract                                                                                                                                                                                 | f from W w                                          | ith Borrow                         |  |

|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|--------------|-----------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|------------------------------------|--|

| Syntax:             | SLEEP                                                                                                                                   |                                      |              | Syntax:                                                   | SUBFWB                                                                                                                                                                                   | f {,d {,a}}                                         |                                    |  |

| Operands:           | None                                                                                                                                    |                                      |              | Operands:                                                 | $0 \le f \le 255$                                                                                                                                                                        | 5                                                   |                                    |  |

| Operation:          | $00h \rightarrow WE$                                                                                                                    |                                      |              |                                                           | d ∈ [0,1]<br>a ∈ [0,1]                                                                                                                                                                   |                                                     |                                    |  |

|                     | $0 \rightarrow WDT$<br>$1 \rightarrow TO$ ,                                                                                             | postscaler,                          |              | Operation                                                 |                                                                                                                                                                                          | $(\overline{C}) \rightarrow \text{dest}$            |                                    |  |

|                     | $1 \rightarrow 10, \\ 0 \rightarrow PD$                                                                                                 |                                      |              | Operation:<br>Status Affected:                            |                                                                                                                                                                                          |                                                     |                                    |  |

| Status Affected:    | TO, PD                                                                                                                                  |                                      |              |                                                           | N, OV, C,                                                                                                                                                                                |                                                     |                                    |  |

| Encoding:           | 0000                                                                                                                                    | 0000 000                             | 0 0011       | Encoding:                                                 | 0101                                                                                                                                                                                     | 01da ff                                             |                                    |  |

| Description:        | The Power-Down Status bit (PD) is<br>cleared. The Time-out Status bit (TO)<br>is set. Watchdog Timer and its<br>postscaler are cleared. |                                      | Description: | (borrow) fi<br>method). I<br>in W. If 'd'<br>register 'f' | Subtract register 'f' and Carry flag<br>(borrow) from W (2's complement<br>method). If 'd' is '0', the result is stored<br>in W. If 'd' is '1', the result is stored in<br>register 'f'. |                                                     |                                    |  |

|                     | with the os                                                                                                                             | ssor is put into<br>scillator stoppe |              |                                                           |                                                                                                                                                                                          | the BSR is use                                      | nk is selected.<br>d to select the |  |

| Words:              | 1                                                                                                                                       |                                      |              |                                                           |                                                                                                                                                                                          | <br>and the extenc                                  | led instruction                    |  |