Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 40MHz                                                                      |

| Connectivity               | CANbus, I <sup>2</sup> C, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                |

| Number of I/O              | 25                                                                         |

| Program Memory Size        | 16KB (8K x 16)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 768 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                  |

| Data Converters            | A/D 8x10b                                                                  |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-VQFN Exposed Pad                                                        |

| Supplier Device Package    | 28-QFN (6x6)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf2480-i-ml |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

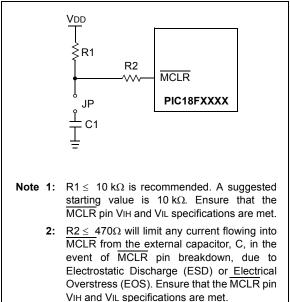

# 2.3 Master Clear (MCLR) Pin

The MCLR pin provides two specific device functions: Device Reset, and Device Programming and Debugging. If programming and debugging are not required in the end application, a direct connection to VDD may be all that is required. The addition of other components, to help increase the application's resistance to spurious Resets from voltage sags, may be beneficial. A typical configuration is shown in Figure 2-1. Other circuit designs may be implemented, depending on the application's requirements.

During programming and debugging, the resistance and capacitance that can be added to the pin must be considered. Device programmers and debuggers drive the MCLR pin. Consequently, specific voltage levels (VIH and VIL) and fast signal transitions must not be adversely affected. Therefore, specific values of R1 and C1 will need to be adjusted based on the application and PCB requirements. For example, it is recommended that the capacitor, C1, be isolated from the MCLR pin during programming and debugging operations by using a jumper (Figure 2-2). The jumper is replaced for normal run-time operations.

Any components associated with the  $\overline{\text{MCLR}}$  pin should be placed within 0.25 inch (6 mm) of the pin.

#### FIGURE 2-2: EXAMPLE OF MCLR PIN CONNECTIONS

# 2.4 ICSP Pins

The PGC and PGD pins are used for In-Circuit Serial Programming<sup>TM</sup> (ICSP<sup>TM</sup>) and debugging purposes. It is recommended to keep the trace length between the ICSP connector and the ICSP pins on the device as short as possible. If the ICSP connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of ohms, not to exceed 100 $\Omega$ .

Pull-up resistors, series diodes, and capacitors on the PGC and PGD pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits and pin input voltage high (VIH) and input low (VIL) requirements.

For device emulation, ensure that the "Communication Channel Select" (i.e., PGCx/PGDx pins) programmed into the device matches the physical connections for the ICSP to the Microchip debugger/emulator tool.

For more information on available Microchip development tools connection requirements, refer to **Section 27.0 "Development Support"**.

| IABLE 5-4: |                    |      |                                    |                                                                  | DITIONS FOR ALL |                                 |     |      |      |

|------------|--------------------|------|------------------------------------|------------------------------------------------------------------|-----------------|---------------------------------|-----|------|------|

| Register   | Applicable Devices |      | Power-on Reset,<br>Brown-out Reset | MCLR Resets,<br>WDT Reset,<br>RESET Instruction,<br>Stack Resets |                 | Wake-up via WDT<br>or Interrupt |     |      |      |

| TXB2D6     | 2480               | 2580 | 4480                               | 4580                                                             | XXXX XXXX       | นนนน นนเ                        | ่าน | 0uuu | นนนน |

| TXB2D5     | 2480               | 2580 | 4480                               | 4580                                                             | XXXX XXXX       | นนนน นนเ                        | มน  | Ouuu | นนนน |

| TXB2D4     | 2480               | 2580 | 4480                               | 4580                                                             | XXXX XXXX       | นนนน นนเ                        | มน  | Ouuu | uuuu |

| TXB2D3     | 2480               | 2580 | 4480                               | 4580                                                             | XXXX XXXX       | นนนน นนเ                        | ่าน | Ouuu | uuuu |

| TXB2D2     | 2480               | 2580 | 4480                               | 4580                                                             | XXXX XXXX       | นนนน นนเ                        | ่าน | Ouuu | uuuu |

| TXB2D1     | 2480               | 2580 | 4480                               | 4580                                                             | XXXX XXXX       | นนนน นนเ                        | มน  | Ouuu | uuuu |

| TXB2D0     | 2480               | 2580 | 4480                               | 4580                                                             | XXXX XXXX       | นนนน นนเ                        | มน  | Ouuu | uuuu |

| TXB2DLC    | 2480               | 2580 | 4480                               | 4580                                                             | -x xxxx         | -u uui                          | ่าน | -u   | uuuu |

| TXB2EIDL   | 2480               | 2580 | 4480                               | 4580                                                             | XXXX XXXX       | นนนน นนเ                        | มน  | սսսս | uuuu |

| TXB2EIDH   | 2480               | 2580 | 4480                               | 4580                                                             | XXXX XXXX       | นนนน นนเ                        | ่าน | սսսս | uuuu |

| TXB2SIDL   | 2480               | 2580 | 4480                               | 4580                                                             | XXXX X-XX       | uuuu u-1                        | มน  | -uuu | uuuu |

| TXB2SIDH   | 2480               | 2580 | 4480                               | 4580                                                             | XXX- X-XX       | uuu- u-1                        | มน  | uuu- | u-uu |

| TXB2CON    | 2480               | 2580 | 4480                               | 4580                                                             | 0000 0-00       | 0000 0-0                        | 00  | սսսս | u-uu |

| RXM1EIDL   | 2480               | 2580 | 4480                               | 4580                                                             | XXXX XXXX       | นนนน นนเ                        | มน  | սսսս | uuuu |

| RXM1EIDH   | 2480               | 2580 | 4480                               | 4580                                                             | XXXX XXXX       | นนนน นนเ                        | มน  | uuuu | uuuu |

| RXM1SIDL   | 2480               | 2580 | 4480                               | 4580                                                             | XXX- X-XX       | uuu- u-1                        | มน  | uuu- | u-uu |

| RXM1SIDH   | 2480               | 2580 | 4480                               | 4580                                                             | XXXX XXXX       | นนนน นนเ                        | มน  | սսսս | uuuu |

| RXM0EIDL   | 2480               | 2580 | 4480                               | 4580                                                             | XXXX XXXX       | นนนน นนเ                        | มน  | սսսս | uuuu |

| RXM0EIDH   | 2480               | 2580 | 4480                               | 4580                                                             | XXXX XXXX       | นนนน นนเ                        | มน  | սսսս | uuuu |

| RXM0SIDL   | 2480               | 2580 | 4480                               | 4580                                                             | XXX- X-XX       | uuu- u-1                        | มน  | uuu- | u-uu |

| RXM0SIDH   | 2480               | 2580 | 4480                               | 4580                                                             | XXXX XXXX       | นนนน นนเ                        | มน  | uuuu | uuuu |

| RXF5EIDL   | 2480               | 2580 | 4480                               | 4580                                                             | XXXX XXXX       | นนนน นนเ                        | มน  | սսսս | uuuu |

| RXF5EIDH   | 2480               | 2580 | 4480                               | 4580                                                             | XXXX XXXX       | นนนน นนเ                        | มน  | սսսս | uuuu |

| RXF5SIDL   | 2480               | 2580 | 4480                               | 4580                                                             | XXX- X-XX       | uuu- u-1                        | มน  | uuu- | u-uu |

| RXF5SIDH   | 2480               | 2580 | 4480                               | 4580                                                             | XXXX XXXX       | นนนน นนเ                        | มน  | սսսս | uuuu |

| RXF4EIDL   | 2480               | 2580 | 4480                               | 4580                                                             | XXXX XXXX       | นนนน นนเ                        | มน  | սսսս | uuuu |

| RXF4EIDH   | 2480               | 2580 | 4480                               | 4580                                                             | XXXX XXXX       | นนนน นนเ                        | มน  | սսսս | uuuu |

| RXF4SIDL   | 2480               | 2580 | 4480                               | 4580                                                             | XXX- X-XX       | uuu- u-1                        | มน  | uuu- | u-uu |

| RXF4SIDH   | 2480               | 2580 | 4480                               | 4580                                                             | XXXX XXXX       | นนนน นนเ                        | มน  | սսսս | uuuu |

| RXF3EIDL   | 2480               | 2580 | 4480                               | 4580                                                             | XXXX XXXX       | นนนน นนเ                        | ่าน | սսսս | uuuu |

| RXF3EIDH   | 2480               | 2580 | 4480                               | 4580                                                             | XXXX XXXX       | นนนน นนเ                        | ่าน | սսսս | uuuu |

| TABLE 5-4: | INITIALIZATION CONDITIONS FOR ALL REGISTERS (CONTINUED) |

|------------|---------------------------------------------------------|

|------------|---------------------------------------------------------|

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition. Shaded cells indicate conditions do not apply for the designated device.

Note 1: One or more bits in the INTCONx or PIRx registers will be affected (to cause wake-up).

2: When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the PC is loaded with the interrupt vector (0008h or 0018h).

**3:** When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the TOSU, TOSH and TOSL are updated with the current value of the PC. The STKPTR is modified to point to the next location in the hardware stack.

4: See Table 5-3 for Reset value for specific condition.

**5:** Bits 6 and 7 of PORTA, LATA and TRISA are enabled, depending on the oscillator mode selected. When not enabled as PORTA pins, they are disabled and read '0'.

6: This register reads all '0's until ECAN<sup>™</sup> technology is set up in Mode 1 or Mode 2.

## 8.6 Operation During Code-Protect

Data EEPROM memory has its own code-protect bits in Configuration Words. External read and write operations are disabled if code protection is enabled.

The microcontroller itself can both read and write to the internal data EEPROM, regardless of the state of the code-protect Configuration bit. Refer to Section 25.0 "Special Features of the CPU" for additional information.

# 8.7 Protection Against Spurious Write

There are conditions when the device may not want to write to the data EEPROM memory. To protect against spurious EEPROM writes, various mechanisms have been implemented. On power-up, the WREN bit is cleared. In addition, writes to the EEPROM are blocked during the Power-up Timer period (TPWRT, parameter 33).

The write initiate sequence and the WREN bit together help prevent an accidental write during brown-out, power glitch or software malfunction.

#### 8.8 Using the Data EEPROM

The data EEPROM is a high-endurance, byte addressable array that has been optimized for the storage of frequently changing information (e.g., program variables or other data that are updated often). Frequently changing values will typically be updated more often than specification D124. If this is not the case, an array refresh must be performed. For this reason, variables that change infrequently (such as constants, IDs, calibration, etc.) should be stored in Flash program memory.

A simple data EEPROM refresh routine is shown in Example 8-3.

**Note:** If data EEPROM is only used to store constants and/or data that changes rarely, an array refresh is likely not required. See specification D124.

| EXAMPLE 8-3: DATA EEPROM REFRESH ROUTINE |

|------------------------------------------|

|------------------------------------------|

|      | CLRF   | EEADR         | ; Start at address 0         |

|------|--------|---------------|------------------------------|

|      | BCF    | EECON1, CFGS  | ; Set for memory             |

|      | BCF    | EECON1, EEPGD | ; Set for Data EEPROM        |

|      | BCF    | INTCON, GIE   | ; Disable interrupts         |

|      | BSF    | EECON1, WREN  | ; Enable writes              |

| LOOP |        |               | ; Loop to refresh array      |

|      | BSF    | EECON1, RD    | ; Read current address       |

|      | MOVLW  | 55h           | ;                            |

|      | MOVWF  | EECON2        | ; Write 55h                  |

|      | MOVLW  | 0AAh          | ;                            |

|      | MOVWF  | EECON2        | ; Write OAAh                 |

|      | BSF    | EECON1, WR    | ; Set WR bit to begin write  |

|      | BTFSC  | EECON1, WR    | ; Wait for write to complete |

|      | BRA    | \$-2          |                              |

|      | INCFSZ | EEADR, F      | ; Increment address          |

|      | BRA    | LOOP          | ; Not zero, do it again      |

|      |        |               |                              |

|      | BCF    | EECON1, WREN  | ; Disable writes             |

|      | BSF    | INTCON, GIE   | ; Enable interrupts          |

|      |        |               |                              |

#### 10.2 PIR Registers

The PIR registers contain the individual flag bits for the peripheral interrupts. Due to the number of peripheral interrupt sources, there are two Peripheral Interrupt Request (Flag) registers (PIR1, PIR2).

- **Note 1:** Interrupt flag bits are set when an interrupt condition occurs regardless of the state of its corresponding enable bit or the global interrupt enable bit, GIE (INTCON<7>).

- 2: User software should ensure the appropriate interrupt flag bits are cleared prior to enabling an interrupt and after servicing that interrupt.

#### REGISTER 10-4: PIR1: PERIPHERAL INTERRUPT REQUEST (FLAG) REGISTER 1

| R/W-0                                                                                | R/W-0                                                                                                                                     | R-0                                            | R-0            | R/W-0                    | R/W-0             | R/W-0           | R/W-0  |  |  |  |  |  |

|--------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|----------------|--------------------------|-------------------|-----------------|--------|--|--|--|--|--|

| PSPIF <sup>(1)</sup>                                                                 | ADIF                                                                                                                                      | RCIF                                           | TXIF           | SSPIF                    | CCP1IF            | TMR2IF          | TMR1IF |  |  |  |  |  |

| bit 7                                                                                |                                                                                                                                           |                                                |                |                          |                   |                 | bit 0  |  |  |  |  |  |

|                                                                                      |                                                                                                                                           |                                                |                |                          |                   |                 |        |  |  |  |  |  |

| Legend:                                                                              |                                                                                                                                           |                                                |                |                          |                   | (0)             |        |  |  |  |  |  |

| R = Readable                                                                         | R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'.n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown |                                                |                |                          |                   |                 |        |  |  |  |  |  |

| -n = value at                                                                        | POR                                                                                                                                       | "I" = Bit is set                               |                | $0^{\circ} = Bit is cle$ | eared             | x = Bit is unkr | lown   |  |  |  |  |  |

| bit 7 <b>PSPIF:</b> Parallel Slave Port Read/Write Interrupt Flag bit <sup>(1)</sup> |                                                                                                                                           |                                                |                |                          |                   |                 |        |  |  |  |  |  |

|                                                                                      |                                                                                                                                           | r a write operat<br>or write has oc            |                | place (must b            | e cleared in soft | ware)           |        |  |  |  |  |  |

| bit 6                                                                                | ADIF: A/D Co                                                                                                                              | onverter Interru                               | pt Flag bit    |                          |                   |                 |        |  |  |  |  |  |

|                                                                                      |                                                                                                                                           | onversion com<br>conversion is r               | • •            | be cleared in s          | oftware)          |                 |        |  |  |  |  |  |

| bit 5                                                                                |                                                                                                                                           | RT Receive Inte                                |                |                          |                   |                 |        |  |  |  |  |  |

|                                                                                      |                                                                                                                                           | ART receive bu<br>ART receive bu               |                | is full (cleared         | when RCREG        | is read)        |        |  |  |  |  |  |

| bit 4                                                                                |                                                                                                                                           | RT Transmit Inte                               |                |                          |                   |                 |        |  |  |  |  |  |

|                                                                                      |                                                                                                                                           | ART transmit b<br>ART transmit b               |                | , is empty (clea         | ared when TXRE    | EG is written)  |        |  |  |  |  |  |

| bit 3                                                                                | SSPIF: Maste                                                                                                                              | er Synchronous                                 | Serial Port I  | nterrupt Flag bi         | it                |                 |        |  |  |  |  |  |

|                                                                                      |                                                                                                                                           | mission/recept<br>transmit/recei               |                | te (must be cle          | ared in software  | e)              |        |  |  |  |  |  |

| bit 2                                                                                | CCP1IF: CCF                                                                                                                               | P1 Interrupt Fla                               | g bit          |                          |                   |                 |        |  |  |  |  |  |

|                                                                                      |                                                                                                                                           | <u>e:</u><br>egister capture<br>register captu |                | ust be cleared           | in software)      |                 |        |  |  |  |  |  |

|                                                                                      |                                                                                                                                           |                                                |                |                          | cleared in softw  | are)            |        |  |  |  |  |  |

| <u>PWM mode:</u><br>Unused in this mode.                                             |                                                                                                                                           |                                                |                |                          |                   |                 |        |  |  |  |  |  |

| bit 1                                                                                | TMR2IF: TMF                                                                                                                               | R2 to PR2 Mate                                 | ch Interrupt F | lag bit                  |                   |                 |        |  |  |  |  |  |

|                                                                                      |                                                                                                                                           | PR2 match occ<br>to PR2 match                  |                | be cleared in so         | oftware)          |                 |        |  |  |  |  |  |

| bit 0                                                                                | TMR1IF: TMF                                                                                                                               | R1 Overflow Int                                | errupt Flag b  | it                       |                   |                 |        |  |  |  |  |  |

|                                                                                      |                                                                                                                                           | gister overflowe<br>gister did not ov          |                | leared in softwa         | are)              |                 |        |  |  |  |  |  |

|                                                                                      |                                                                                                                                           |                                                |                |                          |                   |                 |        |  |  |  |  |  |

Note 1: This bit is reserved on PIC18F2X80 devices; always maintain this bit clear.

# 13.0 TIMER1 MODULE

The Timer1 timer/counter module incorporates these features:

- Software-selectable operation as a 16-bit timer or counter

- Readable and writable 8-bit registers (TMR1H and TMR1L)

- Selectable clock source (internal or external) with device clock or Timer1 oscillator internal options

- Interrupt-on-overflow

- Module Reset on CCP Special Event Trigger

- Device clock status flag (T1RUN)

A simplified block diagram of the Timer1 module is shown in Figure 13-1. A block diagram of the module's operation in Read/Write mode is shown in Figure 13-2.

The module incorporates its own low-power oscillator to provide an additional clocking option. The Timer1 oscillator can also be used as a low-power clock source for the microcontroller in power-managed operation.

Timer1 can also be used to provide Real-Time Clock (RTC) functionality to applications with only a minimal addition of external components and code overhead.

Timer1 is controlled through the T1CON Control register (Register 13-1). It also contains the Timer1 Oscillator Enable bit (T1OSCEN). Timer1 can be enabled or disabled by setting or clearing control bit, TMR1ON (T1CON<0>).

| R/W-0     | R-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0  | R/W-0  | R/W-0  |  |

|-----------|-------|---------|---------|---------|--------|--------|--------|--|

| RD16      | T1RUN | T1CKPS1 | T1CKPS0 | T1OSCEN | T1SYNC | TMR1CS | TMR10N |  |

| bit 7 bit |       |         |         |         |        |        |        |  |

#### REGISTER 13-1: T1CON: TIMER1 CONTROL REGISTER

| Legend:         | <b>b</b> :4     | $\lambda = \lambda / \pi + \pi$ | l l – l laimalana arta d bit                                 | read as (0)        |

|-----------------|-----------------|---------------------------------------------------------------------------------|--------------------------------------------------------------|--------------------|

| R = Readable    |                 | W = Writable bit                                                                | U = Unimplemented bit,                                       |                    |

| -n = Value at I | POR             | '1' = Bit is set                                                                | '0' = Bit is cleared                                         | x = Bit is unknown |

| h:+ 7           |                 | -Bit Read/Write Mode Enat                                                       |                                                              |                    |

| bit 7           |                 |                                                                                 |                                                              |                    |

|                 |                 |                                                                                 | mer1 in one 16-bit operation<br>mer1 in two 8-bit operations |                    |

| bit 6           |                 | Timer1 System Clock Status                                                      | •                                                            |                    |

|                 |                 | ce clock is derived from Tim                                                    |                                                              |                    |

|                 |                 | ce clock is derived from and                                                    |                                                              |                    |

| bit 5-4         | T1CKPS          | <1:0>: Timer1 Input Clock F                                                     | Prescale Select bits                                         |                    |

|                 | 11 <b>= 1:8</b> | Prescale value                                                                  |                                                              |                    |

|                 |                 | Prescale value                                                                  |                                                              |                    |

|                 |                 | Prescale value                                                                  |                                                              |                    |

|                 |                 | Prescale value                                                                  |                                                              |                    |

| bit 3           |                 | N: Timer1 Oscillator Enable                                                     | bit                                                          |                    |

|                 |                 | r1 oscillator is enabled                                                        |                                                              |                    |

|                 |                 | er1 oscillator is shut off                                                      | resistor are turned off to elimin                            | ate power drain    |

| bit 2           |                 |                                                                                 | ut Synchronization Select bit                                |                    |

| DIL Z           |                 |                                                                                 | at Synchronization Select bit                                |                    |

|                 |                 | ot synchronize external cloc                                                    | k input                                                      |                    |

|                 |                 | hronize external clock input                                                    |                                                              |                    |

|                 |                 | IR1CS = 0:                                                                      |                                                              |                    |

|                 | This bit is     | ignored. Timer1 uses the in                                                     | nternal clock when TMR1CS =                                  | 0.                 |

| bit 1           | TMR1CS          | : Timer1 Clock Source Sele                                                      | ect bit                                                      |                    |

|                 | 1 = Exte        | rnal clock from pin RC0/T10                                                     | DSO/T13CKI (on the rising edg                                | je)                |

|                 | 0 = Inter       | nal clock (Fosc/4)                                                              |                                                              |                    |

| bit 0           | TMR10N          | I: Timer1 On bit                                                                |                                                              |                    |

|                 |                 | oles Timer1                                                                     |                                                              |                    |

|                 | 0 = Stop        | s Timer1                                                                        |                                                              |                    |

# 16.2 Capture Mode

In Capture mode, the CCPR1H:CCPR1L register pair captures the 16-bit value of the TMR1 or TMR3 registers when an event occurs on the CCP1 pin (RB3 or RC1, depending on device configuration). An event is defined as one of the following:

- · every falling edge

- · every rising edge

- every 4th rising edge

- every 16th rising edge

The event is selected by the mode select bits, CCP1M<3:0> (CCP1CON<3:0>). When a capture is made, the interrupt request flag bit, CCP1IF (PIR2<1>), is set; it must be cleared in software. If another capture occurs before the value in register CCPR1 is read, the old captured value is overwritten by the new captured value.

#### 16.2.1 CCP1/ECCP1 PIN CONFIGURATION

In Capture mode, the appropriate CCP1/ECCP1 pin should be configured as an input by setting the corresponding TRIS direction bit.

# **Note:** If RC2/CCP1 or RD4/PSP4/ECCP1/P1A is configured as an output, a write to the port can cause a capture condition.

#### 16.2.2 TIMER1/TIMER3 MODE SELECTION

The timers that are to be used with the capture feature (Timer1 and/or Timer3) must be running in Timer mode or Synchronized Counter mode. In Asynchronous Counter mode, the capture operation may not work. The timer to be used with each CCP module is selected in the T3CON register (see Section 16.1.1 "CCP Modules and Timer Resources").

#### 16.2.3 SOFTWARE INTERRUPT

When the Capture mode is changed, a false capture interrupt may be generated. The user should keep the CCPxIE interrupt enable bit clear to avoid false interrupts. The interrupt flag bit, CCPxIF, should also be cleared following any such change in operating mode.

#### 16.2.4 CCP PRESCALER

There are four prescaler settings in Capture mode; they are specified as part of the operating mode selected by the mode select bits (CCP1M<3:0>). Whenever the CCP module is turned off or the CCP module is not in Capture mode, the prescaler counter is cleared. This means that any Reset will clear the prescaler counter.

Switching from one capture prescaler to another may generate an interrupt. Also, the prescaler counter will not be cleared; therefore, the first capture may be from a non-zero prescaler. Example 16-1 shows the recommended method for switching between capture prescalers. This example also clears the prescaler counter and will not generate the "false" interrupt.

#### 16.2.5 CAN MESSAGE TIME-STAMP

The CAN capture event occurs when a message is received in any of the receive buffers. When configured, the CAN module provides the trigger to the CCP1 module to cause a capture event. This feature is provided to "time-stamp" the received CAN messages.

This feature is enabled by setting the CANCAP bit of the CAN I/O Control register (CIOCON<4>). The message receive signal from the CAN module then takes the place of the events on RC2/CCP1.

If this feature is selected, then four different capture options for CCP1M<3:0> are available:

- 0100 every time a CAN message is received

- 0101 every time a CAN message is received

- 0110 every 4th time a CAN message is received

- 0111 capture mode, every 16th time a CAN message is received

#### EXAMPLE 16-1: CHANGING BETWEEN CAPTURE PRESCALERS

|           |                |   | Turn CCP module off<br>Load WREG with the |

|-----------|----------------|---|-------------------------------------------|

| PIO V LIW | NEW_0/11 _ 1 0 |   | new prescaler mode                        |

|           |                |   | value and CCP ON                          |

| MOVWE     | CCP1CON        |   | Load CCP1CON with                         |

| 110 1 111 | 0011001        |   | this value                                |

|           |                | ' | chiis varue                               |

The CCPR1H register and a 2-bit internal latch are used to double-buffer the PWM duty cycle. This double-buffering is essential for glitchless PWM operation.

When the CCPR1H and 2-bit latch match TMR2, concatenated with an internal 2-bit Q clock or 2 bits of the TMR2 prescaler, the CCP1 pin is cleared.

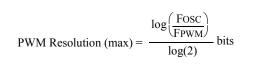

The maximum PWM resolution (bits) for a given PWM frequency is given by the equation.

#### **EQUATION 16-3:**

Note: If the PWM duty cycle value is longer than the PWM period, the CCP1 pin will not be cleared.

### TABLE 16-4: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS AT 40 MHz

| PWM Frequency              | 2.44 kHz | 9.77 kHz | 39.06 kHz | 156.25 kHz | 312.50 kHz | 416.67 kHz |

|----------------------------|----------|----------|-----------|------------|------------|------------|

| Timer Prescaler (1, 4, 16) | 16       | 4        | 1         | 1          | 1          | 1          |

| PR2 Value                  | FFh      | FFh      | FFh       | 3Fh        | 1Fh        | 17h        |

| Maximum Resolution (bits)  | 10       | 10       | 10        | 8          | 7          | 6.58       |

#### 16.4.3 PWM AUTO-SHUTDOWN (ECCP1 ONLY)

The PWM auto-shutdown features of the Enhanced CCP module are available to ECCP1 in PIC18F4480/4580 (40/44-pin) devices. The operation of this feature is discussed in detail in **Section 17.4.7 "Enhanced PWM Auto-Shutdown"**.

Auto-shutdown features are not available for CCP1.

#### 16.4.4 SETUP FOR PWM OPERATION

The following steps should be taken when configuring the CCP module for PWM operation:

- 1. Set the PWM period by writing to the PR2 register.

- Set the PWM duty cycle by writing to the CCPR1L register and CCP1CON<5:4> bits.

- 3. Make the CCP1 pin an output by clearing the appropriate TRIS bit.

- 4. Set the TMR2 prescale value, then enable Timer2 by writing to T2CON.

- 5. Configure the CCP1 module for PWM operation.

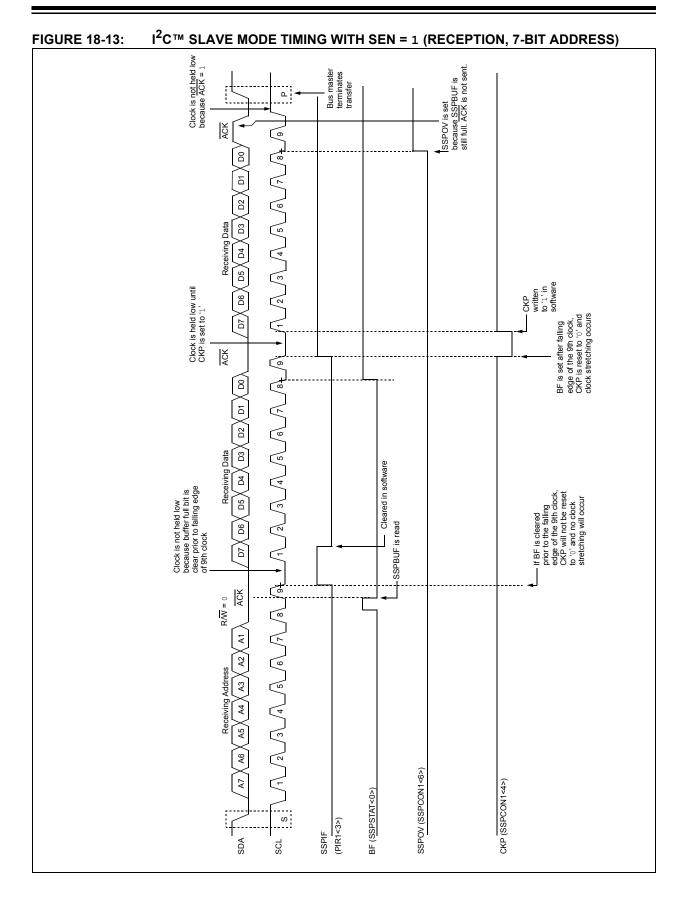

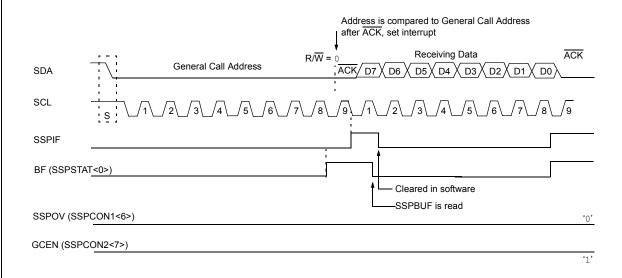

#### 18.4.5 GENERAL CALL ADDRESS SUPPORT

The addressing procedure for the I<sup>2</sup>C bus is such that the first byte after the Start condition usually determines which device will be the slave addressed by the master. The exception is the general call address which can address all devices. When this address is used, all devices should, in theory, respond with an Acknowledge.

The general call address is one of eight addresses reserved for specific purposes by the  $I^2C$  protocol. It consists of all '0's with R/W = 0.

The general call address is recognized when the General Call Enable bit (GCEN) is enabled (SSPCON2<7> set). Following a Start bit detect, 8 bits are shifted into the SSPSR and the address is compared against the SSPADD. It is also compared to the general call address and fixed in hardware.

If the general call address matches, the SSPSR is transferred to the SSPBUF, the BF flag bit is set (eighth bit), and on the falling edge of the ninth bit (ACK bit), the SSPIF interrupt flag bit is set.

When the interrupt is serviced, the source for the interrupt can be checked by reading the contents of the SSPBUF. The value can be used to determine if the address was device-specific or a general call address.

In 10-bit mode, the SSPADD is required to be updated for the second half of the address to match and the UA bit is set (SSPSTAT<1>). If the general call address is sampled when the GCEN bit is set, while the slave is configured in 10-Bit Addressing mode, then the second half of the address is not necessary, the UA bit will not be set and the slave will begin receiving data after the Acknowledge (Figure 18-15).

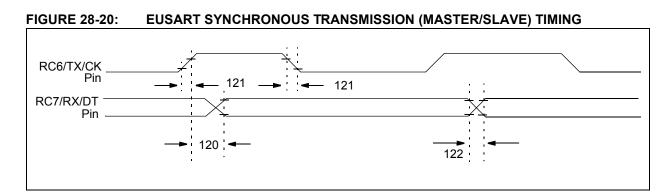

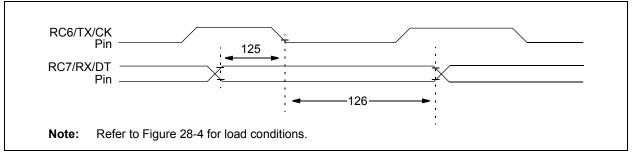

# 19.0 ENHANCED UNIVERSAL SYNCHRONOUS RECEIVER TRANSMITTER (EUSART)

The Universal Synchronous Asynchronous Receiver Transmitter (USART) module is one of the two serial I/O modules. (USART is also known as a Serial Communications Interface or SCI.) The USART can be configured as a full-duplex asynchronous system that can communicate with peripheral devices, such as CRT terminals and personal computers. It can also be configured as a half-duplex synchronous system that can communicate with peripheral devices, such as A/D or D/A integrated circuits, serial EEPROMs and so on.

The EUSART module implements additional features, including automatic baud rate detection and calibration, automatic wake-up on Sync Break reception and 12-bit Break character transmit. These make it ideally suited for use in Local Interconnect Network bus (LIN/J2602 bus) systems.

The EUSART can be configured in the following modes:

- Asynchronous (full-duplex) with:

- Auto-wake-up on character reception

- Auto-baud calibration

- 12-bit Break character transmission

- Synchronous Master (half-duplex) with selectable clock polarity

- Synchronous Slave (half-duplex) with selectable clock polarity

The pins of the Enhanced USART are multiplexed with PORTC. In order to configure RC6/TX/CK and RC7/RX/DT as a USART:

- bit, SPEN (RCSTA<7>), must be set (= 1)

- bit, TRISC<7>, must be set (= 1)

- bit, TRISC<6>, must be cleared (= 0) for Asynchronous and Synchronous Master modes, or set (= 1) for Synchronous Slave mode

| Note: | The EUSART control will automatically       |  |  |  |  |  |  |

|-------|---------------------------------------------|--|--|--|--|--|--|

|       | reconfigure the pin from input to output as |  |  |  |  |  |  |

|       | needed.                                     |  |  |  |  |  |  |

The operation of the Enhanced USART module is controlled through three registers:

- Transmit Status and Control (TXSTA)

- Receive Status and Control (RCSTA)

- Baud Rate Control (BAUDCON)

These are detailed on the following pages in Register 19-1, Register 19-2 and Register 19-3, respectively.

| Name    | Bit 7                                         | Bit 6       | Bit 5       | Bit 4      | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values on<br>Page: |

|---------|-----------------------------------------------|-------------|-------------|------------|-------|--------|--------|--------|-----------------------------|

| INTCON  | GIE/GIEH                                      | PEIE/GIEL   | TMR0IE      | INT0IE     | RBIE  | TMR0IF | INT0IF | RBIF   | 55                          |

| PIR1    | PSPIF <sup>(1)</sup>                          | ADIF        | RCIF        | TXIF       | SSPIF | CCP1IF | TMR2IF | TMR1IF | 58                          |

| PIE1    | PSPIE <sup>(1)</sup>                          | ADIE        | RCIE        | TXIE       | SSPIE | CCP1IE | TMR2IE | TMR1IE | 58                          |

| IPR1    | PSPIP <sup>(1)</sup>                          | ADIP        | RCIP        | TXIP       | SSPIP | CCP1IP | TMR2IP | TMR1IP | 58                          |

| RCSTA   | SPEN                                          | RX9         | SREN        | CREN       | ADDEN | FERR   | OERR   | RX9D   | 57                          |

| TXREG   | EUSART T                                      | ransmit Reg | ister       |            |       |        |        |        | 57                          |

| TXSTA   | CSRC                                          | TX9         | TXEN        | SYNC       | SENDB | BRGH   | TRMT   | TX9D   | 57                          |

| BAUDCON | ABDOVF                                        | RCIDL       | _           | SCKP       | BRG16 | —      | WUE    | ABDEN  | 57                          |

| SPBRGH  | EUSART Baud Rate Generator Register High Byte |             |             |            |       |        |        |        |                             |

| SPBRG   | EUSART B                                      | aud Rate G  | enerator Re | gister Low | Byte  |        |        |        | 57                          |

## TABLE 19-5: REGISTERS ASSOCIATED WITH ASYNCHRONOUS TRANSMISSION

Legend: — = unimplemented locations read as '0'. Shaded cells are not used for asynchronous transmission.

Note 1: Reserved in PIC18F2X80 devices; always maintain these bits clear.

### 23.6 Operation During Sleep

When enabled, the HLVD circuitry continues to operate during Sleep. If the device voltage crosses the trip point, the HLVDIF bit will be set and the device will wake-up from Sleep. Device execution will continue from the interrupt vector address if interrupts have been globally enabled.

## 23.7 Effects of a Reset

A device Reset forces all registers to their Reset state. This forces the HLVD module to be turned off.

| Name    | Bit 7    | Bit 6     | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0   | Reset<br>Values<br>on Page: |

|---------|----------|-----------|--------|--------|--------|--------|--------|---------|-----------------------------|

| HLVDCON | VDIRMAG  | —         | IRVST  | HLVDEN | HLVDL3 | HLVDL2 | HLVDL1 | HLVDL0  | 56                          |

| INTCON  | GIE/GIEH | PEIE/GIEL | TMR0IE | INT0IE | RBIE   | TMR0IF | INT0IF | RBIF    | 55                          |

| PIR2    | OSCFIF   | CMIF      | —      | EEIF   | BCLIF  | HLVDIF | TMR3IF | ECCP1IF | 58                          |

| PIE2    | OSCFIE   | CMIE      | —      | EEIE   | BCLIE  | HLVDIE | TMR3IE | ECCP1IE | 58                          |

| IPR2    | OSCFIP   | CMIP      | _      | EEIP   | BCLIP  | HLVDIP | TMR3IP | ECCP1IP | 57                          |

#### TABLE 23-1: REGISTERS ASSOCIATED WITH HIGH/LOW-VOLTAGE DETECT MODULE

Legend: — = unimplemented, read as '0'. Shaded cells are unused by the HLVD module.

# 24.0 ECAN MODULE

PIC18F2480/2580/4480/4580 devices contain an Enhanced Controller Area Network (ECAN) module. The ECAN module is fully backward compatible with the CAN module available in PIC18CXX8 and PIC18FXX8 devices.

The Controller Area Network (CAN) module is a serial interface which is useful for communicating with other peripherals or microcontroller devices. This interface, or protocol, was designed to allow communications within noisy environments.

The ECAN module is a communication controller, implementing the CAN 2.0A or B protocol as defined in the BOSCH specification. The module will support CAN 1.2, CAN 2.0A, CAN 2.0B Passive and CAN 2.0B Active versions of the protocol. The module implementation is a full CAN system; however, the CAN specification is not covered within this data sheet. Refer to the BOSCH CAN specification for further details.

The module features are as follows:

- Implementation of the CAN protocol, CAN 1.2, CAN 2.0A and CAN 2.0B

- DeviceNet<sup>™</sup> data bytes filter support

- Standard and extended data frames

- · 0-8 bytes data length

- Programmable bit rate up to 1 Mbit/sec

- Fully backward compatible with the PIC18XXX8

CAN module

- Three modes of operation:

- Mode 0 Legacy mode

- Mode 1 Enhanced Legacy mode with DeviceNet support

- Mode 2 FIFO mode with DeviceNet support

- · Support for remote frames with automated handling

- Double-buffered receiver with two prioritized received message storage buffers

- Six buffers programmable as RX and TX message buffers

- 16 full (standard/extended identifier) acceptance filters that can be linked to one of four masks

- Two full acceptance filter masks that can be assigned to any filter

- One full acceptance filter that can be used as either an acceptance filter or acceptance filter mask

- Three dedicated transmit buffers with application specified prioritization and abort capability

- Programmable wake-up functionality with integrated low-pass filter

- Programmable Loopback mode supports self-test operation

- Signaling via interrupt capabilities for all CAN receiver and transmitter error states

- · Programmable clock source

- Programmable link to timer module for time-stamping and network synchronization

- Low-power Sleep mode

#### 24.1 Module Overview

The CAN bus module consists of a protocol engine and message buffering and control. The CAN protocol engine automatically handles all functions for receiving and transmitting messages on the CAN bus. Messages are transmitted by first loading the appropriate data registers. Status and errors can be checked by reading the appropriate registers. Any message detected on the CAN bus is checked for errors and then matched against filters to see if it should be received and stored in one of the two receive registers.

The CAN module supports the following frame types:

- Standard Data Frame

- · Extended Data Frame

- Remote Frame

- Error Frame

- Overload Frame Reception

The CAN module uses the RB2/CANTX and RB3/ CANRX pins to interface with the CAN bus. In normal mode, the CAN module automatically overrides TRISB<2>. The user must ensure that TRISB<3> is set.

#### 24.1.1 MODULE FUNCTIONALITY

The CAN bus module consists of a protocol engine, message buffering and control (see Figure 24-1). The protocol engine can best be understood by defining the types of data frames to be transmitted and received by the module.

The following sequence illustrates the necessary initialization steps before the ECAN module can be used to transmit or receive a message. Steps can be added or removed depending on the requirements of the application.

- 1. Initial LAT and TRIS bits for RX and TX CAN.

- 2. Ensure that the ECAN module is in Configuration mode.

- 3. Select ECAN Operational mode.

- 4. Set up the Baud Rate registers.

- 5. Set up the Filter and Mask registers.

- 6. Set the ECAN module to normal mode or any other mode required by the application logic.

| CLRF                                              | Clear f                                                                                     |                                              |                 | CLRWDT                 | Clear Wat                                 | tchdog Tim                                                             | er        |  |  |

|---------------------------------------------------|---------------------------------------------------------------------------------------------|----------------------------------------------|-----------------|------------------------|-------------------------------------------|------------------------------------------------------------------------|-----------|--|--|

| Syntax:                                           | CLRF f{,                                                                                    | a}                                           |                 | Syntax:                | CLRWDT                                    | CLRWDT                                                                 |           |  |  |

| Operands:                                         | $0 \leq f \leq 255$                                                                         |                                              |                 | Operands:              | None                                      | None                                                                   |           |  |  |

|                                                   | $a \in [0,1]$                                                                               |                                              |                 | Operation:             | $000h \rightarrow Wl$                     | $000h \rightarrow WDT$ ,                                               |           |  |  |

| Operation:                                        | $000h \rightarrow f,$                                                                       |                                              |                 |                        | DT postscaler                             | ,                                                                      |           |  |  |

|                                                   | $1 \rightarrow Z$                                                                           |                                              |                 |                        | $1 \rightarrow TO,$<br>$1 \rightarrow PD$ |                                                                        |           |  |  |

| Status Affected:                                  |                                                                                             | Z                                            |                 | Status Affected:       | TO, PD                                    |                                                                        |           |  |  |

| Encoding:                                         | 0110                                                                                        | 0110 101a ffff ffff                          |                 | Encoding:              |                                           | 0000 00                                                                | 00 0100   |  |  |

| Description: Clears the contents of the specified |                                                                                             | Ū.                                           |                 |                        |                                           |                                                                        |           |  |  |

|                                                   | register.                                                                                   | ha Aaaaaa Bar                                | k in an lost of | Description:           |                                           | CLRWDT instruction resets the Watchdog Timer. It also resets the post- |           |  |  |

|                                                   | If 'a' is '0', the Access Bank is selected.<br>If 'a' is '1', the BSR is used to select the |                                              |                 |                        | •                                         | e WDT. Statu                                                           |           |  |  |

|                                                   | GPR bank.                                                                                   |                                              |                 |                        | PD are set.                               |                                                                        |           |  |  |

| If 'a' is '0' and the extended instruction        |                                                                                             |                                              | Words:          | 1                      |                                           |                                                                        |           |  |  |

|                                                   |                                                                                             | led, this instruc<br>Literal Offset A        | •               | Cycles:                | 1                                         |                                                                        |           |  |  |

|                                                   |                                                                                             | never f $\leq$ 95 (5F                        | •               | Q Cycle Activity:      |                                           |                                                                        |           |  |  |

|                                                   | Section 26                                                                                  | .2.3 "Byte-Ori                               | ented and       | Q1                     | Q2                                        | Q3                                                                     | Q4        |  |  |

|                                                   |                                                                                             | ed Instructions<br>set Mode" for             |                 | Decode                 | No                                        | Process                                                                | No        |  |  |

| Manda.                                            |                                                                                             |                                              | uetans.         |                        | operation                                 | Data                                                                   | operation |  |  |

| Words:                                            | 1                                                                                           |                                              |                 | <b>-</b> .             |                                           |                                                                        |           |  |  |

| Cycles:                                           | 1                                                                                           |                                              |                 | Example:               | CLRWDT                                    |                                                                        |           |  |  |

| Q Cycle Activity:                                 |                                                                                             |                                              |                 | Before Instru<br>WDT C |                                           | ?                                                                      |           |  |  |

| Q1                                                | Q2                                                                                          | Q3                                           | Q4              | After Instruc          |                                           | !                                                                      |           |  |  |

| Decode                                            | Read<br>register 'f'                                                                        | ReadProcessWriteregister 'f'Dataregister 'f' |                 |                        | Counter =                                 | 00h                                                                    |           |  |  |

|                                                   | register i                                                                                  | Data                                         | register i      | WDT P<br>TO            | ostscaler =                               | 0<br>1                                                                 |           |  |  |

| Example:                                          | CLRF                                                                                        | FLAG REG,                                    | 1               | PD                     | =                                         | 1                                                                      |           |  |  |

| Before Instru                                     | ction                                                                                       | —                                            |                 |                        |                                           |                                                                        |           |  |  |

| FLAG_I                                            |                                                                                             | h                                            |                 |                        |                                           |                                                                        |           |  |  |

| After Instruct                                    |                                                                                             | <b>b</b>                                     |                 |                        |                                           |                                                                        |           |  |  |

| FLAG_I                                            | REG = 00                                                                                    | n                                            |                 |                        |                                           |                                                                        |           |  |  |

| IORLW              | Inclusive                             | Inclusive OR Literal with W |      |           |  |  |  |  |

|--------------------|---------------------------------------|-----------------------------|------|-----------|--|--|--|--|

| Syntax:            | IORLW k                               | IORLW k                     |      |           |  |  |  |  |

| Operands:          | $0 \le k \le 255$                     | 5                           |      |           |  |  |  |  |

| Operation:         | (W) .OR. k                            | $\rightarrow W$             |      |           |  |  |  |  |

| Status Affected:   | N, Z                                  |                             |      |           |  |  |  |  |

| Encoding:          | 0000                                  | 1001                        | kkkk | kkkk      |  |  |  |  |

| Description:       | The conter<br>eight-bit lite<br>in W. |                             |      |           |  |  |  |  |

| Words:             | 1                                     |                             |      |           |  |  |  |  |

| Cycles:            | 1                                     |                             |      |           |  |  |  |  |

| Q Cycle Activity:  |                                       |                             |      |           |  |  |  |  |

| Q1                 | Q2                                    | Q3                          | 3    | Q4        |  |  |  |  |

| Decode             | Read<br>literal 'k'                   | Proce<br>Data               |      | rite to W |  |  |  |  |

| Example:           | IORLW                                 | 35h                         |      |           |  |  |  |  |

| Before Instru<br>W | = 9Ah                                 |                             |      |           |  |  |  |  |

| IORWF             | Inclusive                                                                                                                                                                                                                                                       | Inclusive OR W with f                                                                                                                                                                                       |                      |  |  |  |  |  |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|--|--|--|--|--|

| Syntax:           | IORWF f                                                                                                                                                                                                                                                         | {,d {,a}}                                                                                                                                                                                                   |                      |  |  |  |  |  |

| Operands:         |                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                             |                      |  |  |  |  |  |

| Operation:        | (W) .OR. (f                                                                                                                                                                                                                                                     | ) $\rightarrow$ dest                                                                                                                                                                                        |                      |  |  |  |  |  |

| Status Affected:  | N, Z                                                                                                                                                                                                                                                            |                                                                                                                                                                                                             |                      |  |  |  |  |  |

| Encoding:         | 0001                                                                                                                                                                                                                                                            | 00da ff                                                                                                                                                                                                     | ff ffff              |  |  |  |  |  |

| Description:      | <ul> <li>'0', the result is<br/>the result is</li> <li>If 'a' is '0', t</li> <li>If 'a' is '1', t</li> <li>GPR bank.</li> <li>If 'a' is '0' a</li> <li>set is enable</li> <li>in Indexed</li> <li>mode wher</li> <li>Section 26</li> <li>Bit-Oriente</li> </ul> | If 'a' is '0' and the extended instruction<br>set is enabled, this instruction operates<br>in Indexed Literal Offset Addressing<br>mode whenever $f \le 95$ (5Fh). See<br>Section 26.2.3 "Byte-Oriented and |                      |  |  |  |  |  |

|                   |                                                                                                                                                                                                                                                                 | Literal Offset Mode" for details.                                                                                                                                                                           |                      |  |  |  |  |  |

| Words:            |                                                                                                                                                                                                                                                                 | 1                                                                                                                                                                                                           |                      |  |  |  |  |  |

| Cycles:           | 1                                                                                                                                                                                                                                                               | 1                                                                                                                                                                                                           |                      |  |  |  |  |  |

| Q Cycle Activity: |                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                             |                      |  |  |  |  |  |

| Q1                | Q2                                                                                                                                                                                                                                                              | Q3                                                                                                                                                                                                          | Q4                   |  |  |  |  |  |

| Decode            | Read<br>register 'f'                                                                                                                                                                                                                                            | Process<br>Data                                                                                                                                                                                             | Write to destination |  |  |  |  |  |

#### Example:

| imple:             | IORWF          | RESULT, | Ο, | 1 |

|--------------------|----------------|---------|----|---|

| Before Instruction | on             |         |    |   |

| RESULT =<br>W =    | = 13h<br>= 91h |         |    |   |

| After Instruction  |                |         |    |   |

| RESULT =<br>W =    | = 13h<br>= 93h |         |    |   |

After Instruction BFh W =

### 27.2 MPLAB C Compilers for Various Device Families

The MPLAB C Compiler code development systems are complete ANSI C compilers for Microchip's PIC18, PIC24 and PIC32 families of microcontrollers and the dsPIC30 and dsPIC33 families of digital signal controllers. These compilers provide powerful integration capabilities, superior code optimization and ease of use.

For easy source level debugging, the compilers provide symbol information that is optimized to the MPLAB IDE debugger.

# 27.3 HI-TECH C for Various Device Families

The HI-TECH C Compiler code development systems are complete ANSI C compilers for Microchip's PIC family of microcontrollers and the dsPIC family of digital signal controllers. These compilers provide powerful integration capabilities, omniscient code generation and ease of use.

For easy source level debugging, the compilers provide symbol information that is optimized to the MPLAB IDE debugger.

The compilers include a macro assembler, linker, preprocessor, and one-step driver, and can run on multiple platforms.

# 27.4 MPASM Assembler

The MPASM Assembler is a full-featured, universal macro assembler for PIC10/12/16/18 MCUs.

The MPASM Assembler generates relocatable object files for the MPLINK Object Linker, Intel<sup>®</sup> standard HEX files, MAP files to detail memory usage and symbol reference, absolute LST files that contain source lines and generated machine code and COFF files for debugging.

The MPASM Assembler features include:

- · Integration into MPLAB IDE projects

- User-defined macros to streamline assembly code

- Conditional assembly for multi-purpose source files

- Directives that allow complete control over the assembly process

### 27.5 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK Object Linker combines relocatable objects created by the MPASM Assembler and the MPLAB C18 C Compiler. It can link relocatable objects from precompiled libraries, using directives from a linker script.

The MPLIB Object Librarian manages the creation and modification of library files of precompiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

### 27.6 MPLAB Assembler, Linker and Librarian for Various Device Families

MPLAB Assembler produces relocatable machine code from symbolic assembly language for PIC24, PIC32 and dsPIC devices. MPLAB C Compiler uses the assembler to produce its object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- · Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- Command line interface

- · Rich directive set

- Flexible macro language

- MPLAB IDE compatibility

# 28.2 DC Characteristics:

#### Power-Down and Supply Current PIC18F2480/2580/4480/4580 (Industrial, Extended) PIC18LF2480/2580/4480/4580 (Industrial) (Continued)