#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

-XF

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 40MHz                                                                       |

| Connectivity               | CANbus, I <sup>2</sup> C, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                 |

| Number of I/O              | 25                                                                          |

| Program Memory Size        | 16KB (8K x 16)                                                              |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 256 x 8                                                                     |

| RAM Size                   | 768 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                   |

| Data Converters            | A/D 8x10b                                                                   |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 28-VQFN Exposed Pad                                                         |

| Supplier Device Package    | 28-QFN (6x6)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf2480t-i-ml |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

NOTES:

### 4.3 Sleep Mode

The power-managed Sleep mode in the PIC18F2480/2580/4480/4580 devices is identical to the legacy Sleep mode offered in all other PIC devices. It is entered by clearing the IDLEN bit (the default state on device Reset) and executing the SLEEP instruction. This shuts down the selected oscillator (Figure 4-5). All clock source status bits are cleared.

Entering the Sleep mode from any other mode does not require a clock switch. This is because no clocks are needed once the controller has entered Sleep. If the WDT is selected, the INTRC source will continue to operate. If the Timer1 oscillator is enabled, it will also continue to run.

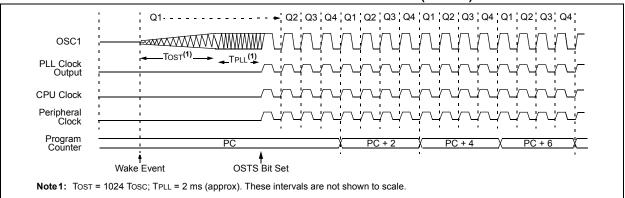

When a wake event occurs in Sleep mode (by interrupt, Reset or WDT time-out), the device will not be clocked until the clock source selected by the SCS1:SCS0 bits becomes ready (see Figure 4-6), or it will be clocked from the internal oscillator block if either the Two-Speed Start-up or the Fail-Safe Clock Monitor are enabled (see **Section 25.0 "Special Features of the CPU"**). In either case, the OSTS bit is set when the primary clock is providing the device clocks. The IDLEN and SCS bits are not affected by the wake-up.

### 4.4 Idle Modes

The Idle modes allow the controller's CPU to be selectively shut down while the peripherals continue to operate. Selecting a particular Idle mode allows users to further manage power consumption.

If the IDLEN bit is set to '1' when a SLEEP instruction is executed, the peripherals will be clocked from the clock source selected using the SCS<1:0> bits; however, the CPU will not be clocked. The clock source status bits are not affected. Setting IDLEN and executing a SLEEP instruction provides a quick method of switching from a given Run mode to its corresponding Idle mode.

If the WDT is selected, the INTRC source will continue to operate. If the Timer1 oscillator is enabled, it will also continue to run.

Since the CPU is not executing instructions, the only exits from any of the Idle modes are by interrupt, WDT time-out or a Reset. When a wake event occurs, CPU execution is delayed by an interval of TCSD (parameter 38, Table 28-10) while it becomes ready to execute code. When the CPU begins executing code, it resumes with the same clock source for the current Idle mode. For example, when waking from RC\_IDLE mode, the internal oscillator block will clock the CPU and peripherals (in other words, RC\_RUN mode). The IDLEN and SCS bits are not affected by the wake-up.

While in any Idle mode or Sleep mode, a WDT time-out will result in a WDT wake-up to the Run mode currently specified by the SCS<1:0> bits.

FIGURE 4-5: TRANSITION TIMING FOR ENTRY TO SLEEP MODE

| Q1 Q2 Q3 Q4           | Q1     |              | - ;      |             |             | <u>.</u>    |          | ;;                                    | ► |

|-----------------------|--------|--------------|----------|-------------|-------------|-------------|----------|---------------------------------------|---|

|                       |        | 1            |          | 1           | 1           |             | 1        |                                       |   |

|                       |        | -<br>-<br>-  | 1        | 1<br>1<br>1 | 1<br>1<br>1 | 1<br>1<br>1 | 1<br>1   | · · ·                                 |   |

|                       | 1      | 1            | 1        | 1           | 1           | 1           | 1        | · · ·                                 |   |

| Peripheral            |        | <u> </u><br> | 1        | 1<br>1      | 1<br>1      |             | 1<br>T   | · · · · · · · · · · · · · · · · · · · |   |

| Sleep                 |        | <u> </u>     |          | <u> </u>    | <u> </u>    | <u> </u>    | <u> </u> | <u>' '</u>                            |   |

|                       | 1      | 1            |          | 1           | 1<br>1      |             | 1        | · ·                                   |   |

| Program<br>Counter PC | PC + 2 |              | <u>.</u> | <u>.</u>    | <u>,</u>    | <u>.</u>    | 1        | <u>' '</u>                            | > |

| File Name             | Bit 7              | Bit 6              | Bit 5      | Bit 4                  | Bit 3                  | Bit 2                  | Bit 1                  | Bit 0                  | Value on<br>POR, BOR | Details on<br>Page: |

|-----------------------|--------------------|--------------------|------------|------------------------|------------------------|------------------------|------------------------|------------------------|----------------------|---------------------|

| PORTE <sup>(3)</sup>  | —                  |                    | _          | _                      | RE3 <sup>(5)</sup>     | RE2 <sup>(3)</sup>     | RE1 <sup>(3)</sup>     | RE0 <sup>(3)</sup>     | xxxx                 | 58, 150             |

| PORTD <sup>(3)</sup>  | PORTD Data         | Direction Regis    | ster       |                        |                        |                        |                        |                        | XXXX XXXX            | 58, 143             |

| PORTC                 | PORTC Data [       | Direction Regis    | ster       |                        |                        |                        |                        |                        | XXXX XXXX            | 58, 141             |

| PORTB                 | PORTB Data         | Direction Regis    | ster       |                        |                        |                        |                        |                        | XXXX XXXX            | 58, 138             |

| PORTA                 | RA7 <sup>(6)</sup> | RA6 <sup>(6)</sup> | PORTA Data | Direction Reg          | gister                 |                        |                        |                        | xx00 0000            | 58, 135             |

| ECANCON               | MDSEL1             | MDSEL0             | FIFOWM     | EWIN4                  | EWIN3                  | EWIN2                  | EWIN1                  | EWIN0                  | 0001 000             | 58, 286             |

| TXERRCNT              | TEC7               | TEC6               | TEC5       | TEC4                   | TEC3                   | TEC2                   | TEC1                   | TEC0                   | 0000 0000            | 58, 291             |

| RXERRCNT              | REC7               | REC6               | REC5       | REC4                   | REC3                   | REC2                   | REC1                   | REC0                   | 0000 0000            | 58, 299             |

| COMSTAT<br>Mode 0     | RXB00VFL           | RXB10VFL           | ТХВО       | TXBP                   | RXBP                   | TXWARN                 | RXWARN                 | EWARN                  | 0000 0000            | 58, 287             |

| COMSTAT<br>Mode 1     | _                  | RXBnOVFL           | ТХВО       | TXBP                   | RXBP                   | TXWARN                 | RXWARN                 | EWARN                  | -000 0000            | 58, 287             |

| COMSTAT<br>Mode 2     | FIFOEMPTY          | RXBnOVFL           | ТХВО       | TXBP                   | RXBP                   | TXWARN                 | RXWARN                 | EWARN                  | 0000 0000            | 58, 287             |

| CIOCON                | _                  | _                  | ENDRHI     | CANCAP                 | _                      | _                      | _                      | _                      | 00                   | 58, 320             |

| BRGCON3               | WAKDIS             | WAKFIL             | _          | _                      | _                      | SEG2PH2                | SEG2PH1                | SEG2PH0                | 00000                | 59, 319             |

| BRGCON2               | SEG2PHTS           | SAM                | SEG1PH2    | SEG1PH1                | SEG1PH0                | PRSEG2                 | PRSEG1                 | PRSEG0                 | 0000 0000            | 59, 318             |

| BRGCON1               | SJW1               | SJW0               | BRP5       | BRP4                   | BRP3                   | BRP2                   | BRP1                   | BRP0                   | 0000 0000            | 59, 317             |

| CANCON<br>Mode 0      | REQOP2             | REQOP1             | REQOP0     | ABAT                   | WIN2 <sup>(7)</sup>    | WIN1 <sup>(7)</sup>    | WIN0 <sup>(7)</sup>    | (7)                    | 1000 000-            | 59, 282             |

| CANCON<br>Mode 1      | REQOP2             | REQOP1             | REQOP0     | ABAT                   | (7)                    | (7)                    | (7)                    | (7)                    | 1000                 | 59, 282             |

| CANCON<br>Mode 2      | REQOP2             | REQOP1             | REQOP0     | ABAT                   | FP3 <sup>(7)</sup>     | FP2 <sup>(7)</sup>     | FP1 <sup>(7)</sup>     | FP0 <sup>(7)</sup>     | 1000 0000            | 59, 282             |

| CANSTAT<br>Mode 0     | OPMODE2            | OPMODE1            | OPMODE0    | (7)                    | ICODE3 <sup>(7)</sup>  | ICODE2 <sup>(7)</sup>  | ICODE1 <sup>(7)</sup>  | (7)                    | 000- 0000            | 59, 283             |

| CANSTAT<br>Modes 1, 2 | OPMODE2            | OPMODE1            | OPMODE0    | EICODE4 <sup>(7)</sup> | EICODE3 <sup>(7)</sup> | EICODE2 <sup>(7)</sup> | EICODE1 <sup>(7)</sup> | EICODE0 <sup>(7)</sup> | 0000 0000            | 59, 283             |

| RXB0D7                | RXB0D77            | RXB0D76            | RXB0D75    | RXB0D74                | RXB0D73                | RXB0D72                | RXB0D71                | RXB0D70                | XXXX XXXX            | 59, 298             |

| RXB0D6                | RXB0D67            | RXB0D66            | RXB0D65    | RXB0D64                | RXB0D63                | RXB0D62                | RXB0D61                | RXB0D60                | XXXX XXXX            | 59, 298             |

| RXB0D5                | RXB0D57            | RXB0D56            | RXB0D55    | RXB0D54                | RXB0D53                | RXB0D52                | RXB0D51                | RXB0D50                | XXXX XXXX            | 59, 298             |

| RXB0D4                | RXB0D47            | RXB0D46            | RXB0D45    | RXB0D44                | RXB0D43                | RXB0D42                | RXB0D41                | RXB0D40                | XXXX XXXX            | 59, 298             |

| RXB0D3                | RXB0D37            | RXB0D36            | RXB0D35    | RXB0D34                | RXB0D33                | RXB0D32                | RXB0D31                | RXB0D30                | XXXX XXXX            | 59, 298             |

| RXB0D2                | RXB0D27            | RXB0D26            | RXB0D25    | RXB0D24                | RXB0D23                | RXB0D22                | RXB0D21                | RXB0D20                | XXXX XXXX            | 59, 298             |

| RXB0D1                | RXB0D17            | RXB0D16            | RXB0D15    | RXB0D14                | RXB0D13                | RXB0D12                | RXB0D11                | RXB0D10                | XXXX XXXX            | 59, 298             |

| RXB0D0                | RXB0D07            | RXB0D06            | RXB0D05    | RXB0D04                | RXB0D03                | RXB0D02                | RXB0D01                | RXB0D00                | XXXX XXXX            | 59, 298             |

| RXB0DLC               | —                  | RXRTR              | RB1        | RB0                    | DLC3                   | DLC2                   | DLC1                   | DLC0                   | -xxx xxxx            | 59, 298             |

| RXB0EIDL              | EID7               | EID6               | EID5       | EID4                   | EID3                   | EID2                   | EID1                   | EID0                   | XXXX XXXX            | 59, 297             |

| RXB0EIDH              | EID15              | EID14              | EID13      | EID12                  | EID11                  | EID10                  | EID9                   | EID8                   | XXXX XXXX            | 59, 297             |

| RXB0SIDL              | SID2               | SID1               | SID0       | SRR                    | EXID                   | —                      | EID17                  | EID16                  | xxxx x-xx            | 59, 297             |

| RXB0SIDH              | SID10              | SID9               | SID8       | SID7                   | SID6                   | SID5                   | SID4                   | SID3                   | XXXX XXXX            | 59, 296             |

### TABLE 6-2:REGISTER FILE SUMMARY (PIC18F2480/2580/4480/4580) (CONTINUED)

**Legend:** x = unknown, u = unchanged, - = unimplemented, q = value depends on condition

Note 1: Bit 21 of the PC is only available in Test mode and Serial Programming modes.

The SBOREN bit is only available when CONFIG2L<1:0> = 01; otherwise, it is disabled and reads as '0'. See Section 5.4 "Brown-out Reset (BOR)".

These registers and/or bits are not implemented on PIC18F2X80 devices and are read as '0'. Reset values are shown for PIC18F4X80 devices; individual unimplemented bits should be interpreted as '-'.

4: The PLLEN bit is only available in specific oscillator configuration; otherwise, it is disabled and reads as '0'. See Section 3.6.4 "PLL in INTOSC Modes".

5: The RE3 bit is only available when Master Clear Reset is disabled (CONFIG3H<7> = 0); otherwise, RE3 reads as '0'. This bit is read-only.

6: RA6/RA7 and their associated latch and direction bits are individually configured as port pins based on various primary oscillator modes. When disabled, these bits read as '0'.

7: CAN bits have multiple functions depending on the selected mode of the CAN module.

8: This register reads all '0's until the ECAN™ technology is set up in Mode 1 or Mode 2.

9: These registers are available on PIC18F4X80 devices only.

### 6.4.3.2 FSR Registers and POSTINC, POSTDEC, PREINC and PLUSW

In addition to the INDF operand, each FSR register pair also has four additional indirect operands. Like INDF, these are "virtual" registers that cannot be indirectly read or written to. Accessing these registers actually accesses the associated FSR register pair, but also performs a specific action on its stored value. They are:

- POSTDEC: accesses the FSR value, then automatically decrements it by 1 afterwards

- POSTINC: accesses the FSR value, then automatically increments it by 1 afterwards

- PREINC: increments the FSR value by 1, then uses it in the operation

- PLUSW: adds the signed value of the W register (range of -127 to 128) to that of the FSR and uses the new value in the operation.

In this context, accessing an INDF register, uses the value in the FSR registers without changing them. Similarly, accessing a PLUSW register gives the FSR value offset by that in the W register; neither value is actually changed in the operation. Accessing the other virtual registers changes the value of the FSR registers.

Operations on the FSRs with POSTDEC, POSTINC and PREINC affect the entire register pair; that is, rollovers of the FSRnL register from FFh to 00h carry over to the FSRnH register. On the other hand, results of these operations do not change the value of any flags in the STATUS register (e.g., Z, N, OV, etc.).

The PLUSW register can be used to implement a form of Indexed Addressing in the data memory space. By manipulating the value in the W register, users can reach addresses that are fixed offsets from pointer addresses. In some applications, this can be used to implement some powerful program control structure, such as software stacks, inside of data memory.

### 6.4.3.3 Operations by FSRs on FSRs

Indirect Addressing operations that target other FSRs or virtual registers represent special cases. For example, using an FSR to point to one of the virtual registers will not result in successful operations. As a specific case, assume that FSR0H:FSR0L contains FE7h, the address of INDF1. Attempts to read the value of the INDF1 using INDF0 as an operand will return 00h. Attempts to write to INDF1 using INDF0 as the operand will result in a NOP.

On the other hand, using the virtual registers to write to an FSR pair may not occur as planned. In these cases, the value will be written to the FSR pair but without any incrementing or decrementing. Thus, writing to INDF2 or POSTDEC2 will write the same value to the FSR2H:FSR2L.

Since the FSRs are physical registers mapped in the SFR space, they can be manipulated through all direct operations. Users should proceed cautiously when working on these registers, particularly if their code uses Indirect Addressing.

Similarly, operations by Indirect Addressing are generally permitted on all other SFRs. Users should exercise the appropriate caution that they do not inadvertently change settings that might affect the operation of the device.

### 10.6 INTx Pin Interrupts

External interrupts on the RB0/INT0, RB1/INT1 and RB2/INT2 pins are edge-triggered. If the corresponding INTEDGx bit in the INTCON2 register is set (= 1), the interrupt is triggered by a rising edge; if the bit is clear, the trigger is on the falling edge. When a valid edge appears on the RBx/INTx pin, the corresponding flag bit, INTxF, is set. This interrupt can be disabled by clearing the corresponding enable bit, INTxE. Flag bit, INTxF, must be cleared in software in the Interrupt Service Routine before re-enabling the interrupt.

All external interrupts (INT0, INT1 and INT2) can wakeup the processor from the power-managed modes, if bit INTxE was set prior to going into power-managed modes. If the Global Interrupt Enable bit, GIE, is set, the processor will branch to the interrupt vector following wake-up.

Interrupt priority for INT1 and INT2 is determined by the value contained in the interrupt priority bits, INT1IP (INTCON3<6>) and INT2IP (INTCON3<7>). There is no priority bit associated with INT0. It is always a high-priority interrupt source.

### 10.7 TMR0 Interrupt

In 8-bit mode (which is the default), an overflow in the TMR0 register (FFh  $\rightarrow$  00h) will set flag bit TMR0IF. In 16-bit mode, an overflow in the TMR0H:TMR0L register pair (FFFFh  $\rightarrow$  0000h) will set TMR0IF. The interrupt can be enabled/disabled by setting/clearing enable bit TMR0IE (INTCON<5>). Interrupt priority for Timer0 is determined by the value contained in the interrupt priority bit, TMR0IP (INTCON2<2>). See Section 14.0 "Timer2 Module" for further details on the Timer0 module.

### 10.8 PORTB Interrupt-on-Change

An input change on PORTB<7:4> sets flag bit, RBIF (INTCON<0>). The interrupt can be enabled/disabled by setting/clearing enable bit, RBIE (INTCON<3>). Interrupt priority for PORTB interrupt-on-change is determined by the value contained in the interrupt priority bit, RBIP (INTCON2<0>).

### **10.9 Context Saving During Interrupts**

During interrupts, the return PC address is saved on the stack. Additionally, the WREG, STATUS and BSR registers are saved on the Fast Return Stack. If a fast return from interrupt is not used (See **Section 6.3 "Data Memory Organization"**), the user may need to save the WREG, STATUS and BSR registers on entry to the Interrupt Service Routine. Depending on the user's application, other registers may also need to be saved. Example 10-1 saves and restores the WREG, STATUS and BSR registers during an Interrupt Service Routine.

| MOVWF W TEMP              | ; W TEMP is in virtual bank    |  |

|---------------------------|--------------------------------|--|

| MOVFF STATUS, STATUS TEMP | ; STATUS TEMP located anywhere |  |

| MOVFF BSR, BSR TEMP       | ; BSR TMEP located anywhere    |  |

| ;                         |                                |  |

| ; USER ISR CODE           |                                |  |

| ;                         |                                |  |

| MOVFF BSR_TEMP, BSR       | ; Restore BSR                  |  |

| MOVF W_TEMP, W            | ; Restore WREG                 |  |

| MOVFF STATUS_TEMP, STATUS | ; Restore STATUS               |  |

| _                         |                                |  |

|                           |                                |  |

### EXAMPLE 10-1: SAVING STATUS, WREG AND BSR REGISTERS IN RAM

### 17.0 ENHANCED CAPTURE/COMPARE/PWM (ECCP) MODULE

**Note:** The ECCP1 module is implemented only in PIC18F4X80 (40/44-pin) devices.

In PIC18F4480/4580 devices, ECCP1 is implemented as a standard CCP module with Enhanced PWM capabilities. These include the provision for 2 or 4 output channels, user-selectable polarity, dead-band control and automatic shutdown and restart. The Enhanced features are discussed in detail in **Section 17.4 "Enhanced PWM Mode"**. Capture, Compare and single-output PWM functions of the ECCP module are the same as described for the standard CCP module.

The control register for the Enhanced CCP module is shown in Register 17-1. It differs from the CCP1CON register in PIC18F2480/2580 devices in that the two Most Significant bits are implemented to control PWM functionality.

### REGISTER 17-1: ECCP1CON REGISTER (ECCP1 MODULE, PIC18F4480/4580 DEVICES)

| R/W-0   | R/W-0   | R/W-0  | R/W-0  | R/W-0   | R/W-0   | R/W-0   | R/W-0   |

|---------|---------|--------|--------|---------|---------|---------|---------|

| EPWM1M1 | EPWM1M0 | EDC1B1 | EDC1B0 | ECCP1M3 | ECCP1M2 | ECCP1M1 | ECCP1M0 |

| bit 7   |         |        |        |         |         |         | bit 0   |

| Legend:      |                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                         |                                                                                                                        |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|

| R = Readab   | le bit                                                                                                                                                                         | W = Writable bit                                                                                                                                                                                                                                                                                                 | U = Unimplemented bit                                                                                                                                                                                                                                                                                   | , read as '0'                                                                                                          |

| -n = Value a | t POR                                                                                                                                                                          | '1' = Bit is set                                                                                                                                                                                                                                                                                                 | '0' = Bit is cleared                                                                                                                                                                                                                                                                                    | x = Bit is unknown                                                                                                     |

| bit 7-6      | <u>If ECCP1</u><br>xx = P1A<br><u>If ECCP1</u><br>00 = Sing<br>01 = Full-<br>10 = Half                                                                                         | <u>M&lt;3:2&gt; = 11:</u><br>gle output: P1A modulated; P<br>bridge output forward: P1D r<br>-bridge output: P1A, P1B mod                                                                                                                                                                                        | are input/output; P1B, P1C, F<br>1B, P1C, P1D assigned as p<br>nodulated; P1A active; P1B,                                                                                                                                                                                                              | ort pins<br>P1C inactive<br>ol; P1C, P1D assigned as port pins                                                         |

| bit 5-4      | <u>Capture r</u><br>Unused.<br><u>Compare</u><br>Unused.<br><u>PWM mo</u>                                                                                                      | <u>mode:</u><br><u>de:</u><br>s are the two LSbs of the 10-                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                         | It MSbs of the duty cycle are found                                                                                    |

| bit 3-0      | ECCP1M<br>0000 = 0<br>0001 = F<br>0010 = 0<br>0011 = F<br>0100 = 0<br>0111 = 0<br>1000 = 0<br>1010 = 0<br>1010 = 0<br>1011 = 0<br>1011 = 0<br>1001 = F<br>1100 = F<br>1110 = F | <3:0>: Enhanced CCP1 Moc<br>Capture/Compare/PWM off (re<br>Reserved<br>Compare mode; toggle output<br>Reserved<br>Capture mode; every falling e<br>Capture mode; every falling e<br>Capture mode; every falling e<br>Capture mode; every 16th risi<br>Compare mode; initialize ECC<br>Compare mode; generate sof | esets ECCP1 module)<br>t on match<br>dge<br>g edge<br>g edge<br>CP1 pin low; set output on co<br>P1 pin high; clear output on c<br>tware interrupt only; ECCP1<br>al event (ECCP1 resets TMR<br>ECCP1 match)<br>-high; P1B, P1D active-high<br>-high; P1B, P1D active-low<br>-low; P1B, P1D active-high | mpare match (set ECCP1IF)<br>ompare match (set ECCP1IF)<br>pin reverts to I/O state<br>1 or TMR3, sets ECCP1IF bit and |

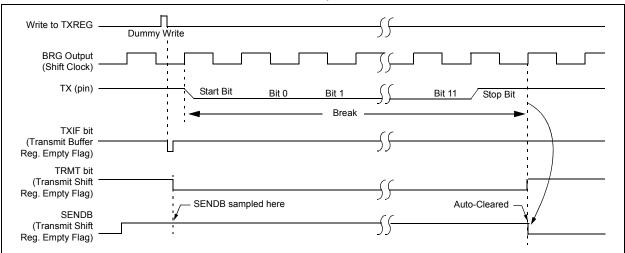

### 19.2.5 BREAK CHARACTER SEQUENCE

The Enhanced EUSART module has the capability of sending the special Break character sequences that are required by the LIN/J2602 bus standard. The Break character transmit consists of a Start bit, followed by twelve '0' bits and a Stop bit. The Frame Break character is sent whenever the SENDB and TXEN bits (TXSTA<3> and TXSTA<5>) are set while the Transmit Shift register is loaded with data. Note that the value of data written to TXREG will be ignored and all '0's will be transmitted.

The SENDB bit is automatically reset by hardware after the corresponding Stop bit is sent. This allows the user to preload the transmit FIFO with the next transmit byte following the Break character (typically, the Sync character in the LIN/J2602 specification).

Note that the data value written to the TXREG for the Break character is ignored. The write simply serves the purpose of initiating the proper sequence.

The TRMT bit indicates when the transmit operation is active or Idle, just as it does during normal transmission. See Figure 19-10 for the timing of the Break character sequence.

### 19.2.5.1 Break and Sync Transmit Sequence

The following sequence will send a message frame header made up of a Break, followed by an Auto-Baud Sync byte. This sequence is typical of a LIN/J2602 bus master.

- 1. Configure the EUSART for the desired mode.

- 2. Set the TXEN and SENDB bits to set up the Break character.

- 3. Load the TXREG with a dummy character to initiate transmission (the value is ignored).

- 4. Write '55h' to TXREG to load the Sync character into the transmit FIFO buffer.

- 5. After the Break has been sent, the SENDB bit is reset by hardware. The Sync character now transmits in the preconfigured mode.

When the TXREG becomes empty, as indicated by the TXIF, the next data byte can be written to TXREG.

### 19.2.6 RECEIVING A BREAK CHARACTER

The Enhanced USART module can receive a Break character in two ways.

The first method forces configuration of the baud rate at a frequency of 9/13 the typical speed. This allows for the Stop bit transition to be at the correct sampling location (13 bits for Break versus Start bit and 8 data bits for typical data).

The second method uses the auto-wake-up feature described in **Section 19.2.4 "Auto-Wake-up on Sync Break Character"**. By enabling this feature, the EUSART will sample the next two transitions on RX/DT, cause an RCIF interrupt and receive the next data byte followed by another interrupt.

Note that following a Break character, the user will typically want to enable the Auto-Baud Rate Detect feature. For both methods, the user can set the ABD bit once the TXIF interrupt is observed.

#### FIGURE 19-10: SEND BREAK CHARACTER SEQUENCE

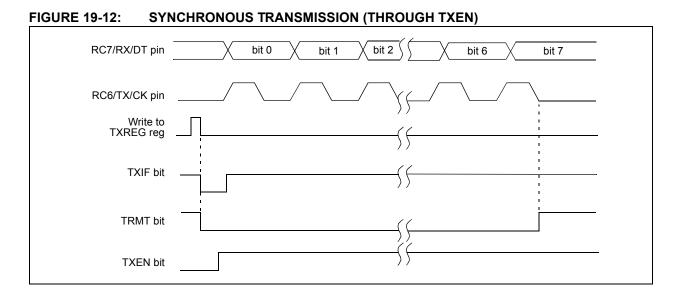

#### TABLE 19-7: REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER TRANSMISSION

| Name    | Bit 7                                          | Bit 6       | Bit 5       | Bit 4       | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on Page: |

|---------|------------------------------------------------|-------------|-------------|-------------|-------|--------|--------|--------|-----------------------------|

| INTCON  | GIE/GIEH                                       | PEIE/GIEL   | TMR0IE      | INT0IE      | RBIE  | TMR0IF | INT0IF | RBIF   | 55                          |

| PIR1    | PSPIF <sup>(1)</sup>                           | ADIF        | RCIF        | TXIF        | SSPIF | CCP1IF | TMR2IF | TMR1IF | 58                          |

| PIE1    | PSPIE <sup>(1)</sup>                           | ADIE        | RCIE        | TXIE        | SSPIE | CCP1IE | TMR2IE | TMR1IE | 58                          |

| IPR1    | PSPIP <sup>(1)</sup>                           | ADIP        | RCIP        | TXIP        | SSPIP | CCP1IP | TMR2IP | TMR1IP | 58                          |

| RCSTA   | SPEN                                           | RX9         | SREN        | CREN        | ADDEN | FERR   | OERR   | RX9D   | 57                          |

| TXREG   | EUSART T                                       | ransmit Reg | ister       |             |       |        |        |        | 57                          |

| TXSTA   | CSRC                                           | TX9         | TXEN        | SYNC        | SENDB | BRGH   | TRMT   | TX9D   | 57                          |

| BAUDCON | ABDOVF                                         | RCIDL       | _           | SCKP        | BRG16 | —      | WUE    | ABDEN  | 57                          |

| SPBRGH  | EUSART Baud Rate Generator Register, High Byte |             |             |             |       |        |        |        | 57                          |

| SPBRG   | EUSART E                                       | aud Rate G  | enerator Re | gister, Low | Byte  |        |        |        | 57                          |

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used for synchronous master transmission.

**Note 1:** Reserved in PIC18F2X80 devices; always maintain these bits clear.

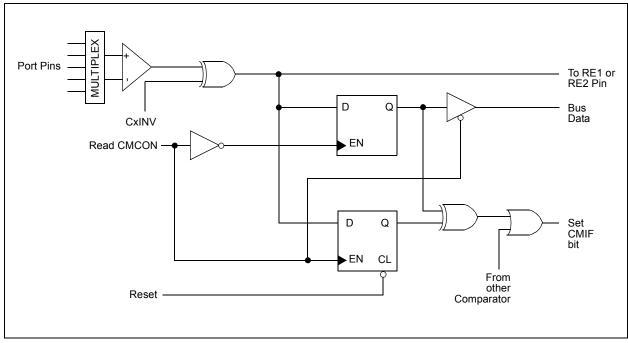

### FIGURE 21-3: COMPARATOR OUTPUT BLOCK DIAGRAM

### 21.6 Comparator Interrupts

The comparator interrupt flag is set whenever there is a change in the output value of either comparator. Software will need to maintain information about the status of the output bits, as read from CMCON<7:6>, to determine the actual change that occurred. The CMIF bit (PIR2<6>) is the Comparator Interrupt Flag. The CMIF bit must be reset by clearing it. Since it is also possible to write a '1' to this register, a simulated interrupt may be initiated.

Both the CMIE bit (PIE2<6>) and the PEIE bit (INTCON<6>) must be set to enable the interrupt. In addition, the GIE bit (INTCON<7>) must also be set. If any of these bits are clear, the interrupt is not enabled, though the CMIF bit will still be set if an interrupt condition occurs.

The user, in the Interrupt Service Routine, can clear the interrupt in the following manner:

- a) Any read or write of CMCON will end the mismatch condition.

- b) Clear flag bit CMIF.

A mismatch condition will continue to set flag bit, CMIF. Reading CMCON will end the mismatch condition and allow flag bit, CMIF, to be cleared.

### 21.7 Comparator Operation During Sleep

When a comparator is active and the device is placed in Sleep mode, the comparator remains active and the interrupt is functional if enabled. This interrupt will wake-up the device from Sleep mode when enabled. While the comparator is powered up, higher Sleep currents than shown in the power-down current specification will occur. Each operational comparator will consume additional current, as shown in the comparator specifications. To minimize power consumption while in Sleep mode, turn off the comparators (CM<2:0> = 111) before entering Sleep. If the device wakes up from Sleep, the contents of the CMCON register are not affected.

### 21.8 Effects of a Reset

A device Reset forces the CMCON register to its Reset state, causing the comparator module to be in the Comparator Reset mode (CM<2:0> = 000). This ensures that all potential inputs are analog inputs. Device current is minimized when analog inputs are present at Reset time. The comparators are powered down during the Reset interval.

| Mada           | R/C-0                                     | R/C-0                                                  | R-0              | R-0       | R-0            | R-0            | R-0            | R-0   |

|----------------|-------------------------------------------|--------------------------------------------------------|------------------|-----------|----------------|----------------|----------------|-------|

| Mode 0         | RXB00VFL                                  | RXB10VFL                                               | TXBO             | TXBP      | RXBP           | TXWARN         | RXWARN         | EWARN |

|                |                                           |                                                        |                  |           |                |                |                |       |

| Mode 1         | R/C-0                                     | R/C-0                                                  | R-0              | R-0       | R-0            | R-0            | R-0            | R-0   |

|                | —                                         | RXBnOVFL                                               | TXB0             | TXBP      | RXBP           | TXWARN         | RXWARN         | EWARN |

|                | R/C-0                                     | R/C-0                                                  | R-0              | R-0       | R-0            | R-0            | R-0            | R-0   |

| Mode 2         | FIFOEMPTY                                 |                                                        | ТХВО             | TXBP      | RXBP           | TXWARN         | RXWARN         | EWARN |

|                | bit 7                                     |                                                        |                  |           |                |                |                | bit   |

| Legend:        |                                           |                                                        | C = Clearab      | le hit    |                |                |                |       |

| R = Read       | lahla hit                                 |                                                        | W = Writable     |           | II = I Inimol  | emented bit, r | n, se pee      |       |

|                | e at POR                                  |                                                        | '1' = Bit is se  |           | '0' = Bit is c |                | x = Bit is unk | nown  |

| bit 7          | Mode 0:                                   |                                                        |                  |           |                |                |                |       |

|                |                                           | Receive Buffe                                          | r 0 Overflow     | bit       |                |                |                |       |

|                |                                           | Buffer 0 overflo<br>Buffer 0 has no                    |                  | ł         |                |                |                |       |

|                | Mode 1:                                   | ata da Danadara (                                      |                  |           |                |                |                |       |

|                | Mode 2:                                   | nted: Read as                                          | 0                |           |                |                |                |       |

|                |                                           | : FIFO Not Em                                          | pty bit          |           |                |                |                |       |

|                | 1 = Receive                               | FIFO is not em<br>FIFO is empty                        |                  |           |                |                |                |       |

| bit 6          | <u>Mode 0:</u>                            | : Receive Buffe                                        | r 1 Overflow     | bit       |                |                |                |       |

|                |                                           | Buffer 1 overflo<br>Buffer 1 has no                    |                  | ł         |                |                |                |       |

|                | <u>Mode 1, 2:</u><br>RXBnOVFL             | : Receive Buffe                                        | r n Overflow     | bit       |                |                |                |       |

|                |                                           | Buffer n has ov<br>Buffer n has no                     |                  | ł         |                |                |                |       |

| bit 5          | TXBO: Tran                                | smitter Bus-Off                                        | bit              |           |                |                |                |       |

|                |                                           | t error counter ><br>t error counter ≤                 |                  |           |                |                |                |       |

| bit 4          | TXBP: Trans                               | smitter Bus Pas                                        | sive bit         |           |                |                |                |       |

|                |                                           | t error counter ><br>t error counter ≤                 |                  |           |                |                |                |       |

| bit 3          |                                           | eiver Bus Passi                                        |                  |           |                |                |                |       |

|                | 1 = Receive                               | error counter >                                        | 127              |           |                |                |                |       |

| bit 2          |                                           | ransmitter War                                         |                  |           |                |                |                |       |

|                | 1 = Transmit                              | t error counter ><br>t error counter ≤                 | • 95             |           |                |                |                |       |

|                |                                           |                                                        |                  |           |                |                |                |       |

| bit 1          | RXWARN: F                                 | Receiver Warnir                                        | iy bit           |           |                |                |                |       |

| bit 1          | 1 <b>= 127</b> ≥ Re                       | Receiver Warnir<br>eceive error cou<br>error counter ≤ | inter > 95       |           |                |                |                |       |

| bit 1<br>bit 0 | 1 = 127 ≥ Re<br>0 = Receive<br>EWARN: Err | eceive error cou                                       | inter > 95<br>95 | WARN bits |                |                |                |       |

## $\label{eq:register24-26:BnSIDL: TX/RX BUFFER n STANDARD IDENTIFIER REGISTERS, \\ LOW BYTE IN RECEIVE MODE [0 \le n \le 5, TXnEN (BSEL0<n>) = 0]^{(1)}$

| R-x   | R-x  | R-x  | R-x | R-x  | U-0 | R-x   | R-x   |

|-------|------|------|-----|------|-----|-------|-------|

| SID2  | SID1 | SID0 | SRR | EXID | —   | EID17 | EID16 |

| bit 7 |      |      |     |      |     |       | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 7-5 | SID<2:0>: Standard Identifier bits (if EXID = 0)                                                                                                                             |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | Extended Identifier bits, EID<20:18> (if EXID = 1).                                                                                                                          |

| bit 4   | SRR: Substitute Remote Transmission Request bit                                                                                                                              |

|         | This bit is always '1' when EXID = 1 or equal to the value of RXRTRRO (BnCON<5>) when EXID = 0.                                                                              |

| bit 3   | EXID: Extended Identifier Enable bit                                                                                                                                         |

|         | <ul> <li>1 = Received message is an extended identifier frame (SID&lt;10:0&gt; are EID&lt;28:18&gt;)</li> <li>0 = Received message is a standard identifier frame</li> </ul> |

| bit 2   | Unimplemented: Read as '0'                                                                                                                                                   |

| bit 1-0 | EID<17:16>: Extended Identifier bits                                                                                                                                         |

|         |                                                                                                                                                                              |

**Note 1:** These registers are available in Mode 1 and 2 only.

## $\label{eq:register24-27:BnSiDL: TX/RX BUFFER n STANDARD IDENTIFIER REGISTERS, \\ LOW BYTE IN RECEIVE MODE [0 \le n \le 5, TXnEN (BSEL0<n>) = 1]^{(1)}$

| R/W-x | R/W-x | R/W-x | U-0 | R/W-x | U-0 | R/W-x | R/W-x |

|-------|-------|-------|-----|-------|-----|-------|-------|

| SID2  | SID1  | SID0  | —   | EXIDE | —   | EID17 | EID16 |

| bit 7 |       |       |     |       |     |       | bit 0 |

| Legend:           |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

| bit 7-5 | SID<2:0>: Standard Identifier bits (if EXIDE = 0)                                                                                                                            |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | Extended Identifier bits, EID<20:18> (if EXIDE = 1).                                                                                                                         |

| bit 4   | Unimplemented: Read as '0'                                                                                                                                                   |

| bit 3   | EXIDE: Extended Identifier Enable bit                                                                                                                                        |

|         | <ul> <li>1 = Received message is an extended identifier frame (SID&lt;10:0&gt; are EID&lt;28:18&gt;)</li> <li>0 = Received message is a standard identifier frame</li> </ul> |

| bit 2   | Unimplemented: Read as '0'                                                                                                                                                   |

| bit 1-0 | EID<17:16>: Extended Identifier bits                                                                                                                                         |

Note 1: These registers are available in Mode 1 and 2 only.

### 24.7.3 ENHANCED FIFO MODE

When configured for Mode 2, two of the dedicated receive buffers in combination with one or more programmable transmit/receive buffers, are used to create a maximum of an 8 buffer deep FIFO buffer. In this mode, there is no direct correlation between filters and receive buffer registers. Any filter that has been enabled can generate an acceptance. When a message has been accepted, it is stored in the next available receive buffer register and an internal Write Pointer is incremented. The FIFO can be a maximum of 8 buffers deep. The entire FIFO must consist of contiguous receive buffers. The FIFO head begins at RXB0 buffer and its tail spans toward B5. The maximum length of the FIFO is limited by the presence or absence of the first transmit buffer starting from B0. If a buffer is configured as a transmit buffer, the FIFO length is reduced accordingly. For instance, if B3 is configured as a transmit buffer, the actual FIFO will consist of RXB0, RXB1, B0, B1 and B2, a total of 5 buffers. If B0 is configured as a transmit buffer, the FIFO length will be 2. If none of the programmable buffers are configured as a transmit buffer, the FIFO will be 8 buffers deep. A system that requires more transmit buffers should try to locate transmit buffers at the very end of B0-B5 buffers to maximize available FIFO length.

When a message is received in FIFO mode, the interrupt flag code bits (EICODE<4:0>) in the CANSTAT register will have a value of '10000', indicating the FIFO has received a message. FIFO Pointer bits, FP<3:0> in the CANCON register, point to the buffer that contains data not yet read. The FIFO Pointer bits, in this sense, serve as the FIFO Read Pointer. The user should use FP bits and read corresponding buffer data. When receive data is no longer needed, the RXFUL bit in the current buffer must be cleared, causing FP<3:0> to be updated by the module.

To determine whether FIFO is empty or not, the user may use the FP<3:0> bits to access the RXFUL bit in the current buffer. If RXFUL is cleared, the FIFO is considered to be empty. If it is set, the FIFO may contain one or more messages. In Mode 2, the module also provides a bit called FIFO High Water Mark (FIFOWM) in the ECANCON register. This bit can be used to cause an interrupt whenever the FIFO contains only one or four empty buffers. The FIFO high water mark interrupt can serve as an early warning to a full FIFO condition.

### 24.7.4 TIME-STAMPING

The CAN module can be programmed to generate a time-stamp for every message that is received. When enabled, the module generates a capture signal for CCP1, which in turn captures the value of either Timer1 or Timer3. This value can be used as the message time-stamp.

To use the time-stamp capability, the CANCAP bit (CIOCON<4>) must be set. This replaces the capture input for CCP1 with the signal generated from the CAN module. In addition, CCP1CON<3:0> must be set to '0011' to enable the CCP Special Event Trigger for CAN events.

### 24.8 Message Acceptance Filters and Masks

The message acceptance filters and masks are used to determine if a message in the Message Assembly Buffer should be loaded into any of the receive buffers. Once a valid message has been received into the MAB, the identifier fields of the message are compared to the filter values. If there is a match, that message will be loaded into the appropriate receive buffer. The filter masks are used to determine which bits in the identifier are examined with the filters. A truth table is shown below in Table 24-2 that indicates how each bit in the identifier is compared to the masks and filters to determine if a message should be loaded into a receive buffer. The mask essentially determines which bits to apply the acceptance filters to. If any mask bit is set to a zero, then that bit will automatically be accepted regardless of the filter bit.

| TABLE 24-2: FILTER/MASK TRUTH TABLE | ABLE 24-2: | FILTER/MASK TRUTH TABLE |

|-------------------------------------|------------|-------------------------|

|-------------------------------------|------------|-------------------------|

| Mask<br>bit n | Filter<br>bit n | Message<br>Identifier<br>bit n001 | Accept or<br>Reject<br>bit n |

|---------------|-----------------|-----------------------------------|------------------------------|

| 0             | Х               | х                                 | Accept                       |

| 1             | 0               | 0                                 | Accept                       |

| 1             | 0               | 1                                 | Reject                       |

| 1             | 1               | 0                                 | Reject                       |

| 1             | 1               | 1                                 | Accept                       |

Legend: x = don't care

In Mode 0, acceptance filters, RXF0 and RXF1, and filter mask, RXM0, are associated with RXB0. Filters, RXF2, RXF3, RXF4 and RXF5, and mask, RXM1, are associated with RXB1.

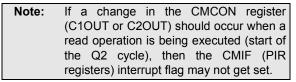

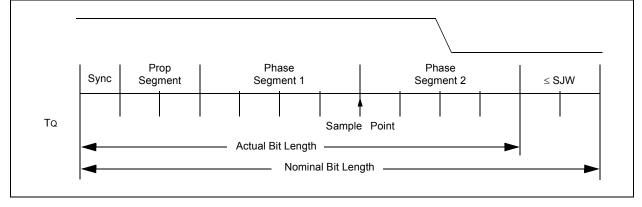

### 24.11 Programming Time Segments

Some requirements for programming of the time segments:

- Prop\_Seg + Phase\_Seg 1  $\geq$  Phase\_Seg 2

- Phase\_Seg  $2 \ge$  Sync Jump Width.

For example, assume that a 125 kHz CAN baud rate is desired, using 20 MHz for Fosc. With a Tosc of 50 ns, a baud rate prescaler value of 04h gives a TQ of 500 ns. To obtain a Nominal Bit Rate of 125 kHz, the Nominal Bit Time must be 8  $\mu$ s or 16 TQ.

Using 1 TQ for the Sync\_Seg, 2 TQ for the Prop\_Seg and 7 TQ for Phase Segment 1 would place the sample point at 10 TQ after the transition. This leaves 6 TQ for Phase Segment 2. By the rules above, the Sync Jump Width could be the maximum of 4 Tq. However, normally a large SJW is only necessary when the clock generation of the different nodes is inaccurate or unstable, such as using ceramic resonators. Typically, an SJW of 1 is enough.

### 24.12 Oscillator Tolerance

As a rule of thumb, the bit timing requirements allow ceramic resonators to be used in applications with transmission rates of up to 125 Kbit/sec. For the full bus speed range of the CAN protocol, a quartz oscillator is required. Refer to ISO11898-1 for oscillator tolerance requirements.

## 25.5 Program Verification and Code Protection

The overall structure of the code protection on the PIC18 Flash devices differs significantly from other  $\text{PIC}^{\texttt{®}}$  devices.

The user program memory is divided into five blocks. One of these is a boot block of 2 Kbytes. The remainder of the memory is divided into four blocks on binary boundaries. Each of the five blocks has three code protection bits associated with them. They are:

- Code-Protect bit (CPn)

- Write-Protect bit (WRTn)

- External Block Table Read bit (EBTRn)

Figure 25-5 shows the program memory organization for 16 and 32-Kbyte devices and the specific code protection bit associated with each block. The actual locations of the bits are summarized in Table 25-3.

#### FIGURE 25-5: CODE-PROTECTED PROGRAM MEMORY FOR PIC18F2480/2580/4480/4580

| Address |                            | MEMORY S                   |                            |                            |                                         |

|---------|----------------------------|----------------------------|----------------------------|----------------------------|-----------------------------------------|

| Range   |                            | bytes<br>580/4580)         |                            | bytes<br>480/4480)         | Block Code Protection<br>Controlled by: |

| BBSIZ   | 0                          | 1                          | 0                          | 1                          |                                         |

| 000000h | Boot Block                 |                            | Boot Block                 |                            |                                         |

| 0007FFh | 1 kW                       | Boot Block                 | 1 kW                       | Boot Block                 | CPB, WRTB, EBRTB                        |

| 000800h |                            | 2 kW                       |                            | 2 kW                       | (Boot Block)                            |

| 000FFFh | Block 0                    |                            | Block 0                    |                            |                                         |

| 001000h | 3 kW                       | Block 0                    | 3 kW                       | Block 0                    | CP0, WRT0, EBRT0                        |

| 001FFFh |                            | 2 kW                       |                            | 2 kW                       | (Block 0)                               |

| 002000h | Block 1<br>4 kW            | Block 1<br>4 kW            | Block 1<br>4 kW            | Block 1<br>4 kW            | CP!, WRT1, EBRT1<br>(Block 1)           |

| 003FFFh |                            |                            |                            |                            |                                         |

| 004000h |                            |                            |                            |                            |                                         |

|         | Block 2<br>4 kW            | Block 2<br>4 kW            |                            |                            | CP2, WRT2, EBRT2<br>(Block 2)           |

| 005FFFh |                            |                            |                            |                            |                                         |

| 006000h |                            |                            | •                          |                            |                                         |

|         | Block 3<br>4 kW            | Block 3<br>4 kW            |                            |                            | CP3, WRT3, EBTR3<br>(Block 3)           |

| 007FFFh |                            |                            |                            |                            |                                         |

| 008000h | Unimplemented<br>Read '0's | Unimplemented<br>Read '0's | Unimplemented<br>Read '0's | Unimplemented<br>Read '0's | (Unimplemented Memory Space)            |

| 1FFFFFh |                            |                            |                            |                            |                                         |

Bit Set f

BSF

| BRA                                                                                                                                                                                                                           | BRA Unconditional Branch |                     |                     |                 |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|---------------------|---------------------|-----------------|--|--|--|

| Synta                                                                                                                                                                                                                         | ax:                      | BRA n               |                     |                 |  |  |  |

| Oper                                                                                                                                                                                                                          | ands:                    | -1024 ≤ n ≤         | 1023                |                 |  |  |  |

| Oper                                                                                                                                                                                                                          | ation:                   | (PC) + 2 + 2        | $2n \rightarrow PC$ |                 |  |  |  |

| Statu                                                                                                                                                                                                                         | s Affected:              | None                |                     |                 |  |  |  |

| Enco                                                                                                                                                                                                                          | ding:                    | 1101                | 0nnn nn             | nn nnnn         |  |  |  |

| Description: Add the 2's complement number '2n' to<br>the PC. Since the PC will have<br>incremented to fetch the next<br>instruction, the new address will be<br>PC + 2 + 2n. This instruction is a<br>two-cycle instruction. |                          |                     |                     |                 |  |  |  |

| Word                                                                                                                                                                                                                          | ls:                      | 1                   | 1                   |                 |  |  |  |

| Cycle                                                                                                                                                                                                                         | es:                      | 2                   | 2                   |                 |  |  |  |

| QC                                                                                                                                                                                                                            | ycle Activity:           |                     |                     |                 |  |  |  |

|                                                                                                                                                                                                                               | Q1                       | Q2                  | Q3                  | Q4              |  |  |  |

|                                                                                                                                                                                                                               | Decode                   | Read literal<br>'n' | Process<br>Data     | Write to PC     |  |  |  |

|                                                                                                                                                                                                                               | No<br>operation          | No<br>operation     | No<br>operation     | No<br>operation |  |  |  |

| Example:HEREBRAJumpBefore InstructionPC=address(HERE)After InstructionPC=address(Jump)                                                                                                                                        |                          |                     |                     |                 |  |  |  |

| -                           |                                                                                                                                                                                                                                                                                                                                            |              |         |             |  |  |  |

|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|---------|-------------|--|--|--|

| Syntax:                     | BSF f, b                                                                                                                                                                                                                                                                                                                                   | {,a}         |         |             |  |  |  |

| Operands:                   | $0 \le f \le 255$<br>$0 \le b \le 7$<br>$a \in [0,1]$                                                                                                                                                                                                                                                                                      |              |         |             |  |  |  |

| Operation:                  | $1 \rightarrow \text{f}$                                                                                                                                                                                                                                                                                                                   |              |         |             |  |  |  |

| Status Affected:            | None                                                                                                                                                                                                                                                                                                                                       |              |         |             |  |  |  |

| Encoding:                   | 1000                                                                                                                                                                                                                                                                                                                                       | bbba         | ffff    | ffff        |  |  |  |

| Description:                | Bit 'b' in re                                                                                                                                                                                                                                                                                                                              | gister 'f' i | s set.  |             |  |  |  |

|                             | If 'a' is '0', the Access Bank is sele<br>If 'a' is '1', the BSR is used to select<br>GPR bank.<br>If 'a' is '0' and the extended instruct<br>set is enabled, this instruction oper<br>in Indexed Literal Offset Addressin<br>mode whenever $f \le 95$ (5Fh). See<br>Section 26.2.3 "Byte-Oriented ar<br>Bit-Oriented Instructions in Inde |              |         |             |  |  |  |

| Words:                      | Literal Off                                                                                                                                                                                                                                                                                                                                | Set mout     |         | 2110.       |  |  |  |

| Cycles:                     | 1                                                                                                                                                                                                                                                                                                                                          |              |         |             |  |  |  |

| Q Cycle Activity:           |                                                                                                                                                                                                                                                                                                                                            |              |         |             |  |  |  |

| Q1                          | Q2                                                                                                                                                                                                                                                                                                                                         | Q3           | 5       | Q4          |  |  |  |

| Decode                      | Read                                                                                                                                                                                                                                                                                                                                       | Proce        | SS      | Write       |  |  |  |

|                             | register 'f'                                                                                                                                                                                                                                                                                                                               | Data         | a re    | egister 'f' |  |  |  |

| Example:<br>Before Instruct |                                                                                                                                                                                                                                                                                                                                            | FLAG_RE      | G, 7, 1 | -           |  |  |  |

| Belore instruction          |                                                                                                                                                                                                                                                                                                                                            |              |         |             |  |  |  |

FLAG\_REG = 0Ah After Instruction FLAG\_REG = 8Ah

| GOTO                    | Uncondit                  | ional Branc            | h                                         | INCF                                  | Incremen                                                    | t f                                                                                               |                                                |

|-------------------------|---------------------------|------------------------|-------------------------------------------|---------------------------------------|-------------------------------------------------------------|---------------------------------------------------------------------------------------------------|------------------------------------------------|

| Syntax:                 | GOTO k                    |                        |                                           | Syntax:                               | INCF f{,c                                                   | l {,a}}                                                                                           |                                                |

| Operands:               | $0 \le k \le 104$         | 8575                   |                                           | Operands:                             | $0 \leq f \leq 255$                                         |                                                                                                   |                                                |

| Operation:              | $k \rightarrow PC<20$     | ):1>                   |                                           |                                       | d ∈ [0,1]                                                   |                                                                                                   |                                                |

| Status Affected:        | None                      |                        |                                           | Operation:                            | $a \in [0,1]$<br>(f) + 1 $\rightarrow de$                   | het                                                                                               |                                                |

| Encoding:               |                           |                        |                                           | Status Affected:                      | $(1) \neq 1 \rightarrow 0$<br>C, DC, N, (                   |                                                                                                   |                                                |

| 1st word (k<7:0>)       | 1110                      | /                      | kk kkkk <sub>0</sub>                      |                                       | <b></b>                                                     |                                                                                                   |                                                |

| 2nd word(k<19:8>        | ) 1111                    | k <sub>19</sub> kkk kk | kk kkkk <sub>8</sub>                      | Encoding:<br>Description:             | 0010                                                        | 10da ff                                                                                           | ff ffff                                        |

| Description:            | anywhere w<br>2-Mbyte me  |                        |                                           |                                       | incremente<br>placed in W<br>placed bac<br>lf 'a' is '0', t | d. If 'd' is '0', t<br>/. If 'd' is '1', tf<br>k in register 'f'<br>he Access Ba<br>he BSR is use | the result is<br>ne result is<br>nk is selecte |

| Words:                  | 2                         |                        |                                           |                                       |                                                             | nd the extend                                                                                     | ed instruction                                 |