#### Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 40MHz                                                                     |

| Connectivity               | CANbus, I <sup>2</sup> C, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                               |

| Number of I/O              | 36                                                                        |

| Program Memory Size        | 32KB (16K x 16)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 1.5К х 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                 |

| Data Converters            | A/D 11x10b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Through Hole                                                              |

| Package / Case             | 40-DIP (0.600", 15.24mm)                                                  |

| Supplier Device Package    | 40-PDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf4580-i-p |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

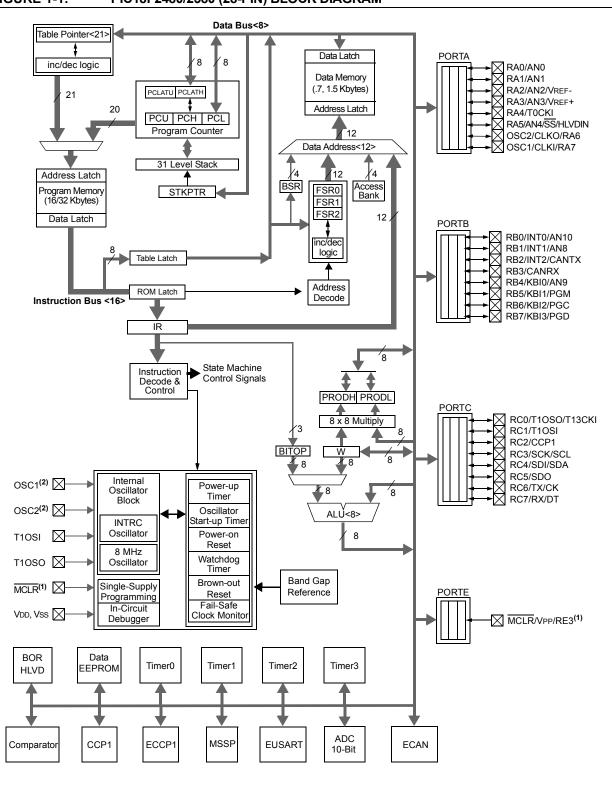

### FIGURE 1-1: PIC18F2480/2580 (28-PIN) BLOCK DIAGRAM

Note 1: RE3 is multiplexed with MCLR and is only available when the MCLR Resets are disabled.

2: OSC1/CLKI and OSC2/CLKO are only available in select oscillator modes and when these pins are not being used as digital I/O. Refer to Section 3.0 "Oscillator Configurations" for additional information.

### 3.7.1 OSCILLATOR CONTROL REGISTER

The OSCCON register (Register 3-2) controls several aspects of the device clock's operation, both in full-power operation and in power-managed modes.

The System Clock Select bits, SCS<1:0>, select the clock source. The available clock sources are the primary clock (defined by the FOSC<3:0> Configuration bits), the secondary clock (Timer1 oscillator) and the internal oscillator block. The clock source changes immediately after one or more of the bits is written to, following a brief clock transition interval. The SCS bits are cleared on all forms of Reset.

The Internal Oscillator Frequency Select bits, IRCF<2:0>, select the frequency output of the internal oscillator block to drive the device clock. The choices are the INTRC source, the INTOSC source (8 MHz) or one of the frequencies derived from the INTOSC post-scaler (31 kHz to 4 MHz). If the internal oscillator block is supplying the device clock, changing the states of these bits will have an immediate change on the internal oscillator's output. On device Resets, the default output frequency of the internal oscillator block is set at 1 MHz.

When an output frequency of 31 kHz is selected (IRCF<2:0> = 000), users may choose which internal oscillator acts as the source. This is done with the INTSRC bit in the OSCTUNE register (OSCTUNE<7>). Setting this bit selects INTOSC as a 31.25 kHz clock source by enabling the divide-by-256 output of the INTOSC postscaler. Clearing INTSRC selects INTRC (nominally 31 kHz) as the clock source.

This option allows users to select the tunable and more precise INTOSC as a clock source, while maintaining power savings with a very low clock speed. Regardless of the setting of INTSRC, INTRC always remains the clock source for features such as the Watchdog Timer and the Fail-Safe Clock Monitor.

The OSTS, IOFS and T1RUN bits indicate which clock source is currently providing the device clock. The OSTS bit indicates that the Oscillator Start-up Timer (OST) has timed out and the primary clock is providing the device clock in primary clock modes. The IOFS bit indicates when the internal oscillator block has stabilized and is providing the device clock in RC Clock modes. The T1RUN bit (T1CON<6>) indicates when the Timer1 oscillator is providing the device clock in secondary clock modes. In power-managed modes, only one of these three bits will be set at any time. If none of these bits are set, the INTRC is providing the clock or the internal oscillator block has just started and is not yet stable. The IDLEN bit determines if the device goes into Sleep mode or one of the Idle modes when the SLEEP instruction is executed.

The use of the flag and control bits in the OSCCON register is discussed in more detail in **Section 4.0** "Power-Managed Modes".

- Note 1: The Timer1 oscillator must be enabled to select the secondary clock source. The Timer1 oscillator is enabled by setting the T1OSCEN bit in the Timer1 Control register (T1CON<3>). If the Timer1 oscillator is not enabled, then any attempt to select a secondary clock source when executing a SLEEP instruction will be ignored.

- 2: It is recommended that the Timer1 oscillator be operating and stable before executing the SLEEP instruction, or a very long delay may occur while the Timer1 oscillator starts.

### 3.7.2 OSCILLATOR TRANSITIONS

PIC18F2480/2580/4480/4580 devices contain circuitry to prevent clock "glitches" when switching between clock sources. A short pause in the device clock occurs during the clock switch. The length of this pause is the sum of two cycles of the old clock source and three to four cycles of the new clock source. This formula assumes that the new clock source is stable.

Clock transitions are discussed in greater detail in **Section 4.1.2 "Entering Power-Managed Modes"**.

### 5.4 Brown-out Reset (BOR)

PIC18F2480/2580/4480/4580 devices implement a BOR circuit that provides the user with a number of configuration and power-saving options. The BOR is controlled by the BORV<1:0> and BOREN<1:0> Configuration bits. There are a total of four BOR configurations which are summarized in Table 5-1.

The BOR threshold is set by the BORV<1:0> bits. If BOR is enabled (any values of BOREN<1:0>, except '00'), any drop of VDD below VBOR (parameter D005) for greater than TBOR (parameter 35) will reset the device. A Reset may or may not occur if VDD falls below VBOR for less than TBOR. The chip will remain in Brown-out Reset until VDD rises above VBOR.

If the Power-up Timer is enabled, it will be invoked after VDD rises above VBOR; it then will keep the chip in Reset for an additional time delay, TPWRT (parameter 33). If VDD drops below VBOR while the Power-up Timer is running, the chip will go back into a Brown-out Reset and the Power-up Timer will be initialized. Once VDD rises above VBOR, the Power-up Timer will execute the additional time delay.

BOR and the Power-on Timer (PWRT) are independently configured. Enabling a Brown-out Reset does not automatically enable the PWRT.

### 5.4.1 SOFTWARE ENABLED BOR

When BOREN<1:0> = 01, the BOR can be enabled or disabled by the user in software. This is done with the control bit, SBOREN (RCON<6>). Setting SBOREN enables the BOR to function as previously described. Clearing SBOREN disables the BOR entirely. The SBOREN bit operates only in this mode; otherwise it is read as '0'.

Placing the BOR under software control gives the user the additional flexibility of tailoring the application to its environment without having to reprogram the device to change BOR configuration. It also allows the user to tailor device power consumption in software by eliminating the incremental current that the BOR consumes. While the BOR current is typically very small, it may have some impact in low-power applications.

| Note: | Even when BOR is under software control,<br>the Brown-out Reset voltage level is still |

|-------|----------------------------------------------------------------------------------------|

|       | set by the BORV<1:0> Configuration bits.<br>It cannot be changed in software.          |

### 5.4.2 DETECTING BOR

When Brown-out Reset is enabled, the BOR bit always resets to '0' on any Brown-out Reset or Power-on Reset event. This makes it difficult to determine if a Brown-out Reset event has occurred just by reading the state of BOR alone. A more reliable method is to simultaneously check the state of both POR and BOR. This assumes that the POR bit is reset to '1' in software immediately after any Power-on Reset event. IF BOR is '0' while POR is '1', it can be reliably assumed that a Brown-out Reset event has occurred.

### 5.4.3 DISABLING BOR IN SLEEP MODE

When BOREN<1:0> = 10, the BOR remains under hardware control and operates as previously described. Whenever the device enters Sleep mode, however, the BOR is automatically disabled. When the device returns to any other operating mode, BOR is automatically re-enabled.

This mode allows for applications to recover from brown-out situations, while actively executing code, when the device requires BOR protection the most. At the same time, it saves additional power in Sleep mode by eliminating the small incremental BOR current.

| BOR Con | figuration | Status of           |                                                                                    |

|---------|------------|---------------------|------------------------------------------------------------------------------------|

| BOREN1  | BOREN0     | SBOREN<br>(RCON<6>) | BOR Operation                                                                      |

| 0       | 0          | Unavailable         | BOR disabled; must be enabled by reprogramming the Configuration bits.             |

| 0       | 1          | Available           | BOR enabled in software; operation controlled by SBOREN.                           |

| 1       | 0          | Unavailable         | BOR enabled in hardware in Run and Idle modes, disabled during Sleep mode.         |

| 1       | 1          | Unavailable         | BOR enabled in hardware; must be disabled by reprogramming the Configuration bits. |

TABLE 5-1: BOR CONFIGURATIONS

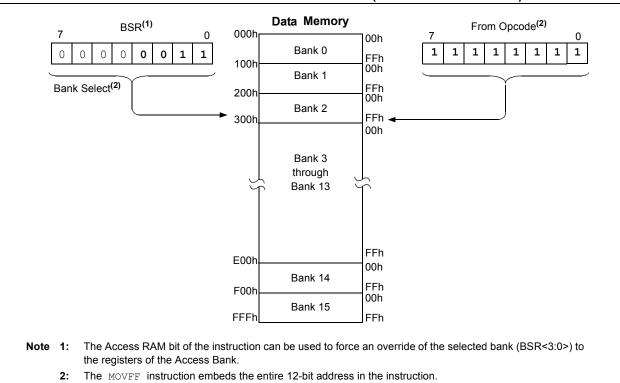

### FIGURE 6-7: USE OF THE BANK SELECT REGISTER (DIRECT ADDRESSING)

### 6.3.2 ACCESS BANK

While the use of the BSR with an embedded 8-bit address allows users to address the entire range of data memory, it also means that the user must always ensure that the correct bank is selected. Otherwise, data may be read from or written to the wrong location. This can be disastrous if a GPR is the intended target of an operation, but an SFR is written to instead. Verifying and/or changing the BSR for each read or write to data memory can become very inefficient.

To streamline access for the most commonly used data memory locations, the data memory is configured with an Access Bank, which allows users to access a mapped block of memory without specifying a BSR. The Access Bank consists of the first 128 bytes of memory (00h-7Fh) in Bank 0 and the last 128 bytes of memory (80h-FFh) in Block 15. The lower half is known as the "Access RAM" and is composed of GPRs. The upper half is where the device's SFRs are mapped. These two areas are mapped contiguously in the Access Bank and can be addressed in a linear fashion by an 8-bit address (Figure 6-6).

The Access Bank is used by core PIC18 instructions that include the Access RAM bit (the 'a' parameter in the instruction). When 'a' is equal to '1', the instruction uses the BSR and the 8-bit address included in the opcode for the data memory address. When 'a' is '0'

however, the instruction is forced to use the Access Bank address map; the current value of the BSR is ignored entirely.

Using this "forced" addressing allows the instruction to operate on a data address in a single cycle, without updating the BSR first. For 8-bit addresses of 80h and above, this means that users can evaluate and operate on SFRs more efficiently. The Access RAM below 80h is a good place for data values that the user might need to access rapidly, such as immediate computational results or common program variables. Access RAM also allows for faster and more code efficient context saving and switching of variables.

The mapping of the Access Bank is slightly different when the extended instruction set is enabled (XINST Configuration bit = 1). This is discussed in more detail in Section 6.6.3 "Mapping the Access Bank in Indexed Literal Offset Mode".

### 6.3.3 GENERAL PURPOSE REGISTER FILE

PIC18 devices may have banked memory in the GPR area. This is data RAM, which is available for use by all instructions. GPRs start at the bottom of Bank 0 (address 000h) and grow upwards towards the bottom of the SFR area. GPRs are not initialized by a Power-on Reset and are unchanged on all other Resets.

| File Name               | Bit 7           | Bit 6                        | Bit 5               | Bit 4               | Bit 3                 | Bit 2                          | Bit 1                 | Bit 0                 | Value on POR, BOR | Details on<br>Page: |

|-------------------------|-----------------|------------------------------|---------------------|---------------------|-----------------------|--------------------------------|-----------------------|-----------------------|-------------------|---------------------|

| FSR2H                   | _               | _                            | _                   | —                   | Indirect Data M       | lemory Address                 | Pointer 2 High        |                       | xxxx              | 56, 96              |

| FSR2L                   | Indirect Data N | Memory Addres                | ss Pointer 2 L      | ow Byte             |                       |                                |                       |                       | XXXX XXXX         | 56, 96              |

| STATUS                  | —               | —                            | —                   | Ν                   | OV                    | Z                              | DC                    | С                     | x xxxx            | 56, 94              |

| TMR0H                   | Timer0 Regist   | er High Byte                 |                     |                     |                       |                                | •                     | •                     | 0000 0000         | 56, 153             |

| TMR0L                   | Timer0 Regist   | er Low Byte                  |                     |                     |                       |                                |                       |                       | XXXX XXXX         | 56, 153             |

| TOCON                   | TMR0ON          | T08BIT                       | TOCS                | T0SE                | PSA                   | T0PS2                          | T0PS1                 | T0PS0                 | 1111 1111         | 56, 153             |

| OSCCON                  | IDLEN           | IRCF2                        | IRCF1               | IRCF0               | OSTS                  | IOFS                           | SCS1                  | SCS0                  | 0000 q000         | 36, 56              |

| HLVDCON                 | VDIRMAG         | _                            | IRVST               | HLVDEN              | HLVDL3                | HLVDL2                         | HLVDL1                | HLVDL0                | 0-00 0101         | 56, 273             |

| WDTCON                  | —               | -                            | —                   | _                   | —                     | —                              | —                     | SWDTEN                | 0                 | 56, 359             |

| RCON                    | IPEN            | SBOREN <sup>(2)</sup>        | _                   | RI                  | TO                    | PD                             | POR                   | BOR                   | 0q-1 11q0         | 56, 133             |

| TMR1H                   | Timer1 Regist   | er High Byte                 |                     |                     |                       |                                | •                     | •                     | XXXX XXXX         | 56, 159             |

| TMR1L                   | Timer1 Regist   | er Low Byte                  |                     |                     |                       |                                |                       |                       | 0000 0000         | 56, 159             |

| T1CON                   | RD16            | T1RUN                        | T1CKPS1             | T1CKPS0             | T1OSCEN               | T1SYNC                         | TMR1CS                | TMR10N                | 0000 0000         | 56, 155             |

| TMR2                    | Timer2 Regist   | er                           |                     |                     |                       |                                |                       |                       | 1111 1111         | 56, 162             |

| PR2                     | Timer2 Period   | Register                     |                     |                     |                       |                                |                       |                       | -000 0000         | 56, 159             |

| T2CON                   | —               | T2OUTPS3                     | T2OUTPS2            | T2OUTPS1            | T2OUTPS0              | TMR2ON                         | T2CKPS1               | T2CKPS0               | -000 0000         | 56, 161             |

| SSPBUF                  | MSSP Receiv     | e Buffer/Transr              | nit Register        |                     |                       |                                |                       |                       | XXXX XXXX         | 56, 199             |

| SSPADD                  | MSSP Addres     | s Register in I <sup>2</sup> | C Slave Mod         | e. MSSP Bau         | d Rate Reload I       | Register in I <sup>2</sup> C M | laster Mode.          |                       | 0000 0000         | 56, 199             |

| SSPSTAT                 | SMP             | CKE                          | D/A                 | Р                   | S                     | R/W                            | UA                    | BF                    | 0000 0000         | 56, 201             |

| SSPCON1                 | WCOL            | SSPOV                        | SSPEN               | CKP                 | SSPM3                 | SSPM2                          | SSPM1                 | SSPM0                 | 0000 0000         | 56, 202             |

| SSPCON2                 | GCEN            | ACKSTAT                      | ACKDT               | ACKEN               | RCEN                  | PEN                            | RSEN                  | SEN                   | 0000 0000         | 56, 203             |

| ADRESH                  | A/D Result Re   | gister High Byt              | e                   |                     |                       |                                |                       |                       | XXXX XXXX         | 56, 262             |

| ADRESL                  | A/D Result Re   | gister Low Byte              | е                   |                     |                       |                                |                       |                       | XXXX XXXX         | 56, 262             |

| ADCON0                  | _               | _                            | CHS3                | CHS2                | CHS1                  | CHS0                           | GO/DONE               | ADON                  | 00 0000           | 56, 253             |

| ADCON1                  | _               | _                            | VCFG1               | VCFG0               | PCFG3                 | PCFG2                          | PCFG1                 | PCFG0                 | 00 0qqq           | 56, 254             |

| ADCON2                  | ADFM            | _                            | ACQT2               | ACQT1               | ACQT0                 | ADCS2                          | ADCS1                 | ADCS0                 | 0-00 0000         | 57, 255             |

| CCPR1H                  | Capture/Comp    | are/PWM Reg                  | ister 1 High B      | yte                 |                       |                                |                       |                       | XXXX XXXX         | 57, 172             |

| CCPR1L                  | Capture/Comp    | oare/PWM Reg                 | ister 1 Low B       | yte                 |                       |                                |                       |                       | XXXX XXXX         | 57, 172             |

| CCP1CON                 | _               | _                            | DC1B1               | DC1B0               | CCP1M3                | CCP1M2                         | CCP1M1                | CCP1M0                | 00 0000           | 57, 167             |

| ECCPR1H <sup>(9)</sup>  | Enhanced Ca     | pture/Compare                | /PWM Regist         | er 1 High Byte      | 9                     |                                |                       |                       | XXXX XXXX         | 57, 171             |

| ECCPR1L <sup>(9)</sup>  |                 | pture/Compare                |                     |                     |                       |                                |                       |                       | XXXX XXXX         | 57, 171             |

| ECCP1CON <sup>(9)</sup> | EPWM1M1         | EPWM1M0                      | EDC1B1              | EDC1B0              | ECCP1M3               | ECCP1M2                        | ECCP1M1               | ECCP1M0               | 0000 0000         | 57, 172             |

| BAUDCON                 | ABDOVF          | RCIDL                        | _                   | SCKP                | BRG16                 | _                              | WUE                   | ABDEN                 | 01-0 0000         | 57, 234             |

| ECCP1DEL <sup>(9)</sup> | PRSEN           | PDC6 <sup>(3)</sup>          | PDC5 <sup>(3)</sup> | PDC4 <sup>(3)</sup> | PDC3 <sup>(3)</sup>   | PDC2 <sup>(3)</sup>            | PDC1 <sup>(3)</sup>   | PDC0 <sup>(3)</sup>   | 0000 0000         | 57, 187             |

| ECCP1AS <sup>(9)</sup>  | ECCPASE         | ECCPAS2                      | ECCPAS1             | ECCPAS0             | PSSAC1                | PSSAC0                         | PSSBD1 <sup>(3)</sup> | PSSBD0 <sup>(3)</sup> | 0000 0000         | 57, 187             |

| CVRCON <sup>(9)</sup>   | CVREN           | CVROE                        | CVRR                | CVRSS               | CVR3                  | CVR2                           | CVR1                  | CVR0                  | 0000 0000         | 57, 269             |

| CMCON <sup>(9)</sup>    | C2OUT           | C1OUT                        | C2INV               | C1INV               | CIS                   | CM2                            | CM1                   | CM0                   | 0000 0000         | 57, 263             |

| TMR3H                   | Timer3 Regist   | er High Byte                 |                     |                     |                       |                                |                       |                       | XXXX XXXX         | 57, 165             |

| TMR3L                   | Timer3 Regist   | er Low Byte                  |                     |                     |                       |                                |                       |                       | XXXX XXXX         | 57, 165             |

| T3CON                   | RD16            | T3ECCP1 <sup>(9)</sup>       | T3CKPS1             | T3CKPS0             | T3CCP1 <sup>(9)</sup> | T3SYNC                         | TMR3CS                | TMR3ON                | 0000 0000         | 57, 165             |

### TABLE 6-2:REGISTER FILE SUMMARY (PIC18F2480/2580/4480/4580) (CONTINUED)

Note 1: Bit 21 of the PC is only available in Test mode and Serial Programming modes.

2: The SBOREN bit is only available when CONFIG2L<1:0> = 01; otherwise, it is disabled and reads as '0'. See Section 5.4 "Brown-out Reset (BOR)".

3: These registers and/or bits are not implemented on PIC18F2X80 devices and are read as '0'. Reset values are shown for PIC18F4X80 devices; individual unimplemented bits should be interpreted as '-'.

4: The PLLEN bit is only available in specific oscillator configuration; otherwise, it is disabled and reads as '0'. See Section 3.6.4 "PLL in INTOSC Modes".

5: The RE3 bit is only available when Master Clear Reset is disabled (CONFIG3H<7> = 0); otherwise, RE3 reads as '0'. This bit is read-only.

6: RA6/RA7 and their associated latch and direction bits are individually configured as port pins based on various primary oscillator modes. When disabled, these bits read as '0'.

7: CAN bits have multiple functions depending on the selected mode of the CAN module.

8: This register reads all '0's until the ECAN™ technology is set up in Mode 1 or Mode 2.

9: These registers are available on PIC18F4X80 devices only.

### 10.4 IPR Registers

The IPR registers contain the individual priority bits for the peripheral interrupts. Due to the number of peripheral interrupt sources, there are two Peripheral Interrupt Priority registers (IPR1, IPR2). Using the priority bits requires that the Interrupt Priority Enable (IPEN) bit be set.

### REGISTER 10-10: IPR1: PERIPHERAL INTERRUPT PRIORITY REGISTER 1

| R/W-1                | R/W-1                          | R/W-1            | R/W-1            | R/W-1             | R/W-1           | R/W-1           | R/W-1  |

|----------------------|--------------------------------|------------------|------------------|-------------------|-----------------|-----------------|--------|

| PSPIP <sup>(1)</sup> | ADIP                           | RCIP             | TXIP             | SSPIP             | CCP1IP          | TMR2IP          | TMR1IP |

| bit 7                |                                |                  |                  |                   |                 |                 | bit 0  |

| Legend:              |                                |                  |                  |                   |                 |                 |        |

| R = Readable         | e bit                          | W = Writable     | bit              | U = Unimpler      | nented bit, rea | d as '0'        |        |

| -n = Value at        |                                | '1' = Bit is set |                  | '0' = Bit is cle  |                 | x = Bit is unkr | nown   |

| 1.1.7                |                                |                  |                  |                   | (1)             |                 |        |

| bit 7                |                                | lel Slave Port F | Read/write Int   | errupt Priority i | DIT             |                 |        |

|                      | 1 = High prio<br>0 = Low prior |                  |                  |                   |                 |                 |        |

| bit 6                | •                              | onverter Interru | pt Priority bit  |                   |                 |                 |        |

|                      | 1 = High prio                  |                  |                  |                   |                 |                 |        |

|                      | 0 = Low prior                  | rity             |                  |                   |                 |                 |        |

| bit 5                |                                | RT Receive Int   | errupt Priority  | bit               |                 |                 |        |

|                      | 1 = High prio<br>0 = Low prior | •                |                  |                   |                 |                 |        |

| bit 4                |                                | RT Transmit Int  | errupt Prioritv  | bit               |                 |                 |        |

|                      | 1 = High prio                  |                  |                  |                   |                 |                 |        |

|                      | 0 = Low prior                  |                  |                  |                   |                 |                 |        |

| bit 3                | SSPIP: Maste                   | er Synchronous   | Serial Port I    | nterrupt Priority | / bit           |                 |        |

|                      | 1 = High prio                  |                  |                  |                   |                 |                 |        |

|                      | 0 = Low prior                  | •                | .,,              |                   |                 |                 |        |

| bit 2                |                                | P1 Interrupt Pri | ority bit        |                   |                 |                 |        |

|                      | 1 = High prio<br>0 = Low prior |                  |                  |                   |                 |                 |        |

| bit 1                |                                | R2 to PR2 Mate   | ch Interrupt P   | riority bit       |                 |                 |        |

|                      | 1 = High prio                  |                  |                  | 5                 |                 |                 |        |

|                      | 0 = Low prior                  | rity             |                  |                   |                 |                 |        |

| bit 0                |                                | R1 Overflow In   | terrupt Priority | / bit             |                 |                 |        |

|                      | 1 = High prio                  |                  |                  |                   |                 |                 |        |

|                      | 0 = Low prior                  | nty              |                  |                   |                 |                 |        |

**Note 1:** This bit is reserved on PIC18F2X80 devices; always maintain this bit set.

| Mode 0       | R/W-1                                                   | R/W-1                                          | R/W-1          | R/W-1           | R/W-1                          | R/W-1                          | R/W-1           | R/W-1             |

|--------------|---------------------------------------------------------|------------------------------------------------|----------------|-----------------|--------------------------------|--------------------------------|-----------------|-------------------|

| Mode U       | IRXIP                                                   | WAKIP                                          | ERRIP          | TXB2IP          | TXB1IP <sup>(1)</sup>          | TXB0IP <sup>(1)</sup>          | RXB1IP          | RXB0IP            |

|              |                                                         |                                                |                |                 |                                |                                |                 |                   |

| Mode 1,2     | R/W-1                                                   | R/W-1<br>WAKIP                                 | R/W-1<br>ERRIP | R/W-1<br>TXBnIP | R/W-1<br>TXB1IP <sup>(1)</sup> | R/W-1<br>TXB0IP <sup>(1)</sup> | R/W-1<br>RXBnIP | R/W-1<br>FIFOWMIP |

|              | bit 7                                                   | WARIP                                          | ERRIP          | TADIIP          | IXBIIP()                       | I ADUIP( /                     | KADIIIP         | bit (             |

|              | bit i                                                   |                                                |                |                 |                                |                                |                 | bit (             |

| Legend:      |                                                         |                                                |                |                 |                                |                                |                 |                   |

| R = Readat   | ole bit                                                 |                                                | W = Writabl    | e bit           | U = Unimple                    | mented bit, r                  | ead as '0'      |                   |

| -n = Value a | at POR                                                  |                                                | '1' = Bit is s | et              | '0' = Bit is cl                | eared                          | x = Bit is un   | known             |

| bit 7        | IRXIP: CAN<br>1 = High pric<br>0 = Low pric             |                                                | ived Messag    | e Interrupt P   | Priority bit                   |                                |                 |                   |

| bit 6        | WAKIP: CA<br>1 = High prid<br>0 = Low prid              | •                                              | v Wake-up In   | terrupt Priori  | ity bit                        |                                |                 |                   |

| bit 5        | <b>ERRIP:</b> CAN<br>1 = High pric<br>0 = Low pric      |                                                | terrupt Priori | ty bit          |                                |                                |                 |                   |

| bit 4        |                                                         |                                                | uffer 2 Interr | upt Priority b  | bit                            |                                |                 |                   |

|              | When CAN                                                | <u>is in Mode 1 (</u><br>N Transmit E<br>ority |                | ot Priority bit |                                |                                |                 |                   |

| bit 3        | <b>TXB1IP:</b> CA<br>1 = High pric<br>0 = Low pric      | •                                              | uffer 1 Interr | upt Priority t  | <sub>Dit</sub> (1)             |                                |                 |                   |

| bit 2        | <b>TXB0IP:</b> CA<br>1 = High pric<br>0 = Low pric      |                                                | uffer 0 Interr | upt Priority t  | bit <sup>(1)</sup>             |                                |                 |                   |

| bit 1        | When CAN                                                | <u>is in Mode 0:</u><br>AN Receive B<br>ority  | uffer 1 Intern | upt Priority b  | it                             |                                |                 |                   |

|              |                                                         |                                                |                | ots Priority bi | t                              |                                |                 |                   |

| bit 0        | RXB0IP: CA<br>1 = High prid<br>0 = Low prid<br>When CAN |                                                |                | upt Priority b  | it                             |                                |                 |                   |

|              |                                                         |                                                | nark Interrup  | t Priority bit  |                                |                                |                 |                   |

### REGISTER 10-12: IPR3: PERIPHERAL INTERRUPT PRIORITY REGISTER 3

Note 1: In CAN Mode 1 and 2, these bits are forced to '0'.

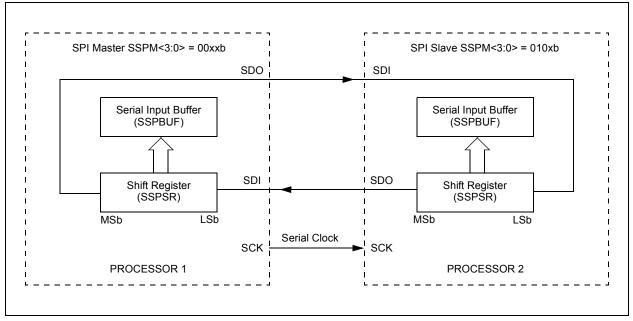

### 18.3.3 ENABLING SPI I/O

To enable the serial port, MSSP Enable bit, SSPEN (SSPCON1<5>), must be set. To reset or reconfigure SPI mode, clear the SSPEN bit, reinitialize the SSPCON registers and then set the SSPEN bit. This configures the SDI, SDO, SCK and SS pins as serial port pins. For the pins to behave as the serial port function, some must have their data direction bits (in the TRIS register) appropriately programmed as follows:

- · SDI is automatically controlled by the SPI module

- SDO must have TRISC<5> bit cleared

- SCK (Master mode) must have TRISC<3> bit cleared

- SCK (Slave mode) must have TRISC<3> bit set

- SS must have TRISF<7> bit set

Any serial port function that is not desired may be overridden by programming the corresponding Data Direction (TRIS) register to the opposite value.

### 18.3.4 TYPICAL CONNECTION

Figure 18-2 shows a typical connection between two microcontrollers. The master controller (Processor 1) initiates the data transfer by sending the SCK signal. Data is shifted out of both shift registers on their programmed clock edge and latched on the opposite edge of the clock. Both processors should be programmed to the same Clock Polarity (CKP), then both controllers would send and receive data at the same time. Whether the data is meaningful (or dummy data) depends on the application software. This leads to three scenarios for data transmission:

- · Master sends data Slave sends dummy data

- · Master sends data Slave sends data

- · Master sends dummy data Slave sends data

- Note: When the module is enabled and in Master mode (CKE, SSPSTAT<6> = 1), a small glitch of approximately half a Tcy may be seen on the SCK pin. To resolve this, keep the SCK pin as an input while setting SPEN. Then, configure the SCK pin as an output (TRISC<3> = 0).

### FIGURE 18-2: SPI MASTER/SLAVE CONNECTION

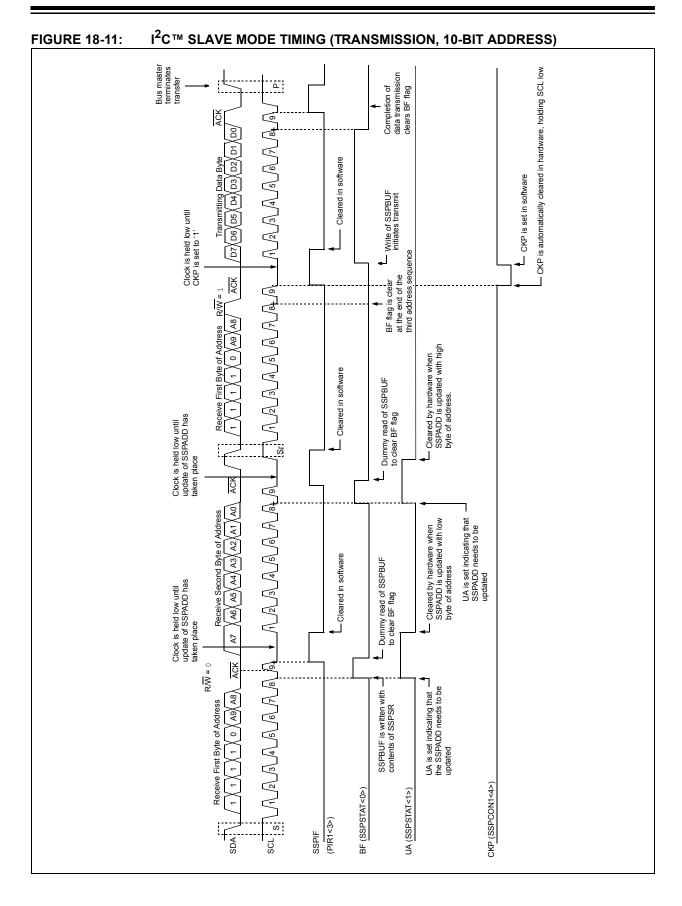

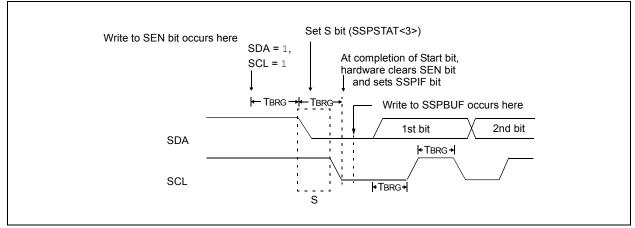

### 18.4.8 I<sup>2</sup>C MASTER MODE START CONDITION TIMING

To initiate a Start condition, the user sets the Start Condition Enable bit, SEN (SSPCON2<0>). If the SDA and SCL pins are sampled high, the Baud Rate Generator is reloaded with the contents of SSPADD<6:0> and starts its count. If SCL and SDA are both sampled high when the Baud Rate Generator times out (TBRG), the SDA pin is driven low. The action of the SDA being driven low while SCL is high is the Start condition and causes the S bit (SSPSTAT<3>) to be set. Following this, the Baud Rate Generator is reloaded with the contents of SSPADD<6:0> and resumes its count. When the Baud Rate Generator times out (TBRG), the SEN bit (SSPCON2<0>) will be automatically cleared by hardware, the Baud Rate Generator is suspended, leaving the SDA line held low and the Start condition is complete.

Note: If, at the beginning of the Start condition, the SDA and SCL pins are already sampled low, or if during the Start condition, the SCL line is sampled low before the SDA line is driven low, a bus collision occurs, the Bus Collision Interrupt Flag, BCLIF, is set, the Start condition is aborted and the I<sup>2</sup>C module is reset into its Idle state.

### 18.4.8.1 WCOL Status Flag

If the user writes the SSPBUF when a Start sequence is in progress, the WCOL is set and the contents of the buffer are unchanged (the write doesn't occur).

Note: Because queueing of events is not allowed, writing to the lower 5 bits of SSPCON2 is disabled until the Start condition is complete.

### FIGURE 18-19: FIRST START BIT TIMING

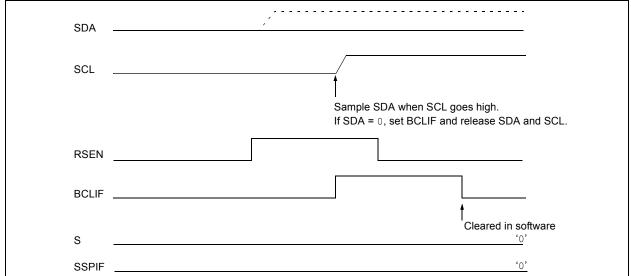

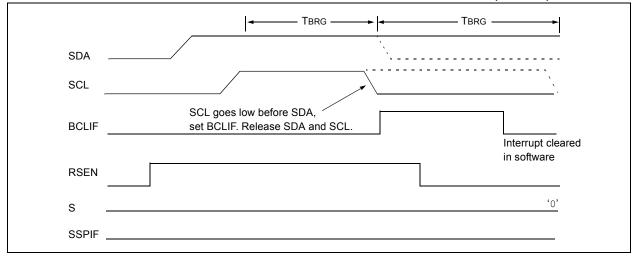

## 18.4.17.2 Bus Collision During a Repeated Start Condition

During a Repeated Start condition, a bus collision occurs if:

- a) A low level is sampled on SDA when SCL goes from a low level to a high level.

- b) SCL goes low before SDA is asserted low, indicating that another master is attempting to transmit a data '1'.

When the user deasserts SDA and the pin is allowed to float high, the BRG is loaded with SSPADD<6:0> and counts down to 0. The SCL pin is then deasserted and when sampled high, the SDA pin is sampled.

If SDA is low, a bus collision has occurred (i.e., another master is attempting to transmit a data '0', see Figure 18-29). If SDA is sampled high, the BRG is reloaded and begins counting. If SDA goes from high-to-low before the BRG times out, no bus collision occurs because no two masters can assert SDA at exactly the same time.

If SCL goes from high-to-low before the BRG times out, and SDA has not already been asserted, a bus collision occurs. In this case, another master is attempting to transmit a data '1' during the Repeated Start condition, see Figure 18-30.

If, at the end of the BRG time-out, both SCL and SDA are still high, the SDA pin is driven low and the BRG is reloaded and begins counting. At the end of the count regardless of the status of the SCL pin, the SCL pin is driven low and the Repeated Start condition is complete.

### FIGURE 18-29: BUS COLLISION DURING A REPEATED START CONDITION (CASE 1)

### FIGURE 18-30: BUS COLLISION DURING REPEATED START CONDITION (CASE 2)

The value in the ADRESH/ADRESL registers is not modified for a Power-on Reset. The ADRESH/ADRESL registers will contain unknown data after a Power-on Reset.

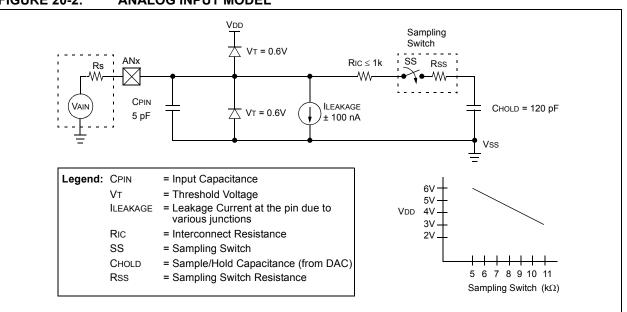

After the A/D module has been configured as desired, the selected channel must be acquired before the conversion is started. The analog input channels must have their corresponding TRIS bits selected as an input. To determine acquisition time, see **Section 20.1 "A/D Acquisition Requirements"**. After this acquisition time has elapsed, the A/D conversion can be started. An acquisition time <u>can be</u> programmed to occur between setting the GO/DONE bit and the actual start of the conversion.

The following steps should be followed to perform an A/D conversion:

- 1. Configure the A/D module:

- Configure analog pins, voltage reference and digital I/O (ADCON1)

- Select A/D input channel (ADCON0)

- Select A/D acquisition time (ADCON2)

- Select A/D conversion clock (ADCON2)

- Turn on A/D module (ADCON0)

- FIGURE 20-2: ANALOG INPUT MODEL

- 2. Configure A/D interrupt (if desired):

- Clear ADIF bit

- Set ADIE bit

- · Set GIE bit

- 3. Wait the required acquisition time (if required).

- 4. Start conversion:

- Set GO/DONE bit (ADCON0 register)

- 5. Wait for A/D conversion to complete, by either:

Polling for the GO/DONE bit to be cleared OR

- Waiting for the A/D interrupt

- 6. Read A/D Result registers (ADRESH:ADRESL); clear bit, ADIF, if required.

- 7. For next conversion, go to step 1 or step 2, as required. The A/D conversion time per bit is defined as TAD. A minimum wait of 2 TAD is required before next acquisition starts.

| RXFBCON0        | R/W-0             | R/W-0   | R/W-0           | R/W-0                            | R/W-0          | R/W-0   | R/W-0                  | R/W-0          |  |

|-----------------|-------------------|---------|-----------------|----------------------------------|----------------|---------|------------------------|----------------|--|

| <b>NAFBCONU</b> | F1BP_3            | F1BP_2  | F1BP_1          | F1BP_0                           | F0BP_3         | F0BP_2  | F0BP_1                 | F0BP_0         |  |

|                 |                   |         |                 |                                  |                |         |                        |                |  |

| RXFBCON1        | R/W-0             | R/W-0   | R/W-0           | R/W-1                            | R/W-0          | R/W-0   | R/W-0                  | R/W-1          |  |

|                 | F3BP_3            | F3BP_2  | F3BP_1          | F3BP_0                           | F2BP_3         | F2BP_2  | F2BP_1                 | F2BP_0         |  |

|                 |                   |         |                 |                                  |                |         |                        |                |  |

| RXFBCON2        | R/W-0             | R/W-0   | R/W-0           | R/W-1                            | R/W-0          | R/W-0   | R/W-0                  | R/W-1          |  |

|                 | F5BP_3            | F5BP_2  | F5BP_1          | F5BP_0                           | F4BP_3         | F4BP_2  | F4BP_1                 | F4BP_0         |  |

|                 |                   |         |                 |                                  |                |         |                        |                |  |

| RXFBCON3        | R/W-0             | R/W-0   | R/W-0           | R/W-0                            | R/W-0          | R/W-0   | R/W-0                  | R/W-0          |  |

|                 | F7BP_3            | F7BP_2  | F7BP_1          | F7BP_0                           | F6BP_3         | F6BP_2  | F6BP_1                 | F6BP_0         |  |

| r               | [                 |         |                 |                                  |                |         |                        |                |  |

| RXFBCON4        | R/W-0             | R/W-0   | R/W-0           | R/W-0                            | R/W-0          | R/W-0   | R/W-0                  | R/W-0          |  |

|                 | F9BP_3            | F9BP_2  | F9BP_1          | F9BP_0                           | F8BP_3         | F8BP_2  | F8BP_1                 | F8BP_0         |  |

| r               |                   |         |                 |                                  |                |         |                        |                |  |

| RXFBCON5        | R/W-0             | R/W-0   | R/W-0           | R/W-0                            | R/W-0          | R/W-0   | R/W-0                  | R/W-0          |  |

|                 | F11BP_3           | F11BP_2 | F11BP_1         | F11BP_0                          | F10BP_3        | F10BP_2 | F10BP_1                | F10BP_0        |  |

|                 |                   |         |                 |                                  |                |         |                        |                |  |

| RXFBCON6        | R/W-0             | R/W-0   | R/W-0           | R/W-0                            | R/W-0          | R/W-0   | R/W-0                  | R/W-0          |  |

|                 | F13BP_3           | F13BP_2 | F13BP_1         | F13BP_0                          | F12BP_3        | F12BP_2 | F12BP_1                | F12BP_0        |  |

|                 |                   | 5444.0  | 5444.0          | <b>D</b> # 4 / 0                 | 5444.0         | 5444.0  | <b>D</b> 444 A         | <b>D</b> 444 0 |  |

| RXFBCON7        | R/W-0             | R/W-0   | R/W-0           | R/W-0                            | R/W-0          | R/W-0   | R/W-0                  | R/W-0          |  |

|                 | F15BP_3           | F15BP_2 | F15BP_1         | F15BP_0                          | F14BP_3        | F14BP_2 | F14BP_1                | F14BP_0        |  |

|                 | bit 7             |         |                 |                                  |                |         |                        | bit 0          |  |

| Legend:         |                   |         |                 |                                  |                |         |                        |                |  |

| R = Readable    | a hit             |         | W = Writable    | W = Writable bit U = Unimplement |                |         | ented bit, read as '0' |                |  |

|                 |                   |         | '1' = Bit is se |                                  | '0' = Bit is c |         |                        | known          |  |

| -ii – vaiue al  | -n = Value at POR |         |                 | <i>.</i>                         |                |         | x = Bit is unknown     |                |  |

### REGISTER 24-47: RXFBCONn: RECEIVE FILTER BUFFER CONTROL REGISTER n<sup>(1)</sup>

bit 7-0 **FnBP\_<3:0>:** Filter n Buffer Pointer Nibble bits

- 0000 = Filter n is associated with RXB0

- 0001 = Filter n is associated with RXB1

- 0010 = Filter n is associated with B0

- 0011 = Filter n is associated with B1

0111 = Filter n is associated with B5 1111-1000 = Reserved

Note 1: This register is available in Mode 1 and 2 only.

...

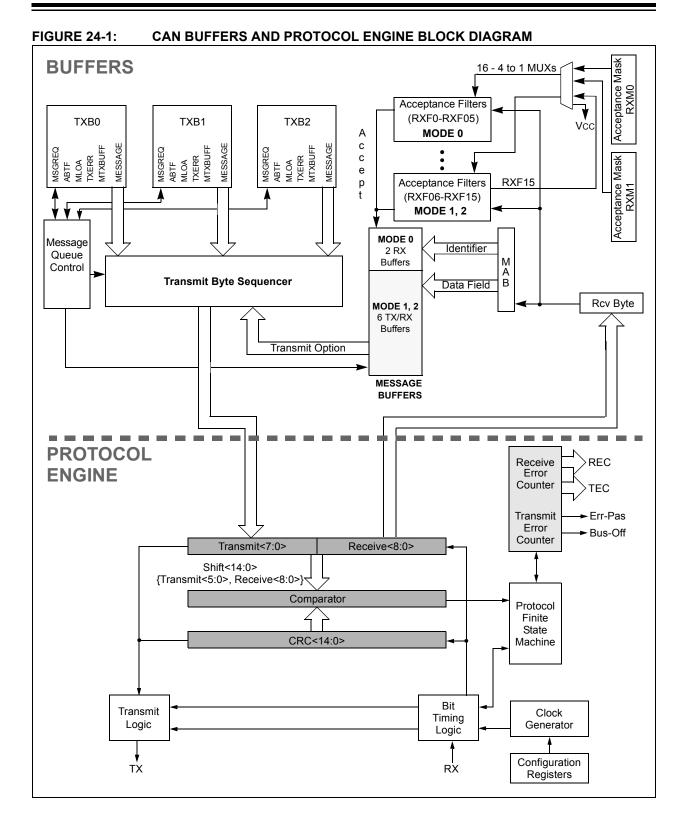

### 24.3 CAN Modes of Operation

The PIC18F2480/2580/4480/4580 has six main modes of operation:

- Configuration mode

- · Disable/Sleep mode

- Normal Operation mode

- · Listen Only mode

- · Loopback mode

- · Error Recognition mode

All modes, except Error Recognition, are requested by setting the REQOP bits (CANCON<7:5>). Error Recognition mode is requested through the RXM bits of the Receive Buffer register(s). Entry into a mode is Acknowledged by monitoring the OPMODE bits.

When changing modes, the mode will not actually change until all pending message transmissions are complete. Because of this, the user must verify that the device has actually changed into the requested mode before further operations are executed.

### 24.3.1 CONFIGURATION MODE

The CAN module has to be initialized before the activation. This is only possible if the module is in the Configuration mode. The Configuration mode is requested by setting the REQOP2 bit. Only when the status bit, OPMODE2, has a high level can the initialization be performed. Afterwards, the Configuration registers, the acceptance mask registers and the acceptance filter registers can be written. The module is activated by setting the REQOP control bits to zero.

The module will protect the user from accidentally violating the CAN protocol through programming errors. All registers which control the configuration of the module can not be modified while the module is online. The CAN module will not be allowed to enter the Configuration mode while a transmission or reception is taking place. The Configuration mode serves as a lock to protect the following registers:

- Configuration Registers

- Functional Mode Selection Registers

- Bit Timing Registers

- Identifier Acceptance Filter Registers

- Identifier Acceptance Mask Registers

- Filter and Mask Control Registers

- Mask Selection Registers

In the Configuration mode, the module will not transmit or receive. The error counters are cleared and the interrupt flags remain unchanged. The programmer will have access to Configuration registers that are access restricted in other modes. I/O pins will revert to normal I/O functions.

### 24.3.2 DISABLE/SLEEP MODE

In Disable/Sleep mode, the module will not transmit or receive. The module has the ability to set the WAKIF bit due to bus activity; however, any pending interrupts will remain and the error counters will retain their value.

If the REQOP<2:0> bits are set to '001', the module will enter the module Disable/Sleep mode. This mode is similar to disabling other peripheral modules by turning off the module enables. This causes the module internal clock to stop unless the module is active (i.e., receiving or transmitting a message). If the module is active, the module will wait for 11 recessive bits on the CAN bus, detect that condition as an Idle bus, then accept the module Disable/Sleep command. OPMODE<2:0> = 001 indicates whether the module successfully went into the module Disable/Sleep mode.

The WAKIF interrupt is the only module interrupt that is still active in the Disable/Sleep mode. If the WAKDIS is cleared and WAKIE is set, the processor will receive an interrupt whenever the module detects recessive to dominant transition. On wake-up, the module will automatically be set to the previous mode of operation. For example, if the module was switched from Normal to Disable/Sleep mode on bus activity wake-up, the module will automatically enter into Normal mode and the first message that caused the module to wake-up is lost. The module will not generate any error frame. Firmware logic must detect this condition and make sure that retransmission is requested. If the processor receives a wake-up interrupt while it is sleeping, more than one message may get lost. The actual number of messages lost would depend on the processor oscillator start-up time and incoming message bit rate.

The TXCAN pin will stay in the recessive state while the module is in Disable/Sleep mode.

### 24.3.3 NORMAL MODE

This is the standard operating mode of the PIC18F2480/2580/4480/4580 devices. In this mode, the device actively monitors all bus messages and generates Acknowledge bits, error frames, etc. This is also the only mode in which the PIC18F2480/2580/4480/4580 devices will transmit messages over the CAN bus.

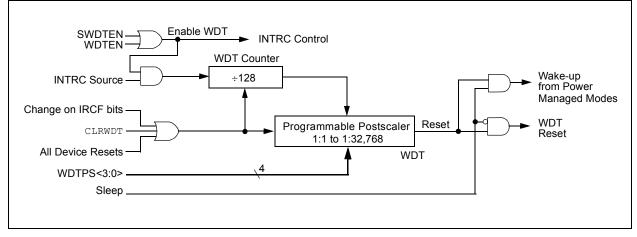

### 25.2 Watchdog Timer (WDT)

For PIC18F2480/2580/4480/4580 devices, the WDT is driven by the INTRC source. When the WDT is enabled, the clock source is also enabled. The nominal WDT period is 4 ms and has the same stability as the INTRC oscillator.

The 4 ms period of the WDT is multiplied by a 16-bit postscaler. Any output of the WDT postscaler is selected by a multiplexer, controlled by bits in Configuration Register 2H. Available periods range from 4 ms to 131.072 seconds (2.18 minutes). The WDT and postscaler are cleared when any of the following events occur: a SLEEP or CLRWDT instruction is executed, the IRCF bits (OSCCON<6:4>) are changed or a clock failure has occurred.

- Note 1: The CLRWDT and SLEEP instructions clear the WDT and postscaler counts when executed.

- 2: Changing the setting of the IRCF bits (OSCCON<6:4>) clears the WDT and postscaler counts.

- **3:** When a CLRWDT instruction is executed, the postscaler count will be cleared.

### 25.2.1 CONTROL REGISTER

Register 25-14 shows the WDTCON register. This is a readable and writable register which contains a control bit that allows software to override the WDT enable Configuration bit, but only if the Configuration bit has disabled the WDT.

### FIGURE 25-1: WDT BLOCK DIAGRAM

| RETFIE                  | Return fr                                                                       | om Interrup                       | t                  | RET   | LW                   | Return Li                        | teral to W                         |                           |

|-------------------------|---------------------------------------------------------------------------------|-----------------------------------|--------------------|-------|----------------------|----------------------------------|------------------------------------|---------------------------|

| Syntax:                 | RETFIE {                                                                        | s}                                |                    | Synt  | ax:                  | RETLW k                          |                                    |                           |

| Operands:               | $s \in [0,1]$                                                                   | s ∈ [0,1]                         |                    |       | rands:               | $0 \le k \le 255$                |                                    |                           |

| Operation:              | $(TOS) \rightarrow PC$ ,<br>1 $\rightarrow$ GIE/GIEH or PEIE/GIEL;<br>if s = 1, |                                   |                    | Oper  | ration:              | k → W,<br>(TOS) → P<br>PCLATU, P | C,<br>CLATH are u                  | nchanged                  |

|                         | $(WS) \rightarrow W$                                                            | ) $\rightarrow$ STATUS,           |                    | Statu | is Affected:         | None                             |                                    |                           |

|                         | $(BSRS) \rightarrow$                                                            |                                   |                    | Enco  | oding:               | 0000                             | 1100 kk                            | kk kkkk                   |

|                         |                                                                                 | CLATH are ur                      | nchanged.          | Desc  | cription:            | W is loaded                      | with the eigh                      | t-bit literal 'k'.        |

| Status Affected:        | GIE/GIEH,                                                                       | PEIE/GIEL.                        |                    |       |                      |                                  |                                    | aded from the             |

| Encoding:               | 0000                                                                            | 0000 00                           | 01 000s            |       |                      | •                                | tack (the retur<br>Idress latch (F |                           |

| Description:            | Return from                                                                     | n interrupt. Sta                  | ack is popped      |       |                      | remains un                       | •                                  | 02/111)                   |

|                         | •                                                                               | -Stack (TOS) i                    |                    | Word  | ds:                  | 1                                |                                    |                           |

|                         |                                                                                 | errupts are ena<br>er the high or |                    | Cycle | es:                  | 2                                |                                    |                           |

|                         |                                                                                 |                                   | t. If 's' = 1, the | QC    | ycle Activity:       |                                  |                                    |                           |

|                         |                                                                                 | the shadow re<br>and BSRS, are    | •                  |       | Q1                   | Q2                               | Q3                                 | Q4                        |

|                         |                                                                                 | ponding regis                     |                    |       | Decode               | Read                             | Process                            | POP PC                    |

|                         |                                                                                 |                                   | = 0, no update     |       |                      | literal 'k'                      | Data                               | from stack,<br>Write to W |

| Words:                  | 1                                                                               | gisters occurs.                   |                    |       | No                   | No                               | No                                 | No                        |

|                         | 2                                                                               |                                   |                    |       | operation            | operation                        | operation                          | operation                 |

| Cycles:                 | 2                                                                               |                                   |                    |       |                      |                                  |                                    |                           |

| Q Cycle Activity:<br>Q1 | Q2                                                                              | Q3                                | Q4                 | Exar  | nple:                |                                  |                                    |                           |

| Decode                  | No                                                                              | No                                | POP PC             |       | CALL TABLE           | ; W CONT<br>; offset             | ains table<br>value                |                           |

| 200040                  | operation                                                                       | operation                         | from stack         |       |                      | ; W now                          |                                    |                           |

|                         |                                                                                 |                                   | Set GIEH or        |       |                      | ; table                          | value                              |                           |

|                         |                                                                                 |                                   | GIEL               | TABI  | :<br>LE              |                                  |                                    |                           |

| No<br>operation         | No<br>operation                                                                 | No<br>operation                   | No<br>operation    |       | ADDWF PCL            | ; W = of                         | fset                               |                           |

| operation               | operation                                                                       | operation                         | operation          |       | RETLW k0<br>RETLW k1 | ; Begin                          | table                              |                           |

| Example:                | RETFIE                                                                          | 1                                 |                    | :     | KEILW KI             | ;                                |                                    |                           |

| After Interrup          | ot                                                                              |                                   |                    | :     | :                    |                                  |                                    |                           |

| PC .                    |                                                                                 | = TOS                             |                    |       | RETLW kn             | ; End of                         | table                              |                           |

| W<br>BSR                |                                                                                 | = WS<br>= BSRS                    | ;                  |       | Before Instruc<br>W  | ction<br>= 07h                   |                                    |                           |

| STATUS                  | S<br>EH, PEIE/GIEL                                                              | = STATU<br>= 1                    | JSS                |       | After Instructi      |                                  |                                    |                           |

| GIE/GIE                 |                                                                                 |                                   |                    |       |                      | -                                | <sup>f</sup> kn                    |                           |

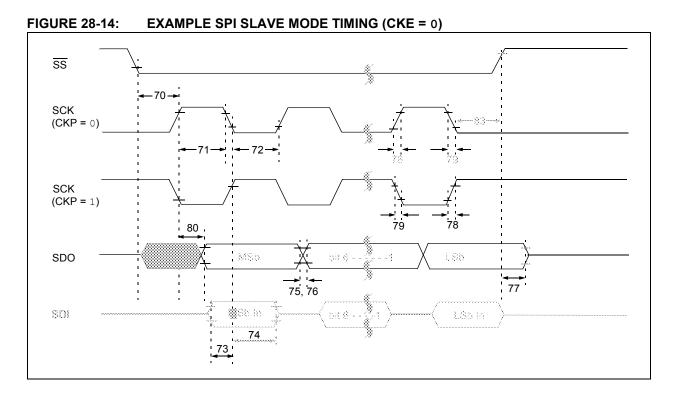

| Param<br>No. | Symbol                | Characteristic                                                         | Min                  | Max           | Units | Conditions |            |

|--------------|-----------------------|------------------------------------------------------------------------|----------------------|---------------|-------|------------|------------|

| 70           | TssL2scH              | $\overline{SS} \downarrow$ to SCK $\downarrow$ or SCK $\uparrow$ Input |                      | 3 TCY         | _     | ns         |            |

|              | ,<br>TssL2scL         |                                                                        |                      |               |       |            |            |

| 71           | TscH                  | SCK Input High Time                                                    | Continuous           | 1.25 Tcy + 30 | _     | ns         |            |

| 71A          |                       |                                                                        | Single Byte          | 40            | _     | ns         | (Note 1)   |

| 72           | TscL                  | SCK Input Low Time                                                     | Continuous           | 1.25 Tcy + 30 | _     | ns         |            |

| 72A          |                       |                                                                        | Single Byte          | 40            | _     | ns         | (Note 1)   |

| 73           | TDIV2scH,<br>TDIV2scL | Setup Time of SDI Data Input to SCK E                                  | 20                   | _             | ns    |            |            |

| 73A          | Тв2в                  | Last Clock Edge of Byte1 to the First Cloc                             | 1.5 Tcy + 40         | _             | ns    | (Note 2)   |            |

| 74           | TscH2diL,<br>TscL2diL | Hold Time of SDI Data Input to SCK Ed                                  | ge                   | 40            | _     | ns         |            |

| 75           | TDOR                  | SDO Data Output Rise Time                                              | PIC18FXXXX           |               | 25    | ns         |            |

|              |                       |                                                                        | PIC18LFXXXX          |               | 45    | ns         | VDD = 2.0V |

| 76           | TDOF                  | SDO Data Output Fall Time                                              | •                    | —             | 25    | ns         |            |

| 77           | TssH2doZ              | SS ↑ to SDO Output High-Impedance                                      |                      | 10            | 50    | ns         |            |

| 80           | TscH2doV              | SDO Data Output Valid after SCK                                        | PIC18FXXXX           |               | 50    | ns         |            |

|              | ,<br>TscL2doV         | Edge                                                                   | PIC18 <b>LF</b> XXXX |               | 100   | ns         | VDD = 2.0V |

| 83           | TscH2ssH<br>,         | SS ↑ after SCK Edge                                                    |                      | 1.5 TCY + 40  | —     | ns         |            |

|              | TscL2ssH              |                                                                        |                      |               |       |            |            |

### TABLE 28-16: EXAMPLE SPI MODE REQUIREMENTS (SLAVE MODE TIMING, CKE = 0)

**Note 1:** Requires the use of Parameter #73A.

**2:** Only if Parameter #71A and #72A are used.

| 447      |

|----------|

| 448      |

| 449      |

| 450      |

| 440      |

| 437      |

| 452      |

| 454      |

|          |

| 453      |

|          |

| 446      |

| 441      |

|          |

|          |

| 443      |

|          |

| 444      |

|          |

|          |

| 143      |

| 407      |

| 349, 360 |

|          |

| 72       |

|          |

| 235      |

|          |

### ۷

| 436                  |

|----------------------|

|                      |

|                      |

| 349, 358             |

| 359                  |

|                      |

|                      |

|                      |

| . 219, 220, 221, 224 |

| . 219, 220, 221, 224 |

|                      |

| 7                    |

|                      |

|                      |

|                      |

| 408                  |

|                      |

### WORLDWIDE SALES AND SERVICE

### AMERICAS

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support: http://support.microchip.com Web Address: www.microchip.com

Atlanta Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

Boston Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago Itasca, IL Tel: 630-285-0071 Fax: 630-285-0075

**Cleveland** Independence, OH Tel: 216-447-0464 Fax: 216-447-0643

**Dallas** Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

Detroit Farmington Hills, MI Tel: 248-538-2250 Fax: 248-538-2260

Kokomo Kokomo, IN Tel: 765-864-8360 Fax: 765-864-8387

Los Angeles Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608

Santa Clara Santa Clara, CA Tel: 408-961-6444 Fax: 408-961-6445

Toronto Mississauga, Ontario, Canada Tel: 905-673-0699 Fax: 905-673-6509

### ASIA/PACIFIC

Asia Pacific Office Suites 3707-14, 37th Floor Tower 6, The Gateway Harbour City, Kowloon Hong Kong Tel: 852-2401-1200 Fax: 852-2401-3431

Australia - Sydney Tel: 61-2-9868-6733 Fax: 61-2-9868-6755

**China - Beijing** Tel: 86-10-8528-2100 Fax: 86-10-8528-2104

**China - Chengdu** Tel: 86-28-8665-5511 Fax: 86-28-8665-7889

**China - Hong Kong SAR** Tel: 852-2401-1200 Fax: 852-2401-3431

**China - Nanjing** Tel: 86-25-8473-2460

Fax: 86-25-8473-2470 China - Qingdao

Tel: 86-532-8502-7355 Fax: 86-532-8502-7205

**China - Shanghai** Tel: 86-21-5407-5533 Fax: 86-21-5407-5066

China - Shenyang Tel: 86-24-2334-2829 Fax: 86-24-2334-2393

**China - Shenzhen** Tel: 86-755-8203-2660 Fax: 86-755-8203-1760

**China - Wuhan** Tel: 86-27-5980-5300 Fax: 86-27-5980-5118

**China - Xiamen** Tel: 86-592-2388138 Fax: 86-592-2388130

**China - Xian** Tel: 86-29-8833-7252 Fax: 86-29-8833-7256

**China - Zhuhai** Tel: 86-756-3210040 Fax: 86-756-3210049

### ASIA/PACIFIC

India - Bangalore Tel: 91-80-3090-4444 Fax: 91-80-3090-4080

India - New Delhi Tel: 91-11-4160-8631 Fax: 91-11-4160-8632

India - Pune Tel: 91-20-2566-1512 Fax: 91-20-2566-1513

**Japan - Yokohama** Tel: 81-45-471- 6166 Fax: 81-45-471-6122

**Korea - Daegu** Tel: 82-53-744-4301 Fax: 82-53-744-4302

Korea - Seoul Tel: 82-2-554-7200 Fax: 82-2-558-5932 or 82-2-558-5934

Malaysia - Kuala Lumpur Tel: 60-3-6201-9857 Fax: 60-3-6201-9859

**Malaysia - Penang** Tel: 60-4-227-8870 Fax: 60-4-227-4068

Philippines - Manila Tel: 63-2-634-9065 Fax: 63-2-634-9069

Singapore Tel: 65-6334-8870 Fax: 65-6334-8850

**Taiwan - Hsin Chu** Tel: 886-3-6578-300 Fax: 886-3-6578-370

**Taiwan - Kaohsiung** Tel: 886-7-536-4818 Fax: 886-7-536-4803

Taiwan - Taipei Tel: 886-2-2500-6610 Fax: 886-2-2508-0102

**Thailand - Bangkok** Tel: 66-2-694-1351 Fax: 66-2-694-1350

### EUROPE

Austria - Wels Tel: 43-7242-2244-39 Fax: 43-7242-2244-393 Denmark - Copenhagen Tel: 45-4450-2828 Fax: 45-4485-2829

France - Paris Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

**Germany - Munich** Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

**Italy - Milan** Tel: 39-0331-742611 Fax: 39-0331-466781

Netherlands - Drunen Tel: 31-416-690399 Fax: 31-416-690340

**Spain - Madrid** Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

**UK - Wokingham** Tel: 44-118-921-5869 Fax: 44-118-921-5820

03/26/09