Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 40MHz                                                                      |

| Connectivity               | CANbus, I <sup>2</sup> C, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                |

| Number of I/O              | 36                                                                         |

| Program Memory Size        | 32KB (16K x 16)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 1.5K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                  |

| Data Converters            | A/D 11x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-TQFP                                                                    |

| Supplier Device Package    | 44-TQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf4580-i-pt |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 4.0 POWER-MANAGED MODES

PIC18F2480/2580/4480/4580 devices offer a total of seven operating modes for more efficient power management. These modes provide a variety of options for selective power conservation in applications where resources may be limited (i.e., battery-powered devices).

There are three categories of power-managed modes:

- Run modes

- Idle modes

- Sleep mode

These categories define which portions of the device are clocked, and sometimes, what speed. The Run and Idle modes may use any of the three available clock sources (primary, secondary or internal oscillator block); the Sleep mode does not use a clock source.

The power-managed modes include several power-saving features offered on previous PIC<sup>®</sup> devices. One is the clock switching feature, offered in other PIC18 devices, allowing the controller to use the Timer1 oscillator in place of the primary oscillator. Also included is the Sleep mode, offered by all PIC devices, where all device clocks are stopped.

#### 4.1 Selecting Power-Managed Modes

Selecting a power-managed mode requires two decisions: if the CPU is to be clocked or not and the selection of a clock source. The IDLEN bit (OSCCON<7>) controls CPU clocking, while the SCS<1:0> bits (OSCCON<1:0>) select the clock source. The individual modes, bit settings, clock sources and affected modules are summarized in Table 4-1.

### 4.1.1 CLOCK SOURCES

The SCS<1:0> bits allow the selection of one of three clock sources for power-managed modes. They are:

- The primary clock, as defined by the FOSC<3:0> Configuration bits

- The secondary clock (the Timer1 oscillator)

- The internal oscillator block (for RC modes)

#### 4.1.2 ENTERING POWER-MANAGED MODES

Switching from one power-managed mode to another begins by loading the OSCCON register. The SCS<1:0> bits select the clock source and determine which Run or Idle mode is to be used. Changing these bits causes an immediate switch to the new clock source, assuming that it is running. The switch may also be subject to clock transition delays. These are discussed in **Section 4.1.3 "Clock Transitions and Status Indicators"** and subsequent sections.

Entry to the power-managed Idle or Sleep modes is triggered by the execution of a SLEEP instruction. The actual mode that results depends on the status of the IDLEN bit.

Depending on the current mode and the mode being switched to, a change to a power-managed mode does not always require setting all of these bits. Many transitions may be done by changing the oscillator select bits, or changing the IDLEN bit, prior to issuing a SLEEP instruction. If the IDLEN bit is already configured correctly, it may only be necessary to perform a SLEEP instruction to switch to the desired mode.

| IADLE 4-1: | POWER                | K-INIANAGED IV | IODE3   |             |                                                                                                              |

|------------|----------------------|----------------|---------|-------------|--------------------------------------------------------------------------------------------------------------|

| Mada       | OSCC                 | ON<7,1:0>      | Modul   | e Clocking  | Augilable Clask and Ossillator Source                                                                        |

| Mode       | IDLEN <sup>(1)</sup> | SCS<1:0>       | CPU     | Peripherals | Available Clock and Oscillator Source                                                                        |

| Sleep      | 0                    | N/A            | Off     | Off         | None – All clocks are disabled                                                                               |

| PRI_RUN    | N/A                  | 00             | Clocked | Clocked     | Primary – LP, XT, HS, HSPLL, RC, EC, INTRC <sup>(2)</sup> :<br>This is the normal full-power execution mode. |

| SEC_RUN    | N/A                  | 01             | Clocked | Clocked     | Secondary – Timer1 Oscillator                                                                                |

| RC_RUN     | N/A                  | 1x             | Clocked | Clocked     | Internal Oscillator Block <sup>(2)</sup>                                                                     |

| PRI_IDLE   | 1                    | 00             | Off     | Clocked     | Primary – LP, XT, HS, HSPLL, RC, EC                                                                          |

| SEC_IDLE   | 1                    | 01             | Off     | Clocked     | Secondary – Timer1 Oscillator                                                                                |

| RC_IDLE    | 1                    | 1x             | Off     | Clocked     | Internal Oscillator Block <sup>(2)</sup>                                                                     |

TABLE 4-1: POWER-MANAGED MODES

Note 1: IDLEN reflects its value when the **SLEEP** instruction is executed.

2: Includes INTOSC and INTOSC postscaler, as well as the INTRC source.

| File Name                              | Bit 7 | Bit 6 | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   | Value on POR, BOR | Details on<br>Page: |

|----------------------------------------|-------|-------|---------|---------|---------|---------|---------|---------|-------------------|---------------------|

| B4D2 <sup>(8)</sup>                    | B4D27 | B4D26 | B4D25   | B4D24   | B4D23   | B4D22   | B4D21   | B4D20   | XXXX XXXX         | 63, 305             |

| B4D1 <sup>(8)</sup>                    | B4D17 | B4D16 | B4D15   | B4D14   | B4D13   | B4D12   | B4D11   | B4D10   | XXXX XXXX         | 63, 305             |

| B4D0 <sup>(8)</sup>                    | B4D07 | B4D06 | B4D05   | B4D04   | B4D03   | B4D02   | B4D01   | B4D00   | XXXX XXXX         | 62, 305             |

| B4DLC <sup>(8)</sup><br>Receive mode   | —     | RXRTR | RB1     | RB0     | DLC3    | DLC2    | DLC1    | DLC0    | -xxx xxxx         | 63, 307             |

| B4DLC <sup>(8)</sup><br>Transmit mode  | —     | TXRTR | —       | —       | DLC3    | DLC2    | DLC1    | DLC0    | -x xxxx           | 63, 307             |

| B4EIDL <sup>(8)</sup>                  | EID7  | EID6  | EID5    | EID4    | EID3    | EID2    | EID1    | EID0    | XXXX XXXX         | 63, 305             |

| B4EIDH <sup>(8)</sup>                  | EID15 | EID14 | EID13   | EID12   | EID11   | EID10   | EID9    | EID8    | XXXX XXXX         | 63, 304             |

| B4SIDL <sup>(8)</sup><br>Receive mode  | SID2  | SID1  | SID0    | SRR     | EXID    | —       | EID17   | EID16   | XXXX X-XX         | 63, 303             |

| B4SIDL <sup>(8)</sup><br>Transmit mode | SID2  | SID1  | SID0    |         | EXIDE   | —       | EID17   | EID16   | xxx- x-xx         | 63, 303             |

| B4SIDH <sup>(8)</sup>                  | SID10 | SID9  | SID8    | SID7    | SID6    | SID5    | SID4    | SID3    | XXXX XXXX         | 63, 302             |

| B4CON <sup>(8)</sup><br>Receive mode   | RXFUL | RXM1  | RXRTRRO | FILHIT4 | FILHIT3 | FILHIT2 | FILHIT1 | FILHITO | 0000 0000         | 63, 301             |

| B4CON <sup>(8)</sup><br>Transmit mode  | TXBIF | TXABT | TXLARB  | TXERR   | TXREQ   | RTREN   | TXPRI1  | TXPRI0  | 0000 0000         | 63, 301             |

| B3D7 <sup>(8)</sup>                    | B3D77 | B3D76 | B3D75   | B3D74   | B3D73   | B3D72   | B3D71   | B3D70   | XXXX XXXX         | 63, 305             |

| B3D6 <sup>(8)</sup>                    | B3D67 | B3D66 | B3D65   | B3D64   | B3D63   | B3D62   | B3D61   | B3D60   | XXXX XXXX         | 63, 305             |

| B3D5 <sup>(8)</sup>                    | B3D57 | B3D56 | B3D55   | B3D54   | B3D53   | B3D52   | B3D51   | B3D50   | XXXX XXXX         | 63, 305             |

| B3D4 <sup>(8)</sup>                    | B3D47 | B3D46 | B3D45   | B3D44   | B3D43   | B3D42   | B3D41   | B3D40   | XXXX XXXX         | 63, 305             |

| B3D3 <sup>(8)</sup>                    | B3D37 | B3D36 | B3D35   | B3D34   | B3D33   | B3D32   | B3D31   | B3D30   | XXXX XXXX         | 63, 305             |

| B3D2 <sup>(8)</sup>                    | B3D27 | B3D26 | B3D25   | B3D24   | B3D23   | B3D22   | B3D21   | B3D20   | XXXX XXXX         | 63, 305             |

| B3D1 <sup>(8)</sup>                    | B3D17 | B3D16 | B3D15   | B3D14   | B3D13   | B3D12   | B3D11   | B3D10   | XXXX XXXX         | 63, 305             |

| B3D0 <sup>(8)</sup>                    | B3D07 | B3D06 | B3D05   | B3D04   | B3D03   | B3D02   | B3D01   | B3D00   | XXXX XXXX         | 63, 305             |

| B3DLC <sup>(8)</sup><br>Receive mode   | _     | RXRTR | RB1     | RB0     | DLC3    | DLC2    | DLC1    | DLC0    | -xxx xxxx         | 63, 307             |

| B3DLC <sup>(8)</sup><br>Transmit mode  | —     | TXRTR | —       | —       | DLC3    | DLC2    | DLC1    | DLC0    | -x xxxx           | 63, 307             |

| B3EIDL <sup>(8)</sup>                  | EID7  | EID6  | EID5    | EID4    | EID3    | EID2    | EID1    | EID0    | XXXX XXXX         | 63, 305             |

| B3EIDH <sup>(8)</sup>                  | EID15 | EID14 | EID13   | EID12   | EID11   | EID10   | EID9    | EID8    | XXXX XXXX         | 63, 304             |

| B3SIDL <sup>(8)</sup><br>Receive mode  | SID2  | SID1  | SID0    | SRR     | EXID    | —       | EID17   | EID16   | XXXX X-XX         | 63, 303             |

| B3SIDL <sup>(8)</sup><br>Transmit mode | SID2  | SID1  | SID0    | —       | EXIDE   | —       | EID17   | EID16   | xxx- x-xx         | 63, 303             |

| B3SIDH <sup>(8)</sup>                  | SID10 | SID9  | SID8    | SID7    | SID6    | SID5    | SID4    | SID3    | XXXX XXXX         | 63, 302             |

| B3CON <sup>(8)</sup><br>Receive mode   | RXFUL | RXM1  | RXRTRRO | FILHIT4 | FILHIT3 | FILHIT2 | FILHIT1 | FILHIT0 | 0000 0000         | 63, 301             |

| B3CON <sup>(8)</sup><br>Transmit mode  | TXBIF | TXABT | TXLARB  | TXERR   | TXREQ   | RTREN   | TXPRI1  | TXPRI0  | 0000 0000         | 63, 301             |

| B2D7 <sup>(8)</sup>                    | B2D77 | B2D76 | B2D75   | B2D74   | B2D73   | B2D72   | B2D71   | B2D70   | XXXX XXXX         | 63, 305             |

| B2D6 <sup>(8)</sup>                    | B2D67 | B2D66 | B2D65   | B2D64   | B2D63   | B2D62   | B2D61   | B2D60   | XXXX XXXX         | 63, 305             |

| B2D5 <sup>(8)</sup>                    | B2D57 | B2D56 | B2D55   | B2D54   | B2D53   | B2D52   | B2D51   | B2D50   | XXXX XXXX         | 63, 305             |

#### TABLE 6-2:REGISTER FILE SUMMARY (PIC18F2480/2580/4480/4580) (CONTINUED)

**Legend:** x = unknown, u = unchanged, – = unimplemented, q = value depends on condition

**Note 1:** Bit 21 of the PC is only available in Test mode and Serial Programming modes.

2: The SBOREN bit is only available when CONFIG2L<1:0> = 01; otherwise, it is disabled and reads as '0'. See Section 5.4 "Brown-out Reset (BOR)".

These registers and/or bits are not implemented on PIC18F2X80 devices and are read as '0'. Reset values are shown for PIC18F4X80 devices; individual unimplemented bits should be interpreted as '—'.

4: The PLLEN bit is only available in specific oscillator configuration; otherwise, it is disabled and reads as '0'. See Section 3.6.4 "PLL in INTOSC Modes".

5: The RE3 bit is only available when Master Clear Reset is disabled (CONFIG3H<7> = 0); otherwise, RE3 reads as '0'. This bit is read-only.

6: RA6/RA7 and their associated latch and direction bits are individually configured as port pins based on various primary oscillator modes. When disabled, these bits read as '0'.

7: CAN bits have multiple functions depending on the selected mode of the CAN module.

8: This register reads all '0's until the ECAN™ technology is set up in Mode 1 or Mode 2.

9: These registers are available on PIC18F4X80 devices only.

| R/W-x         | R/W-x         | U-0                                      | R/W-0        | R/W-x                         | R/W-0             | R/S-0             | R/S-0           |

|---------------|---------------|------------------------------------------|--------------|-------------------------------|-------------------|-------------------|-----------------|

| EEPGD         | CFGS          | —                                        | FREE         | WRERR <sup>(1)</sup>          | WREN              | WR                | RD              |

| bit 7         |               |                                          |              |                               |                   |                   | bit 0           |

| Legend:       |               | S = Settable                             | oit          |                               |                   |                   |                 |

| R = Readable  | a hit         | W = Writable                             |              | II = I Inimplen               | nented bit, rea   | d as 'O'          |                 |

| -n = Value at |               | '1' = Bit is set                         |              | '0' = Bit is cle              |                   | x = Bit is unkr   | NWD             |

|               |               |                                          |              |                               | uicu              |                   |                 |

| bit 7         | EEPGD: Fla    | ish Program or I                         | Data EEPROI  | M Memory Sele                 | ct bit            |                   |                 |

|               |               | Flash program r                          |              |                               |                   |                   |                 |

|               | 0 = Access    | data EEPROM r                            | nemory       |                               |                   |                   |                 |

| bit 6         |               | h Program/Data                           |              | Configuration S               | Select bit        |                   |                 |

|               |               | Configuration re                         |              | OM momony                     |                   |                   |                 |

| bit 5         |               | Flash program o<br>nted: Read as '       |              | OWITHEITIOLY                  |                   |                   |                 |

| bit 4         | -             | n Row Erase En                           |              |                               |                   |                   |                 |

| DIL 4         |               | he program me                            |              | Iressed by TRI                | PTR on the ne     | ext WR comma      | nd (cleared by  |

|               |               | tion of erase ope                        |              |                               |                   |                   |                 |

|               | 0 = Perform   | •                                        |              |                               |                   |                   |                 |

| bit 3         | WRERR: FI     | ash Program/Da                           | ta EEPROM    | Error Flag bit <sup>(1)</sup> |                   |                   |                 |

|               |               | operation is pre                         | •            | · •                           | set during self-  | timed programr    | ning in norma   |

|               |               | on or an imprope<br>te operation con     |              | pt)                           |                   |                   |                 |

| bit 2         |               | sh Program/Data                          |              | /rite Enable bit              |                   |                   |                 |

|               |               | write cycles to F                        |              |                               |                   |                   |                 |

|               |               | write cycles to F                        |              |                               |                   |                   |                 |

| bit 1         | WR: Write C   | Control bit                              |              |                               |                   |                   |                 |

|               |               | a data EEPRO                             |              |                               |                   |                   |                 |

|               |               | eration is self-til<br>R bit can only be |              |                               |                   | e write is compl  | ete.            |

|               |               | cle to the EEPF                          |              |                               | .)                |                   |                 |

| bit 0         | RD: Read C    |                                          | I.           |                               |                   |                   |                 |

|               | 1 = Initiates | an EEPROM re                             | ad (Read tak | es one cycle. RI              | ) is cleared in I | nardware. The F   | RD bit can only |

|               |               | not cleared) in s                        |              | oit cannot be se              | t when EEPGI      | D = 1  or  CFGS = | = 1.)           |

|               | 0 = Does n    | ot initiate an EE                        | -ROM read    |                               |                   |                   |                 |

### REGISTER 8-1: EECON1: DATA EEPROM CONTROL REGISTER 1

**Note 1:** When a WRERR occurs, the EEPGD and CFGS bits are not cleared. This allows tracing of the error condition.

NOTES:

## **10.0 INTERRUPTS**

The PIC18F2480/2580/4480/4580 devices have multiple interrupt sources and an interrupt priority feature that allows each interrupt source to be assigned a high-priority level or a low-priority level. The high-priority interrupt vector is at 000008h and the low-priority interrupt vector is at 000018h. High-priority interrupts will interrupt any low-priority interrupts that may be in progress.

There are ten registers which are used to control interrupt operation. These registers are:

- RCON

- INTCON

- INTCON2

- INTCON3

- PIR1, PIR2, PIR3

- PIE1, PIE2, PIE3

- IPR1, IPR2, IPR3

It is recommended that the Microchip header files supplied with MPLAB<sup>®</sup> IDE be used for the symbolic bit names in these registers. This allows the assembler/ compiler to automatically take care of the placement of these bits within the specified register.

Each interrupt source has three bits to control its operation. The functions of these bits are:

- Flag bit to indicate that an interrupt event occurred

- Enable bit that allows program execution to branch to the interrupt vector address when the flag bit is set

- Priority bit to select high priority or low priority

The interrupt priority feature is enabled by setting the IPEN bit (RCON<7>). When interrupt priority is enabled, there are two bits which enable interrupts globally. Setting the GIEH bit (INTCON<7>) enables all interrupts that have the priority bit set (high priority). Setting the GIEL bit (INTCON<6>) enables all interrupts that have the priority bit cleared (low priority). When the interrupt flag, enable bit and appropriate global interrupt enable bit are set, the interrupt will vector immediately to address 000008h or 000018h, depending on the priority bit setting. Individual interrupts can be disabled through their corresponding enable bits.

When the IPEN bit is cleared (default state), the interrupt priority feature is disabled and interrupts are compatible with PIC<sup>®</sup> mid-range devices. In Compatibility mode, the interrupt priority bits for each source have no effect. INTCON<6> is the PEIE bit, which enables/disables all peripheral interrupt sources. INT-CON<7> is the GIE bit, which enables/disables all interrupt sources. All interrupts branch to address 000008h in Compatibility mode.

When an interrupt is responded to, the global interrupt enable bit is cleared to disable further interrupts. If the IPEN bit is cleared, this is the GIE bit. If interrupt priority levels are used, this will be either the GIEH or GIEL bit. High-priority interrupt sources can interrupt a lowpriority interrupt. Low-priority interrupts are not processed while high-priority interrupts are in progress.

The return address is pushed onto the stack and the PC is loaded with the interrupt vector address (00008h or 000018h). Once in the Interrupt Service Routine, the source(s) of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bits must be cleared in software before re-enabling interrupts to avoid recursive interrupts.

The "return from interrupt" instruction, RETFIE, exits the interrupt routine and sets the GIE bit (GIEH or GIEL if priority levels are used), which re-enables interrupts.

For external interrupt events, such as the INTx pins or the PORTB input change interrupt, the interrupt latency will be three to four instruction cycles. The exact latency is the same for one or two-cycle instructions. Individual interrupt flag bits are set, regardless of the status of their corresponding enable bit or the GIE bit.

Note: Do not use the MOVFF instruction to modify any of the Interrupt Control registers while any interrupt is enabled. Doing so may cause erratic microcontroller behavior.

#### 12.3 Prescaler

An 8-bit counter is available as a prescaler for the Timer0 module. The prescaler is not directly readable or writable; its value is set by the PSA and T0PS<2:0> bits (T0CON<3:0>) which determine the prescaler assignment and prescale ratio.

Clearing the PSA bit assigns the prescaler to the Timer0 module. When it is assigned, prescale values from 1:2 through 1:256 in power-of-2 increments are selectable.

When assigned to the Timer0 module, all instructions writing to the TMR0 register (e.g., CLRF TMR0, MOVWF TMR0, BSF TMR0, etc.) clear the prescaler count.

Note: Writing to TMR0 when the prescaler is assigned to Timer0 will clear the prescaler count but will not change the prescaler assignment.

#### 12.3.1 SWITCHING PRESCALER ASSIGNMENT

The prescaler assignment is fully under software control and can be changed "on-the-fly" during program execution.

### 12.4 Timer0 Interrupt

The TMR0 interrupt is generated when the TMR0 register overflows from FFh to 00h in 8-bit mode, or from FFFFh to 0000h in 16-bit mode. This overflow sets the TMR0IF flag bit. The interrupt can be masked by clearing the TMR0IE bit (INTCON<5>). Before reenabling the interrupt, the TMR0IF bit must be cleared in software by the Interrupt Service Routine.

Since Timer0 is shut down in Sleep mode, the TMR0 interrupt cannot awaken the processor from Sleep.

TABLE 12-1:

REGISTERS ASSOCIATED WITH TIMER0

| Name   | Bit 7                                                                     | Bit 6                  | Bit 5  | Bit 4  | Bit 3 | Bit 2  | Bit 1  | Bit 0 | Reset<br>Values<br>on Page: |  |

|--------|---------------------------------------------------------------------------|------------------------|--------|--------|-------|--------|--------|-------|-----------------------------|--|

| TMR0L  | Timer0 Reg                                                                | ner0 Register Low Byte |        |        |       |        |        |       |                             |  |

| TMR0H  | Timer0 Reg                                                                | ister High By          | /te    |        |       |        |        |       | 56                          |  |

| INTCON | GIE/GIEH                                                                  | PEIE/GIEL              | TMR0IE | INT0IE | RBIE  | TMR0IF | INT0IF | RBIF  | 55                          |  |

| T0CON  | TMR00N                                                                    | T08BIT                 | TOCS   | T0SE   | PSA   | T0PS2  | T0PS1  | T0PS0 | 56                          |  |

| TRISA  | TRISA7 <sup>(1)</sup> TRISA6 <sup>(1)</sup> PORTA Data Direction Register |                        |        |        |       |        |        |       | 58                          |  |

Legend: — = unimplemented locations, read as '0'. Shaded cells are not used by Timer0.

**Note 1:** RA6/RA7 and their associated latch and direction bits are individually configured as port pins based on various primary oscillator modes. When disabled, these bits read as '0'.

NOTES:

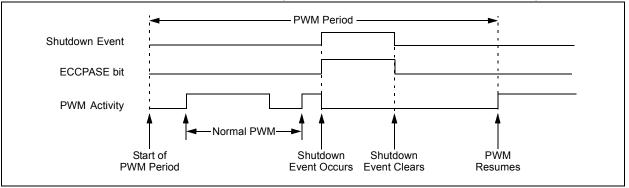

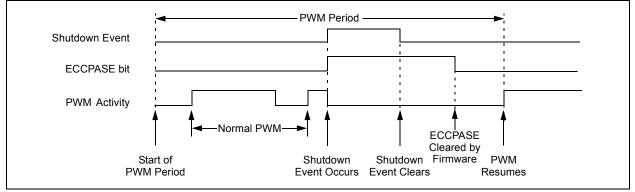

### 17.4.7.1 Auto-Shutdown and Auto-Restart

The auto-shutdown feature can be configured to allow automatic restarts of the module following a shutdown event. This is enabled by setting the PRSEN bit of the ECCP1DEL register (ECCP1DEL<7>).

In Shutdown mode with PRSEN = 1 (Figure 17-10), the ECCPASE bit will remain set for as long as the cause of the shutdown continues. When the shutdown condition clears, the ECCP1ASE bit is cleared. If PRSEN = 0 (Figure 17-11), once a shutdown condition occurs, the ECCPASE bit will remain set until it is cleared by firmware. Once ECCPASE is cleared, the Enhanced PWM will resume at the beginning of the next PWM period.

| Note: | Writing to the ECCPASE bit is disabled |

|-------|----------------------------------------|

|       | while a shutdown condition is active.  |

Independent of the PRSEN bit setting, if the auto-shutdown source is one of the comparators, the shutdown condition is a level. The ECCPASE bit cannot be cleared as long as the cause of the shutdown persists.

The Auto-Shutdown mode can be forced by writing a '1' to the ECCPASE bit.

### 17.4.8 START-UP CONSIDERATIONS

When the ECCP module is used in the PWM mode, the application hardware must use the proper external pull-up and/or pull-down resistors on the PWM output pins. When the microcontroller is released from Reset, all of the I/O pins are in the high-impedance state. The external circuits must keep the power switch devices in the off state until the microcontroller drives the I/O pins with the proper signal levels, or activates the PWM output(s).

The CCP1M<1:0> bits (ECCP1CON<1:0>) allow the user to choose whether the PWM output signals are active-high or active-low for each pair of PWM output pins (P1A/P1C and P1B/P1D). The PWM output polarities must be selected before the PWM pins are configured as outputs. Changing the polarity configuration while the PWM pins are configured as outputs is not recommended, since it may result in damage to the application circuits.

The P1A, P1B, P1C and P1D output latches may not be in the proper states when the PWM module is initialized. Enabling the PWM pins for output at the same time as the ECCP module may cause damage to the application circuit. The ECCP module must be enabled in the proper output mode and complete a full PWM cycle before configuring the PWM pins as outputs. The completion of a full PWM cycle is indicated by the TMR2IF bit being set as the second PWM period begins.

#### FIGURE 17-10: PWM AUTO-SHUTDOWN (PRSEN = 1, AUTO-RESTART ENABLED)

### FIGURE 17-11: PWM AUTO-SHUTDOWN (PRSEN = 0, AUTO-RESTART DISABLED)

| R/W-0         | R/W-0                                                                                                       | R/W-0                                                                                                              | R/W-0                                                                             | R/W-0                                                    | R/W-0                                       | R/W-0                | R/W-0                |

|---------------|-------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|----------------------------------------------------------|---------------------------------------------|----------------------|----------------------|

| WCOL          | SSPOV                                                                                                       | SSPEN <sup>(1)</sup>                                                                                               | CKP                                                                               | SSPM3 <sup>(2)</sup>                                     | SSPM2 <sup>(2)</sup>                        | SSPM1 <sup>(2)</sup> | SSPM0 <sup>(2)</sup> |

| bit 7         |                                                                                                             |                                                                                                                    |                                                                                   |                                                          |                                             |                      | bit                  |

|               |                                                                                                             |                                                                                                                    |                                                                                   |                                                          |                                             |                      |                      |

| Legend:       |                                                                                                             |                                                                                                                    |                                                                                   |                                                          |                                             |                      |                      |

| R = Readabl   |                                                                                                             | W = Writable I                                                                                                     | oit                                                                               | -                                                        | nented bit, reac                            |                      |                      |

| -n = Value at | POR                                                                                                         | '1' = Bit is set                                                                                                   |                                                                                   | '0' = Bit is cle                                         | ared                                        | x = Bit is unkr      | IOWN                 |

| bit 7         | WCOL: Write                                                                                                 | e Collision Deteo                                                                                                  | ct bit                                                                            |                                                          |                                             |                      |                      |

|               |                                                                                                             | ansmit mode:                                                                                                       |                                                                                   |                                                          |                                             |                      |                      |

|               |                                                                                                             | to the SSPBUF                                                                                                      | register wa                                                                       | s attempted wi                                           | hile the I <sup>2</sup> C co                | nditions were r      | not valid for        |

|               |                                                                                                             | ssion to be starte                                                                                                 | ed (must be c                                                                     | leared in softwa                                         | are)                                        |                      |                      |

|               | 0 = No collis                                                                                               |                                                                                                                    |                                                                                   |                                                          |                                             |                      |                      |

|               | In Slave Train<br>1 = The SSI<br>software                                                                   | PBUF register is                                                                                                   | written while                                                                     | e it is still transn                                     | nitting the previ                           | ous word (mus        | t be cleared         |

|               | 0 = No collis                                                                                               | /                                                                                                                  |                                                                                   |                                                          |                                             |                      |                      |

|               | <u>In Receive m</u><br>This is a "do                                                                        | <u>node (Master or</u><br>n't care" bit.                                                                           | Slave modes                                                                       | <u>s):</u>                                               |                                             |                      |                      |

| bit 6         | SSPOV: Red                                                                                                  | ceive Overflow Ir                                                                                                  | ndicator bit                                                                      |                                                          |                                             |                      |                      |

|               | In Receive m<br>1 = A byte is<br>software<br>0 = No over                                                    | s received while<br>e)                                                                                             | the SSPBUF                                                                        | register is still l                                      | holding the prev                            | rious byte (mus      | t be cleared         |

|               | <u>In Transmit r</u><br>This is a "do                                                                       | <u>mode:</u><br>n't care" bit in Tr                                                                                | ansmit mode                                                                       |                                                          |                                             |                      |                      |

| bit 5         | SSPEN: Mas                                                                                                  | ster Synchronou                                                                                                    | s Serial Port                                                                     | Enable bit <sup>(1)</sup>                                |                                             |                      |                      |

|               |                                                                                                             | the serial port and serial port and                                                                                |                                                                                   |                                                          |                                             | e serial port pins   | 6                    |

| bit 4         | CKP: SCK F                                                                                                  | Release Control                                                                                                    | bit                                                                               |                                                          |                                             |                      |                      |

|               | In Slave mod                                                                                                | de:                                                                                                                |                                                                                   |                                                          |                                             |                      |                      |

|               | 1 = Release                                                                                                 |                                                                                                                    |                                                                                   |                                                          |                                             |                      |                      |

|               |                                                                                                             | ock low (clock st                                                                                                  | retch), used i                                                                    | to ensure data                                           | setup time                                  |                      |                      |

|               | In Master mo<br>Unused in th                                                                                |                                                                                                                    |                                                                                   |                                                          |                                             |                      |                      |

| bit 3-0       |                                                                                                             | : Master Synchro                                                                                                   | onous Serial                                                                      | Port Mode Sele                                           | ect hits(2)                                 |                      |                      |

|               | $1111 =  ^{2}C \le$<br>$1110 =  ^{2}C \le$<br>$1011 =  ^{2}C =$<br>$1000 =  ^{2}C =$<br>$0111 =  ^{2}C \le$ | Slave mode, 10-<br>Slave mode, 7-bi<br>Firmware Contro<br>Vlaster mode, clo<br>Slave mode, 10-<br>Slave mode, 7-bi | bit address w<br>it address wit<br>illed Master n<br>ock = Fosc/(4<br>bit address | rith Start and St<br>h Start and Sto<br>node (slave Idle | op bit interrupts<br>p bit interrupts<br>e) |                      |                      |

|               |                                                                                                             |                                                                                                                    |                                                                                   |                                                          |                                             |                      |                      |

# REGISTER 18-4: SSPCON1: MSSP CONTROL REGISTER 1 (I<sup>2</sup>C<sup>™</sup> MODE)

- Note 1: When enabled, the SDA and SCL pins must be properly configured as input or output.

- 2: Bit combinations not specifically listed here are either reserved or implemented in SPI mode only.

| R/W-0        | R/W-0                      | R/W-0                             | R/W-0          | R/W-0            | R/W-0           | R-1             | R/W-0 |

|--------------|----------------------------|-----------------------------------|----------------|------------------|-----------------|-----------------|-------|

| CSRC         | TX9                        | TXEN <sup>(1)</sup>               | SYNC           | SENDB            | BRGH            | TRMT            | TX9D  |

| bit 7        |                            |                                   |                |                  |                 |                 | bit   |

|              |                            |                                   |                |                  |                 |                 |       |

| Legend:      |                            |                                   |                |                  |                 |                 |       |

| R = Readab   |                            | W = Writable                      |                |                  | nented bit, rea |                 |       |

| -n = Value a | t POR                      | '1' = Bit is set                  |                | '0' = Bit is cle | ared            | x = Bit is unki | nown  |

| bit 7        | CSRC: Cloc                 | k Source Select                   | bit            |                  |                 |                 |       |

|              | Asynchrono                 | us mode:                          |                |                  |                 |                 |       |

|              | Don't care.                |                                   |                |                  |                 |                 |       |

|              | <u>Synchronou</u>          |                                   |                |                  |                 |                 |       |

|              |                            | node (clock gen                   |                |                  |                 |                 |       |

| bit 6        |                            | ode (clock from<br>ransmit Enable |                | ce)              |                 |                 |       |

|              |                            | 9-bit transmissio                 |                |                  |                 |                 |       |

|              |                            | 8-bit transmissic                 |                |                  |                 |                 |       |

| bit 5        | TXEN: Tran                 | smit Enable bit <sup>(1</sup>     | )              |                  |                 |                 |       |

|              | 1 = Transmi                | t enabled                         |                |                  |                 |                 |       |

|              | 0 <b>= Transmi</b>         | t disabled                        |                |                  |                 |                 |       |

| bit 4        | SYNC: EUS                  | ART Mode Sele                     | ct bit         |                  |                 |                 |       |

|              | 1 = Synchro                |                                   |                |                  |                 |                 |       |

| bit 3        | -                          | onous mode<br>nd Break Chara      | otor hit       |                  |                 |                 |       |

| DIL S        | Asynchrono                 |                                   |                |                  |                 |                 |       |

|              |                            | nc Break on ne                    | xt transmissio | n (cleared by h  | ardware upon    | completion)     |       |

|              |                            | eak transmissior                  |                | ()               | F -             | ,               |       |

|              | <u>Synchronou</u>          | <u>s mode:</u>                    |                |                  |                 |                 |       |

|              | Don't care.                |                                   |                |                  |                 |                 |       |

| bit 2        | -                          | n Baud Rate Sel                   | ect bit        |                  |                 |                 |       |

|              | Asynchrono<br>1 = High spe |                                   |                |                  |                 |                 |       |

|              | 0 = Low spe                |                                   |                |                  |                 |                 |       |

|              | Synchronou                 |                                   |                |                  |                 |                 |       |

|              | Unused in th               | nis mode.                         |                |                  |                 |                 |       |

| bit 1        |                            | smit Shift Regist                 | er Status bit  |                  |                 |                 |       |

|              | 1 = TSR em                 |                                   |                |                  |                 |                 |       |

| L:1 0        | 0 = TSR full               |                                   | 10             |                  |                 |                 |       |

| bit 0        | Can be add                 | it of Transmit Da                 |                |                  |                 |                 |       |

|              |                            |                                   |                |                  |                 |                 |       |

### REGISTER 19-1: TXSTA: TRANSMIT STATUS AND CONTROL REGISTER

|              |                       |            |                             |                       | SYNC              | = 0, BRGH                   | <b>i =</b> 0, BRG     | i <b>16 =</b> 1 |                             |                       |            |                             |

|--------------|-----------------------|------------|-----------------------------|-----------------------|-------------------|-----------------------------|-----------------------|-----------------|-----------------------------|-----------------------|------------|-----------------------------|

| BAUD<br>RATE | Fosc                  | = 40.000   | ) MHz                       | Fosc                  | Fosc = 20.000 MHz |                             |                       | = 10.000        | ) MHz                       | Fosc = 8.000 MHz      |            |                             |

| (K)          | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error        | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error      | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) |

| 0.3          | 0.300                 | 0.00       | 8332                        | 0.300                 | 0.02              | 4165                        | 0.300                 | 0.02            | 2082                        | 0.300                 | -0.04      | 1665                        |

| 1.2          | 1.200                 | 0.02       | 2082                        | 1.200                 | -0.03             | 1041                        | 1.200                 | -0.03           | 520                         | 1.201                 | -0.16      | 415                         |

| 2.4          | 2.402                 | 0.06       | 1040                        | 2.399                 | -0.03             | 520                         | 2.404                 | 0.16            | 259                         | 2.403                 | -0.16      | 207                         |

| 9.6          | 9.615                 | 0.16       | 259                         | 9.615                 | 0.16              | 129                         | 9.615                 | 0.16            | 64                          | 9.615                 | -0.16      | 51                          |

| 19.2         | 19.231                | 0.16       | 129                         | 19.231                | 0.16              | 64                          | 19.531                | 1.73            | 31                          | 19.230                | -0.16      | 25                          |

| 57.6         | 58.140                | 0.94       | 42                          | 56.818                | -1.36             | 21                          | 56.818                | -1.36           | 10                          | 55.555                | 3.55       | 8                           |

| 115.2        | 113.636               | -1.36      | 21                          | 113.636               | -1.36             | 10                          | 125.000               | 8.51            | 4                           | —                     | _          | —                           |

### TABLE 19-3: BAUD RATES FOR ASYNCHRONOUS MODES (CONTINUED)

|             |                       |            | S                           | YNC = 0, E            | BRGH = (   | ), BRG16 =                  | 1                     |            |                             |  |

|-------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|--|

| BAUD        | Foso                  | = 4.000    | MHz                         | Fos                   | c = 2.000  | MHz                         | Fosc = 1.000 MHz      |            |                             |  |

| RATE<br>(K) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) |  |

| 0.3         | 0.300                 | 0.04       | 832                         | 0.300                 | -0.16      | 415                         | 0.300                 | -0.16      | 207                         |  |

| 1.2         | 1.202                 | 0.16       | 207                         | 1.201                 | -0.16      | 103                         | 1.201                 | -0.16      | 51                          |  |

| 2.4         | 2.404                 | 0.16       | 103                         | 2.403                 | -0.16      | 51                          | 2.403                 | -0.16      | 25                          |  |

| 9.6         | 9.615                 | 0.16       | 25                          | 9.615                 | -0.16      | 12                          | _                     | _          | _                           |  |

| 19.2        | 19.231                | 0.16       | 12                          | —                     | _          | _                           | _                     | _          | _                           |  |

| 57.6        | 62.500                | 8.51       | 3                           | —                     | _          | _                           | —                     | _          | _                           |  |

| 115.2       | 125.000               | 8.51       | 1                           | _                     | _          | —                           | _                     | _          | _                           |  |

|              |                       |            |                             | SYNC = 0,             | , BRGH =   | = 1, BRG16                  | = 1 or SY             | NC = 1,    | BRG16 = 1                   |                       |            |                             |

|--------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|

| BAUD<br>RATE | Fosc                  | = 40.000   | ) MHz                       | Fosc                  | = 20.000   | ) MHz                       | Fosc                  | = 10.000   | ) MHz                       | Fosc = 8.000 MHz      |            |                             |

| (K)          | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) |

| 0.3          | 0.300                 | 0.00       | 33332                       | 0.300                 | 0.00       | 16665                       | 0.300                 | 0.00       | 8332                        | 0.300                 | -0.01      | 6665                        |

| 1.2          | 1.200                 | 0.00       | 8332                        | 1.200                 | 0.02       | 4165                        | 1.200                 | 0.02       | 2082                        | 1.200                 | -0.04      | 1665                        |

| 2.4          | 2.400                 | 0.02       | 4165                        | 2.400                 | 0.02       | 2082                        | 2.402                 | 0.06       | 1040                        | 2.400                 | -0.04      | 832                         |

| 9.6          | 9.606                 | 0.06       | 1040                        | 9.596                 | -0.03      | 520                         | 9.615                 | 0.16       | 259                         | 9.615                 | -0.16      | 207                         |

| 19.2         | 19.193                | -0.03      | 520                         | 19.231                | 0.16       | 259                         | 19.231                | 0.16       | 129                         | 19.230                | -0.16      | 103                         |

| 57.6         | 57.803                | 0.35       | 172                         | 57.471                | -0.22      | 86                          | 58.140                | 0.94       | 42                          | 57.142                | 0.79       | 34                          |

| 115.2        | 114.943               | -0.22      | 86                          | 116.279               | 0.94       | 42                          | 113.636               | -1.36      | 21                          | 117.647               | -2.12      | 16                          |

|              |                       | SYN        | IC = 0, BR(                 | GH = 1, BF            | <b>RG16 =</b> 1 | or SYNC =                   | : 1, BRG1             | 6 = 1      |                             |  |

|--------------|-----------------------|------------|-----------------------------|-----------------------|-----------------|-----------------------------|-----------------------|------------|-----------------------------|--|

| BAUD<br>RATE | Foso                  | c = 4.000  | MHz                         | Fos                   | c = 2.000       | MHz                         | Fosc = 1.000 MHz      |            |                             |  |

| (K)          | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error      | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) |  |

| 0.3          | 0.300                 | 0.01       | 3332                        | 0.300                 | -0.04           | 1665                        | 0.300                 | -0.04      | 832                         |  |

| 1.2          | 1.200                 | 0.04       | 832                         | 1.201                 | -0.16           | 415                         | 1.201                 | -0.16      | 207                         |  |

| 2.4          | 2.404                 | 0.16       | 415                         | 2.403                 | -0.16           | 207                         | 2.403                 | -0.16      | 103                         |  |

| 9.6          | 9.615                 | 0.16       | 103                         | 9.615                 | -0.16           | 51                          | 9.615                 | -0.16      | 25                          |  |

| 19.2         | 19.231                | 0.16       | 51                          | 19.230                | -0.16           | 25                          | 19.230                | -0.16      | 12                          |  |

| 57.6         | 58.824                | 2.12       | 16                          | 55.555                | 3.55            | 8                           | —                     | —          | —                           |  |

| 115.2        | 111.111               | -3.55      | 8                           | _                     | _               | _                           | _                     | _          | _                           |  |

# 21.0 COMPARATOR MODULE

The analog comparator module contains two comparators that can be configured in a variety of ways. The inputs can be selected from the analog inputs multiplexed with pins, RA0 through RA5, as well as the on-chip voltage reference (see Section 22.0 "Comparator Voltage Reference Module"). The digital outputs (normal or inverted) are available at the pin level and can also be read through the control register.

The CMCON register (Register 21-1) selects the comparator input and output configuration. Block diagrams of the various comparator configurations are shown in Figure 21-1.

#### REGISTER 21-1: CMCON: COMPARATOR CONTROL REGISTER

| R-0           | R-0                                             | R/W-0                                   | R/W-0          | R/W-0            | R/W-0            | R/W-0           | R/W-0 |

|---------------|-------------------------------------------------|-----------------------------------------|----------------|------------------|------------------|-----------------|-------|

| C2OUT         | C1OUT                                           | C2INV                                   | C1INV          | CIS              | CM2              | CM1             | CM0   |

| bit 7         |                                                 |                                         |                |                  |                  |                 | bit 0 |

|               |                                                 |                                         |                |                  |                  |                 |       |

| Legend:       |                                                 |                                         |                |                  |                  |                 |       |

| R = Readabl   |                                                 | W = Writable                            |                | •                | mented bit, rea  |                 |       |

| -n = Value at | POR                                             | '1' = Bit is set                        |                | '0' = Bit is cle | ared             | x = Bit is unkr | nown  |

| h:+ <b>7</b>  |                                                 |                                         |                |                  |                  |                 |       |

| bit 7         | When C2INV                                      | nparator 2 Outp                         |                |                  |                  |                 |       |

|               | 1 = C2 VIN+3                                    |                                         |                |                  |                  |                 |       |

|               | 0 = C2 VIN+                                     | -                                       |                |                  |                  |                 |       |

|               | When C2INV                                      | <u>/ = 1:</u>                           |                |                  |                  |                 |       |

|               | 1 = C2 VIN+                                     | < C2 VIN-                               |                |                  |                  |                 |       |

|               | 0 = C2 VIN+                                     | > C2 VIN-                               |                |                  |                  |                 |       |

| bit 6         | C1OUT: Com                                      | parator 1 Outp                          | ut bit         |                  |                  |                 |       |

|               | When C1INV                                      |                                         |                |                  |                  |                 |       |

|               | 1 = C1 VIN+<br>0 = C1 VIN+                      |                                         |                |                  |                  |                 |       |

|               | When C1INV                                      |                                         |                |                  |                  |                 |       |

|               | 1 = C1 VIN+                                     |                                         |                |                  |                  |                 |       |

|               | 0 = C1 VIN+                                     | > C1 VIN-                               |                |                  |                  |                 |       |

| bit 5         | C2INV: Com                                      | parator 2 Outpu                         | t Inversion bi | t                |                  |                 |       |

|               | 1 <b>= C2 outpu</b>                             |                                         |                |                  |                  |                 |       |

|               | •                                               | it not inverted                         |                |                  |                  |                 |       |

| bit 4         |                                                 | parator 1 Outpu                         | t Inversion bi | t                |                  |                 |       |

|               | 1 = C1 outpu                                    |                                         |                |                  |                  |                 |       |

|               | •                                               | it not inverted                         |                |                  |                  |                 |       |

| bit 3         | -                                               | ator Input Swite                        | h bit          |                  |                  |                 |       |

|               | $\frac{\text{When CM} < 2}{1 - C1 \text{ Vis}}$ | : <u>0&gt; = 110:</u><br>connects to RD |                | LL.              |                  |                 |       |

|               |                                                 | connects to RD                          |                |                  |                  |                 |       |

|               | -                                               | connects to RD                          |                |                  |                  |                 |       |

|               | C2 VIN-                                         | connects to RD                          | 3/PSP3/C2IN    | -                |                  |                 |       |

| bit 2-0       | CM<2:0>: Co                                     | omparator Mode                          | e bits         |                  |                  |                 |       |

|               | Figure 21-1                                     | shows the Com                           | parator mode   | s and the CM<    | 2:0> bit setting | S.              |       |

|               |                                                 |                                         |                |                  |                  |                 |       |

### 23.0 HIGH/LOW-VOLTAGE DETECT (HLVD)

PIC18F2480/2580/4480/4580 devices have a High/Low-Voltage Detect module (HLVD). This is a programmable circuit that allows the user to specify both a device voltage trip point and the direction of change from that point. If the device experiences an excursion past the trip point in that direction, an interrupt flag is set. If the interrupt is enabled, the program execution will branch to the interrupt vector address and the software can then respond to the interrupt.

The High/Low-Voltage Detect Control register (Register 23-1) completely controls the operation of the HLVD module. This allows the circuitry to be "turned off" by the user under software control, which minimizes the current consumption for the device.

The block diagram for the HLVD module is shown in Figure 23-1.

### REGISTER 23-1: HLVDCON: HIGH/LOW-VOLTAGE DETECT CONTROL REGISTER

| R/W-0             | U-0                           | R-0              | R/W-0           | R/W-0                              | R/W-1                 | R/W-0                 | R/W-1                 |

|-------------------|-------------------------------|------------------|-----------------|------------------------------------|-----------------------|-----------------------|-----------------------|

| VDIRMAG           |                               | IRVST            | HLVDEN          | HLVDL3 <sup>(1)</sup>              | HLVDL2 <sup>(1)</sup> | HLVDL1 <sup>(1)</sup> | HLVDL0 <sup>(1)</sup> |

| bit 7             |                               |                  |                 |                                    |                       |                       | bit 0                 |

|                   |                               |                  |                 |                                    |                       |                       | 1                     |

| Legend:           |                               |                  |                 |                                    |                       |                       |                       |

| R = Readable      |                               | W = Writable     |                 | -                                  | nented bit, read      |                       |                       |

| -n = Value at POR |                               | '1' = Bit is set |                 | '0' = Bit is cle                   | ared                  | x = Bit is unkr       | nown                  |

| h:+ 7             |                               | altara Directia  | . Magaituda (   | Calaat hit                         |                       |                       |                       |

| bit 7             |                               | oltage Direction | -               |                                    | oint (HLVDL<3:0       |                       |                       |

|                   |                               |                  |                 |                                    | point (HLVDL<         |                       |                       |

| bit 6             |                               | ted: Read as '   |                 |                                    |                       | /                     |                       |

| bit 5             | IRVST: Interna                | al Reference V   | oltage Stable   | Flag bit                           |                       |                       |                       |

|                   | 1 = Indicates                 | that the voltag  | e detect logic  | will generate th                   | e interrupt flag      | at the specified      | voltage range         |

|                   |                               |                  |                 | c will not gener<br>not be enabled | ate the interrup      | t flag at the sp      | ecified voltage       |

| bit 4             | HLVDEN: Hig                   | h/Low-Voltage    | Detect Powe     | r Enable bit                       |                       |                       |                       |

|                   | 1 = HLVD en                   |                  |                 |                                    |                       |                       |                       |

|                   | 0 = HLVD dis                  |                  |                 | (1)                                |                       |                       |                       |

| bit 3-0           |                               | : High/Low-Vol   | •               |                                    |                       |                       |                       |

|                   | 1111 = Extern<br>1110 = 4.48V | <b>v</b> ,       | it is used (inp | ut comes from                      | the HLVDIN pir        | 1)                    |                       |

|                   | 1101 <b>= 4.23</b> V          |                  |                 |                                    |                       |                       |                       |

|                   | 1100 <b>= 4.01V</b>           |                  |                 |                                    |                       |                       |                       |

|                   | 1011 = 3.81V                  |                  |                 |                                    |                       |                       |                       |

|                   | 1010 = 3.63V<br>1001 = 3.46V  |                  |                 |                                    |                       |                       |                       |

|                   | 1000 = 3.31V                  |                  |                 |                                    |                       |                       |                       |

|                   | 0111 <b>= 3.05V</b>           |                  |                 |                                    |                       |                       |                       |

|                   | 0110 = 2.82V                  |                  |                 |                                    |                       |                       |                       |

|                   | 0101 = 2.72V<br>0100 = 2.54V  |                  |                 |                                    |                       |                       |                       |

|                   | 0011 = 2.38V                  |                  |                 |                                    |                       |                       |                       |

|                   | 0010 <b>= 2.31V</b>           |                  |                 |                                    |                       |                       |                       |

|                   | 0001 = 2.18V                  | -                |                 |                                    |                       |                       |                       |

|                   | 0000 <b>= 2.12V</b>           | -2.22V           |                 |                                    |                       |                       |                       |

Note 1: HLVDL<3:0> modes that result in a trip point below the valid operating voltage of the device are not tested.

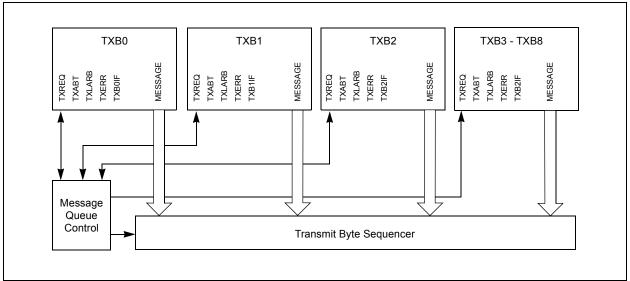

### 24.6.3 TRANSMIT PRIORITY

Transmit priority is a prioritization within the PIC18F2480/2580/4480/4580 devices of the pending transmittable messages. This is independent from and not related to any prioritization implicit in the message arbitration scheme built into the CAN protocol. Prior to sending the Start-Of-Frame (SOF), the priority of all buffers that are queued for transmission is compared.

The transmit buffer with the highest priority will be sent first. If two buffers have the same priority setting, the buffer with the highest buffer number will be sent first. There are four levels of transmit priority. If the TXP bits for a particular message buffer are set to '11', that buffer has the highest possible priority. If the TXP bits for a particular message buffer are set to '00', that buffer has the lowest possible priority.

# REGISTER 25-1: CONFIG1H: CONFIGURATION REGISTER 1 HIGH (BYTE ADDRESS 300001h)

| R/P-0        | R/P-0                                                                                                                 | U-0                                                                          | U-0             | R/P-0         | R/P-1            | R/P-1      | R/P-1 |  |  |  |