Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 40 MIPs                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                     |

| Number of I/O              | 21                                                                             |

| Program Memory Size        | 128KB (43K x 24)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 8K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                      |

| Data Converters            | A/D 10x10b/12b                                                                 |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                             |

| Mounting Type              | Through Hole                                                                   |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                        |

| Supplier Device Package    | 28-SPDIP                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24hj128gp202-e-sp |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 3.4 CPU Resources

Many useful resources related to the CPU are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the |

|-------|---------------------------------------------|

|       | product page using the link above, enter    |

|       | this URL in your browser:                   |

|       | http://www.microchip.com/wwwproducts/       |

|       | Devices.aspx?dDocName=en534555              |

#### 3.4.1 KEY RESOURCES

- Section 2. "CPU" (DS70204)

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All related dsPIC33F/PIC24H Family Reference Manuals Sections

- Development Tools

| File Name  | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6    | Bit 5 | Bit 4                                                                                                  | Bit 3 | Bit 2 | Bit 1                                                                                    | Bit 0 | All<br>Resets |  |

|------------|------|--------|--------|--------|--------|--------|--------|-------|-------|-------|----------|-------|--------------------------------------------------------------------------------------------------------|-------|-------|------------------------------------------------------------------------------------------|-------|---------------|--|

| C1RXF11SID | 046C |        |        |        | SID<   | 10:3>  |        |       |       |       | SID<2:0> |       | -                                                                                                      | EXIDE | —     | EID<1                                                                                    | 7:16> | XXXX          |  |

| C1RXF11EID | 046E |        |        |        | EID<   | 15:8>  |        |       |       |       |          |       | EID<                                                                                                   | 7:0>  |       |                                                                                          |       | xxxx          |  |

| C1RXF12SID | 0470 |        |        |        | SID<   | 10:3>  |        |       |       |       | SID<2:0> |       | —                                                                                                      | EXIDE |       | EID<1                                                                                    | 7:16> | XXXX          |  |

| C1RXF12EID | 0472 |        |        |        | EID<   | 15:8>  |        |       |       |       |          |       | —         EXIDE         —         EID<17:16>           EID<7:0>         —         EID<17:16>         — |       |       |                                                                                          |       |               |  |

| C1RXF13SID | 0474 |        |        |        | SID<   | 10:3>  |        |       |       |       | SID<2:0> |       | —                                                                                                      | EXIDE |       | <ul> <li>EID&lt;17:16&gt;</li> <li>EID&lt;17:16&gt;</li> <li>EID&lt;17:16&gt;</li> </ul> |       |               |  |

| C1RXF13EID | 0476 |        |        |        | EID<   | 15:8>  |        |       |       |       |          |       | EID<                                                                                                   | 7:0>  | XXXX  |                                                                                          |       |               |  |

| C1RXF14SID | 0478 |        |        |        | SID<   | 10:3>  |        |       |       |       | SID<2:0> |       | —                                                                                                      | EXIDE |       | EID<1                                                                                    | 7:16> | XXXX          |  |

| C1RXF14EID | 047A |        |        |        | EID<   | 15:8>  |        |       |       |       |          |       | EID<                                                                                                   | 7:0>  |       |                                                                                          |       | XXXX          |  |

| C1RXF15SID | 047C |        |        |        | SID<   | 10:3>  |        |       |       |       | SID<2:0> |       | —                                                                                                      | EXIDE | _     | EID<1                                                                                    | 7:16> | XXXX          |  |

| C1RXF15EID | 047E |        |        |        | EID<   | 15:8>  |        |       |       |       |          |       | EID<                                                                                                   | 7:0>  |       |                                                                                          |       | XXXX          |  |

#### TABLE 4-18: ECAN1 REGISTER MAP WHEN C1CTRL1.WIN = 1 (FOR PIC24HJ128GP502/504 AND PIC24HJ64GP502/504) (CONTINUED)

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-19: PERIPHERAL PIN SELECT INPUT REGISTER MAP

| File Name              | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10     | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4                   | Bit 3 | Bit 2      | Bit 1 | Bit 0 | All<br>Resets |

|------------------------|------|--------|--------|--------|--------|--------|------------|-------|-------|-------|-------|-------|-------------------------|-------|------------|-------|-------|---------------|

| RPINR0                 | 0680 | _      | _      | —      |        |        | INT1R<4:0> |       |       | _     | _     | -     | _                       | —     | —          | —     | —     | 1F00          |

| RPINR1                 | 0682 | -      | _      | _      | _      | _      | _          | _     | _     |       |       | _     |                         |       | INT2R<4:02 | >     |       | 001F          |

| RPINR3                 | 0686 | _      |        | _      |        |        | T3CKR<4:0> |       |       | _     | -     | -     |                         |       | T2CKR<4:0  | >     |       | 1F1F          |

| RPINR4                 | 0688 | _      | _      | _      |        |        | T5CKR<4:0> |       |       | _     | _     | _     |                         |       | T4CKR<4:0  | >     |       | 1F1F          |

| RPINR7                 | 068E | _      | _      | _      |        |        | IC2R<4:0>  |       |       | -     | -     | _     |                         |       | IC1R<4:0>  |       |       | 1F1F          |

| RPINR10                | 0694 | _      | _      | _      |        |        | IC8R<4:0>  |       |       | _     | _     | _     | IC7R<4:0><br>OCFAR<4:0> |       |            |       |       | 1F1F          |

| RPINR11                | 0696 | _      | _      | _      | _      | _      | _          | _     | _     | -     | -     | _     |                         |       | OCFAR<4:0  | )>    |       | 001F          |

| RPINR18                | 06A4 | -      | _      | _      |        |        | U1CTSR<4:0 | >     |       |       | -     | _     |                         |       | U1RXR<4:0  | >     |       | 1F1F          |

| RPINR19                | 06A6 | -      | _      | _      |        |        | U2CTSR<4:0 | >     |       |       |       | _     |                         |       | U2RXR<4:0  | >     |       | 1F1F          |

| RPINR20                | 06A8 | -      | _      | _      |        |        | SCK1R<4:0> |       |       |       | -     | _     |                         |       | SDI1R<4:0  | >     |       | 1F1F          |

| RPINR21                | 06AA | -      | _      | _      | _      | _      | _          | _     | _     |       |       | _     |                         |       | SS1R<4:0>  | >     |       | 001F          |

| RPINR22                | 06AC | -      | _      | _      |        |        | SCK2R<4:0> |       |       |       | -     | _     | SDI2R<4:0>              |       |            |       | 1F1F  |               |

| RPINR23                | 06AE | _      | _      | _      | _      | _      | _          | _     | _     | _     |       | _     |                         |       | SS2R<4:0>  | >     |       | 001F          |

| RPINR26 <sup>(1)</sup> | 06B4 | _      |        | _      | _      | _      | _          | _     | _     |       | _     | _     |                         |       | C1RXR<4:0  | >     |       | 001F          |

**nd:** x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This register is present for PIC24HJ128GP502/504 and PIC24HJ64GP502/504 devices only.

# TABLE 4-20:PERIPHERAL PIN SELECT OUTPUT REGISTER MAP FOR PIC24HJ128GP202/502, PIC24HJ64GP202/502 AND<br/>PIC24HJ32GP302

| File Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10    | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2      | Bit 1 | Bit 0 | All<br>Resets |

|-----------|------|--------|--------|--------|--------|--------|-----------|-------|-------|-------|-------|-------|-------|-------|------------|-------|-------|---------------|

| RPOR0     | 06C0 | -      | _      | —      |        |        | RP1R<4:0  | >     |       | —     | —     | —     |       |       | RP0R<4:0>  |       |       | 0000          |

| RPOR1     | 06C2 | _      | _      | _      |        |        | RP3R<4:0  | >     |       | _     | _     | _     |       |       | RP2R<4:0>  |       |       | 0000          |

| RPOR2     | 06C4 |        | —      | _      |        |        | RP5R<4:0> | >     |       | _     | —     | _     |       |       | RP4R<4:0>  |       |       | 0000          |

| RPOR3     | 06C6 |        | _      | _      |        |        | RP7R<4:0> | >     |       | _     | _     | _     |       |       | RP6R<4:0>  |       |       | 0000          |

| RPOR4     | 06C8 | -      | _      | _      |        |        | RP9R<4:0> | >     |       | —     | _     | _     |       |       | RP8R<4:0>  |       |       | 0000          |

| RPOR5     | 06CA | _      | _      | _      |        |        | RP11R<4:0 | >     |       | _     | _     | _     |       | I     | RP10R<4:0> |       |       | 0000          |

| RPOR6     | 06CC |        | —      | _      |        |        | RP13R<4:0 | >     |       | _     | —     | —     |       | I     | RP12R<4:0> |       |       | 0000          |

| RPOR7     | 06CE | -      | _      | _      |        |        | RP15R<4:0 | >     |       | _     | _     | _     |       | I     | RP14R<4:0> |       |       | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# TABLE 4-21:PERIPHERAL PIN SELECT OUTPUT REGISTER MAP FOR PIC24HJ128GP204/504, PIC24HJ64GP204/504 AND<br/>PIC24HJ32GP304

|           |      |        |        |        |        |        |           |          |       |       |       |       |            |                                       |            | -     |       |               |

|-----------|------|--------|--------|--------|--------|--------|-----------|----------|-------|-------|-------|-------|------------|---------------------------------------|------------|-------|-------|---------------|

| File Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10    | Bit 9    | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4      | Bit 3                                 | Bit 2      | Bit 1 | Bit 0 | All<br>Resets |

| RPOR0     | 06C0 | _      | _      | _      |        |        | RP1R<4:0> | >        |       | _     | _     |       |            |                                       | RP0R<4:0>  |       |       | 0000          |

| RPOR1     | 06C2 | _      | _      | _      |        |        | RP3R<4:0> | >        |       | _     | _     | _     |            |                                       | RP2R<4:0>  |       |       | 0000          |

| RPOR2     | 06C4 | _      | _      | _      |        |        | RP5R<4:0> | >        |       | _     | _     | _     |            |                                       | RP4R<4:0>  |       |       | 0000          |

| RPOR3     | 06C6 | _      | _      |        |        |        | RP7R<4:0> | <b>`</b> |       | _     | _     | _     |            |                                       | RP6R<4:0>  |       |       | 0000          |

| RPOR4     | 06C8 |        |        | _      |        |        | RP9R<4:0> | >        |       | _     |       | _     |            |                                       | RP8R<4:0>  |       |       | 0000          |

| RPOR5     | 06CA |        |        | _      |        |        | RP11R<4:0 | >        |       | _     |       | _     |            | RP8R<4:0><br>RP10R<4:0><br>RP12R<4:0> |            |       |       | 0000          |

| RPOR6     | 06CC |        |        |        |        |        | RP13R<4:0 | >        |       | _     |       |       |            |                                       | RP12R<4:0> | >     |       | 0000          |

| RPOR7     | 06CE | _      | _      | _      |        |        | RP15R<4:0 | >        |       | _     | _     | _     |            |                                       | RP14R<4:0> | >     |       | 0000          |

| RPOR8     | 06D0 | _      | _      | _      |        |        | RP17R<4:0 | >        |       | _     | _     | _     |            |                                       | RP16R<4:0> | >     |       | 0000          |

| RPOR9     | 06D2 |        |        |        |        |        | RP19R<4:0 | >        |       | _     | _     |       |            |                                       | RP18R<4:0> | >     |       | 0000          |

| RPOR10    | 06D4 |        |        |        |        |        | RP21R<4:0 | >        |       | _     | _     |       |            |                                       | RP20R<4:0> | >     |       | 0000          |

| RPOR11    | 06D6 | _      |        |        |        |        | RP23R<4:0 | >        |       | _     | _     |       | RP22R<4:0> |                                       |            |       |       | 0000          |

| RPOR12    | 06D8 |        | _      | _      |        |        | RP25R<4:0 | >        |       | _     | _     |       |            |                                       | RP24R<4:0> | >     |       | 0000          |

Legend: x = unknown value on Reset, -- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| File Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|-----------|------|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|-------|--------|--------|--------|---------------|

| BSRAM     | 0750 | _      | —      | _      |        |        | —      | -     | -     | —     | _     |       | _     | -     | IW_BSR | IR_BSR | RL_BSR | 0000          |

| SSRAM     | 0752 | _      | _      | _      | —      | —      | —      | -     | -     | —     | —     | —     | —     | —     | IW_SSR | IR_SSR | RL_SSR | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This register is not present in devices with 32K Flash (PIC24HJ32GP302/304).

#### TABLE 4-33: NVM REGISTER MAP

| File Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3   | Bit 2 | Bit 1  | Bit 0 | All<br>Resets |

|-----------|------|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|---------|-------|--------|-------|---------------|

| NVMCON    | 0760 | WR     | WREN   | WRERR  | —      | —      | —      | —     | —     | _     | ERASE | _     | -     |         | NVMO  | P<3:0> |       | 0000          |

| NVMKEY    | 0766 |        | —      | _      | —      | —      | —      |       |       |       |       |       | NVMKE | EY<7:0> |       |        |       | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-34: PMD REGISTER MAP

| File Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8 | Bit 7  | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-----------|------|--------|--------|--------|--------|--------|--------|--------|-------|--------|-------|-------|--------|--------|-------|-------|-------|---------------|

| PMD1      | 0770 | T5MD   | T4MD   | T3MD   | T2MD   | T1MD   | _      | _      | —     | I2C1MD | U2MD  | U1MD  | SPI2MD | SPI1MD | —     | C1MD  | AD1MD | 0000          |

| PMD2      | 0772 | IC8MD  | IC7MD  | _      | _      | _      | _      | IC2MD  | IC1MD | _      | _     | _     | _      | OC4MD  | OC3MD | OC2MD | OC1MD | 0000          |

| PMD3      | 0774 | _      | _      | _      | _      | _      | CMPMD  | RTCCMD | PMPMD | CRCMD  | _     | _     | _      | _      | _     | _     | _     | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| Symbol | Parameter                        | Value            |

|--------|----------------------------------|------------------|

| VPOR   | POR threshold                    | 1.8V nominal     |

| TPOR   | POR extension time               | 30 μs maximum    |

| VBOR   | BOR threshold                    | 2.5V nominal     |

| TBOR   | BOR extension time               | 100 μs maximum   |

| TPWRT  | Programmable power-up time delay | 0-128 ms nominal |

| TFSCM  | Fail-Safe Clock Monitor Delay    | 900 μs maximum   |

|  | <b>TABLE 6-2</b> : | OSCILLATOR DELAY |

|--|--------------------|------------------|

|--|--------------------|------------------|

Note: When the device exits the Reset condition (begins normal operation), the device operating parameters (voltage, frequency, temperature, etc.) must be within their operating ranges, otherwise the device may not function correctly. The user application must ensure that the delay between the time power is first applied, and the time SYSRST becomes inactive, is long enough to get operating parameters within all specification.

#### 6.4 **Power-on Reset (POR)**

A Power-on Reset (POR) circuit ensures the device is reset from power-on. The POR circuit is active until VDD crosses the VPOR threshold and the delay TPOR has elapsed. The delay TPOR ensures the internal device bias circuits become stable.

The device supply voltage characteristics must meet the specified starting voltage and rise rate requirements to generate the POR. Refer to Section 28.0 "Electrical Characteristics" for details.

The POR status bit (POR) in the Reset Control register (RCON<0>) is set to indicate the Power-on Reset.

### 6.4.1 Brown-out Reset (BOR) and Power-up timer (PWRT)

The on-chip regulator has a Brown-out Reset (BOR) circuit that resets the device when the VDD is too low (VDD < VBOR) for proper device operation. The BOR circuit keeps the device in Reset until VDD crosses VBOR threshold and the delay TBOR has elapsed. The delay TBOR ensures the voltage regulator output becomes stable.

The Brown-out Reset status bit (BOR) in the Reset Control register (RCON<1>) is set to indicate the BOR.

The device will not run at full speed after a BOR as the VDD should rise to acceptable levels for full-speed operation. The PWRT provides power-up time delay (TPWRT) to ensure that the system power supplies have stabilized at the appropriate levels for full-speed operation before the SYSRST is released.

The power-up timer delay (TPWRT) is programmed by the Power-on Reset Timer Value Select bits (FPWRT<2:0>) in the POR Configuration register (FPOR<2:0>), which provides eight settings (from 0 ms to 128 ms). Refer to **Section 25.0 "Special Features"** for further details.

Figure 6-3 shows the typical brown-out scenarios. The reset delay (TBOR + TPWRT) is initiated each time VDD rises above the VBOR trip point

| U-0          | R/W-1        | R/W-0                                   | R/W-0           | U-0               | R/W-1          | R/W-0           | R/W-0 |

|--------------|--------------|-----------------------------------------|-----------------|-------------------|----------------|-----------------|-------|

| _            |              | T1IP<2:0>                               |                 | —                 |                | OC1IP<2:0>      |       |

| bit 15       |              |                                         |                 |                   |                |                 | bit 8 |

|              |              |                                         |                 |                   |                |                 |       |

| U-0          | R/W-1        | R/W-0                                   | R/W-0           | U-0               | R/W-1          | R/W-0           | R/W-0 |

| _            |              | IC1IP<2:0>                              |                 |                   |                | INT0IP<2:0>     |       |

| bit 7        |              |                                         |                 |                   |                |                 | bit C |

| Legend:      |              |                                         |                 |                   |                |                 |       |

| R = Readab   | le bit       | W = Writable I                          | oit             | U = Unimple       | mented bit, re | ad as '0'       |       |

| -n = Value a | It POR       | '1' = Bit is set                        |                 | '0' = Bit is cle  |                | x = Bit is unkn | own   |

|              |              |                                         |                 |                   |                |                 |       |

| bit 15       | Unimpleme    | ented: Read as '                        | )'              |                   |                |                 |       |

| bit 14-12    | T1IP<2:0>:   | Timer1 Interrupt                        | Priority bits   |                   |                |                 |       |

|              | 111 = Interr | upt is priority 7 (ł                    | nighest priorit | y interrupt)      |                |                 |       |

|              | •            |                                         |                 |                   |                |                 |       |

|              | •            |                                         |                 |                   |                |                 |       |

|              |              | upt is priority 1                       |                 |                   |                |                 |       |

|              |              | upt source is dis                       |                 |                   |                |                 |       |

| bit 11       | -            | ented: Read as '                        |                 |                   |                |                 |       |

| bit 10-8     |              | >: Output Compa                         |                 |                   | rity bits      |                 |       |

|              | 111 = Interr | upt is priority 7 (I                    | highest priorit | y interrupt)      |                |                 |       |

|              | •            |                                         |                 |                   |                |                 |       |

|              | •            |                                         |                 |                   |                |                 |       |

|              |              | upt is priority 1<br>upt source is disa | ahled           |                   |                |                 |       |

| bit 7        |              | ented: Read as '                        |                 |                   |                |                 |       |

| bit 6-4      | •            | : Input Capture C                       |                 | errupt Priority b | oits           |                 |       |

|              |              | upt is priority 7 (I                    |                 |                   |                |                 |       |

|              | •            |                                         |                 |                   |                |                 |       |

|              | •            |                                         |                 |                   |                |                 |       |

|              |              | upt is priority 1                       |                 |                   |                |                 |       |

|              |              | upt source is dis                       | abled           |                   |                |                 |       |

| bit 3        | Unimpleme    | ented: Read as '                        | )'              |                   |                |                 |       |

| bit 2-0      | INT0IP<2:0   | >: External Interr                      | upt 0 Priority  | bits              |                |                 |       |

|              | 111 = Interr | upt is priority 7 (I                    | nighest priorit | y interrupt)      |                |                 |       |

|              | •            |                                         |                 |                   |                |                 |       |

|              | •            |                                         |                 |                   |                |                 |       |

|              |              |                                         |                 |                   |                |                 |       |

001 = Interrupt is priority 1 000 = Interrupt source is disabled

#### REGISTER 11-7: RPINR11: PERIPHERAL PIN SELECT INPUT REGISTER 11

| U-0                             | U-0 | U-0                                    | U-0        | U-0              | U-0   | U-0             | U-0   |

|---------------------------------|-----|----------------------------------------|------------|------------------|-------|-----------------|-------|

| _                               |     | -                                      | _          | —                | —     | —               | —     |

| bit 15                          |     |                                        |            |                  |       |                 | bit 8 |

|                                 |     |                                        |            |                  |       |                 |       |

| U-0                             | U-0 | U-0                                    | R/W-1      | R/W-1            | R/W-1 | R/W-1           | R/W-1 |

| _                               | _   | _                                      | OCFAR<4:0> |                  |       |                 |       |

| bit 7                           |     |                                        |            |                  |       |                 | bit 0 |

|                                 |     |                                        |            |                  |       |                 |       |

| Legend:                         |     |                                        |            |                  |       |                 |       |

| R = Readable bit W = Writable b |     | bit U = Unimplemented bit, read as '0' |            |                  |       |                 |       |

| -n = Value at P                 | OR  | '1' = Bit is set                       |            | '0' = Bit is cle | ared  | x = Bit is unki | nown  |

| •                               |     |                                        |            |                  |       |                 |       |

bit 15-5 Unimplemented: Read as '0'

| bit 4-0 | <b>OCFAR&lt;4:0&gt;:</b> Assign Output Compare A (OCFA) to the corresponding RPn pin |

|---------|--------------------------------------------------------------------------------------|

| DIL 4-0 | OCIAN 4.0/. Assign Output Compare A (OCIA) to the corresponding IV in pin            |

11111 = Input tied to Vss 11001 = Input tied to RP25

.

• 00001 = Input tied to RP1 00000 = Input tied to RP0

| REGISTER     |                       | R19: PERIPHE                       | _                    |                |                 | -               |       |

|--------------|-----------------------|------------------------------------|----------------------|----------------|-----------------|-----------------|-------|

| U-0          | U-0                   | U-0                                | R/W-1                | R/W-1          | R/W-1           | R/W-1           | R/W-1 |

| —            | —                     | —                                  |                      |                | U2CTSR<4:       | )>              |       |

| bit 15       |                       |                                    |                      |                |                 |                 | bit 8 |

| U-0          | U-0                   | U-0                                | R/W-1                | R/W-1          | R/W-1           | R/W-1           | R/W-1 |

| _            | _                     | _                                  |                      |                | U2RXR<4:0       | >               |       |

| bit 7        |                       |                                    |                      |                |                 |                 | bit ( |

| Legend:      |                       |                                    |                      |                |                 |                 |       |

| R = Readab   | le bit                | W = Writable b                     | bit                  | U = Unimple    | mented bit, rea | ad as '0'       |       |

| -n = Value a | t POR                 | '1' = Bit is set                   | et '0' = Bit is clea |                | eared           | x = Bit is unkı | nown  |

|              | •<br>•<br>00001 = Inp | ut tied to RP25                    |                      |                |                 |                 |       |

| bit 7-5      | •                     | ut tied to RP0<br>nted: Read as '0 | ,                    |                |                 |                 |       |

| bit 4-0      | •                     | >: Assign UART2                    |                      | 2RX) to the co | rresponding R   | Pn nin          |       |

| 511 4-0      | 11111 <b>= Inp</b>    | ut tied to Vss<br>ut tied to RP25  |                      |                |                 | i ii piii       |       |

|              | •                     |                                    |                      |                |                 |                 |       |

|              | •                     |                                    |                      |                |                 |                 |       |

|              | •                     |                                    |                      |                |                 |                 |       |

|              |                       | ut tied to RP1                     |                      |                |                 |                 |       |

00000 = Input tied to RP0

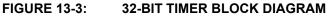

#### 13.3 Timer Resources

Many useful resources related to Timers are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

Note: In the event you are not able to access the product page using the link above, enter this URL in your browser: http://www.microchip.com/wwwproducts/ Devices.aspx?dDocName=en532315

#### 13.3.1 KEY RESOURCES

- Section 11. "Timers" (DS70205)

- Code Samples

- Application Notes

- Software Libraries

- · Webinars

- All related dsPIC33F/PIC24H Family Reference Manuals Sections

- Development Tools

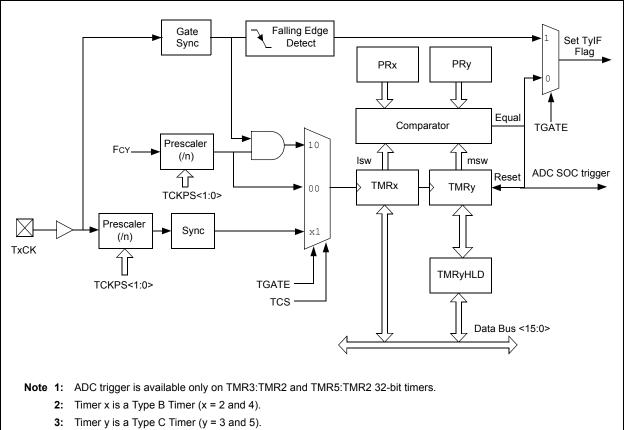

#### 15.1 Output Compare Modes

Configure the Output Compare modes by setting the appropriate Output Compare Mode bits (OCM<2:0>) in the Output Compare Control register (OCxCON<2:0>). Table 15-1 lists the different bit settings for the Output Compare modes. Figure 15-2 illustrates the output compare operation for various modes. The user application must disable the associated timer when writing to the output compare control registers to avoid malfunctions.

| TABLE 15-1: | <b>OUTPUT COMPARE MODES</b> |

|-------------|-----------------------------|

|-------------|-----------------------------|

- Note 1: Only OC1 and OC2 can trigger a DMA data transfer.

- 2: See Section 13. "Output Compare" (DS70209) in the "dsPIC33F/PIC24H Family Reference Manual" for OCxR and OCxRS register restrictions.

| OCM<2:0> | Mode                                 | OCx Pin Initial State                        | OCx Interrupt Generation         |

|----------|--------------------------------------|----------------------------------------------|----------------------------------|

| 000      | Module Disabled                      | Controlled by GPIO register                  | —                                |

| 001      | Active-Low One-Shot                  | 0                                            | OCx Rising edge                  |

| 010      | Active-High One-Shot                 | 1                                            | OCx Falling edge                 |

| 011      | Toggle Mode                          | Current output is maintained                 | OCx Rising and Falling edge      |

| 100      | Delayed One-Shot                     | 0                                            | OCx Falling edge                 |

| 101      | Continuous Pulse mode                | 0                                            | OCx Falling edge                 |

| 110      | PWM mode without fault<br>protection | 0, if OCxR is zero<br>1, if OCxR is non-zero | No interrupt                     |

| 111      | PWM mode with fault protection       | 0, if OCxR is zero<br>1, if OCxR is non-zero | OCFA Falling edge for OC1 to OC4 |

| U-0                 | U-0                                                                                                                                | U-0                                                  | R/W-0                  | R/W-0              | R/W-0              | R/W-0            | R/W-0                |  |  |  |

|---------------------|------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|------------------------|--------------------|--------------------|------------------|----------------------|--|--|--|

|                     |                                                                                                                                    | _                                                    | DISSCK                 | DISSDO             | MODE16             | SMP              | CKE <sup>(1)</sup>   |  |  |  |

| oit 15              |                                                                                                                                    |                                                      |                        |                    |                    | •                | bit                  |  |  |  |

|                     |                                                                                                                                    |                                                      |                        |                    |                    |                  |                      |  |  |  |

| R/W-0               | R/W-0                                                                                                                              | R/W-0                                                | R/W-0                  | R/W-0              | R/W-0              | R/W-0            | R/W-0                |  |  |  |

| SSEN <sup>(3)</sup> | CKP                                                                                                                                | MSTEN                                                |                        | SPRE<2:0>(2        | 2)                 | PPRE             | <1:0> <sup>(2)</sup> |  |  |  |

| bit 7               |                                                                                                                                    | ·                                                    | •                      |                    |                    |                  | bit                  |  |  |  |

|                     |                                                                                                                                    |                                                      |                        |                    |                    |                  |                      |  |  |  |

| Legend:             |                                                                                                                                    |                                                      |                        |                    |                    |                  |                      |  |  |  |

| R = Readab          | le bit                                                                                                                             | W = Writable                                         | bit                    | U = Unimpler       | mented bit, read   | l as '0'         |                      |  |  |  |

| -n = Value a        | t POR                                                                                                                              | '1' = Bit is set                                     |                        | '0' = Bit is cle   | ared               | x = Bit is unkr  | nown                 |  |  |  |

|                     |                                                                                                                                    |                                                      |                        |                    |                    |                  |                      |  |  |  |

| bit 15-13           | •                                                                                                                                  | nted: Read as '                                      |                        |                    |                    |                  |                      |  |  |  |

| bit 12              |                                                                                                                                    | sable SCKx pin<br>SPI clock is disa                  |                        |                    |                    |                  |                      |  |  |  |

|                     |                                                                                                                                    | SPI clock is ena                                     |                        |                    |                    |                  |                      |  |  |  |

| bit 11              | DISSDO: Di                                                                                                                         | sable SDOx pin                                       | bit                    |                    |                    |                  |                      |  |  |  |

|                     | <ul> <li>1 = SDOx pin is not used by module; pin functions as I/O</li> <li>0 = SDOx pin is controlled by the module</li> </ul>     |                                                      |                        |                    |                    |                  |                      |  |  |  |

|                     | -                                                                                                                                  |                                                      | -                      |                    |                    |                  |                      |  |  |  |

| bit 10              | MODE16: Word/Byte Communication Select bit<br>1 = Communication is word-wide (16 bits)                                             |                                                      |                        |                    |                    |                  |                      |  |  |  |

|                     |                                                                                                                                    | nication is byte-                                    |                        |                    |                    |                  |                      |  |  |  |

| bit 9               |                                                                                                                                    | Data Input Sam                                       | . ,                    |                    |                    |                  |                      |  |  |  |

|                     | Master mode                                                                                                                        | e:                                                   |                        |                    |                    |                  |                      |  |  |  |

|                     | 1 = Input data sampled at end of data output time                                                                                  |                                                      |                        |                    |                    |                  |                      |  |  |  |

|                     | <ul> <li>Input data sampled at middle of data output time</li> <li>Slave mode:</li> </ul>                                          |                                                      |                        |                    |                    |                  |                      |  |  |  |

|                     |                                                                                                                                    | SMP must be cleared when SPIx is used in Slave mode. |                        |                    |                    |                  |                      |  |  |  |

| bit 8               | CKE: SPIX (                                                                                                                        | Clock Edge Sele                                      | ect bit <sup>(1)</sup> |                    |                    |                  |                      |  |  |  |

|                     |                                                                                                                                    | utput data chang                                     |                        |                    |                    |                  |                      |  |  |  |

|                     |                                                                                                                                    | utput data chang                                     |                        |                    | ock state to activ | /e clock state ( | see bit 6)           |  |  |  |

| bit 7               |                                                                                                                                    | e Select Enable                                      | •                      | de) <sup>(3)</sup> |                    |                  |                      |  |  |  |

|                     |                                                                                                                                    | used for Slave in not used by mo                     |                        | rolled by port fu  | unction            |                  |                      |  |  |  |

| bit 6               | <ul> <li>0 = SSx pin not used by module. Pin controlled by port function</li> <li><b>CKP:</b> Clock Polarity Select bit</li> </ul> |                                                      |                        |                    |                    |                  |                      |  |  |  |

|                     |                                                                                                                                    | e for clock is a h                                   |                        | ve state is a lov  | v level            |                  |                      |  |  |  |

|                     |                                                                                                                                    | e for clock is a l                                   |                        |                    |                    |                  |                      |  |  |  |

| bit 5               |                                                                                                                                    | ster Mode Enat                                       | ole bit                |                    |                    |                  |                      |  |  |  |

|                     | 1 = Master n<br>0 = Slave m                                                                                                        |                                                      |                        |                    |                    |                  |                      |  |  |  |

|                     |                                                                                                                                    |                                                      |                        |                    |                    |                  |                      |  |  |  |

(FRMEN = 1).

- 2: Do not set both Primary and Secondary prescalers to a value of 1:1.

- 3: This bit must be cleared when FRMEN = 1.

## PIC24HJ32GP302/304, PIC24HJ64GPX02/X04 AND PIC24HJ128GPX02/X04

|                               |                                                                                                       | R/W-0                                                                                                                                        | U-0                                | U-0               | U-0               | U-0             | U-0   |

|-------------------------------|-------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|-------------------|-------------------|-----------------|-------|

|                               | DMABS<2:0>                                                                                            |                                                                                                                                              | —                                  | —                 | _                 | —               | —     |

| bit 15                        |                                                                                                       |                                                                                                                                              |                                    |                   |                   |                 | bit 8 |

| U-0                           | U-0                                                                                                   | U-0                                                                                                                                          | R/W-0                              | R/W-0             | R/W-0             | R/W-0           | R/W-0 |

| _                             | _                                                                                                     | _                                                                                                                                            |                                    |                   | FSA<4:0>          |                 |       |

| bit 7                         |                                                                                                       |                                                                                                                                              |                                    |                   |                   |                 | bit ( |

| Levende                       |                                                                                                       | C = M/rite eble                                                                                                                              |                                    | 'O' oon ho writte | ve to close the l | .:4             |       |

| <b>Legend:</b><br>R = Readabl | a hit                                                                                                 | W = Writable                                                                                                                                 | •                                  | '0' can be writte |                   |                 |       |

| n = Value at                  |                                                                                                       | '1' = Bit is set                                                                                                                             |                                    | 0 = Onimplen      | nented bit, read  | x = Bit is unkr |       |

|                               | FUR                                                                                                   |                                                                                                                                              |                                    |                   | aleu              |                 | IOWIT |

| bit 12-5                      | 101 = 24 buffe<br>100 = 16 buffe<br>011 = 12 buffe<br>010 = 8 buffe<br>001 = 6 buffe<br>000 = 4 buffe | ers in DMA RA<br>ers in DMA RA<br>ers in DMA RA<br>ers in DMA RA<br>rs in DMA RAN<br>rs in DMA RAN<br>rs in DMA RAN<br><b>ted:</b> Read as ' | AM<br>AM<br>AM<br>A<br>A<br>A<br>A |                   |                   |                 |       |

| bit 4-0                       | •                                                                                                     | FO Area Starts                                                                                                                               |                                    | oite              |                   |                 |       |

|                               | 11111 = Read<br>11110 = Read<br>•                                                                     | d buffer RB31                                                                                                                                |                                    | 5113              |                   |                 |       |

| R/W-0        | R-0                                                                                                                                                     | R-0                                        | R-0                            | R/W-0            | R/W-0             | R/W-0           | R/W-0         |  |  |  |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|--------------------------------|------------------|-------------------|-----------------|---------------|--|--|--|

| TXENn        | TXABTn                                                                                                                                                  | TXLARBn                                    | TXERRn                         | TXREQn           | RTRENn            | TXnPF           | RI<1:0>       |  |  |  |

| bit 15       |                                                                                                                                                         |                                            |                                |                  |                   | •               | bit 8         |  |  |  |

|              |                                                                                                                                                         |                                            |                                |                  |                   |                 |               |  |  |  |

| R/W-0        | R-0                                                                                                                                                     | R-0                                        | R-0                            | R/W-0            | R/W-0             | R/W-0           | R/W-0         |  |  |  |

| TXENm        | TXABTm <sup>(1)</sup>                                                                                                                                   | TXLARBm <sup>(1)</sup>                     | TXERRm <sup>(1)</sup>          | TXREQm           | RTRENm            | TXmPF           | RI<1:0>       |  |  |  |

| bit 7        |                                                                                                                                                         |                                            |                                |                  |                   |                 | bit (         |  |  |  |

| Legend:      |                                                                                                                                                         | C = Writeable                              | bit but only '(                | )' can be writte | en to clear the b | it              |               |  |  |  |

| R = Readab   | le bit                                                                                                                                                  | W = Writable                               | -                              |                  | nented bit, read  |                 |               |  |  |  |

| -n = Value a |                                                                                                                                                         | '1' = Bit is set                           |                                | '0' = Bit is cle |                   | x = Bit is unkr | nown          |  |  |  |

|              |                                                                                                                                                         |                                            |                                |                  |                   |                 |               |  |  |  |

| bit 15-8     | See Definitior                                                                                                                                          | n for Bits 7-0, C                          | Controls Buffer                | n                |                   |                 |               |  |  |  |

| bit 7        |                                                                                                                                                         | RX Buffer Sele                             |                                |                  |                   |                 |               |  |  |  |

|              | 1 = Buffer TR                                                                                                                                           | Bn is a transm                             | it buffer                      |                  |                   |                 |               |  |  |  |

|              | 0 = Buffer TR                                                                                                                                           | Bn is a receive                            | e buffer                       |                  |                   |                 |               |  |  |  |

| bit 6        | TXABTm: Me                                                                                                                                              | TXABTm: Message Aborted bit <sup>(1)</sup> |                                |                  |                   |                 |               |  |  |  |

|              | 1 = Message was aborted                                                                                                                                 |                                            |                                |                  |                   |                 |               |  |  |  |

|              | -                                                                                                                                                       | -                                          | nsmission succ                 | -                |                   |                 |               |  |  |  |

| bit 5        |                                                                                                                                                         | 0                                          | Arbitration bit <sup>(1)</sup> |                  |                   |                 |               |  |  |  |

|              |                                                                                                                                                         |                                            | while being se                 |                  |                   |                 |               |  |  |  |

| 1.1.4        |                                                                                                                                                         |                                            | bitration while                |                  |                   |                 |               |  |  |  |

| bit 4        | TXERRm: Error Detected During Transmission bit <sup>(1)</sup>                                                                                           |                                            |                                |                  |                   |                 |               |  |  |  |

|              | <ul> <li>1 = A bus error occurred while the message was being sent</li> <li>0 = A bus error did not occur while the message was being sent</li> </ul>   |                                            |                                |                  |                   |                 |               |  |  |  |

| bit 3        |                                                                                                                                                         | essage Send F                              |                                | sage was bei     | ng sent           |                 |               |  |  |  |

|              |                                                                                                                                                         | -                                          | -                              | bit automatica   | ally clears when  | the message i   | s successfull |  |  |  |

|              | 0 = Clearing t                                                                                                                                          | he bit to '0' wh                           | ile set request                | s a message a    | abort             |                 |               |  |  |  |

| bit 2        | RTRENm: Au                                                                                                                                              | ito-Remote Tra                             | ansmit Enable I                | bit              |                   |                 |               |  |  |  |

|              | <ul> <li>1 = When a remote transmit is received, TXREQ will be set</li> <li>0 = When a remote transmit is received, TXREQ will be unaffected</li> </ul> |                                            |                                |                  |                   |                 |               |  |  |  |

| bit 1-0      | TXmPRI<1:0                                                                                                                                              | >: Message Tr                              | ansmission Pri                 | ority bits       |                   |                 |               |  |  |  |

|              | 11 = Highest                                                                                                                                            | message prior                              | ity                            |                  |                   |                 |               |  |  |  |

|              | •                                                                                                                                                       | ermediate mes                              | • • •                          |                  |                   |                 |               |  |  |  |

|              | 01 = Low inte                                                                                                                                           | rmediate mess                              | sage priority                  |                  |                   |                 |               |  |  |  |

|              |                                                                                                                                                         | message priori                             |                                |                  |                   |                 |               |  |  |  |

#### ~ .

The buffers, SID, EID, DLC, Data Field and Receive Status registers are located in DMA RAM. Note:

## PIC24HJ32GP302/304, PIC24HJ64GPX02/X04 AND PIC24HJ128GPX02/X04

#### **REGISTER 22-6: RTCVAL (WHEN RTCPTR<1:0> =** 01): **WKDYHR: WEEKDAY AND HOURS VALUE REGISTER<sup>(1)</sup>**

| U-0    | U-0 | U-0   | U-0   | U-0   | R/W-x   | R/W-x     | R/W-x   |

|--------|-----|-------|-------|-------|---------|-----------|---------|

| 0-0    | 0-0 | 0-0   | 0-0   | 0-0   | N/ VV-X |           | FV/VV-X |

| —      | —   |       | _     | _     |         | WDAY<2:0> |         |

| bit 15 |     |       |       |       |         |           | bit 8   |

|        |     |       |       |       |         |           |         |

| U-0    | U-0 | R/W-x | R/W-x | R/W-x | R/W-x   | R/W-x     | R/W-x   |

| U-0   | U-0 | R/W-x      | R/W-x | R/W-x      | R/W-x | R/W-x | R/W-x |

|-------|-----|------------|-------|------------|-------|-------|-------|

| —     | —   | HRTEN<1:0> |       | HRONE<3:0> |       |       |       |

| bit 7 |     |            |       |            |       |       | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-11 | Unimplemented: Read as '0'                                                                |

|-----------|-------------------------------------------------------------------------------------------|

| bit 10-8  | WDAY<2:0>: Binary Coded Decimal Value of Weekday Digit; contains a value from 0 to 6      |

| bit 7-6   | Unimplemented: Read as '0'                                                                |

| bit 5-4   | HRTEN<1:0>: Binary Coded Decimal Value of Hour's Tens Digit; contains a value from 0 to 2 |

| bit 3-0   | HRONE<3:0>: Binary Coded Decimal Value of Hour's Ones Digit; contains a value from 0 to 9 |

**Note 1:** A write to this register is only allowed when RTCWREN = 1.

#### **REGISTER 22-7: RTCVAL (WHEN RTCPTR<1:0> =** 00): **MINUTES AND SECONDS VALUE REGISTER**

| U-0    | R/W-x | R/W-x       | R/W-x | R/W-x | R/W-x | R/W-x   | R/W-x |

|--------|-------|-------------|-------|-------|-------|---------|-------|

| —      |       | MINTEN<2:0> |       |       | MINON | IE<3:0> |       |

| bit 15 |       |             |       |       |       |         | bit 8 |

|        |       |             |       |       |       |         |       |

| U-0    | R/W-x | R/W-x       | R/W-x | R/W-x | R/W-x | R/W-x   | R/W-x |

|        |       | SECTEN<2:0> |       |       | SECON | IE<3:0> |       |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 15    | Unimplemented: Read as '0'                                                                   |

|-----------|----------------------------------------------------------------------------------------------|

| bit 14-12 | MINTEN<2:0>: Binary Coded Decimal Value of Minute's Tens Digit; contains a value from 0 to 5 |

| bit 11-8  | MINONE<3:0>: Binary Coded Decimal Value of Minute's Ones Digit; contains a value from 0 to 9 |

| bit 7     | Unimplemented: Read as '0'                                                                   |

| bit 6-4   | SECTEN<2:0>: Binary Coded Decimal Value of Second's Tens Digit; contains a value from 0 to 5 |

| bit 3-0   | SECONE<3:0>: Binary Coded Decimal Value of Second's Ones Digit; contains a value from 0 to 9 |

bit 7

bit 0

| U-0                               | U-0 | U-0              | U-0                                | U-0                  | U-0 | U-0                     | U-0    |

|-----------------------------------|-----|------------------|------------------------------------|----------------------|-----|-------------------------|--------|

| —                                 | —   | _                | _                                  | —                    | _   | —                       |        |

| bit 15                            |     |                  |                                    |                      |     |                         | bit 8  |

|                                   |     |                  |                                    |                      |     |                         |        |

| U-0                               | U-0 | U-0              | U-0                                | U-0                  | U-0 | R/W-0                   | R/W-0  |

| _                                 | _   | —                | —                                  | —                    | _   | RTSECSEL <sup>(1)</sup> | PMPTTL |

| bit 7                             |     |                  |                                    |                      | •   |                         | bit 0  |

|                                   |     |                  |                                    |                      |     |                         |        |

| Legend:                           |     |                  |                                    |                      |     |                         |        |

| R = Readable bit W = Writable bit |     | bit              | U = Unimplemented bit, read as '0' |                      |     |                         |        |

| -n = Value at POR '1'             |     | '1' = Bit is set |                                    | '0' = Bit is cleared |     | x = Bit is unknown      |        |

|                                   |     |                  |                                    |                      |     |                         |        |

bit 15-2 Unimplemented: Read as '0'

| bit 1 | RTSECSEL: RTCC Seconds Clock Output Select bit <sup>(1)</sup> |  |  |  |

|-------|---------------------------------------------------------------|--|--|--|

|       | 1 = RTCC seconds clock is selected for the RTCC pin           |  |  |  |

|       | 0 = RTCC alarm pulse is selected for the RTCC pin             |  |  |  |

| bit 0 | PMPTTL: PMP Module TTL Input Buffer Select bit                |  |  |  |

|       | 1 = PMP module uses TTL input buffers                         |  |  |  |

|       | 0 = PMP module uses Schmitt Trigger input buffers             |  |  |  |

**Note 1:** To enable the actual RTCC output, the RTCOE bit (RCFGCAL<10>) needs to be set.

#### 27.7 MPLAB SIM Software Simulator

The MPLAB SIM Software Simulator allows code development in a PC-hosted environment by simulating the PIC MCUs and dsPIC<sup>®</sup> DSCs on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a comprehensive stimulus controller. Registers can be logged to files for further run-time analysis. The trace buffer and logic analyzer display extend the power of the simulator to record and track program execution, actions on I/O, most peripherals and internal registers.

The MPLAB SIM Software Simulator fully supports symbolic debugging using the MPLAB C Compilers, and the MPASM and MPLAB Assemblers. The software simulator offers the flexibility to develop and debug code outside of the hardware laboratory environment, making it an excellent, economical software development tool.

#### 27.8 MPLAB REAL ICE In-Circuit Emulator System

MPLAB REAL ICE In-Circuit Emulator System is Microchip's next generation high-speed emulator for Microchip Flash DSC and MCU devices. It debugs and programs PIC<sup>®</sup> Flash MCUs and dsPIC<sup>®</sup> Flash DSCs with the easy-to-use, powerful graphical user interface of the MPLAB Integrated Development Environment (IDE), included with each kit.

The emulator is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with either a connector compatible with incircuit debugger systems (RJ11) or with the new high-speed, noise tolerant, Low-Voltage Differential Signal (LVDS) interconnection (CAT5).

The emulator is field upgradable through future firmware downloads in MPLAB IDE. In upcoming releases of MPLAB IDE, new devices will be supported, and new features will be added. MPLAB REAL ICE offers significant advantages over competitive emulators including low-cost, full-speed emulation, run-time variable watches, trace analysis, complex breakpoints, a ruggedized probe interface and long (up to three meters) interconnection cables.

#### 27.9 MPLAB ICD 3 In-Circuit Debugger System

MPLAB ICD 3 In-Circuit Debugger System is Microchip's most cost effective high-speed hardware debugger/programmer for Microchip Flash Digital Signal Controller (DSC) and microcontroller (MCU) devices. It debugs and programs PIC<sup>®</sup> Flash microcontrollers and dsPIC<sup>®</sup> DSCs with the powerful, yet easyto-use graphical user interface of MPLAB Integrated Development Environment (IDE).

The MPLAB ICD 3 In-Circuit Debugger probe is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with a connector compatible with the MPLAB ICD 2 or MPLAB REAL ICE systems (RJ-11). MPLAB ICD 3 supports all MPLAB ICD 2 headers.

### 27.10 PICkit 3 In-Circuit Debugger/ Programmer and PICkit 3 Debug Express

The MPLAB PICkit 3 allows debugging and of PIC<sup>®</sup> dsPIC® programming and Flash microcontrollers at a most affordable price point using the powerful graphical user interface of the MPLAB Integrated Development Environment (IDE). The MPLAB PICkit 3 is connected to the design engineer's PC using a full speed USB interface and can be connected to the target via an Microchip debug (RJ-11) connector (compatible with MPLAB ICD 3 and MPLAB REAL ICE). The connector uses two device I/O pins and the reset line to implement in-circuit debugging and In-Circuit Serial Programming™.

The PICkit 3 Debug Express include the PICkit 3, demo board and microcontroller, hookup cables and CDROM with user's guide, lessons, tutorial, compiler and MPLAB IDE software.