Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

⊡XFI

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | PIC                                                                             |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 40 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                            |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                      |

| Number of I/O              | 21                                                                              |

| Program Memory Size        | 128KB (43K x 24)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 8K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 10x10b/12b                                                                  |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 28-VQFN Exposed Pad                                                             |

| Supplier Device Package    | 28-QFN-S (6x6)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24hj128gp202t-i-mm |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Part<br>Number | Vendor    | Freq.  | Load<br>Cap. | Package<br>Case | Frequency<br>Tolerance | Mounting<br>Type | Operating<br>Temperature |

|----------------|-----------|--------|--------------|-----------------|------------------------|------------------|--------------------------|

| FCR4.0M5T      | TDK Corp. | 4 MHz  | N/A          | Radial          | ±0.5%                  | TH               | -40°C to +85°C           |

| FCR8.0M5       | TDK Corp. | 8 MHz  | N/A          | Radial          | ±0.5%                  | TH               | -40°C to +85°C           |

| HWZT-10.00MD   | TDK Corp. | 10 MHz | N/A          | Radial          | ±0.5%                  | TH               | -40°C to +85°C           |

| HWZT-20.00MD   | TDK Corp. | 20 MHz | N/A          | Radial          | ±0.5%                  | TH               | -40°C to +85°C           |

| <b>TABLE 2-2:</b> | RESONATOR | RECOMMENDATIONS |

|-------------------|-----------|-----------------|

|-------------------|-----------|-----------------|

Legend: TH = Through Hole

## 2.7 Oscillator Value Conditions on Device Start-up

If the PLL of the target device is enabled and configured for the device start-up oscillator, the maximum oscillator source frequency must be limited to  $\leq$ 8 MHz for start-up with the PLL enabled to comply with device PLL start-up conditions. This means that if the external oscillator frequency is outside this range, the application must start-up in the FRC mode first. The default PLL settings after a POR with an oscillator frequency outside this range will violate the device operating speed.

Once the device powers up, the application firmware can initialize the PLL SFRs, CLKDIV and PLLDBF to a suitable value, and then perform a clock switch to the Oscillator + PLL clock source. Note that clock switching must be enabled in the device Configuration word.

## 2.8 Configuration of Analog and Digital Pins During ICSP Operations

If MPLAB ICD 3 or REAL ICE is selected as a debugger, it automatically initializes all of the A/D input pins (ANx) as "digital" pins, by setting all bits in the AD1PCFGL register.

The bits in this register that correspond to the A/D pins that are initialized by MPLAB ICD 3 or REAL ICE, must not be cleared by the user application firmware; otherwise, communication errors will result between the debugger and the device.

If your application needs to use certain A/D pins as analog input pins during the debug session, the user application must clear the corresponding bits in the AD1PCFGL register during initialization of the ADC module.

When MPLAB ICD 3 or REAL ICE is used as a programmer, the user application firmware must correctly configure the AD1PCFGL register. Automatic initialization of this register is only done during debugger operation. Failure to correctly configure the register(s) will result in all A/D pins being recognized as analog input pins, resulting in the port value being read as a logic '0', which may affect user application functionality.

## 2.9 Unused I/Os

Unused I/O pins should be configured as outputs and driven to a logic-low state.

Alternatively, connect a 1k to 10k resistor between Vss and the unused pins.

# 3.5 CPU Control Registers

REGISTER 3-1:

**SR: CPU STATUS REGISTER**

| U-0                | U-0                                                 | U-0                                                                                                                                                    | U-0                                                                      | U-0                                                     | U-0                                               | U-0               | R/W-0           |  |

|--------------------|-----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|---------------------------------------------------------|---------------------------------------------------|-------------------|-----------------|--|

|                    | _                                                   | _                                                                                                                                                      | _                                                                        |                                                         | _                                                 | _                 | DC              |  |

| bit 15             |                                                     |                                                                                                                                                        |                                                                          |                                                         |                                                   |                   | bit 8           |  |

| R/W-0 <sup>(</sup> | <sup>1)</sup> R/W-0 <sup>(2)</sup>                  | R/W-0 <sup>(2)</sup>                                                                                                                                   | R-0                                                                      | R/W-0                                                   | R/W-0                                             | R/W-0             | R/W-0           |  |

|                    | IPL<2:0> <sup>(2)</sup>                             |                                                                                                                                                        | RA                                                                       | Ν                                                       | OV                                                | Z                 | С               |  |

| oit 7              |                                                     |                                                                                                                                                        |                                                                          |                                                         |                                                   |                   | bit (           |  |

| Legend:            |                                                     |                                                                                                                                                        |                                                                          |                                                         |                                                   |                   |                 |  |

| C = Clear          | only bit                                            | R = Readable                                                                                                                                           | e bit                                                                    | U = Unimpler                                            | nented bit, read                                  | as '0'            |                 |  |

| S = Set or         | ly bit                                              | W = Writable                                                                                                                                           | bit                                                                      | -n = Value at                                           | POR                                               |                   |                 |  |

| '1' = Bit is       | set                                                 | '0' = Bit is cle                                                                                                                                       | ared                                                                     | x = Bit is unkr                                         | nown                                              |                   |                 |  |

| bit 15-9           | Unimplemer                                          | nted: Read as '                                                                                                                                        | 0'                                                                       |                                                         |                                                   |                   |                 |  |

| bit 8              | -                                                   | U Half Carry/Bo                                                                                                                                        |                                                                          |                                                         |                                                   |                   |                 |  |

| 511 0              |                                                     | -                                                                                                                                                      |                                                                          | for byte-sized d                                        | lata) or 8th low-o                                | order bit (for wo | ord-sized data  |  |

|                    |                                                     | sult occurred                                                                                                                                          |                                                                          |                                                         |                                                   |                   |                 |  |

|                    | •                                                   |                                                                                                                                                        |                                                                          | bit (for byte-size                                      | ed data) or 8th                                   | low-order bit (   | for word-sized  |  |

|                    | ,                                                   | the result occur                                                                                                                                       |                                                                          |                                                         |                                                   |                   |                 |  |

| bit 7-5            |                                                     | PU Interrupt Pri                                                                                                                                       |                                                                          |                                                         |                                                   |                   |                 |  |

|                    |                                                     | nterrupt Priority                                                                                                                                      |                                                                          |                                                         | ots disabled                                      |                   |                 |  |

|                    |                                                     | nterrupt Priority<br>nterrupt Priority                                                                                                                 |                                                                          |                                                         |                                                   |                   |                 |  |

|                    |                                                     | nterrupt Priority                                                                                                                                      |                                                                          |                                                         |                                                   |                   |                 |  |

|                    |                                                     | nterrupt Priority                                                                                                                                      |                                                                          |                                                         |                                                   |                   |                 |  |

|                    |                                                     | nterrupt Priority                                                                                                                                      |                                                                          |                                                         |                                                   |                   |                 |  |

|                    |                                                     | nterrupt Priority<br>nterrupt Priority                                                                                                                 |                                                                          |                                                         |                                                   |                   |                 |  |

| bit 4              |                                                     | Loop Active bit                                                                                                                                        |                                                                          | 1                                                       |                                                   |                   |                 |  |

|                    | 1 = REPEAT                                          | loop in progress                                                                                                                                       | 5                                                                        |                                                         |                                                   |                   |                 |  |

|                    |                                                     | loop not in prog                                                                                                                                       | ress                                                                     |                                                         |                                                   |                   |                 |  |

| bit 3              |                                                     | Negative bit                                                                                                                                           |                                                                          |                                                         |                                                   |                   |                 |  |

|                    | 1 = Result w                                        | as negative<br>as non-negative                                                                                                                         | e (zero or nos                                                           | itive)                                                  |                                                   |                   |                 |  |

| bit 2              |                                                     | U Overflow bit                                                                                                                                         |                                                                          | live)                                                   |                                                   |                   |                 |  |

|                    |                                                     |                                                                                                                                                        | ithmetic (two'                                                           | s complement).                                          | . It indicates an                                 | overflow of a r   | nagnitude tha   |  |

|                    |                                                     | ign bit to chang                                                                                                                                       | · ·                                                                      | , ,                                                     |                                                   |                   | 0               |  |

|                    |                                                     |                                                                                                                                                        | gned arithmet                                                            | tic (in this arithn                                     | netic operation)                                  |                   |                 |  |

|                    | 0 = No overfl                                       |                                                                                                                                                        |                                                                          |                                                         |                                                   |                   |                 |  |

| bit 1              | Z: MCU ALU                                          |                                                                                                                                                        |                                                                          |                                                         |                                                   |                   |                 |  |

|                    |                                                     |                                                                                                                                                        |                                                                          |                                                         | time in the past                                  | non-zero resu     | lt)             |  |

|                    |                                                     | <ul> <li>0 = The most recent operation that affects the Z bit has cleared it (i.e., a non-zero result)</li> <li>C: MCU ALU Carry/Borrow bit</li> </ul> |                                                                          |                                                         |                                                   |                   |                 |  |

| hit 0              |                                                     | Carry/Rorrow                                                                                                                                           | hit                                                                      |                                                         |                                                   |                   |                 |  |

| bit 0              |                                                     |                                                                                                                                                        |                                                                          | bit of the result                                       | occurred                                          |                   |                 |  |

| bit 0              | 1 = A carry-c                                       | I Carry/Borrow I<br>out from the Mos<br>out from the Mo                                                                                                | st Significant I                                                         |                                                         |                                                   |                   |                 |  |

| bit 0<br>Note 1:   | 1 = A carry-c<br>0 = No carry-                      | out from the Mos<br>out from the Mo                                                                                                                    | st Significant I<br>ost Significant                                      | t bit of the resul                                      | It occurred                                       | m the CPU Int     | errupt Priority |  |

|                    | 1 = A carry-c                                       | out from the Mos<br>out from the Mos<br>are concatenat                                                                                                 | st Significant I<br>ost Significant<br>ted with the IF                   | t bit of the resul<br>PL<3> bit (COR                    | It occurred                                       |                   |                 |  |

| Note 1:            | 1 = A carry-c<br>0 = No carry-<br>The IPL<2:0> bits | out from the Mos-<br>out from the Mos-<br>are concatenal<br>n parentheses i                                                                            | st Significant I<br>ost Significant<br>ted with the IF<br>ndicates the I | t bit of the resul<br>PL<3> bit (COR<br>IPL if IPL<3> = | It occurred<br>CON<3>) to for<br>1. User interrup | ots are disabled  |                 |  |

| Symbol | Parameter                        | Value            |  |

|--------|----------------------------------|------------------|--|

| VPOR   | POR threshold                    | 1.8V nominal     |  |

| TPOR   | POR extension time               | 30 μs maximum    |  |

| VBOR   | BOR threshold                    | 2.5V nominal     |  |

| TBOR   | BOR extension time               | 100 μs maximum   |  |

| TPWRT  | Programmable power-up time delay | 0-128 ms nominal |  |

| TFSCM  | Fail-Safe Clock Monitor Delay    | 900 μs maximum   |  |

|  | <b>TABLE 6-2</b> : | OSCILLATOR DELAY |

|--|--------------------|------------------|

|--|--------------------|------------------|

Note: When the device exits the Reset condition (begins normal operation), the device operating parameters (voltage, frequency, temperature, etc.) must be within their operating ranges, otherwise the device may not function correctly. The user application must ensure that the delay between the time power is first applied, and the time SYSRST becomes inactive, is long enough to get operating parameters within all specification.

## 6.4 **Power-on Reset (POR)**

A Power-on Reset (POR) circuit ensures the device is reset from power-on. The POR circuit is active until VDD crosses the VPOR threshold and the delay TPOR has elapsed. The delay TPOR ensures the internal device bias circuits become stable.

The device supply voltage characteristics must meet the specified starting voltage and rise rate requirements to generate the POR. Refer to Section 28.0 "Electrical Characteristics" for details.

The POR status bit (POR) in the Reset Control register (RCON<0>) is set to indicate the Power-on Reset.

## 6.4.1 Brown-out Reset (BOR) and Power-up timer (PWRT)

The on-chip regulator has a Brown-out Reset (BOR) circuit that resets the device when the VDD is too low (VDD < VBOR) for proper device operation. The BOR circuit keeps the device in Reset until VDD crosses VBOR threshold and the delay TBOR has elapsed. The delay TBOR ensures the voltage regulator output becomes stable.

The Brown-out Reset status bit (BOR) in the Reset Control register (RCON<1>) is set to indicate the BOR.

The device will not run at full speed after a BOR as the VDD should rise to acceptable levels for full-speed operation. The PWRT provides power-up time delay (TPWRT) to ensure that the system power supplies have stabilized at the appropriate levels for full-speed operation before the SYSRST is released.

The power-up timer delay (TPWRT) is programmed by the Power-on Reset Timer Value Select bits (FPWRT<2:0>) in the POR Configuration register (FPOR<2:0>), which provides eight settings (from 0 ms to 128 ms). Refer to **Section 25.0 "Special Features"** for further details.

Figure 6-3 shows the typical brown-out scenarios. The reset delay (TBOR + TPWRT) is initiated each time VDD rises above the VBOR trip point

## REGISTER 7-11: IEC1: INTERRUPT ENABLE CONTROL REGISTER 1 (CONTINUED)

- 1 = Interrupt request enabled

- 0 = Interrupt request not enabled

- bit 1 MI2C1IE: I2C1 Master Events Interrupt Enable bit

- 1 = Interrupt request enabled

- 0 = Interrupt request not enabled

- bit 0 SI2C1IE: I2C1 Slave Events Interrupt Enable bit

- 1 = Interrupt request enabled

- 0 = Interrupt request not enabled

## REGISTER 7-24: IPC9: INTERRUPT PRIORITY CONTROL REGISTER 9

| U-0             | U-0 | U-0              | U-0 | U-0                                | U-0                        | U-0   | U-0   |

|-----------------|-----|------------------|-----|------------------------------------|----------------------------|-------|-------|

| —               | —   | _                | -   | —                                  |                            | —     | —     |

| bit 15          |     |                  |     |                                    |                            |       | bit 8 |

|                 |     |                  |     |                                    |                            |       |       |

| U-0             | U-0 | U-0              | U-0 | U-0                                | R/W-1                      | R/W-0 | R/W-0 |

| _               | —   | —                | —   | —                                  | DMA3IP<2:0>                |       |       |

| bit 7           |     |                  |     | bit 0                              |                            |       |       |

|                 |     |                  |     |                                    |                            |       |       |

| Legend:         |     |                  |     |                                    |                            |       |       |

| R = Readable b  | oit | W = Writable I   | bit | U = Unimplemented bit, read as '0' |                            |       |       |

| -n = Value at P | OR  | '1' = Bit is set |     | '0' = Bit is cle                   | cleared x = Bit is unknown |       |       |

|                 |     |                  |     |                                    |                            |       |       |

bit 15-3 Unimplemented: Read as '0'

bit 2-0 DMA3IP<2:0>: DMA Channel 3 Data Transfer Complete Interrupt Priority bits 111 = Interrupt is priority 7 (highest priority interrupt)

٠

001 = Interrupt is priority 1

000 = Interrupt source is disabled

NOTES:

## 9.1 CPU Clocking System

The PIC24HJ32GP302/304, PIC24HJ64GPX02/X04 and PIC24HJ128GPX02/X04 devices provide seven system clock options:

- Fast RC (FRC) Oscillator

- FRC Oscillator with Phase-Locked Loop (PLL)

- Primary (XT, HS or EC) Oscillator

- Primary Oscillator with PLL

- Secondary (LP) Oscillator

- · Low-Power RC (LPRC) Oscillator

- · FRC Oscillator with postscaler

#### 9.1.1 SYSTEM CLOCK SOURCES

The Fast RC (FRC) internal oscillator runs at a nominal frequency of 7.37 MHz. User software can tune the FRC frequency. User software can optionally specify a factor (ranging from 1:2 to 1:256) by which the FRC clock frequency is divided. This factor is selected using the FRCDIV<2:0> (CLKDIV<10:8>) bits.

The primary oscillator can use one of the following as its clock source:

- Crystal (XT): Crystals and ceramic resonators in the range of 3 MHz to 10 MHz. The crystal is connected to the OSC1 and OSC2 pins.

- High-Speed Crystal (HS): Crystals in the range of 10 MHz to 40 MHz. The crystal is connected to the OSC1 and OSC2 pins.

- External Clock (EC): External clock signal is directly applied to the OSC1 pin.

The secondary (LP) oscillator is designed for low power and uses a 32.768 kHz crystal or ceramic resonator. The LP oscillator uses the SOSCI and SOSCO pins.

The Low-Power RC (LPRC) internal oscillator runs at a nominal frequency of 32.768 kHz. It is also used as a reference clock by the Watchdog Timer (WDT) and Fail-Safe Clock Monitor (FSCM).

The clock signals generated by the FRC and primary oscillators can be optionally applied to an on-chip PLL to provide a wide range of output frequencies for device operation. PLL configuration is described in **Section 9.1.3 "PLL Configuration**".

The FRC frequency depends on the FRC accuracy (see Table 28-19) and the value of the FRC Oscillator Tuning register (see Register 9-4).

#### 9.1.2 SYSTEM CLOCK SELECTION

The oscillator source used at a device Power-on Reset event is selected using Configuration bit settings. The oscillator Configuration bit settings are located in the Configuration registers in the program memory. (Refer to Section 25.1 "Configuration Bits" for further details.) The Initial Oscillator FNOSC<2:0> Selection Configuration bits, (FOSCSEL<2:0>), and the Primary Oscillator Mode Select Configuration bits, POSCMD<1:0> (FOSC<1:0>), select the oscillator source that is used at a Power-on Reset. The FRC primary oscillator is the default (unprogrammed) selection.

The Configuration bits allow users to choose among 12 different clock modes, shown in Table 9-1.

The output of the oscillator (or the output of the PLL if a PLL mode has been selected) Fosc is divided by 2 to generate the device instruction clock (FcY) and the peripheral clock time base (FP). FcY defines the operating speed of the device, and speeds up to 40 MHz are supported by the PIC24HJ32GP302/304, PIC24HJ64GPX02/X04 and PIC24HJ128GPX02/X04 architecture.

Instruction execution speed or device operating frequency, FCY, is given by:

### EQUATION 9-1: DEVICE OPERATING FREQUENCY

$$FCY = \frac{FOSC}{2}$$

## 11.7 I/O Helpful Tips

- 1. In some cases, certain pins as defined in Table 28-9 under "Injection Current", have internal protection diodes to VDD and VSS. The term "Injection Current" is also referred to as "Clamp Current". On designated pins, with sufficient external current limiting precautions by the user, I/O pin input voltages are allowed to be greater or less than the data sheet absolute maximum ratings with nominal VDD with respect to the Vss and VDD supplies. Note that when the user application forward biases either of the high or low side internal input clamp diodes, that the resulting current being injected into the device that is clamped internally by the VDD and VSS power rails, may affect the ADC accuracy by four to six counts.

- I/O pins that are shared with any analog input pin, 2 (i.e., ANx), are always analog pins by default after any reset. Consequently, any pin(s) configured as an analog input pin, automatically disables the digital input pin buffer. As such, any attempt to read a digital input pin will always return a '0' regardless of the digital logic level on the pin if the analog pin is configured. To use a pin as a digital I/O pin on a shared ANx pin, the user application needs to configure the analog pin configuration registers in the ADC module, (i.e., ADxPCFGL, AD1PCFGH), by setting the appropriate bit that corresponds to that I/O port pin to a '1'. On devices with more than one ADC, both analog pin configurations for both ADC modules must be configured as a digital I/O pin for that pin to function as a digital I/O pin.

- **Note:** Although it is not possible to use a digital input pin when its analog function is enabled, it is possible to use the digital I/O output function, TRISx = 0x0, while the analog function is also enabled. However, this is not recommended, particularly if the analog input is connected to an external analog voltage source, which would create signal contention between the analog signal and the output pin driver.

Most I/O pins have multiple functions. Referring to the device pin diagrams in the data sheet, the priorities of the functions allocated to any pins are indicated by reading the pin name from left-to-right. The left most function name takes precedence over any function to its right in the naming convention. For example: AN16/T2CK/T7CK/RC1. This indicates that AN16 is the highest priority in this example and will supersede all other functions to its right, even if enabled, would not work as long as any other function to its left was enabled. This rule applies to all of the functions listed for a given pin.

## 11.8 I/O Ports Resources

Many useful resources related to I/O Ports are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

Note: In the event you are not able to access the product page using the link above, enter this URL in your browser: http://www.microchip.com/wwwproducts/ Devices.aspx?dDocName=en532315

## 11.8.1 KEY RESOURCES

- Section 10. "I/O Ports" (DS70193)

- Code Samples

- Application Notes

- · Software Libraries

- Webinars

- All related dsPIC33F/PIC24H Family Reference Manuals Sections

- Development Tools

## 11.9 Peripheral Pin Select Registers

The PIC24HJ32GP302/304, PIC24HJ64GPX02/X04 and PIC24HJ128GPX02/X04 family of devices implement 27 registers for remappable peripheral configuration:

- 14 Input Remappable Peripheral Registers:

- RPINR0-RPINR1, RPINR3-RPINR4, RPINR7, RPINR10-RPINR11, RPINR18-RPINR23 and PRINR26

- 13 Output Remappable Peripheral Registers:

- RPOR0-RPOR12

Note: Input and Output Register values can only be changed if the IOLOCK bit (OSCCON<6>) is set to '0'. See Section 11.6.3.1 "Control Register Lock" for a specific command sequence.

## REGISTER 11-15: RPOR0: PERIPHERAL PIN SELECT OUTPUT REGISTERS 0

| U-0              | U-0                             | U-0              | R/W-0                              | R/W-0                | R/W-0     | R/W-0              | R/W-0 |

|------------------|---------------------------------|------------------|------------------------------------|----------------------|-----------|--------------------|-------|

| —                |                                 | _                |                                    |                      | RP1R<4:0> | •                  |       |

| bit 15           |                                 |                  |                                    |                      |           |                    | bit 8 |

|                  |                                 |                  |                                    |                      |           |                    |       |

| U-0              | U-0                             | U-0              | R/W-0                              | R/W-0                | R/W-0     | R/W-0              | R/W-0 |

| —                | _                               | —                | RP0R<4:0>                          |                      |           |                    |       |

| bit 7            |                                 | ·                |                                    |                      |           |                    | bit ( |

|                  |                                 |                  |                                    |                      |           |                    |       |

| Legend:          |                                 |                  |                                    |                      |           |                    |       |

| R = Readable b   | = Readable bit W = Writable bit |                  | U = Unimplemented bit, read as '0' |                      |           |                    |       |

| -n = Value at PO | OR                              | '1' = Bit is set |                                    | '0' = Bit is cleared |           | x = Bit is unknown |       |

bit 15-13 Unimplemented: Read as '0'

bit 12-8 **RP1R<4:0>:** Peripheral Output Function is Assigned to RP1 Output Pin bits (see Table 11-2 for peripheral function numbers)

bit 7-5 Unimplemented: Read as '0'

bit 4-0 **RP0R<4:0>:** Peripheral Output Function is Assigned to RP0 Output Pin bits (see Table 11-2 for peripheral function numbers)

#### REGISTER 11-16: RPOR1: PERIPHERAL PIN SELECT OUTPUT REGISTERS 1

| U-0    | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0     | R/W-0 | R/W-0 |

|--------|-----|-----|-------|-------|-----------|-------|-------|

| —      | —   | —   |       |       | RP3R<4:0> |       |       |

| bit 15 |     |     |       |       |           |       | bit 8 |

| U-0   | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0     | R/W-0 | R/W-0 |

|-------|-----|-----|-------|-------|-----------|-------|-------|

| —     | —   | —   |       |       | RP2R<4:0> |       |       |

| bit 7 |     |     |       |       |           |       | bit 0 |

| Legend:           |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

bit 15-13 Unimplemented: Read as '0'

bit 12-8 **RP3R<4:0>:** Peripheral Output Function is Assigned to RP3 Output Pin bits (see Table 11-2 for peripheral function numbers)

bit 7-5 Unimplemented: Read as '0'

bit 4-0 **RP2R<4:0>:** Peripheral Output Function is Assigned to RP2 Output Pin bits (see Table 11-2 for peripheral function numbers)

# PIC24HJ32GP302/304, PIC24HJ64GPX02/X04 AND PIC24HJ128GPX02/X04

| U-0                                                                | U-0                | U-0                                 | R-0          | R-0              | R-0               | R-0             | R-0  |

|--------------------------------------------------------------------|--------------------|-------------------------------------|--------------|------------------|-------------------|-----------------|------|

| —                                                                  | —                  | —                                   |              |                  | FILHIT<4:0>       |                 |      |

| oit 15                                                             |                    |                                     |              |                  |                   |                 | bit  |

| U-0                                                                | R-1                | R-0                                 | R-0          | R-0              | R-0               | R-0             | R-0  |

|                                                                    | 112-1              | 14-0                                | 11-0         | ICODE<6:0        |                   | 11-0            | 11-0 |

| pit 7                                                              |                    |                                     |              | 10002 0.0        |                   |                 | bit  |

|                                                                    |                    | $\Omega = M/rite able$              | hit hut only | (O' con he writt | an to alcor the b | :4              |      |

| Legend:C = Writeable bit, but onlyR = Readable bitW = Writable bit |                    |                                     |              |                  | mented bit, read  |                 |      |

| n = Value at                                                       |                    | '1' = Bit is set                    |              | '0' = Bit is cle |                   | x = Bit is unkr | NOWD |

|                                                                    |                    |                                     |              |                  |                   |                 |      |

| bit 15-13                                                          | Unimplemen         | ted: Read as '                      | 0'           |                  |                   |                 |      |

| oit 12-8                                                           | FILHIT<4:0>:       | : Filter Hit Num                    | ber bits     |                  |                   |                 |      |

|                                                                    |                    | 1 = Reserved                        |              |                  |                   |                 |      |

|                                                                    | 01111 = Filte      | er 15                               |              |                  |                   |                 |      |

|                                                                    | •                  |                                     |              |                  |                   |                 |      |

|                                                                    | •                  |                                     |              |                  |                   |                 |      |

|                                                                    | 00001 = Filte      | or 1                                |              |                  |                   |                 |      |

|                                                                    | 00000 = Filte      |                                     |              |                  |                   |                 |      |

| bit 7                                                              | Unimplemen         | ted: Read as '                      | 0'           |                  |                   |                 |      |

| bit 6-0                                                            | ICODE<6:0>         | : Interrupt Flag                    | Code bits    |                  |                   |                 |      |

|                                                                    |                    | 11111 = Rese                        |              |                  |                   |                 |      |

|                                                                    |                    | IFO almost full<br>Receiver overflo |              |                  |                   |                 |      |

|                                                                    |                    | Vake-up interru                     |              |                  |                   |                 |      |

|                                                                    | 1000001 <b>= E</b> | rror interrupt                      | •            |                  |                   |                 |      |

|                                                                    | 1000000 <b>= N</b> | lo interrupt                        |              |                  |                   |                 |      |

|                                                                    | •                  |                                     |              |                  |                   |                 |      |

|                                                                    | •                  |                                     |              |                  |                   |                 |      |

|                                                                    | •                  | .11111 <b>= Rese</b>                | rved         |                  |                   |                 |      |

|                                                                    |                    | RB15 buffer Inte                    |              |                  |                   |                 |      |

|                                                                    | •                  |                                     | -            |                  |                   |                 |      |

|                                                                    | •                  |                                     |              |                  |                   |                 |      |

|                                                                    | •                  |                                     |              |                  |                   |                 |      |

|                                                                    |                    | RB9 buffer inter                    |              |                  |                   |                 |      |

|                                                                    |                    | RB8 buffer inter                    |              |                  |                   |                 |      |

|                                                                    |                    | RB6 buffer inte                     |              |                  |                   |                 |      |

|                                                                    |                    | RB5 buffer inte                     |              |                  |                   |                 |      |

|                                                                    |                    | RB4 buffer inte<br>RB3 buffer inte  |              |                  |                   |                 |      |

|                                                                    |                    | RB2 buffer inte                     |              |                  |                   |                 |      |

|                                                                    | 0000001 <b>= T</b> | RB1 buffer inte                     | errupt       |                  |                   |                 |      |

|                                                                    | 000000 <b>- T</b>  | RB0 Buffer inte                     |              |                  |                   |                 |      |

|                                   | 13-10. 0100         |                                            |                  |                                    |                   | <b>NEOIOTEN</b> |                |  |  |

|-----------------------------------|---------------------|--------------------------------------------|------------------|------------------------------------|-------------------|-----------------|----------------|--|--|

| R/W-0                             | R/W-0               | R/W-0                                      | R/W-0            | R/W-0                              | R/W-0             | R/W-0           | R/W-0          |  |  |

|                                   | F15B                | P<3:0>                                     |                  |                                    |                   |                 |                |  |  |

| bit 15                            |                     |                                            |                  |                                    |                   |                 | bit 8          |  |  |

| R/W-0                             | R/W-0               | R/W-0                                      | R/W-0            | R/W-0                              | R/W-0             | R/W-0           | R/W-0          |  |  |

| 10,00-0                           |                     | P<3:0>                                     | 10,00-0          | 10,00-0                            |                   | P<3:0>          | 10,00-0        |  |  |

| bit 7                             | 1 150               | 1 \3.02                                    |                  |                                    | 1 1201            | <b>NOP</b>      | bit 0          |  |  |

|                                   |                     |                                            |                  |                                    |                   |                 |                |  |  |

| Legend: C = Writeable bit, but or |                     |                                            | bit, but only '  | 0' can be writte                   | en to clear the b | oit             |                |  |  |

| R = Readabl                       | e bit               | W = Writable                               | bit              | U = Unimplemented bit, read as '0' |                   |                 |                |  |  |

| -n = Value at                     | POR                 | '1' = Bit is set                           | '1' = Bit is set |                                    | ared              | x = Bit is unkr | Bit is unknown |  |  |

|                                   |                     |                                            |                  |                                    |                   |                 |                |  |  |

| bit 15-12                         | F15BP<3:0           | : RX Buffer ma                             | sk for Filter 15 | 5                                  |                   |                 |                |  |  |

|                                   | 1111 = Filte        | r hits received in                         | n RX FIFO but    | ffer                               |                   |                 |                |  |  |

|                                   | 1110 <b>= Filte</b> | er hits received in                        | n RX Buffer 14   | 1                                  |                   |                 |                |  |  |

|                                   | •                   |                                            |                  |                                    |                   |                 |                |  |  |

|                                   | •                   |                                            |                  |                                    |                   |                 |                |  |  |

|                                   | •                   |                                            |                  |                                    |                   |                 |                |  |  |

|                                   |                     | er hits received in<br>ar hits received in |                  |                                    |                   |                 |                |  |  |

| bit 11-8                          | F14BP<3:0           | >: RX Buffer ma                            | sk for Filter 14 | (same values                       | as bit 15-12)     |                 |                |  |  |

|                                   |                     |                                            |                  |                                    |                   |                 |                |  |  |

## REGISTER 19-15: CiBUFPNT4: ECAN™ FILTER 12-15 BUFFER POINTER REGISTER

| bit 3-0 | <b>F12BP&lt;3:0&gt;:</b> RX Buffer mask for Filter 12 (same values as bit 15-12) |

|---------|----------------------------------------------------------------------------------|

|---------|----------------------------------------------------------------------------------|

## **REGISTER 22-1:** RCFGCAL: RTCC CALIBRATION AND CONFIGURATION REGISTER<sup>(1)</sup> (CONTINUED)

| bit 7-0 | CAL<7:0>: RTC Drift Calibration bits                                                                                                                                          |  |  |  |  |  |  |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

|         | 11111111 = Minimum negative adjustment; subtracts 4 RTC clock pulses every one minute                                                                                         |  |  |  |  |  |  |

|         | •                                                                                                                                                                             |  |  |  |  |  |  |

|         | •                                                                                                                                                                             |  |  |  |  |  |  |

|         | •                                                                                                                                                                             |  |  |  |  |  |  |

|         | 10000000 = Maximum negative adjustment; subtracts 512 RTC clock pulses every one minute<br>01111111 = Maximum positive adjustment; adds 508 RTC clock pulses every one minute |  |  |  |  |  |  |

|         | •                                                                                                                                                                             |  |  |  |  |  |  |

|         | •                                                                                                                                                                             |  |  |  |  |  |  |

|         | •                                                                                                                                                                             |  |  |  |  |  |  |

|         | 00000001 = Minimum positive adjustment; adds 4 RTC clock pulses every one minute<br>00000000 = No adjustment                                                                  |  |  |  |  |  |  |

### Note 1: The RCFGCAL register is only affected by a POR.

- 2: A write to the RTCEN bit is only allowed when RTCWREN = 1.

- 3: This bit is read-only. It is cleared to '0' on a write to the lower half of the MINSEC register.

| REGISTER 24-6: PADCFG1: PAD CONFIGURATION CONTROL REGISTER | [ER 24-6: PAD( | G1: PAD CONFIGURATION CONTROL R | EGISTER |

|------------------------------------------------------------|----------------|---------------------------------|---------|

|------------------------------------------------------------|----------------|---------------------------------|---------|

| U-0                                                                  | U-0 | U-0              | U-0 | U-0                                     | U-0 | U-0                     | U-0    |

|----------------------------------------------------------------------|-----|------------------|-----|-----------------------------------------|-----|-------------------------|--------|

| —                                                                    | —   | _                | _   | —                                       | _   | —                       |        |

| bit 15                                                               |     |                  |     |                                         |     |                         | bit 8  |

|                                                                      |     |                  |     |                                         |     |                         |        |

| U-0                                                                  | U-0 | U-0              | U-0 | U-0                                     | U-0 | R/W-0                   | R/W-0  |

| _                                                                    | _   | —                | —   | —                                       | _   | RTSECSEL <sup>(1)</sup> | PMPTTL |

| bit 7                                                                |     | •                |     |                                         | •   |                         | bit 0  |

|                                                                      |     |                  |     |                                         |     |                         |        |

| Legend:                                                              |     |                  |     |                                         |     |                         |        |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |     |                  |     |                                         |     |                         |        |

| -n = Value at F                                                      | POR | '1' = Bit is set |     | '0' = Bit is cleared x = Bit is unknown |     |                         | wn     |

|                                                                      |     |                  |     |                                         |     |                         |        |

bit 15-2 Unimplemented: Read as '0'

| bit 1 | RTSECSEL: RTCC Seconds Clock Output Select bit <sup>(1)</sup> |  |  |  |  |  |

|-------|---------------------------------------------------------------|--|--|--|--|--|

|       | 1 = RTCC seconds clock is selected for the RTCC pin           |  |  |  |  |  |

|       | 0 = RTCC alarm pulse is selected for the RTCC pin             |  |  |  |  |  |

| bit 0 | PMPTTL: PMP Module TTL Input Buffer Select bit                |  |  |  |  |  |

|       | 1 = PMP module uses TTL input buffers                         |  |  |  |  |  |

|       | 0 = PMP module uses Schmitt Trigger input buffers             |  |  |  |  |  |

**Note 1:** To enable the actual RTCC output, the RTCOE bit (RCFGCAL<10>) needs to be set.

## 25.2 On-Chip Voltage Regulator

All of the PIC24HJ32GP302/304, PIC24HJ64GPX02/X04 and PIC24HJ128GPX02/X04 devices power their core digital logic at a nominal 2.5V. This can create a conflict for designs that are required to operate at a higher typical voltage, such as 3.3V. To simplify system design, all devices in the PIC24HJ32GP302/304, PIC24HJ64GPX02/X04 and PIC24HJ128GPX02/X04 family incorporate an on-chip regulator that allows the device to run its core logic from VDD.

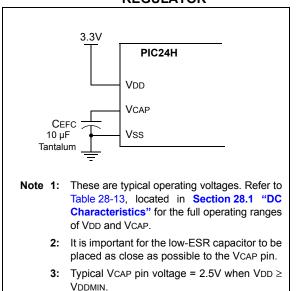

The regulator provides power to the core from the other VDD pins. When the regulator is enabled, a low-ESR (less than 5 Ohms) capacitor (such as tantalum or ceramic) must be connected to the VCAP pin (Figure 25-1). This helps to maintain the stability of the regulator. The recommended value for the filter capacitor is provided in Table 28-13 located in Section 28.1 "DC Characteristics".

| Note: | It is important for the low-ESR capacitor to |

|-------|----------------------------------------------|

|       | be placed as close as possible to the VCAP   |

|       | pin.                                         |

On a POR, it takes approximately 20  $\mu$ s for the on-chip voltage regulator to generate an output voltage. During this time, designated as TSTARTUP, code execution is disabled. TSTARTUP is applied every time the device resumes operation after any power-down.

#### FIGURE 25-1: CONNECTIONS FOR THE ON-CHIP VOLTAGE REGULATOR<sup>(1,2,3)</sup>

## 25.3 Brown-out Reset (BOR)

The Brown-out Reset (BOR) module is based on an internal voltage reference circuit that monitors the regulated supply voltage VCAP. The main purpose of the BOR module is to generate a device Reset when a brown-out condition occurs. Brown-out conditions are generally caused by glitches on the AC mains (for example, missing portions of the AC cycle waveform due to bad power transmission lines, or voltage sags due to excessive current draw when a large inductive load is turned on).

A BOR generates a Reset pulse, which resets the device. The BOR selects the clock source, based on the device Configuration bit values (FNOSC<2:0> and POSCMD<1:0>).

If an oscillator mode is selected, the BOR activates the Oscillator Start-up Timer (OST). The system clock is held until OST expires. If the PLL is used, the clock is held until the LOCK bit (OSCCON<5>) is '1'.

Concurrently, the PWRT time-out (TPWRT) is applied before the internal Reset is released. If TPWRT = 0 and a crystal oscillator is being used, then a nominal delay of TFSCM = 100 is applied. The total delay in this case is TFSCM.

The BOR Status bit (RCON<1>) is set to indicate that a BOR has occurred. The BOR circuit continues to operate while in Sleep or Idle modes and resets the device should VDD fall below the BOR threshold voltage.

## TABLE 28-11: ELECTRICAL CHARACTERISTICS: BOR

| DC CHARACTERISTICS |                                                                                | Standard Operating Conditions: 3.0V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended |  |                    |     |                    |       |            |

|--------------------|--------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--------------------|-----|--------------------|-------|------------|

| Param<br>No.       | Symbol                                                                         | Characteristic                                                                                                                                                                                       |  | Min <sup>(1)</sup> | Тур | Max <sup>(1)</sup> | Units | Conditions |

| BO10               | VBOR                                                                           | BOR Event on VDD transition high-to-low                                                                                                                                                              |  | 2.40               | _   | 2.55               | V     | Vdd        |

| Note 1             | 4. Decemptors are far dealer guidened only and are not tested in manufacturing |                                                                                                                                                                                                      |  |                    |     |                    |       |            |

**Note 1:** Parameters are for design guidance only and are not tested in manufacturing.

#### TABLE 28-12: DC CHARACTERISTICS: PROGRAM MEMORY

|              |                    |                                      | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated) |                       |      |       |                                                            |  |  |  |

|--------------|--------------------|--------------------------------------|-----------------------------------------------------------------------|-----------------------|------|-------|------------------------------------------------------------|--|--|--|

| DC CHA       | DC CHARACTERISTICS |                                      |                                                                       | Operating temperature |      |       | ≤TA ≤+85°C for Industrial<br>≤TA ≤+125°C for Extended      |  |  |  |

| Param<br>No. | Symbol             | Characteristic                       | Min Typ <sup>(1)</sup>                                                |                       | Max  | Units | Conditions                                                 |  |  |  |

|              |                    | Program Flash Memory                 |                                                                       |                       |      |       |                                                            |  |  |  |

| D130a        | Eр                 | Cell Endurance                       | 10,000                                                                | —                     | _    | E/W   | -40° C to +125° C                                          |  |  |  |

| D131         | Vpr                | VDD for Read                         | VMIN                                                                  | —                     | 3.6  | V     | VMIN = Minimum operating<br>voltage                        |  |  |  |

| D132B        | VPEW               | VDD for Self-Timed Write             | VMIN                                                                  | —                     | 3.6  | V     | VMIN = Minimum operating<br>voltage                        |  |  |  |

| D134         | TRETD              | Characteristic Retention             | 20                                                                    | —                     | —    | Year  | Provided no other specifications are violated              |  |  |  |

| D135         | IDDP               | Supply Current during<br>Programming | -                                                                     | 10                    | —    | mA    | _                                                          |  |  |  |

| D136a        | Trw                | Row Write Time                       | 1.32                                                                  | —                     | 1.74 | ms    | Trw = 11064 FRC cycles,<br>Ta = +85°C, See <b>Note 2</b>   |  |  |  |

| D136b        | Trw                | Row Write Time                       | 1.28                                                                  | —                     | 1.79 | ms    | Trw = 11064 FRC cycles,<br>Ta = +125°C, See <b>Note 2</b>  |  |  |  |

| D137a        | Тре                | Page Erase Time                      | 20.1                                                                  | —                     | 26.5 | ms    | TPE = 168517 FRC cycles,<br>TA = +85°C, See <b>Note 2</b>  |  |  |  |

| D137b        | Тре                | Page Erase Time                      | 19.5                                                                  | —                     | 27.3 | ms    | TPE = 168517 FRC cycles,<br>TA = +125°C, See <b>Note 2</b> |  |  |  |

| D138a        | Tww                | Word Write Cycle Time                | 42.3                                                                  | —                     | 55.9 | μs    | Tww = 355 FRC cycles,<br>TA = +85°C, See <b>Note 2</b>     |  |  |  |

| D138b        | Tww                | Word Write Cycle Time                | 41.1                                                                  | —                     | 57.6 | μs    | Tww = 355 FRC cycles,<br>TA = +125°C, See <b>Note 2</b>    |  |  |  |

Note 1: Data in "Typ" column is at 3.3V, 25°C unless otherwise stated.

2: Other conditions: FRC = 7.37 MHz, TUN<5:0> = b'011111 (for Min), TUN<5:0> = b'100000 (for Max). This parameter depends on the FRC accuracy (see Table 28-19) and the value of the FRC Oscillator Tuning register (see Register 9-4). For complete details on calculating the Minimum and Maximum time see Section 5.3 "Programming Operations".

## TABLE 28-13: INTERNAL VOLTAGE REGULATOR SPECIFICATIONS

| Standard Operating Conditions (unless otherwise stated):         Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended |        |                                                   |     |     |     |       |                                                    |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|---------------------------------------------------|-----|-----|-----|-------|----------------------------------------------------|--|

| Param<br>No.                                                                                                                                                                                      | Symbol | Characteristics                                   | Min | Тур | Max | Units | Comments                                           |  |

| _                                                                                                                                                                                                 | CEFC   | External Filter Capacitor<br>Value <sup>(1)</sup> | 4.7 | 10  | —   | μF    | Capacitor must be low series resistance (< 5 Ohms) |  |

**Note 1:** Typical VCAP voltage = 2.5V when VDD  $\ge$  VDDMIN.

## 29.1 High Temperature DC Characteristics

### TABLE 29-1: OPERATING MIPS VS. VOLTAGE

|                |                                     |                              | Max MIPS                                                             |

|----------------|-------------------------------------|------------------------------|----------------------------------------------------------------------|

| Characteristic | racteristic VDD Range<br>(in Volts) | Temperature Range<br>(in °C) | PIC24HJ32GP302/304,<br>PIC24HJ64GPX02/X04 and<br>PIC24HJ128GPX02/X04 |

|                | 3.0V to 3.6V <sup>(1)</sup>         | -40°C to +150°C              | 20                                                                   |

**Note 1:** Device is functional at VBORMIN < VDD < VDDMIN. Analog modules such as the ADC will have degraded performance. Device functionality is tested but not characterized.

#### TABLE 29-2: THERMAL OPERATING CONDITIONS

| Rating                                                                                                                                                                                 |    | Min           | Тур | Max  | Unit |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|---------------|-----|------|------|

| High Temperature Devices                                                                                                                                                               |    |               |     |      |      |

| Operating Junction Temperature Range                                                                                                                                                   |    | -40           | —   | +155 | °C   |

| Operating Ambient Temperature Range                                                                                                                                                    |    | -40           | —   | +150 | °C   |

| Power Dissipation:<br>Internal chip power dissipation:<br>$PINT = VDD x (IDD - \Sigma IOH)$<br>I/O Pin Power Dissipation:<br>$I/O = \Sigma (\{VDD - VOH\} x IOH) + \Sigma (VOL x IOL)$ | PD | PINT + PI/O   |     | W    |      |

| Maximum Allowed Power Dissipation                                                                                                                                                      |    | (Tj - Ta)/θja |     | W    |      |

#### TABLE 29-3: DC TEMPERATURE AND VOLTAGE SPECIFICATIONS

| DC CHARACTERISTICS |                |                | Standard Operating Conditions: 3.0V to 3.6V         (unless otherwise stated)         Operating temperature       -40°C ≤TA ≤+150°C for High Temperature |     |     |   |                 |

|--------------------|----------------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|---|-----------------|

| Parameter<br>No.   | Symbol         | Characteristic | Min Typ Max Units Conditions                                                                                                                             |     |     |   | Conditions      |

| Operating V        | Voltage        |                |                                                                                                                                                          |     |     |   |                 |

| HDC10              | Supply Voltage |                |                                                                                                                                                          |     |     |   |                 |

|                    | Vdd            | _              | 3.0                                                                                                                                                      | 3.3 | 3.6 | V | -40°C to +140°C |

**Note 1:** Device is functional at VBORMIN < VDD < VDDMIN. Analog modules such as the ADC will have degraded performance. Device functionality is tested but not characterized.