Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                   |                                                                                |

|---------------------------|--------------------------------------------------------------------------------|

| Product Status            | Active                                                                         |

| Core Processor            | PIC                                                                            |

| Core Size                 | 16-Bit                                                                         |

| Speed                     | 40 MIPs                                                                        |

| Connectivity              | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                           |

| Peripherals               | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                     |

| Number of I/O             | 35                                                                             |

| Program Memory Size       | 128KB (43K x 24)                                                               |

| Program Memory Type       | FLASH                                                                          |

| EPROM Size                | -                                                                              |

| RAM Size                  | 8K x 8                                                                         |

| oltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                      |

| Data Converters           | A/D 13x10b/12b                                                                 |

| Oscillator Type           | Internal                                                                       |

| Operating Temperature     | -40°C ~ 125°C (TA)                                                             |

| Mounting Type             | Surface Mount                                                                  |

| Package / Case            | 44-VQFN Exposed Pad                                                            |

| Supplier Device Package   | 44-QFN (8x8)                                                                   |

| Purchase URL              | https://www.e-xfl.com/product-detail/microchip-technology/pic24hj128gp204-e-ml |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 1.0 DEVICE OVERVIEW

Note 1: This data sheet summarizes the features of the PIC24HJ32GP302/304, PIC24HJ64GPX02/X04 and PIC24HJ128GPX02/X04 families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the "dsPIC33F/PIC24H Family Reference Manual". Please see the Microchip web site (www.microchip.com) for the latest dsPIC33F/PIC24H Family Reference Manual sections.

2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

This document contains device specific information for the PIC24HJ32GP302/304, PIC24HJ64GPX02/X04 and PIC24HJ128GPX02/X04 devices.

Figure 1-1 shows a general block diagram of the core and peripheral modules in the PIC24HJ32GP302/304, PIC24HJ64GPX02/X04 and PIC24HJ128GPX02/X04 families of devices.

Table 1-1 lists the functions of the various pins shown in the pinout diagrams.

TABLE 4-4: INTERRUPT CONTROLLER REGISTER MAP

| SFR<br>Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13                  | Bit 12 | Bit 11 | Bit 10 | Bit 9      | Bit 8  | Bit 7 | Bit 6                 | Bit 5       | Bit 4   | Bit 3               | Bit 2                 | Bit 1      | Bit 0   | All<br>Resets |

|-------------|-------------|--------|--------|-------------------------|--------|--------|--------|------------|--------|-------|-----------------------|-------------|---------|---------------------|-----------------------|------------|---------|---------------|

| INTCON1     | 0800        | NSTDIS | _      | _                       | _      | _      | _      | _          | _      | _     | DIV0ERR               | DMACERR     | MATHERR | ADDRERR             | STKERR                | OSCFAIL    | _       | 0000          |

| INTCON2     | 0082        | ALTIVT | DISI   | _                       | _      | _      | _      | _          | _      | _     | _                     | _           | _       | _                   | INT2EP                | INT1EP     | INT0EP  | 0000          |

| IFS0        | 0084        | -      | DMA1IF | AD1IF                   | U1TXIF | U1RXIF | SPI1IF | SPI1EIF    | T3IF   | T2IF  | OC2IF                 | IC2IF       | DMA0IF  | T1IF                | OC1IF                 | IC1IF      | INT0IF  | 0000          |

| IFS1        | 0086        | U2TXIF | U2RXIF | INT2IF                  | T5IF   | T4IF   | OC4IF  | OC3IF      | DMA2IF | IC8IF | IC7IF                 | _           | INT1IF  | CNIF                | CMIF                  | MI2C1IF    | SI2C1IF | 0000          |

| IFS2        | 0088        | _      | DMA4IF | PMPIF                   |        | ı      | ı      | _          | _      | _     | _                     | _           | DMA3IF  | C1IF <sup>(1)</sup> | C1RXIF <sup>(1)</sup> | SPI2IF     | SPI2EIF | 0000          |

| IFS3        | 008A        | _      | RTCIF  | DMA5IF                  |        | ı      | ı      | _          | _      | _     | _                     | _           | _       | ı                   | 1                     | _          | _       | 0000          |

| IFS4        | 008C        | -      | ı      | _                       | _      | ı      | ı      | _          | _      | _     | C1TXIF <sup>(1)</sup> | DMA7IF      | DMA6IF  | CRCIF               | U2EIF                 | U1EIF      | _       | 0000          |

| IEC0        | 0094        | _      | DMA1IE | AD1IE                   | U1TXIE | U1RXIE | SPI1IE | SPI1EIE    | T3IE   | T2IE  | OC2IE                 | IC2IE       | DMA0IE  | T1IE                | OC1IE                 | IC1IE      | INT0IE  | 0000          |

| IEC1        | 0096        | U2TXIE | U2RXIE | INT2IE                  | T5IE   | T4IE   | OC4IE  | OC3IE      | DMA2IE | IC8IE | IC7IE                 | _           | INT1IE  | CNIE                | CMIE                  | MI2C1IE    | SI2C1IE | 0000          |

| IEC2        | 0098        | _      | DMA4IE | PMPIE                   |        | -      | I      | _          | _      | _     | _                     | _           | DMA3IE  | C1IE <sup>(1)</sup> | C1RXIE <sup>(1)</sup> | SPI2IE     | SPI2EIE | 0000          |

| IEC3        | 009A        | _      | RTCIE  | DMA5IE                  |        | ı      | ı      | _          | _      | _     | _                     | _           | _       | ı                   | 1                     | _          | _       | 0000          |

| IEC4        | 009C        | _      | I      | _                       |        | ı      | ı      | _          | _      | _     | C1TXIE <sup>(1)</sup> | DMA7IE      | DMA6IE  | CRCIE               | U2EIE                 | U1EIE      | _       | 0000          |

| IPC0        | 00A4        | _      |        | T1IP<2:0>               |        | -      | (      | OC1IP<2:0  | >      | _     |                       | IC1IP<2:0>  |         | 1                   | IN                    | NT0IP<2:0> |         | 4444          |

| IPC1        | 00A6        | _      | •      | T2IP<2:0>               |        | ı      | (      | OC2IP<2:0  | >      | _     |                       | IC2IP<2:0>  |         | ı                   | DN                    | MA0IP<2:0  | >       | 4444          |

| IPC2        | 00A8        | _      | Ú      | 1RXIP<2:0>              | •      | ı      | S      | SPI1IP<2:0 | >      | _     |                       | SPI1EIP<2:0 | >       | ı                   | -                     | Γ3IP<2:0>  |         | 4444          |

| IPC3        | 00AA        | _      | I      | _                       |        | -      | D      | MA1IP<2:   | )>     | _     |                       | AD1IP<2:0>  | •       | 1                   | Ú                     | 1TXIP<2:0> | >       | 0444          |

| IPC4        | 00AC        | _      | (      | CNIP<2:0>               |        | -      |        | CMIP<2:0   | >      | _     |                       | MI2C1IP<2:0 | >       | _                   | SI                    | 2C1IP<2:0  | >       | 4444          |

| IPC5        | 00AE        | _      | I      | C8IP<2:0>               |        | -      |        | IC7IP<2:0  | >      | _     | _                     | _           | _       | _                   | IN                    | NT1IP<2:0> |         | 4404          |

| IPC6        | 00B0        | _      |        | T4IP<2:0>               |        | -      | (      | OC4IP<2:0  | >      | _     |                       | OC3IP<2:0>  | •       | _                   | DN                    | MA2IP<2:0  | >       | 4444          |

| IPC7        | 00B2        | _      | U      | 2TXIP<2:0>              | •      | -      | U      | 2RXIP<2:0  | )>     | _     |                       | INT2IP<2:0> | >       | _                   | -                     | Γ5IP<2:0>  |         | 4444          |

| IPC8        | 00B4        | _      | С      | 1IP<2:0> <sup>(1)</sup> |        | -      | C1     | RXIP<2:0   | >(1)   | _     |                       | SPI2IP<2:0  | >       | _                   | SF                    | PI2EIP<2:0 | >       | 4444          |

| IPC9        | 00B6        | _      | _      | _                       | _      | -      | _      | _          | _      | _     | _                     | _           | _       | _                   | DN                    | MA3IP<2:0  | >       | 0004          |

| IPC11       | 00BA        | _      | _      | _                       | _      | -      | D      | MA4IP<2:   | )>     | _     |                       | PMPIP<2:0   | >       | _                   | _                     | _          | _       | 0440          |

| IPC15       | 00C2        | _      | 1      | _                       |        |        | F      | RTCIP<2:0  | >      |       |                       | DMA5IP<2:0  | >       | _                   | _                     | _          | _       | 0440          |

| IPC16       | 00C4        | _      | С      | RCIP<2:0>               |        | _      | ι      | J2EIP<2:0  | >      | _     |                       | U1EIP<2:0>  | ,       | _                   | _                     | _          | _       | 4440          |

| IPC17       | 00C6        | _      | _      | _                       | _      | _      | C1     | ITXIP<2:0  | >(1)   | _     |                       | DMA7IP<2:0  | >       | _                   | DN                    | MA6IP<2:0  | >       | 0444          |

| INTTREG     | 00E0        | _      | -      | _                       | _      |        | ILR<   | 3:0>       |        | _     |                       |             | VEC     | ONUM<6:0>           |                       |            |         | 4444          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: Interrupts disabled on devices without ECAN™ modules.

TABLE 4-35: FUNDAMENTAL ADDRESSING MODES SUPPORTED

| Addressing Mode                                           | Description                                                                                            |

|-----------------------------------------------------------|--------------------------------------------------------------------------------------------------------|

| File Register Direct                                      | The address of the file register is specified explicitly.                                              |

| Register Direct                                           | The contents of a register are accessed directly.                                                      |

| Register Indirect                                         | The contents of Wn forms the Effective Address (EA).                                                   |

| Register Indirect Post-Modified                           | The contents of Wn forms the EA. Wn is post-modified (incremented or decremented) by a constant value. |

| Register Indirect Pre-Modified                            | Wn is pre-modified (incremented or decremented) by a signed constant value to form the EA.             |

| Register Indirect with Register Offset (Register Indexed) | The sum of Wn and Wb forms the EA.                                                                     |

| Register Indirect with Literal Offset                     | The sum of Wn and a literal forms the EA.                                                              |

# 4.5.3 MOVE (MOV) INSTRUCTION

Move instructions provide a greater degree of addressing flexibility than other instructions. In addition to the Addressing modes supported by most MCU instructions,  ${\tt MOV}$  instructions also support Register Indirect with Register Offset Addressing mode, also referred to as Register Indexed mode.

Note: For the MOV instructions, the addressing mode specified in the instruction can differ for the source and destination EA. However, the 4-bit Wb (Register Offset) field is shared by both source and destination (but typically only used by one).

In summary, the following addressing modes are supported by move instructions:

- · Register Direct

- · Register Indirect

- · Register Indirect Post-modified

- · Register Indirect Pre-modified

- · Register Indirect with Register Offset (Indexed)

- · Register Indirect with Literal Offset

- 8-bit Literal

- 16-bit Literal

Note:

Not all instructions support all the addressing modes given above. Individual instructions may support different subsets of these addressing modes.

#### 4.5.4 OTHER INSTRUCTIONS

Besides the addressing modes outlined previously, some instructions use literal constants of various sizes. For example, BRA (branch) instructions use 16-bit signed literals to specify the branch destination directly, whereas the DISI instruction uses a 14-bit unsigned literal field. In some instructions, such as ADD Acc, the source of an operand or result is implied by the opcode itself. Certain operations, such as NOP, do not have any operands.

#### REGISTER 5-2: NVMKEY: NONVOLATILE MEMORY KEY REGISTER

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | _   | _   | _   | _   | _   | _   | _     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| W-0   | W-0         | W-0 | W-0 | W-0 | W-0 | W-0 | W-0 |  |  |  |  |  |

|-------|-------------|-----|-----|-----|-----|-----|-----|--|--|--|--|--|

|       | NVMKEY<7:0> |     |     |     |     |     |     |  |  |  |  |  |

| bit 7 |             |     |     |     |     |     |     |  |  |  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-8 **Unimplemented:** Read as '0'

bit 7-0 **NVMKEY<7:0>:** Key Register (write-only) bits

TABLE 7-1: INTERRUPT VECTORS

|                  |                   |                   | 1                                  |  |  |

|------------------|-------------------|-------------------|------------------------------------|--|--|

| Vector<br>Number | IVT Address       | AIVT Address      | Interrupt Source                   |  |  |

| 0                | 0x000004          | 0x000104          | Reserved                           |  |  |

| 1                | 0x000006          | 0x000106          | Oscillator Failure                 |  |  |

| 2                | 0x000008          | 0x000108          | Address Error                      |  |  |

| 3                | 0x00000A          | 0x00010A          | Stack Error                        |  |  |

| 4                | 0x00000C          | 0x00010C          | Math Error                         |  |  |

| 5                | 0x00000E          | 0x00010E          | DMA Error                          |  |  |

| 6-7              | 0x000010-0x000012 | 0x000110-0x000112 | Reserved                           |  |  |

| 8                | 0x000014          | 0x000114          | INT0 – External Interrupt 0        |  |  |

| 9                | 0x000016          | 0x000116          | IC1 – Input Capture 1              |  |  |

| 10               | 0x000018          | 0x000118          | OC1 – Output Compare 1             |  |  |

| 11               | 0x00001A          | 0x00011A          | T1 – Timer1                        |  |  |

| 12               | 0x00001C          | 0x00011C          | DMA0 – DMA Channel 0               |  |  |

| 13               | 0x00001E          | 0x00011E          | IC2 – Input Capture 2              |  |  |

| 14               | 0x000020          | 0x000120          | OC2 – Output Compare 2             |  |  |

| 15               | 0x000022          | 0x000122          | T2 – Timer2                        |  |  |

| 16               | 0x000024          | 0x000124          | T3 – Timer3                        |  |  |

| 17               | 0x000026          | 0x000126          | SPI1E – SPI1 Error                 |  |  |

| 18               | 0x000028          | 0x000128          | SPI1 – SPI1 Transfer Done          |  |  |

| 19               | 0x00002A          | 0x00012A          | U1RX – UART1 Receiver              |  |  |

| 20               | 0x00002C          | 0x00012C          | U1TX – UART1 Transmitter           |  |  |

| 21               | 0x00002E          | 0x00012E          | ADC1 – ADC 1                       |  |  |

| 22               | 0x000030          | 0x000130          | DMA1 – DMA Channel 1               |  |  |

| 23               | 0x000032          | 0x000132          | Reserved                           |  |  |

| 24               | 0x000034          | 0x000134          | SI2C1 – I2C1 Slave Events          |  |  |

| 25               | 0x000036          | 0x000136          | MI2C1 – I2C1 Master Events         |  |  |

| 26               | 0x000038          | 0x000138          | CM – Comparator Interrupt          |  |  |

| 27               | 0x00003A          | 0x00013A          | CN – Change Notification Interrupt |  |  |

| 28               | 0x00003C          | 0x00013C          | INT1 – External Interrupt 1        |  |  |

| 29               | 0x00003E          | 0x00013E          | Reserved                           |  |  |

| 30               | 0x000040          | 0x000140          | IC7 – Input Capture 7              |  |  |

| 31               | 0x000042          | 0x000142          | IC8 – Input Capture 8              |  |  |

| 32               | 0x000044          | 0x000144          | DMA2 – DMA Channel 2               |  |  |

| 33               | 0x000046          | 0x000146          | OC3 – Output Compare 3             |  |  |

| 34               | 0x000048          | 0x000148          | OC4 – Output Compare 4             |  |  |

| 35               | 0x00004A          | 0x00014A          | T4 – Timer4                        |  |  |

| 36               | 0x00004C          | 0x00014C          | T5 – Timer5                        |  |  |

| 37               | 0x00004E          | 0x00014E          | INT2 – External Interrupt 2        |  |  |

| 38               | 0x000050          | 0x000150          | U2RX – UART2 Receiver              |  |  |

| 39               | 0x000052          | 0x000152          | U2TX – UART2 Transmitter           |  |  |

| 40               | 0x000054          | 0x000154          | SPI2E – SPI2 Error                 |  |  |

| 41               | 0x000056          | 0x000156          | SPI2 – SPI2 Transfer Done          |  |  |

| 42               | 0x000058          | 0x000158          | C1RX – ECAN1 RX Data Ready         |  |  |

| 43               | 0x00005A          | 0x00015A          | C1 – ECAN1 Event                   |  |  |

| 44               | 0x00005C          | 0x00015C          | DMA3 – DMA Channel 3               |  |  |

| 45-52            | 0x00005E-0x00006C | 0x00015E-0x00016C | Reserved                           |  |  |

| 53               | 0x00006E          | 0x00016E          | PMP – Parallel Master Port         |  |  |

| 54               | 0x000070          | 0x000170          | DMA – DMA Channel 4                |  |  |

#### REGISTER 7-9: IFS4: INTERRUPT FLAG STATUS REGISTER 4

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | _   | _   | _   | _   | _   | _   |       |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | R/W-0                 | R/W-0  | R/W-0  | R/W-0 | R/W-0 | R/W-0 | U-0   |

|-------|-----------------------|--------|--------|-------|-------|-------|-------|

| _     | C1TXIF <sup>(1)</sup> | DMA7IF | DMA6IF | CRCIF | U2EIF | U1EIF | _     |

| bit 7 |                       |        |        |       |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-7 Unimplemented: Read as '0'

bit 6 C1TXIF: ECAN1 Transmit Data Request Interrupt Flag Status bit (1)

1 = Interrupt request has occurred0 = Interrupt request has not occurred

bit 5 DMA7IF: DMA Channel 7 Data Transfer Complete Interrupt Flag Status bit

1 = Interrupt request has occurred0 = Interrupt request has not occurred

bit 4 DMA6IF: DMA Channel 6 Data Transfer Complete Interrupt Flag Status bit

1 = Interrupt request has occurred0 = Interrupt request has not occurred

bit 3 CRCIF: CRC Generator Interrupt Flag Status bit

1 = Interrupt request has occurred0 = Interrupt request has not occurred

bit 2 **U2EIF:** UART2 Error Interrupt Flag Status bit

1 = Interrupt request has occurred0 = Interrupt request has not occurred

bit 1 **U1EIF:** UART1 Error Interrupt Flag Status bit

1 = Interrupt request has occurred0 = Interrupt request has not occurred

bit 0 **Unimplemented:** Read as '0'

Note 1: Interrupts disabled on devices without ECAN™ modules.

#### REGISTER 7-27: IPC16: INTERRUPT PRIORITY CONTROL REGISTER 16

| U-0    | R/W-1 | R/W-0      | R/W-0 | U-0 | R/W-1 | R/W-0      | R/W-0 |

|--------|-------|------------|-------|-----|-------|------------|-------|

| _      |       | CRCIP<2:0> |       | _   |       | U2EIP<2:0> |       |

| bit 15 |       |            |       |     |       |            | bit 8 |

| U-0   | R/W-1 | R/W-0      | R/W-0 | U-0 | U-0 | U-0 | U-0   |

|-------|-------|------------|-------|-----|-----|-----|-------|

| _     |       | U1EIP<2:0> |       | _   | _   | _   | _     |

| bit 7 |       |            |       |     |     |     | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 Unimplemented: Read as '0'

bit 14-12 CRCIP<2:0>: CRC Generator Error Interrupt Flag Priority bits

111 = Interrupt is priority 7 (highest priority interrupt)

•

.

001 = Interrupt is priority 1

000 = Interrupt source is disabled

bit 11 **Unimplemented:** Read as '0'

bit 10-8 **U2EIP<2:0>:** UART2 Error Interrupt Priority bits

111 = Interrupt is priority 7 (highest priority interrupt)

.

•

001 = Interrupt is priority 1

000 = Interrupt source is disabled

bit 7 **Unimplemented:** Read as '0'

bit 6-4 **U1EIP<2:0>:** UART1 Error Interrupt Priority bits

111 = Interrupt is priority 7 (highest priority interrupt)

•

.

•

001 = Interrupt is priority 1

000 = Interrupt source is disabled

bit 3-0 **Unimplemented:** Read as '0'

#### 10.2.2 IDLE MODE

The following occur in Idle mode:

- · The CPU stops executing instructions.

- · The WDT is automatically cleared.

- The system clock source remains active. By default, all peripheral modules continue to operate normally from the system clock source, but can also be selectively disabled (see Section 10.4 "Peripheral Module Disable").

- If the WDT or FSCM is enabled, the LPRC also remains active.

The device wakes from Idle mode on any of these events:

- · Any interrupt that is individually enabled

- · Any device Reset

- · A WDT time-out

On wake-up from Idle mode, the clock is reapplied to the CPU and instruction execution will begin (2 to 4 cycles later), starting with the instruction following the PWRSAV instruction, or the first instruction in the ISR.

# 10.2.3 INTERRUPTS COINCIDENT WITH POWER SAVE INSTRUCTIONS

Any interrupt that coincides with the execution of a PWRSAV instruction is held off until entry into Sleep or Idle mode has completed. The device then wakes up from Sleep or Idle mode.

### 10.3 Doze Mode

The preferred strategies for reducing power consumption are changing clock speed and invoking one of the power-saving modes. In some circumstances, this cannot be practical. For example, it may be necessary for an application to maintain uninterrupted synchronous communication, even while it is doing nothing else. Reducing system clock speed can introduce communication errors, while using a power-saving mode can stop communications completely.

Doze mode is a simple and effective alternative method to reduce power consumption while the device is still executing code. In this mode, the system clock continues to operate from the same source and at the same speed. Peripheral modules continue to be clocked at the same speed, while the CPU clock speed is reduced. Synchronization between the two clock domains is maintained, allowing the peripherals to access the SFRs while the CPU executes code at a slower rate.

Doze mode is enabled by setting the DOZEN bit (CLKDIV<11>). The ratio between peripheral and core clock speed is determined by the DOZE<2:0> bits (CLKDIV<14:12>). There are eight possible configurations, from 1:1 to 1:128, with 1:1 being the default setting.

Programs can use Doze mode to selectively reduce power consumption in event-driven applications. This allows clock-sensitive functions, such as synchronous communications, to continue without interruption while the CPU idles, waiting for something to invoke an interrupt routine. An automatic return to full-speed CPU operation on interrupts can be enabled by setting the ROI bit (CLKDIV<15>). By default, interrupt events have no effect on Doze mode operation.

For example, suppose the device is operating at 20 MIPS and the ECAN module has been configured for 500 kbps based on this device operating speed. If the device is placed in Doze mode with a clock frequency ratio of 1:4, the ECAN module continues to communicate at the required bit rate of 500 kbps, but the CPU now starts executing instructions at a frequency of 5 MIPS.

# 10.4 Peripheral Module Disable

The Peripheral Module Disable (PMD) registers provide a method to disable a peripheral module by stopping all clock sources supplied to that module. When a peripheral is disabled using the appropriate PMD control bit, the peripheral is in a minimum power consumption state. The control and status registers associated with the peripheral are also disabled, so writes to those registers do not have effect and read values are invalid.

A peripheral module is enabled only if both the associated bit in the PMD register is cleared and the peripheral is supported by the specific PIC MCU variant. If the peripheral is present in the device, it is enabled in the PMD register by default.

Note: If a PMD bit is set, the corresponding module is disabled after a delay of one instruction cycle. Similarly, if a PMD bit is cleared, the corresponding module is enabled after a delay of one instruction cycle (assuming the module control registers are already configured to enable

module operation).

#### REGISTER 11-7: RPINR11: PERIPHERAL PIN SELECT INPUT REGISTER 11

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | _   | _   | _   | _   | _   | _   | _     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | R/W-1 | R/W-1 | R/W-1      | R/W-1 | R/W-1 |

|-------|-----|-----|-------|-------|------------|-------|-------|

| _     | _   | _   |       |       | OCFAR<4:0> |       |       |

| bit 7 |     |     |       |       |            |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-5 **Unimplemented:** Read as '0'

bit 4-0 OCFAR<4:0>: Assign Output Compare A (OCFA) to the corresponding RPn pin

11111 = Input tied to Vss 11001 = Input tied to RP25

•

•

•

00001 = Input tied to RP1 00000 = Input tied to RP0

#### 19.4 ECAN Resources

Many useful resources related to ECAN are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

Note:

In the event you are not able to access the product page using the link above, enter this URL in your browser:

http://www.microchip.com/wwwproducts/ Devices.aspx?dDocName=en532315

#### 19.4.1 KEY RESOURCES

- Section 21. "Enhanced Controller Area Network (ECAN™)" (DS70185)

- · Code Samples

- · Application Notes

- · Software Libraries

- Webinars

- All related dsPIC33F/PIC24H Family Reference Manuals Sections

- · Development Tools

#### 19.5 **ECAN Control Registers**

#### REGISTER 19-1: CICTRL1: ECAN™ CONTROL REGISTER 1

| U-0    | U-0 | R/W-0 | R/W-0 | r-0 | R/W-1 | R/W-0      | R/W-0 |  |

|--------|-----|-------|-------|-----|-------|------------|-------|--|

| _      | _   | CSIDL | ABAT  | _   |       | REQOP<2:0> |       |  |

| bit 15 |     |       |       |     | bit   |            |       |  |

| R-1   | R-0         | R-0 | U-0 | R/W-0  | U-0 | U-0 | R/W-0 |

|-------|-------------|-----|-----|--------|-----|-----|-------|

|       | OPMODE<2:0> |     | _   | CANCAP | _   | _   | WIN   |

| bit 7 |             |     |     |        |     |     | bit 0 |

| Legend:           | C = Writable bit, but only '0' can be written to clear the bit $r = Bit$ is Reserved |                      |                    |  |  |  |

|-------------------|--------------------------------------------------------------------------------------|----------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit U = Unimplemented bit, read as '0'                                  |                      |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set                                                                     | '0' = Bit is cleared | x = Bit is unknown |  |  |  |

Unimplemented: Read as '0' bit 15-14 bit 13 **CSIDL:** Stop in Idle Mode bit

1 = Discontinue module operation when device enters Idle mode

0 = Continue module operation in Idle mode

bit 12 **ABAT:** Abort All Pending Transmissions bit

1 = Signal all transmit buffers to abort transmission

0 = Module will clear this bit when all transmissions are aborted

bit 11 Reserved: Do not use

bit 10-8 REQOP<2:0>: Request Operation Mode bits

000 = Set Normal Operation mode

001 = Set Disable mode 010 = Set Loopback mode 011 = Set Listen Only Mode 100 = Set Configuration mode

101 = Reserved 110 = Reserved

111 = Set Listen All Messages mode

OPMODE<2:0>: Operation Mode bits bit 7-5

000 = Module is in Normal Operation mode

001 = Module is in Disable mode 010 = Module is in Loopback mode 011 = Module is in Listen Only mode 100 = Module is in Configuration mode

101 = Reserved 110 = Reserved

111 = Module is in Listen All Messages mode

bit 4 Unimplemented: Read as '0'

CANCAP: CAN Message Receive Timer Capture Event Enable bit bit 3

1 = Enable input capture based on CAN message receive

0 = Disable CAN capture

bit 2-1 Unimplemented: Read as '0'

bit 0 WIN: SFR Map Window Select bit

> 1 = Use filter window 0 = Use buffer window

# REGISTER 19-26: CiTRmnCON: ECAN™ TX/RX BUFFER m CONTROL REGISTER (m = 0,2,4,6; n = 1,3,5,7)

| R/W-0  | R-0    | R-0     | R-0    | R/W-0  | R/W-0  | R/W-0 R/W-0 |  |

|--------|--------|---------|--------|--------|--------|-------------|--|

| TXENn  | TXABTn | TXLARBn | TXERRn | TXREQn | RTRENn | TXnPRI<1:0> |  |

| bit 15 |        |         |        |        |        | bit 8       |  |

| R/W-0     | R-0                   | R-0                    | R-0                   | R/W-0  | R/W-0  | R/W-0 R/W-0 |       |

|-----------|-----------------------|------------------------|-----------------------|--------|--------|-------------|-------|

| TXENm     | TXABTm <sup>(1)</sup> | TXLARBm <sup>(1)</sup> | TXERRm <sup>(1)</sup> | TXREQm | RTRENm | TXmPRI<1:0> |       |

| bit 7 bit |                       |                        |                       |        |        |             | bit 0 |

| Legend:           | C = Writeable bit, but only '0' can be written to clear the bit |                                                     |                    |  |  |  |  |

|-------------------|-----------------------------------------------------------------|-----------------------------------------------------|--------------------|--|--|--|--|

| R = Readable bit  | W = Writable bit                                                | W = Writable bit U = Unimplemented bit, read as '0' |                    |  |  |  |  |

| -n = Value at POR | '1' = Bit is set                                                | '0' = Bit is cleared                                | x = Bit is unknown |  |  |  |  |

| bit 15-8 | See Definition for Bits 7-0, Controls Buffer n                                                          |

|----------|---------------------------------------------------------------------------------------------------------|

| bit 7    | TXENm: TX/RX Buffer Selection bit                                                                       |

|          | 1 = Buffer TRBn is a transmit buffer                                                                    |

|          | 0 = Buffer TRBn is a receive buffer                                                                     |

| bit 6    | TXABTm: Message Aborted bit <sup>(1)</sup>                                                              |

|          | 1 = Message was aborted                                                                                 |

|          | 0 = Message completed transmission successfully                                                         |

| bit 5    | TXLARBm: Message Lost Arbitration bit <sup>(1)</sup>                                                    |

|          | 1 = Message lost arbitration while being sent                                                           |

|          | 0 = Message did not lose arbitration while being sent                                                   |

| bit 4    | TXERRm: Error Detected During Transmission bit <sup>(1)</sup>                                           |

|          | 1 = A bus error occurred while the message was being sent                                               |

|          | 0 = A bus error did not occur while the message was being sent                                          |

| bit 3    | TXREQm: Message Send Request bit                                                                        |

|          | 1 = Requests that a message be sent. The bit automatically clears when the message is successfully sent |

|          | 0 = Clearing the bit to '0' while set requests a message abort                                          |

| bit 2    | RTRENm: Auto-Remote Transmit Enable bit                                                                 |

|          | 1 = When a remote transmit is received, TXREQ will be set                                               |

|          | 0 = When a remote transmit is received, TXREQ will be unaffected                                        |

| bit 1-0  | TXmPRI<1:0>: Message Transmission Priority bits                                                         |

|          | 11 = Highest message priority                                                                           |

|          | 10 = High intermediate message priority                                                                 |

|          | 01 = Low intermediate message priority                                                                  |

|          | 00 = Lowest message priority                                                                            |

Note 1: This bit is cleared when the TXREQ bit is set.

**Note:** The buffers, SID, EID, DLC, Data Field and Receive Status registers are located in DMA RAM.

### 21.1 Comparator Resources

Many useful resources related to Comparators are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

Note:

In the event you are not able to access the product page using the link above, enter this URL in your browser:

http://www.microchip.com/wwwproducts/ Devices.aspx?dDocName=en534555

#### 21.1.1 KEY RESOURCES

- Section 34. "Comparator" (DS70212)

- · Code Samples

- · Application Notes

- · Software Libraries

- Webinars

- All related dsPIC33F/PIC24H Family Reference Manuals Sections

- · Development Tools

### 24.2 PMP Control Registers

#### REGISTER 24-1: PMCON: PARALLEL PORT CONTROL REGISTER

| R/W-0  | U-0 | R/W-0 | R/W-0   | R/W-0 R/W-0 |        | R/W-0  | R/W-0  |

|--------|-----|-------|---------|-------------|--------|--------|--------|

| PMPEN  | _   | PSIDL | ADRMUX1 | ADRMUX0     | PTBEEN | PTWREN | PTRDEN |

| bit 15 |     |       |         |             |        |        | bit 8  |

| R/W-0 | R/W-0 | R/W-0 <sup>(1)</sup> | U-0 | R/W-0 <sup>(1)</sup> | R/W-0 | R/W-0 | R/W-0 |

|-------|-------|----------------------|-----|----------------------|-------|-------|-------|

| CSF1  | CSF0  | ALP                  | _   | CS1P                 | BEP   | WRSP  | RDSP  |

| bit 7 |       |                      |     |                      |       |       | bit 0 |

Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

bit 15 **PMPEN:** Parallel Master Port Enable bit

1 = PMP enabled

0 = PMP disabled, no off-chip access performed

bit 14 **Unimplemented:** Read as '0' bit 13 **PSIDL:** Stop in Idle Mode bit

1 = Discontinue module operation when device enters Idle mode

0 = Continue module operation in Idle mode

bit 12-11 ADRMUX1:ADRMUX0: Address/Data Multiplexing Selection bits<sup>(1)</sup>

11 = Reserved

10 = All 16 bits of address are multiplexed on PMD<7:0> pins

01 = Lower 8 bits of address are multiplexed on PMD<7:0> pins, upper 3 bits are multiplexed on PMA<10:8>

00 = Address and data appear on separate pins

bit 10 **PTBEEN:** Byte Enable Port Enable bit (16-bit Master mode)

1 = PMBE port enabled0 = PMBE port disabled

bit 9 **PTWREN:** Write Enable Strobe Port Enable bit

1 = PMWR/PMENB port enabled0 = PMWR/PMENB port disabled

bit 8 PTRDEN: Read/Write Strobe Port Enable bit

1 = PMRD/<u>PMWR</u> port enabled 0 = PMRD/<u>PMWR</u> port disabled

bit 7-6 CSF1:CSF0: Chip Select Function bits

11 = Reserved

10 = PMCS1 functions as chip select 0x = PMCS1 functions as address bit 14

bit 5 **ALP:** Address Latch Polarity bit<sup>(1)</sup>

1 = Active-high (PMALL and PMALH) 0 = Active-low (PMALL and PMALH)

bit 4 Unimplemented: Read as '0'

bit 3 **CS1P:** Chip Select 1 Polarity bit<sup>(1)</sup>

1 = Active-high (PMCS1/PMCS1)

$0 = Active-low (\overline{PMCS1}/\overline{PMCS1})$

Note 1: These bits have no effect when their corresponding pins are used as address lines.

TABLE 25-5: CODE FLASH SECURITY SEGMENT SIZES FOR 128 KB DEVICES

| CONFIG BITS          | BSS<2:0> = x11 0K                                                          | BSS<2:0> = x10 1K                                                                                                                                                                       | BSS<2:0> = x01 4K                                                                                                                                                                        | BSS<2:0> = x00 8K                                                          |

|----------------------|----------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|

| SSS<2:0> = x11<br>0K | VS = 256 IW                                                                | VS = 256 IW  BS = 768 IW  0x000000h 0x0001FEh 0x00020h 0x0007FEh 0x002000h 0x003FFEh 0x004000h 0x003FFEh 0x004000h 0x007FFEh 0x008000h 0x00FFEh 0x008000h 0x00FFFEh 0x010000h 0x0157FEh | VS = 256 IW  BS = 3840 IW  0x000000h 0x0001FEh 0x00020h 0x0007FEh 0x002000h 0x001FFEh 0x002000h 0x003FFEh 0x004000h 0x007FFEh 0x004000h 0x007FFEh 0x008000h 0x00FFEh 0x010000h 0x0157FEh | VS = 256 IW                                                                |

| SSS<2:0> = x10       | VS = 256 IW                                                                | VS = 256 IW                                                                                                                                                                             | VS = 256 IW                                                                                                                                                                              | VS = 256 IW                                                                |

| 4K                   | GS = 39936 IW  0x003FFEh 0x004000h 0x007FFEh 0x008000h 0x00ABFEh 0x0157FEh | GS = 39936 IW  0x003FFEh 0x004000h 0x007FFEh 0x008000h 0x00ABFEh 0x0157FEh                                                                                                              | GS = 39936 IW  0x0045FEh 0x004000h 0x007FFEh 0x008000h 0x00ABFEh 0x0157FEh                                                                                                               | 0x003FFEh<br>0x004000h<br>0x007FFEh<br>0x008000h<br>0x00ABFEh<br>0x0157FEh |

| SSS<2:0> = x01       | VS = 256 IW                                                                | VS = 256 IW                                                                                                                                                                             | VS = 256 IW                                                                                                                                                                              | VS = 256 IW                                                                |

| 8K                   | GS = 35840 IW                                                              | SS = 7168 IW                                                                                                                                                                            | SS = 4096 IW                                                                                                                                                                             | GS = 35840 IW                                                              |

| SSS<2:0> = x00       | VS = 256 IW                                                                | VS = 256 IW                                                                                                                                                                             | VS = 256 IW                                                                                                                                                                              | VS = 256 IW                                                                |

| 16K                  | SS = 16128 IW                                                              | SS = 15360 IW                                                                                                                                                                           | SS = 12288 IW                                                                                                                                                                            | SS = 8192 IW                                                               |

|                      | GS = 27648 IW 0x010000h 0x0157FEh                                          | GS = 27648 IW                                                                                                                                                                           | GS = 27648 IW                                                                                                                                                                            | GS = 27648 IW                                                              |

| OTES: |  |  |

|-------|--|--|

|       |  |  |

|       |  |  |

|       |  |  |

|       |  |  |

|       |  |  |

|       |  |  |

|       |  |  |

|       |  |  |

|       |  |  |

|       |  |  |

|       |  |  |

|       |  |  |

|       |  |  |

|       |  |  |

|       |  |  |

|       |  |  |

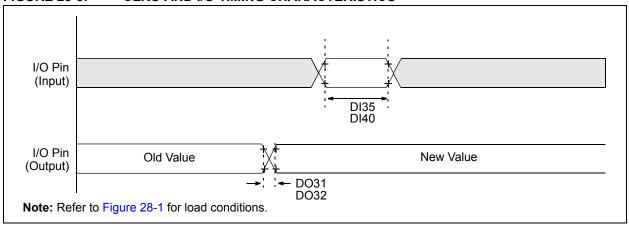

FIGURE 28-3: CLKO AND I/O TIMING CHARACTERISTICS

**TABLE 28-20: I/O TIMING REQUIREMENTS**

| AC CHARACTERISTICS |        |                                   | Standard Oper<br>(unless otherw<br>Operating temp | vise state | e <b>d)</b><br>-40°C ≤ | Ta ≤+85° |       |            |

|--------------------|--------|-----------------------------------|---------------------------------------------------|------------|------------------------|----------|-------|------------|

| Param<br>No.       | Symbol | Characteristic                    |                                                   | Min        | Typ <sup>(1)</sup>     | Max      | Units | Conditions |

| DO31               | TioR   | Port Output Rise Tim              | е                                                 | _          | 10                     | 25       | ns    | _          |

| DO32               | TioF   | Port Output Fall Time             | )                                                 | _          | 10                     | 25       | ns    |            |

| DI35               | TINP   | INTx Pin High or Low Time (input) |                                                   | 20         | _                      |          | ns    |            |

| DI40               | TRBP   | CNx High or Low Time (input)      |                                                   |            | _                      | _        | Tcy   | _          |

Note 1: Data in "Typ" column is at 3.3V, 25°C unless otherwise stated.

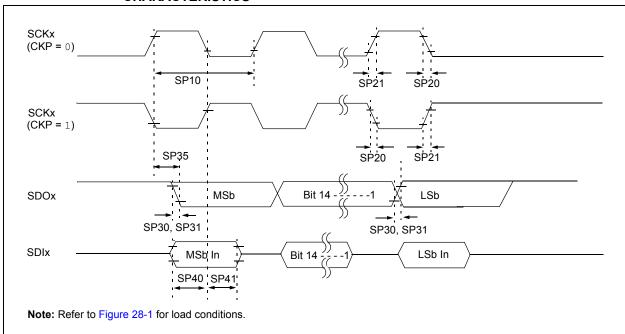

FIGURE 28-12: SPIX MASTER MODE (FULL-DUPLEX, CKE = 0, CKP = x, SMP = 1) TIMING CHARACTERISTICS

TABLE 28-31: SPIX MASTER MODE (FULL-DUPLEX, CKE = 0, CKP = x, SMP = 1) TIMING REQUIREMENTS

| AC CHARACTERISTICS |                       |                                            | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated) Operating temperature -40°C ≤TA ≤+85°C for Industrial -40°C ≤TA ≤+125°C for Extended |                    |     |       |                                       |

|--------------------|-----------------------|--------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----|-------|---------------------------------------|

| Param<br>No.       | Symbol                | Characteristic <sup>(1)</sup>              | Min                                                                                                                                                        | Typ <sup>(2)</sup> | Max | Units | Conditions                            |

| SP10               | TscP                  | Maximum SCK Frequency                      | _                                                                                                                                                          | _                  | 9   | MHz   | -40°C to +125°C and see <b>Note 3</b> |

| SP20               | TscF                  | SCKx Output Fall Time                      | _                                                                                                                                                          | _                  |     | ns    | See parameter DO32 and Note 4         |

| SP21               | TscR                  | SCKx Output Rise Time                      | _                                                                                                                                                          | _                  | _   | ns    | See parameter DO31 and <b>Note 4</b>  |

| SP30               | TdoF                  | SDOx Data Output Fall Time                 |                                                                                                                                                            | _                  | _   | ns    | See parameter DO32 and <b>Note 4</b>  |

| SP31               | TdoR                  | SDOx Data Output Rise Time                 | _                                                                                                                                                          | _                  | _   | ns    | See parameter DO31 and <b>Note 4</b>  |

| SP35               | TscH2doV,<br>TscL2doV | SDOx Data Output Valid after SCKx Edge     | _                                                                                                                                                          | 6                  | 20  | ns    | _                                     |

| SP36               | TdoV2scH,<br>TdoV2scL | SDOx Data Output Setup to First SCKx Edge  | 30                                                                                                                                                         | _                  | _   | ns    | _                                     |

| SP40               | TdiV2scH,<br>TdiV2scL | Setup Time of SDIx Data Input to SCKx Edge | 30                                                                                                                                                         | _                  | _   | ns    | _                                     |

| SP41               | TscH2diL,<br>TscL2diL | Hold Time of SDIx Data Input to SCKx Edge  | 30                                                                                                                                                         | _                  | _   | ns    | _                                     |

- Note 1: These parameters are characterized, but are not tested in manufacturing.

- **2:** Data in "Typ" column is at 3.3V, 25°C unless otherwise stated.

- 3: The minimum clock period for SCKx is 111 ns. The clock generated in Master mode must not violate this specification.

- 4: Assumes 50 pF load on all SPIx pins.

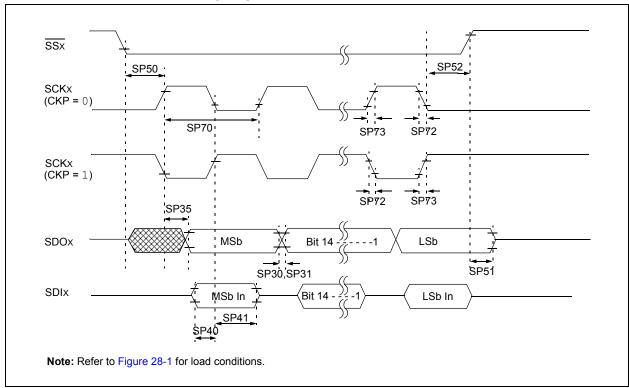

FIGURE 28-15: SPIX SLAVE MODE (FULL-DUPLEX CKE = 0, CKP = 1, SMP = 0) TIMING CHARACTERISTICS

# Revision C (May 2009)

This revision includes minor typographical and formatting changes throughout the data sheet text.

Global changes include:

- Changed all instances of OSCI to OSC1 and OSCO to OSC2

- Changed all instances of VDDCORE and VDDCORE/ VCAP to VCAP/VDDCORE

The other changes are referenced by their respective section in the following table.

TABLE A-2: MAJOR SECTION UPDATES

| TABLE A-2: MAJOR SECTION UPDATES                                             |                                                                                                                         |  |  |  |  |

|------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Section Name                                                                 | Update Description                                                                                                      |  |  |  |  |

| "High-Performance, 16-bit<br>Microcontrollers"                               | Updated all pin diagrams to denote the pin voltage tolerance (see "Pin Diagrams").                                      |  |  |  |  |

|                                                                              | Added Note 2 to the 28-Pin QFN-S and 44-Pin QFN pin diagrams, which references pin connections to Vss.                  |  |  |  |  |

| Section 1.0 "Device Overview"                                                | Updated AVDD in the PINOUT I/O Descriptions (see Table 1-1).                                                            |  |  |  |  |

| Section 2.0 "Guidelines for Getting<br>Started with 16-bit Microcontrollers" | Added new section to the data sheet that provides guidelines on getting started with 16-bit Digital Signal Controllers. |  |  |  |  |

|                                                                              | Added Peripheral Pin Select (PPS) capability column to Pinout I/O Descriptions (see Table 1-1).                         |  |  |  |  |

| Section 3.0 "CPU"                                                            | Updated CPU Core Block Diagram with a connection from the DSP Engine to the Y Data Bus (see Figure 3-1).                |  |  |  |  |

| Section 4.0 "Memory Organization"                                            | Updated Reset value for CORCON in the CPU Core Register Map (see Table 4-1).                                            |  |  |  |  |

|                                                                              | Updated Reset value for IPC15 in the Interrupt Controller Register Map (see Table 4-4).                                 |  |  |  |  |

|                                                                              | Removed the FLTA1IE bit (IEC3) from the Interrupt Controller Register Map (see Table 4-4).                              |  |  |  |  |

|                                                                              | Updated bit locations for RPINR25 in the Peripheral Pin Select Input Register Map (see Table 4-19).                     |  |  |  |  |

|                                                                              | Updated the Reset value for CLKDIV in the System Control Register Map (see Table 4-31).                                 |  |  |  |  |

| Section 5.0 "Flash Program Memory"                                           | Updated <b>Section 5.3 "Programming Operations"</b> with programming time formula.                                      |  |  |  |  |

| Section 9.0 "Oscillator Configuration"                                       | Updated the Oscillator System Diagram and added Note 2 (see Figure 9-1).                                                |  |  |  |  |

|                                                                              | Updated default bit values for DOZE<2:0> and FRCDIV<2:0> in the Clock Divisor (CLKDIV) Register (see Register 9-2).     |  |  |  |  |

|                                                                              | Added a paragraph regarding FRC accuracy at the end of <b>Section 9.1.1</b> "System Clock Sources".                     |  |  |  |  |

|                                                                              | Added Note 3 to Section 9.2.2 "Oscillator Switching Sequence".                                                          |  |  |  |  |

|                                                                              | Added Note 1 to the FRC Oscillator Tuning (OSCTUN) Register (see Register 9-4).                                         |  |  |  |  |