Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 40 MIPs                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                     |

| Number of I/O              | 35                                                                             |

| Program Memory Size        | 128KB (43K x 24)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 8K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                      |

| Data Converters            | A/D 13x10b/12b                                                                 |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 44-VQFN Exposed Pad                                                            |

| Supplier Device Package    | 44-QFN (8x8)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24hj128gp204-i-ml |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 1.0 DEVICE OVERVIEW

- Note 1: This data sheet summarizes the features of the PIC24HJ32GP302/304, PIC24HJ64GPX02/X04 and PIC24HJ128GPX02/X04 families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the "dsPIC33F/PIC24H Family Reference Manual". Please see the Microchip web site (www.microchip.com) for the latest dsPIC33F/PIC24H Family Reference Manual sections.

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

This document contains device specific information for the PIC24HJ32GP302/304, PIC24HJ64GPX02/X04 and PIC24HJ128GPX02/X04 devices.

Figure 1-1 shows a general block diagram of the core and peripheral modules in the PIC24HJ32GP302/304, PIC24HJ64GPX02/X04 and PIC24HJ128GPX02/X04 families of devices.

Table 1-1lists the functions of the various pinsshown in the pinout diagrams.

## 4.0 MEMORY ORGANIZATION

| Note: | This data sheet summarizes the features      |

|-------|----------------------------------------------|

|       | of the PIC24HJ32GP302/304,                   |

|       | PIC24HJ64GPX02/X04 and                       |

|       | PIC24HJ128GPX02/X04 families of              |

|       | devices. It is not intended to be a compre-  |

|       | hensive reference source. To complement      |

|       | the information in this data sheet, refer to |

|       | Section 4. "Program Memory"                  |

|       | (DS70203) of the "dsPIC33F/PIC24H            |

|       | Family Reference Manual", which is avail-    |

|       | able from the Microchip web site             |

|       | (www.microchip.com).                         |

The PIC24HJ32GP302/304, PIC24HJ64GPX02/X04 and PIC24HJ128GPX02/X04 architecture features separate program and data memory spaces and buses. This architecture also allows the direct access of program memory from the data space during code execution.

## 4.1 Program Address Space

The program address memory space of the PIC24HJ32GP302/304, PIC24HJ64GPX02/X04 and PIC24HJ128GPX02/X04 devices is 4M instructions. The space is addressable by a 24-bit value derived either from the 23-bit Program Counter (PC) during program execution, or from table operation or data space remapping as described in Section 4.6 "Interfacing Program and Data Memory Spaces".

User application access to the program memory space is restricted to the lower half of the address range (0x000000 to 0x7FFFFF). The exception is the use of TBLRD/TBLWT operations, which use TBLPAG<7> to permit access to the Configuration bits and Device ID sections of the configuration memory space.

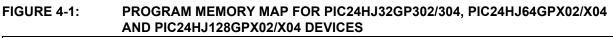

The memory map for the PIC24HJ32GP302/304, PIC24HJ64GPX02/X04 and PIC24HJ128GPX02/X04 devices is shown in Figure 4-1.

|      | PIC24HJ32GP302/304                                   | PIC24HJ64GPX02/X04                | PIC24HJ128GPX02/X04                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|------|------------------------------------------------------|-----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4    | GOTO Instruction                                     | GOTO Instruction                  | GOTO Instruction 0x000000<br>Reset Address 0x000002                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|      | Reset Address                                        | Reset Address                     | 0x000004                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|      | Interrupt Vector Table                               | Interrupt Vector Table            | Interrupt Vector Table 0x0000FE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|      | Reserved                                             | Reserved                          | <u>Reserved</u> 0x000100<br>0x000104                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|      | Alternate Vector Table                               | Alternate Vector Table            | Alternate vector rable 0x0001FE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 2000 | User Program<br>Flash Memory<br>(11264 instructions) | User Program<br>Flash Memory      | 0x000200<br>0x0057FE<br>0x0057FE<br>0x005800                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|      | Unimplemented                                        |                                   | User Program<br>Flash Memory<br>(44032 instructions)<br>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|      | (Read '0's)                                          | Unimplemented                     | 0x0157FE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|      |                                                      | (Read '0's)                       | 0x015800                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|      |                                                      |                                   | Unimplemented<br>(Read '0's)<br>0x7FFFE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|      | Reserved                                             | Reserved                          | 0x800000<br>Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|      | Device Configuration<br>Registers                    | Device Configuration<br>Registers | Device Configuration 0xF7FFE<br>Device Configuration 0xF80000<br>Registers 0xF80017                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|      | Reserved                                             | Reserved                          | Care Control C |

| 0    |                                                      |                                   | DEVID (2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|      | Reserved                                             | Reserved                          | 0xFF0002           Reserved           0xFFFFE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

## 4.4 Special Function Register Maps

## TABLE 4-1: CPU CORE REGISTERS MAP

|             | <b>T</b> I. |        |        |        |        |        |        |         |                |                |            |           |                |              |             |        |       |               |

|-------------|-------------|--------|--------|--------|--------|--------|--------|---------|----------------|----------------|------------|-----------|----------------|--------------|-------------|--------|-------|---------------|

| SFR<br>Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9   | Bit 8          | Bit 7          | Bit 6      | Bit 5     | Bit 4          | Bit 3        | Bit 2       | Bit 1  | Bit 0 | All<br>Resets |

| WREG0       | 0000        |        |        |        |        |        |        |         | Working Re     | gister 0       |            |           |                |              |             |        |       | 0000          |

| WREG1       | 0002        |        |        |        |        |        |        |         | Working Re     | gister 1       |            |           |                |              |             |        |       | 0000          |

| WREG2       | 0004        |        |        |        |        |        |        |         | Working Re     | egister 2      |            |           |                |              |             |        |       | 0000          |

| WREG3       | 0006        |        |        |        |        |        |        |         | Working Re     | egister 3      |            |           |                |              |             |        |       | 0000          |

| WREG4       | 8000        |        |        |        |        |        |        |         | Working Re     | egister 4      |            |           |                |              |             |        |       | 0000          |

| WREG5       | 000A        |        |        |        |        |        |        |         | Working Re     | egister 5      |            |           |                |              |             |        |       | 0000          |

| WREG6       | 000C        |        |        |        |        |        |        |         | Working Re     | egister 6      |            |           |                |              |             |        |       | 0000          |

| WREG7       | 000E        |        |        |        |        |        |        |         | Working Re     | egister 7      |            |           |                |              |             |        |       | 0000          |

| WREG8       | 0010        |        |        |        |        |        |        |         | Working Re     | egister 8      |            |           |                |              |             |        |       | 0000          |

| WREG9       | 0012        |        |        |        |        |        |        |         | Working Re     | egister 9      |            |           |                |              |             |        |       | 0000          |

| WREG10      | 0014        |        |        |        |        |        |        |         | Working Reg    | gister 10      |            |           |                |              |             |        |       | 0000          |

| WREG11      | 0016        |        |        |        |        |        |        |         | Working Reg    | gister 11      |            |           |                |              |             |        |       | 0000          |

| WREG12      | 0018        |        |        |        |        |        |        |         | Working Reg    | gister 12      |            |           |                |              |             |        |       | 0000          |

| WREG13      | 001A        |        |        |        |        |        |        |         | Working Reg    | gister 13      |            |           |                |              |             |        |       | 0000          |

| WREG14      | 001C        |        |        |        |        |        |        |         | Working Reg    | gister 14      |            |           |                |              |             |        |       | 0000          |

| WREG15      | 001E        |        |        |        |        |        |        |         | Working Reg    | gister 15      |            |           |                |              |             |        |       | 0800          |

| SPLIM       | 0020        |        |        |        |        |        |        | Sta     | ack Pointer Li | mit Register   |            |           |                |              |             |        |       | XXXX          |

| PCL         | 002E        |        |        |        |        |        |        | Program | m Counter Lo   | w Word Regi    | ster       |           |                |              |             |        |       | 0000          |

| PCH         | 0030        | _      |        | —      | _      | _      | _      |         | _              |                |            | Progra    | am Counter     | High Byte Re | egister     |        |       | 0000          |

| TBLPAG      | 0032        | _      |        | —      | —      | _      |        |         | —              |                |            | Table     | Page Addre     | ss Pointer R | egister     |        |       | 0000          |

| PSVPAG      | 0034        | -      |        | —      | _      | _      |        |         | —              |                | Prog       | ram Memor | y Visibility P | age Address  | Pointer Reg | gister |       | 0000          |

| RCOUNT      | 0036        |        |        |        |        |        |        | Rep     | eat Loop Cou   | unter Register | r          |           |                |              |             |        |       | XXXX          |

| SR          | 0042        | _      |        | —      | —      | _      | _      |         | DC             | IPL2           | IPL1       | IPL0      | RA             | Ν            | OV          | Z      | С     | 0000          |

| CORCON      | 0044        | _      | _      | _      | —      | _      | _      | _       | -              | _              | _          | _         | _              | IPL3         | PSV         | _      | _     | 0000          |

| DISICNT     | 0052        | _      |        |        |        |        |        |         | Disab          | le Interrupts  | Counter Re | egister   |                |              |             |        |       | XXXX          |

|             |             |        |        |        |        |        |        |         |                |                |            |           |                |              |             |        |       |               |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## 4.6 Interfacing Program and Data Memory Spaces

The PIC24HJ32GP302/304, PIC24HJ64GPX02/X04 and PIC24HJ128GPX02/X04 architecture uses a 24-bit-wide program space and a 16-bit-wide data space. The architecture is also a modified Harvard scheme, meaning that data can also be present in the program space. To use this data successfully, it must be accessed in a way that preserves the alignment of information in both spaces.

Aside from normal execution, the PIC24HJ32GP302/304, PIC24HJ64GPX02/X04 and PIC24HJ128GPX02/X04 architecture provides two methods by which program space can be accessed during operation:

- Using table instructions to access individual bytes or words anywhere in the program space

- Remapping a portion of the program space into the data space (Program Space Visibility)

Table instructions allow an application to read or write to small areas of the program memory. This capability makes the method ideal for accessing data tables that need to be updated periodically. It also allows access to all bytes of the program word. The remapping method allows an application to access a large block of data on a read-only basis, which is ideal for look-ups from a large table of static data. The application can only access the least significant word of the program word.

## 4.6.1 ADDRESSING PROGRAM SPACE

Since the address ranges for the data and program spaces are 16 and 24 bits, respectively, a method is needed to create a 23-bit or 24-bit program address from 16-bit data registers. The solution depends on the interface method to be used.

For table operations, the 8-bit Table Page register (TBLPAG) is used to define a 32K word region within the program space. This is concatenated with a 16-bit EA to arrive at a full 24-bit program space address. In this format, the Most Significant bit (MSb) of TBLPAG is used to determine if the operation occurs in the user memory (TBLPAG<7> = 0) or the configuration memory (TBLPAG<7> = 1).

For remapping operations, the 8-bit Program Space Visibility register (PSVPAG) is used to define a 16K word page in the program space. When the MSb of the EA is '1', PSVPAG is concatenated with the lower 15 bits of the EA to form a 23-bit program space address. Unlike table operations, this limits remapping operations strictly to the user memory area.

Table 4-36 and Figure 4-6 show how the program EA is created for table operations and remapping accesses from the data EA. Here, P<23:0> refers to a program space word, and D<15:0> refers to a data space word.

|                          | Access        | Program Space Address |            |                                      |                   |       |  |  |  |  |

|--------------------------|---------------|-----------------------|------------|--------------------------------------|-------------------|-------|--|--|--|--|

| Access Type              | Space         | <23>                  | <22:16>    | <15>                                 | <14:1>            | <0>   |  |  |  |  |

| Instruction Access       | User          | 0 PC<22:1>            |            |                                      |                   | 0     |  |  |  |  |

| (Code Execution)         |               |                       | 0xx xxxx x | XXX XXXX                             | x xxxx xxx0       |       |  |  |  |  |

| TBLRD/TBLWT              | User          | TB                    | LPAG<7:0>  | Data EA<15:0>                        |                   |       |  |  |  |  |

| (Byte/Word Read/Write)   |               | 0                     | XXX XXXX   | XXXX XX                              | ***               |       |  |  |  |  |

|                          | Configuration | TB                    | LPAG<7:0>  | Data EA<15:0>                        |                   |       |  |  |  |  |

|                          |               | 1                     | XXX XXXX   | XXXX X                               | XXX XXXX XXXX     |       |  |  |  |  |

| Program Space Visibility | User          | 0                     | PSVPAG<7   | AG<7:0> Data EA<14:0> <sup>(1)</sup> |                   | 0>(1) |  |  |  |  |

| (Block Remap/Read)       |               | 0                     | XXXX XXXX  | K                                    | XXX XXXX XXXX XXX |       |  |  |  |  |

**Note 1:** Data EA<15> is always '1' in this case, but is not used in calculating the program space address. Bit 15 of the address is PSVPAG<0>.

| REGISTER 7-13: | IEC3: INTERRUPT ENABLE CONTROL REGISTER 3 |

|----------------|-------------------------------------------|

|----------------|-------------------------------------------|

| U-0             | R/W-0           | R/W-0            | U-0            | U-0              | U-0              | U-0             | U-0   |

|-----------------|-----------------|------------------|----------------|------------------|------------------|-----------------|-------|

| _               | RTCIE           | DMA5IE           | —              | _                | —                | —               | —     |

| bit 15          |                 | -                |                |                  |                  |                 | bit 8 |

|                 |                 |                  |                |                  |                  |                 |       |

| U-0             | U-0             | U-0              | U-0            | U-0              | U-0              | U-0             | U-0   |

| —               | —               | —                | _              | —                | —                | —               | —     |

| bit 7           |                 |                  |                |                  |                  |                 | bit 0 |

|                 |                 |                  |                |                  |                  |                 |       |

| Legend:         |                 |                  |                |                  |                  |                 |       |

| R = Readable    | bit             | W = Writable     | bit            | U = Unimpler     | nented bit, read | as '0'          |       |

| -n = Value at F | POR             | '1' = Bit is set |                | '0' = Bit is cle | ared             | x = Bit is unkr | nown  |

|                 |                 |                  |                |                  |                  |                 |       |

| bit 15          | Unimplemen      | ted: Read as '   | )'             |                  |                  |                 |       |

| bit 14          | RTCIE: Real-    | Time Clock and   | d Calendar Int | errupt Enable    | bit              |                 |       |

|                 | 1 = Interrupt i | request enabled  | b              |                  |                  |                 |       |

0 = Interrupt request not enabled

bit 13 DMA5IE: DMA Channel 5 Data Transfer Complete Interrupt Enable bit

1 = Interrupt request enabled

0 = Interrupt request not enabled

bit 12-0 Unimplemented: Read as '0'

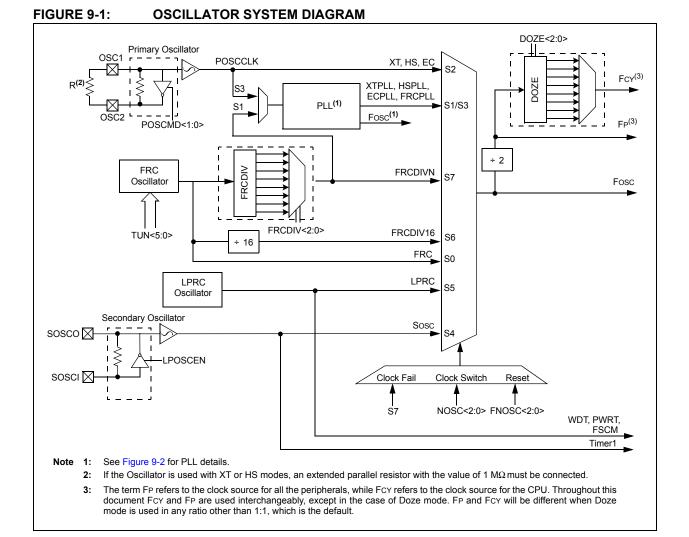

## 9.0 OSCILLATOR CONFIGURATION

- Note 1: This data sheet summarizes the features PIC24HJ32GP302/304 of the PIC24HJ64GPX02/X04 and PIC24HJ128GPX02/X04 families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 39. "Oscillator (Part III)" (DS70216) of the "dsPIC33F/ PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The PIC24HJ32GP302/304, PIC24HJ64GPX02/X04 and PIC24HJ128GPX02/X04 oscillator system provides:

- External and internal oscillator options as clock sources

- An on-chip Phase-Locked Loop (PLL) to scale the internal operating frequency to the required system clock frequency

- An internal FRC oscillator that can also be used with the PLL, thereby allowing full-speed operation without any external clock generation hardware

- Clock switching between various clock sources

- Programmable clock postscaler for system power savings

- A Fail-Safe Clock Monitor (FSCM) that detects clock failure and takes fail-safe measures

- An Oscillator Control register (OSCCON)

- Nonvolatile Configuration bits for main oscillator selection.

- A simplified diagram of the oscillator system is shown in Figure 9-1.

| REGISTER                          | 9-3: PLLFI                          | BD: PLL FEE                                                                 | DBACK DIV | ISUR REGIS                              | IER' / |       |           |  |  |  |  |

|-----------------------------------|-------------------------------------|-----------------------------------------------------------------------------|-----------|-----------------------------------------|--------|-------|-----------|--|--|--|--|

| U-0                               | U-0                                 | U-0                                                                         | U-0       | U-0                                     | U-0    | U-0   | R/W-0     |  |  |  |  |

| _                                 | —                                   | —                                                                           | _         | —                                       | _      | _     | PLLDIV<8> |  |  |  |  |

| bit 15                            |                                     |                                                                             |           |                                         |        |       | bit       |  |  |  |  |

| R/W-0                             | R/W-0                               | R/W-1                                                                       | R/W-1     | R/W-0                                   | R/W-0  | R/W-0 | R/W-0     |  |  |  |  |

| 10000                             | 1000 0                              | 1000 1                                                                      |           | V<7:0>                                  | 10000  | 10000 | 10000     |  |  |  |  |

| bit 7                             |                                     |                                                                             |           |                                         |        |       | bit       |  |  |  |  |

|                                   |                                     |                                                                             |           |                                         |        |       |           |  |  |  |  |

| Legend:                           | - 1-14                              |                                                                             | L 14      |                                         |        | (0)   |           |  |  |  |  |

| R = Readable bit W = Writable bit |                                     |                                                                             |           | U = Unimpler                            |        |       |           |  |  |  |  |

| -n = Value at                     | POR                                 | '1' = Bit is set                                                            |           | '0' = Bit is cleared x = Bit is unknown |        |       |           |  |  |  |  |

| bit 15-9                          | Unimplemer                          | nted: Read as '                                                             | 0'        |                                         |        |       |           |  |  |  |  |

| bit 8-0                           | PLLDIV<8:0                          | LLDIV<8:0>: PLL Feedback Divisor bits (also denoted as 'M', PLL multiplier) |           |                                         |        |       |           |  |  |  |  |

|                                   | 111111111                           | = 513                                                                       |           |                                         |        |       |           |  |  |  |  |

|                                   | •                                   |                                                                             |           |                                         |        |       |           |  |  |  |  |

|                                   | •                                   |                                                                             |           |                                         |        |       |           |  |  |  |  |

|                                   | •                                   |                                                                             |           |                                         |        |       |           |  |  |  |  |

|                                   | 000110000                           | = 50 (default)                                                              |           |                                         |        |       |           |  |  |  |  |

|                                   | •                                   |                                                                             |           |                                         |        |       |           |  |  |  |  |

|                                   | •                                   |                                                                             |           |                                         |        |       |           |  |  |  |  |

|                                   | •                                   |                                                                             |           |                                         |        |       |           |  |  |  |  |

|                                   | 000000010<br>000000001<br>000000000 | = 3                                                                         |           |                                         |        |       |           |  |  |  |  |

## REGISTER 9-3: PLLFBD: PLL FEEDBACK DIVISOR REGISTER<sup>(1)</sup>

Note 1: This register is reset only on a Power-on Reset (POR).

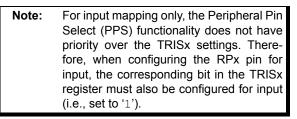

## 11.6 Peripheral Pin Select

Peripheral pin select configuration enables peripheral set selection and placement on a wide range of I/O pins. By increasing the pinout options available on a particular device, programmers can better tailor the microcontroller to their entire application, rather than trimming the application to fit the device.

The peripheral pin select configuration feature operates over a fixed subset of digital I/O pins. Programmers can independently map the input and/or output of most digital peripherals to any one of these I/O pins. Peripheral pin select is performed in software, and generally does not require the device to be reprogrammed. Hardware safeguards are included that prevent accidental or spurious changes to the peripheral mapping, once it has been established.

### 11.6.1 AVAILABLE PINS

The peripheral pin select feature is used with a range of up to 26 pins. The number of available pins depends on the particular device and its pin count. Pins that support the peripheral pin select feature include the designation "RPn" in their full pin designation, where "RP" designates a remappable peripheral and "n" is the remappable pin number.

#### 11.6.2 CONTROLLING PERIPHERAL PIN SELECT

Peripheral pin select features are controlled through two sets of special function registers: one to map peripheral inputs, and another one to map outputs. Because they are separately controlled, a particular peripheral's input and output (if the peripheral has both) can be placed on any selectable function pin without constraint.

The association of a peripheral to a peripheral selectable pin is handled in two different ways, depending on whether an input or output is being mapped.

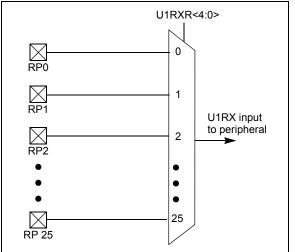

### 11.6.2.1 Input Mapping

The inputs of the peripheral pin select options are mapped on the basis of the peripheral. A control register associated with a peripheral dictates the pin it is mapped to. The RPINRx registers are used to configure peripheral input mapping (see Register 11-1 through Register 11-14). Each register contains sets of 5-bit fields, with each set associated with one of the remappable peripherals. Programming a given peripheral's bit field with an appropriate 5-bit value maps the RPn pin with that value to that peripheral. For any given device, the valid range of values for any bit field corresponds to the maximum number of peripheral pin selections supported by the device.

Figure 11-2 illustrates remappable pin selection for U1RX input.

### FIGURE 11-2: REMAPPABLE MUX INPUT FOR U1RX

| REGISTER     | 11-3: RPIN            | R3: PERIPHE                               | RAL PIN SI | ELECT INPU       | T REGISTER      | 83              |       |

|--------------|-----------------------|-------------------------------------------|------------|------------------|-----------------|-----------------|-------|

| U-0          | U-0                   | U-0                                       | R/W-1      | R/W-1            | R/W-1           | R/W-1           | R/W-1 |

| _            | _                     | _                                         |            |                  | T3CKR<4:0       | )>              |       |

| bit 15       | ·                     | ·                                         | •          |                  |                 |                 | bit 8 |

| U-0          | U-0                   | U-0                                       | R/W-1      | R/W-1            | R/W-1           | R/W-1           | R/W-1 |

| _            | —                     | —                                         |            |                  | T2CKR<4:0       | )>              |       |

| bit 7        | ·                     | ·                                         |            |                  |                 |                 | bit ( |

| Legend:      |                       |                                           |            |                  |                 |                 |       |

| R = Readab   | le bit                | W = Writable                              | bit        | U = Unimple      | mented bit, rea | ad as '0'       |       |

| -n = Value a | t POR                 | '1' = Bit is set                          |            | '0' = Bit is cle | eared           | x = Bit is unki | nown  |

|              | •<br>•<br>00001 = Inp | but tied to RP25                          |            |                  |                 |                 |       |

| bit 7-5      | •                     | out tied to RP0<br><b>nted:</b> Read as ' | n <b>'</b> |                  |                 |                 |       |

| bit 4-0      | •                     | >: Assign Timer                           |            | ock (T2CK) to t  | the correspond  | lina RPn nin    |       |

| 511 4-0      | 11111 <b>= Inp</b>    | out tied to Vss<br>out tied to RP25       |            |                  |                 |                 |       |

|              | •                     |                                           |            |                  |                 |                 |       |

|              | •                     |                                           |            |                  |                 |                 |       |

|              | •                     | ut find to DD1                            |            |                  |                 |                 |       |

|              |                       | but tied to RP1                           |            |                  |                 |                 |       |

00000 = Input tied to RP0

### REGISTER 11-11: RPINR21: PERIPHERAL PIN SELECT INPUT REGISTER 21

| bit 7  | -   | ÷   |       |       |           |       | bit C |

|--------|-----|-----|-------|-------|-----------|-------|-------|

|        |     |     |       |       | SS1R<4:0> |       |       |

| U-0    | U-0 | U-0 | R/W-1 | R/W-1 | R/W-1     | R/W-1 | R/W-1 |

| bit 15 |     |     |       |       |           |       | bit 8 |

| _      | —   | —   | _     | —     | _         | —     | —     |

| U-0    | U-0 | U-0 | U-0   | U-0   | U-0       | U-0   | U-0   |

bit 15-5 Unimplemented: Read as '0'

bit 4-0

SS1R<4:0>: Assign SPI1 Slave Select Input (SS1) to the corresponding RPn pin 11111 = Input tied to Vss 11001 = Input tied to RP25

00001 = Input tied to RP1 00000 = Input tied to RP0

## PIC24HJ32GP302/304, PIC24HJ64GPX02/X04 AND PIC24HJ128GPX02/X04

| BUFFER 19-3     | : ECAN                      | MESSAGE                    | BUFFER V     | VORD 2           |                  |                 |       |

|-----------------|-----------------------------|----------------------------|--------------|------------------|------------------|-----------------|-------|

| R/W-x           | R/W-x                       | R/W-x                      | R/W-x        | R/W-x            | R/W-x            | R/W-x           | R/W-x |

| EID5            | EID4                        | EID3                       | EID2         | EID1             | EID0             | RTR             | RB1   |

| bit 15          |                             |                            |              |                  |                  |                 | bit 8 |

| U-0             | U-0                         | U-0                        | R/W-x        | R/W-x            | R/W-x            | R/W-x           | R/W-x |

|                 |                             | _                          | RB0          | DLC3             | DLC2             | DLC1            | DLC0  |

| bit 7           |                             |                            |              |                  |                  |                 | bit 0 |

|                 |                             |                            |              |                  |                  |                 |       |

| Legend:         |                             |                            |              |                  |                  |                 |       |

| R = Readable b  | bit                         | W = Writable               | bit          | U = Unimpler     | nented bit, read | l as '0'        |       |

| -n = Value at P | OR                          | '1' = Bit is set           |              | '0' = Bit is cle | ared             | x = Bit is unkr | nown  |

| bit 15-10       | <b>EID&lt;5:0&gt;:</b> Ex   | tended Identifie           | er bits      |                  |                  |                 |       |

| bit 9           | RTR: Remote                 | Transmission               | Request bit  |                  |                  |                 |       |

|                 | 1 = Message<br>0 = Normal m | will request rer<br>essage | note transmi | ssion            |                  |                 |       |

| bit 8           | RB1: Reserve                | ed Bit 1                   |              |                  |                  |                 |       |

|         | User must set this bit to '0' per CAN protocol. |

|---------|-------------------------------------------------|

| bit 7-5 | Unimplemented: Read as '0'                      |

| bit 4   | RB0: Reserved Bit 0                             |

|         | User must set this bit to '0' per CAN protocol. |

| bit 3-0 | DLC<3:0>: Data Length Code bits                 |

#### BUFFER 19-4: ECAN™ MESSAGE BUFFER WORD 3

| R/W-x            | R/W-x | R/W-x            | R/W-x | R/W-x             | R/W-x           | R/W-x           | R/W-x |

|------------------|-------|------------------|-------|-------------------|-----------------|-----------------|-------|

|                  |       |                  | B     | yte 1             |                 |                 |       |

| bit 15           |       |                  |       |                   |                 |                 | bit 8 |

|                  |       |                  |       |                   |                 |                 |       |

| R/W-x            | R/W-x | R/W-x            | R/W-x | R/W-x             | R/W-x           | R/W-x           | R/W-x |

|                  |       |                  | B     | yte 0             |                 |                 |       |

| bit 7            |       |                  |       |                   |                 |                 | bit 0 |

| Legend:          |       |                  |       |                   |                 |                 |       |

| R = Readable bit |       | W = Writable bit | t     | U = Unimplen      | nented bit, rea | ad as '0'       |       |

| -n = Value at PO | R     | '1' = Bit is set |       | '0' = Bit is clea | ared            | x = Bit is unkr | nown  |

bit 15-8 Byte 1<15:8>: ECAN™ Message Byte 0

bit 7-0 Byte 0<7:0>: ECAN Message Byte 1

### BUFFER 19-5: ECAN™ MESSAGE BUFFER WORD 4

| R/W-x           | R/W-x | R/W-x            | R/W-x | R/W-x            | R/W-x            | R/W-x           | R/W-x  |

|-----------------|-------|------------------|-------|------------------|------------------|-----------------|--------|

| TOTT X          | TOT A | TOTT A           |       | te 3             |                  |                 | 1017 / |

| 1.1.45          |       |                  | By    |                  |                  |                 | 1.1.0  |

| bit 15          |       |                  |       |                  |                  |                 | bit 8  |

|                 |       |                  |       |                  |                  |                 |        |

| R/W-x           | R/W-x | R/W-x            | R/W-x | R/W-x            | R/W-x            | R/W-x           | R/W-x  |

|                 |       |                  | By    | te 2             |                  |                 |        |

| bit 7           |       |                  |       |                  |                  |                 | bit 0  |

| Legend:         |       |                  |       |                  |                  |                 |        |

| R = Readable I  | oit   | W = Writable     | bit   | U = Unimplen     | nented bit, read | d as '0'        |        |

| -n = Value at P | OR    | '1' = Bit is set |       | '0' = Bit is cle | ared             | x = Bit is unkr | nown   |

bit 15-8 Byte 3<15:8>: ECAN™ Message Byte 3

bit 7-0 Byte 2<7:0>: ECAN Message Byte 2

#### BUFFER 19-6: ECAN™ MESSAGE BUFFER WORD 5

| R/W-x  | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x |  |  |  |

|--------|-------|-------|-------|-------|-------|-------|-------|--|--|--|

| Byte 5 |       |       |       |       |       |       |       |  |  |  |

| bit 15 |       |       |       |       |       |       |       |  |  |  |

| R/W-x            | R/W-x | R/W-x            | R/W-x | R/W-x             | R/W-x            | R/W-x             | R/W-x |

|------------------|-------|------------------|-------|-------------------|------------------|-------------------|-------|

|                  |       |                  | Ву    | te 4              |                  |                   |       |

| bit 7            |       |                  |       |                   |                  |                   | bit 0 |

| Legend:          |       |                  |       |                   |                  |                   |       |

| R = Readable b   | bit   | W = Writable bit | t     | U = Unimplem      | nented bit, read | d as '0'          |       |

| -n = Value at Po | OR    | '1' = Bit is set |       | '0' = Bit is clea | ared             | x = Bit is unknow | 'n    |

bit 15-8 Byte 5<15:8>: ECAN™ Message Byte 5

bit 7-0 Byte 4<7:0>: ECAN Message Byte 4

## REGISTER 24-1: PMCON: PARALLEL PORT CONTROL REGISTER (CONTINUED)

| bit 2 | <b>BEP:</b> Byte Enable Polarity bit<br>1 = Byte enable active-high (PMBE)<br>0 = Byte enable active-low (PMBE) |

|-------|-----------------------------------------------------------------------------------------------------------------|

| bit 1 | WRSP: Write Strobe Polarity bit                                                                                 |

|       | For Slave modes and Master mode 2 (PMMODE<9:8> = 00,01,10):                                                     |

|       | 1 = Write strobe active-high (PMWR)                                                                             |

|       | 0 = Write strobe active-low (PMWR)                                                                              |

|       | For Master mode 1 (PMMODE<9:8> = 11):                                                                           |

|       | 1 = Enable strobe active-high (PMENB)                                                                           |

|       | 0 = Enable strobe active-low (PMENB)                                                                            |

| bit 0 | RDSP: Read Strobe Polarity bit                                                                                  |

|       | For Slave modes and Master mode 2 (PMMODE<9:8> = 00,01,10):                                                     |

|       | 1 = Read strobe active-high (PMRD)                                                                              |

|       | 0 = Read strobe active-low (PMRD)                                                                               |

|       | For Master mode 1 (PMMODE<9:8> = 11):                                                                           |

|       | 1 = Read/write strobe active-high (PMRD/PMWR)                                                                   |

|       | 0 = Read/write strobe active-low (PMRD/PMWR)                                                                    |

**Note 1:** These bits have no effect when their corresponding pins are used as address lines.

## TABLE 25-3: CODE FLASH SECURITY SEGMENT SIZES FOR 32 KB DEVICES