Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| 2 0 0 0 0 0 0              |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 40 MIPs                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                     |

| Number of I/O              | 35                                                                             |

| Program Memory Size        | 128KB (43K x 24)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | · ·                                                                            |

| RAM Size                   | 8K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                      |

| Data Converters            | A/D 13x10b/12b                                                                 |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 44-TQFP                                                                        |

| Supplier Device Package    | 44-TQFP (10x10)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24hj128gp204-i-pt |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 5.0 FLASH PROGRAM MEMORY

- **Note 1:** This data sheet summarizes the features the PIC24HJ32GP302/304. of PIC24HJ64GPX02/X04 and PIC24HJ128GPX02/X04 families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 5. "Flash Programming" (DS70191) of the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The PIC24HJ32GP302/304, PIC24HJ64GPX02/X04 and PIC24HJ128GPX02/X04 devices contain internal Flash program memory for storing and executing application code. The memory is readable, writable and erasable during normal operation over the entire VDD range.

Flash memory can be programmed in two ways:

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) programming capability

- Run-Time Self-Programming (RTSP)

ICSP allows the PIC24HJ32GP302/304, PIC24HJ64GPX02/X04 and PIC24HJ128GPX02/X04 devices to be serially programmed while in the end application circuit. This is done with two lines for programming clock and programming data (one of the alternate programming pin pairs: PGEC1/PGED1, PGEC2/PGED2 or PGEC3/PGED3), and three other lines for power (VDD), ground (VSS) and Master Clear (MCLR). This allows customers to manufacture boards with unprogrammed devices and then program the microcontroller just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed.

RTSP is accomplished using TBLRD (table read) and TBLWT (table write) instructions. With RTSP, the user application can write program memory data either in blocks or 'rows' of 64 instructions (192 bytes) at a time or a single program memory word, and erase program memory in blocks or 'pages' of 512 instructions (1536 bytes) at a time.

## 5.1 Table Instructions and Flash Programming

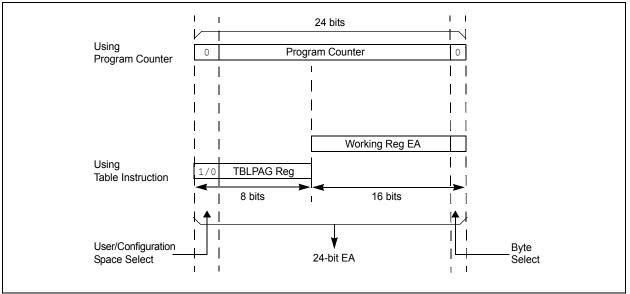

Regardless of the method used, all programming of Flash memory is done with the table read and table write instructions. These allow direct read and write access to the program memory space from the data memory while the device is in normal operating mode. The 24-bit target address in the program memory is formed using bits <7:0> of the TBLPAG register and the Effective Address (EA) from a W register specified in the table instruction, as shown in Figure 5-1.

The TBLRDL and the TBLWTL instructions are used to read or write to bits <15:0> of program memory. TBLRDL and TBLWTL can access program memory in both Word and Byte modes.

The TBLRDH and TBLWTH instructions are used to read or write to bits <23:16> of program memory. TBLRDH and TBLWTH can also access program memory in Word or Byte mode.

### FIGURE 5-1: ADDRESSING FOR TABLE REGISTERS

## 6.0 RESETS

- **Note 1:** This data sheet summarizes the features PIC24HJ32GP302/304. of the PIC24HJ64GPX02/X04 and PIC24HJ128GPX02/X04 families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 8. "Reset" (DS70192) of the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

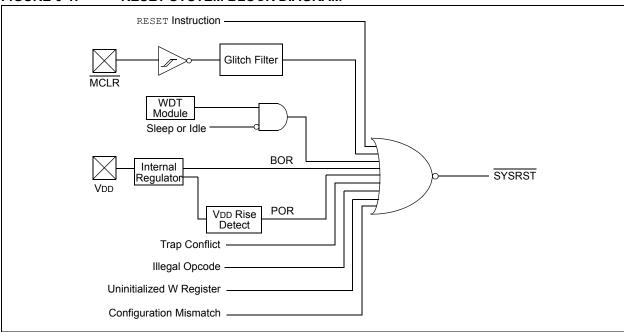

The Reset module combines all reset sources and controls the device Master Reset Signal, SYSRST. The following is a list of device Reset sources:

- POR: Power-on Reset

- BOR: Brown-out Reset

- MCLR: Master Clear Pin Reset

- SWR: RESET Instruction

- WDTO: Watchdog Timer Reset

- CM: Configuration Mismatch Reset

- TRAPR: Trap Conflict Reset

- · IOPUWR: Illegal Condition Device Reset

- Illegal Opcode Reset

- Uninitialized W Register Reset

- Security Reset

#### FIGURE 6-1:

### RESET SYSTEM BLOCK DIAGRAM

A simplified block diagram of the Reset module is shown in Figure 6-1.

Any active source of reset will make the SYSRST signal active. On system Reset, some of the registers associated with the CPU and peripherals are forced to a known Reset state and some are unaffected.

Note: Refer to the specific peripheral section or Section 3.0 "CPU" of this manual for register Reset states.

All types of device Reset sets a corresponding status bit in the RCON register to indicate the type of Reset (see Register 6-1).

A POR clears all the bits, except for the POR bit (RCON<0>), that are set. The user application can set or clear any bit at any time during code execution. The RCON bits only serve as status bits. Setting a particular Reset status bit in software does not cause a device Reset to occur.

The RCON register also has other bits associated with the Watchdog Timer and device power-saving states. The function of these bits is discussed in other sections of this manual.

**Note:** The status bits in the RCON register should be cleared after they are read so that the next RCON register value after a device Reset is meaningful.

## 6.1 Reset Resources

Many useful resources related to Resets are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this URL in your browser: |

|-------|----------------------------------------------------------------------------------------------------------------|

|       | http://www.microchip.com/wwwproducts/<br>Devices.aspx?dDocName=en534555                                        |

## 6.1.1 KEY RESOURCES

- Section 8. "Resets" (DS70192)

- Code Samples

- Application Notes

- Software Libraries

- · Webinars

- All related dsPIC33F/PIC24H Family Reference Manuals Sections

- Development Tools

### 6.2 Reset Control Registers

#### U-0 R/W-0 R/W-0 R/W-0 U-0 U-0 R/W-0 U-0 TRAPR **IOPUWR** CM VREGS bit 15 bit 8 R/W-0 R/W-0 R/W-0 R/W-1 R/W-0 R/W-0 R/W-0 R/W-1 SWDTEN<sup>(2)</sup> EXTR SWR WDTO SLEEP IDLE BOR POR bit 7 bit 0 Legend: R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown bit 15 TRAPR: Trap Reset Flag bit 1 = A Trap Conflict Reset has occurred 0 = A Trap Conflict Reset has not occurred IOPUWR: Illegal Opcode or Uninitialized W Access Reset Flag bit bit 14 1 = An illegal opcode detection, an illegal address mode or uninitialized W register used as an Address Pointer caused a Reset 0 = An illegal opcode or uninitialized W Reset has not occurred Unimplemented: Read as '0' bit 13-10 bit 9 **CM:** Configuration Mismatch Flag bit 1 = A configuration mismatch Reset has occurred. 0 = A configuration mismatch Reset has NOT occurred bit 8 VREGS: Voltage Regulator Standby During Sleep bit 1 = Voltage regulator is active during Sleep 0 = Voltage regulator goes into Standby mode during Sleep bit 7 EXTR: External Reset (MCLR) Pin bit 1 = A Master Clear (pin) Reset has occurred 0 = A Master Clear (pin) Reset has not occurred bit 6 SWR: Software Reset (Instruction) Flag bit 1 = A RESET instruction has been executed 0 = A RESET instruction has not been executed bit 5 SWDTEN: Software Enable/Disable of WDT bit<sup>(2)</sup> 1 = WDT is enabled 0 = WDT is disabled bit 4 WDTO: Watchdog Timer Time-out Flag bit 1 = WDT time-out has occurred 0 = WDT time-out has not occurred bit 3 **SLEEP:** Wake-up from Sleep Flag bit 1 = Device has been in Sleep mode 0 = Device has not been in Sleep mode bit 2 IDLE: Wake-up from Idle Flag bit 1 = Device was in Idle mode 0 = Device was not in Idle mode Note 1: All of the Reset status bits can be set or cleared in software. Setting one of these bits in software does not

### REGISTER 6-1: RCON: RESET CONTROL REGISTER<sup>(1)</sup>

**Note 1:** All of the Reset status bits can be set or cleared in software. Setting one of these bits in software does not cause a device Reset.

2: If the FWDTEN Configuration bit is '1' (unprogrammed), the WDT is always enabled, regardless of the SWDTEN bit setting.

# **REGISTER 6-1: RCON: RESET CONTROL REGISTER<sup>(1)</sup> (CONTINUED)**

- bit 1BOR: Brown-out Reset Flag bit1 = A Brown-out Reset has occurred0 = A Brown-out Reset has not occurredbit 0POR: Power-on Reset Flag bit

- 1 = A Power-on Reset has occurred

0 = A Power-on Reset has not occurred

- **Note 1:** All of the Reset status bits can be set or cleared in software. Setting one of these bits in software does not cause a device Reset.

- 2: If the FWDTEN Configuration bit is '1' (unprogrammed), the WDT is always enabled, regardless of the SWDTEN bit setting.

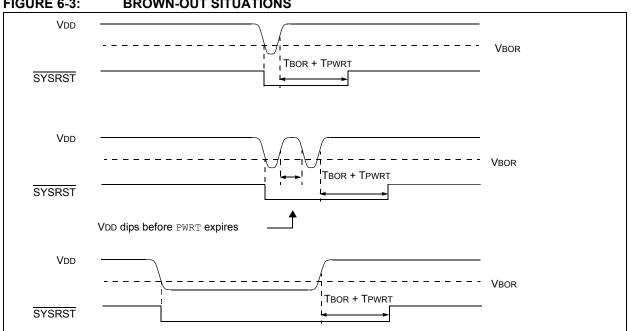

#### **BROWN-OUT SITUATIONS** FIGURE 6-3:

#### 6.5 **External Reset (EXTR)**

The external Reset is generated by driving the MCLR pin low. The MCLR pin is a Schmitt trigger input with an additional glitch filter. Reset pulses that are longer than the minimum pulse width will generate a Reset. Refer to Section 28.0 "Electrical Characteristics" for minimum pulse width specifications. The External Reset (MCLR) Pin (EXTR) bit in the Reset Control (RCON) register is set to indicate the MCLR Reset.

#### 6.5.1 EXTERNAL SUPERVISORY CIRCUIT

Many systems have external supervisory circuits that generate reset signals to reset multiple devices in the system. This external Reset signal can be directly connected to the MCLR pin to reset the device when the rest of system is Reset.

#### 6.5.2 INTERNAL SUPERVISORY CIRCUIT

When using the internal power supervisory circuit to reset the device, the external reset pin (MCLR) should be tied directly or resistively to VDD. In this case, the MCLR pin will not be used to generate a Reset. The external reset pin (MCLR) does not have an internal pull-up and must not be left unconnected.

#### 6.6 Software RESET Instruction (SWR)

Whenever the RESET instruction is executed, the device will assert SYSRST, placing the device in a special Reset state. This Reset state will not reinitialize the clock. The clock source in effect prior to the RESET instruction will remain. SYSRST is released at the next instruction cycle, and the reset vector fetch will commence.

The Software Reset (Instruction) Flag bit (SWR) in the Reset Control register (RCON<6>) is set to indicate the software Reset.

#### 6.7 Watchdog Time-out Reset (WDTO)

Whenever a Watchdog time-out occurs, the device will asynchronously assert SYSRST. The clock source will remain unchanged. A WDT time-out during Sleep or Idle mode will wake-up the processor, but will not reset the processor.

The Watchdog Timer Time-out Flag bit (WDTO) in the Reset Control register (RCON<4>) is set to indicate the Watchdog Reset. Refer to Section 25.4 "Watchdog Timer (WDT)" for more information on Watchdog Reset.

#### 6.8 Trap Conflict Reset

If a lower-priority hard trap occurs while a higher-priority trap is being processed, a hard trap conflict Reset occurs. The hard traps include exceptions of priority level 13 through level 15, inclusive. The address error (level 13) and oscillator error (level 14) traps fall into this category.

The Trap Reset Flag bit (TRAPR) in the Reset Control register (RCON<15>) is set to indicate the Trap Conflict Reset. Refer to Section 7.0 "Interrupt Controller" for more information on trap conflict Resets.

| U-0          | U-0                                                                                      | U-0                                                          | U-0   | U-0               | R/W-1           | R/W-0           | R/W-0 |  |  |  |  |

|--------------|------------------------------------------------------------------------------------------|--------------------------------------------------------------|-------|-------------------|-----------------|-----------------|-------|--|--|--|--|

| 0-0          | 0-0                                                                                      | 0-0                                                          | 0-0   | 0-0               | R/W-I           |                 | R/W-0 |  |  |  |  |

|              | —                                                                                        | _                                                            |       | _                 |                 | DMA1IP<2:0>     |       |  |  |  |  |

| bit 15       |                                                                                          |                                                              |       |                   |                 |                 | bit   |  |  |  |  |

| U-0          | R/W-1                                                                                    | R/W-0                                                        | R/W-0 | U-0               | R/W-1           | R/W-0           | R/W-0 |  |  |  |  |

| _            |                                                                                          | AD1IP<2:0>                                                   |       | _                 |                 | U1TXIP<2:0>     |       |  |  |  |  |

| bit 7        |                                                                                          |                                                              |       |                   | •               |                 | bit   |  |  |  |  |

| Legend:      |                                                                                          |                                                              |       |                   |                 |                 |       |  |  |  |  |

| R = Readab   | ole bit                                                                                  | W = Writable                                                 | bit   | U = Unimpler      | mented bit, rea | d as '0'        |       |  |  |  |  |

| -n = Value a | at POR                                                                                   | '1' = Bit is set                                             |       | '0' = Bit is cle  | ared            | x = Bit is unkr | iown  |  |  |  |  |

|              |                                                                                          |                                                              |       |                   |                 |                 |       |  |  |  |  |

| bit 15-11    | Unimpleme                                                                                | ented: Read as '                                             | 0'    |                   |                 |                 |       |  |  |  |  |

| bit 10-8     | 8 <b>DMA1IP&lt;2:0&gt;:</b> DMA Channel 1 Data Transfer Complete Interrupt Priority bits |                                                              |       |                   |                 |                 |       |  |  |  |  |

|              | 111 = Interr                                                                             | 111 = Interrupt is priority 7 (highest priority interrupt)   |       |                   |                 |                 |       |  |  |  |  |

|              | •                                                                                        |                                                              |       |                   |                 |                 |       |  |  |  |  |

|              | •                                                                                        |                                                              |       |                   |                 |                 |       |  |  |  |  |

|              | 001 = Interr                                                                             | upt is priority 1                                            |       |                   |                 |                 |       |  |  |  |  |

|              |                                                                                          | upt source is dis                                            | abled |                   |                 |                 |       |  |  |  |  |

| bit 7        | Unimpleme                                                                                | nted: Read as '                                              | 0'    |                   |                 |                 |       |  |  |  |  |

| bit 6-4      | AD1IP<2:0>                                                                               | AD1IP<2:0>: ADC1 Conversion Complete Interrupt Priority bits |       |                   |                 |                 |       |  |  |  |  |

|              |                                                                                          | upt is priority 7 (                                          | •     | •                 | 2               |                 |       |  |  |  |  |

|              | •                                                                                        |                                                              |       |                   |                 |                 |       |  |  |  |  |

|              | •                                                                                        |                                                              |       |                   |                 |                 |       |  |  |  |  |

|              | •<br>001 = Interr                                                                        | upt is priority 1                                            |       |                   |                 |                 |       |  |  |  |  |

|              |                                                                                          | upt source is dis                                            | abled |                   |                 |                 |       |  |  |  |  |

| bit 3        |                                                                                          | nted: Read as '                                              |       |                   |                 |                 |       |  |  |  |  |

| bit 2-0      | -                                                                                        | )>: UART1 Trans                                              |       | upt Priority bits |                 |                 |       |  |  |  |  |

|              |                                                                                          | upt is priority 7 (                                          |       |                   |                 |                 |       |  |  |  |  |

|              | •                                                                                        |                                                              | 5     | ,                 |                 |                 |       |  |  |  |  |

|              | •                                                                                        |                                                              |       |                   |                 |                 |       |  |  |  |  |

|              | •                                                                                        |                                                              |       |                   |                 |                 |       |  |  |  |  |

|              | 001 = Interr                                                                             | upt is priority 1                                            |       |                   |                 |                 |       |  |  |  |  |

#### PRIORITY CONTROL REGISTER

001 = Interrupt is priority 1 000 = Interrupt source is disabled

# REGISTER 11-23: RPOR8: PERIPHERAL PIN SELECT OUTPUT REGISTERS 8<sup>(1)</sup>

| U-0                                 | U-0                                                                     | U-0              | R/W-0 | R/W-0         | R/W-0           | R/W-0    | R/W-0 |

|-------------------------------------|-------------------------------------------------------------------------|------------------|-------|---------------|-----------------|----------|-------|

| <b>—</b> — <b>— — — — — — — — —</b> |                                                                         |                  |       |               |                 |          |       |

| bit 15                              |                                                                         |                  |       |               |                 |          | bit 8 |

|                                     |                                                                         |                  |       |               |                 |          |       |

| U-0                                 | U-0                                                                     | U-0              | R/W-0 | R/W-0         | R/W-0           | R/W-0    | R/W-0 |

| —                                   | _                                                                       | —                |       |               | RP16R<4:0       | >        |       |

| bit 7                               |                                                                         |                  |       |               |                 |          | bit C |

| Legend:                             |                                                                         |                  |       |               |                 |          |       |

| R = Readable                        | h:+                                                                     | W = Writable t   | .:+   |               | monted hit rea  | d aa '0' |       |

| R = Readable                        | DIL                                                                     | vv = vvritable t | DIC   | 0 = 0 nimpler | nented bit, rea | d as 0   |       |

| -n = Value at P                     | = Value at POR (1' = Bit is set (0' = Bit is cleared x = Bit is unknown |                  |       |               |                 | nown     |       |

bit 15-13 Unimplemented: Read as '0'

bit 12-8 **RP17R<4:0>:** Peripheral Output Function is Assigned to RP17 Output Pin bits (see Table 11-2 for peripheral function numbers)

bit 7-5 Unimplemented: Read as '0'

bit 4-0 **RP16R<4:0>:** Peripheral Output Function is Assigned to RP16 Output Pin bits (see Table 11-2 for peripheral function numbers)

Note 1: This register is implemented in 44-pin devices only.

## REGISTER 11-24: RPOR9: PERIPHERAL PIN SELECT OUTPUT REGISTERS 9<sup>(1)</sup>

| U-0          | U-0        | U-0                            | R/W-0          | R/W-0            | R/W-0           | R/W-0             | R/W-0        |

|--------------|------------|--------------------------------|----------------|------------------|-----------------|-------------------|--------------|

| _            | _          | _                              |                |                  | RP19R<4:0>      | >                 |              |

| bit 15       |            |                                | •              |                  |                 |                   | bit 8        |

|              |            |                                |                |                  |                 |                   |              |

| U-0          | U-0        | U-0                            | R/W-0          | R/W-0            | R/W-0           | R/W-0             | R/W-0        |

|              | —          | —                              |                |                  | RP18R<4:0>      | >                 |              |

| bit 7        |            |                                |                |                  |                 |                   | bit 0        |

|              |            |                                |                |                  |                 |                   |              |

| Legend:      |            |                                |                |                  |                 |                   |              |

| R = Readab   | le bit     | W = Writable                   | bit            | U = Unimpler     | nented bit, rea | d as '0'          |              |

| -n = Value a | It POR     | '1' = Bit is set               | t              | '0' = Bit is cle | ared            | x = Bit is unkr   | nown         |

|              |            |                                |                |                  |                 |                   |              |

| bit 15-13    | Unimplemen | ted: Read as                   | '0'            |                  |                 |                   |              |

| bit 12-8     |            | Peripheral Or<br>ction numbers |                | is Assigned to   | RP19 Output     | Pin bits (see Tal | ble 11-2 for |

| bit 7-5      | Unimplemen | ted: Read as                   | ʻ0 <b>'</b>    |                  |                 |                   |              |

| bit 4-0      | RP18R<4:0> | Peripheral O                   | utput Function | is Assigned to   | RP18 Output     | Pin bits (see Tal | ble 11-2 for |

bit 4-0 **RP18R<4:0>:** Peripheral Output Function is Assigned to RP18 Output Pin bits (see Table 11-2 for peripheral function numbers)

Note 1: This register is implemented in 44-pin devices only.

# 15.3 Output Compare Control Registers

# **REGISTER 15-1:** OCxCON: OUTPUT COMPAREX CONTROL REGISTER (x = 1, 2, 3 OR 4)

| U-0                                                   | U-0                                                                                                                                        | R/W-0                                                                                                                                                                                                                                             | U-0                                                                                                                                        | U-0                                                                                                                               | U-0                   | U-0             | U-0   |  |

|-------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|-----------------------|-----------------|-------|--|

|                                                       | —                                                                                                                                          | OCSIDL                                                                                                                                                                                                                                            | _                                                                                                                                          | —                                                                                                                                 |                       | —               | —     |  |

| bit 15                                                |                                                                                                                                            |                                                                                                                                                                                                                                                   |                                                                                                                                            |                                                                                                                                   |                       |                 | bit 8 |  |

|                                                       |                                                                                                                                            |                                                                                                                                                                                                                                                   |                                                                                                                                            | <b>-</b>                                                                                                                          |                       |                 |       |  |

| U-0                                                   | U-0                                                                                                                                        | U-0                                                                                                                                                                                                                                               | R-0 HC<br>OCFLT                                                                                                                            | R/W-0         R/W-0         R/W-0         R/V           OCTSEL         OCM<2:0>         OCM<2:0>         OCM<2:0>         OCM<2:0 |                       |                 |       |  |

|                                                       | OCM<2:0>                                                                                                                                   | 1:10                                                                                                                                                                                                                                              |                                                                                                                                            |                                                                                                                                   |                       |                 |       |  |

| bit 7                                                 |                                                                                                                                            |                                                                                                                                                                                                                                                   |                                                                                                                                            |                                                                                                                                   |                       |                 | bit 0 |  |

| Legend: HC = Cleared in Hardware HS = Set in Hardware |                                                                                                                                            |                                                                                                                                                                                                                                                   |                                                                                                                                            |                                                                                                                                   |                       |                 |       |  |

| R = Readab                                            | ole bit                                                                                                                                    | W = Writable bi                                                                                                                                                                                                                                   | t                                                                                                                                          | U = Unimple                                                                                                                       | mented bit, rea       | d as '0'        |       |  |

| -n = Value a                                          | it POR                                                                                                                                     | '1' = Bit is set                                                                                                                                                                                                                                  |                                                                                                                                            | '0' = Bit is cle                                                                                                                  | eared                 | x = Bit is unki | nown  |  |

| bit 13<br>bit 12-5<br>bit 4<br>bit 3                  | 1 = Output Co<br>0 = Output Co<br>Unimplement<br>OCFLT: PWN<br>1 = PWM Fac<br>0 = No PWM<br>(This bit is on<br>OCTSEL: Ou<br>1 = Timer3 is | p Output Compa<br>ompare x halts in<br>ompare x continent<br>ompare x continent<br>of Fault Condition<br>all condition has<br>Fault condition has<br>Fault condition has<br>up used when Output Compare T<br>the clock source<br>the clock source | n CPU Idle more<br>uses to operate<br>of Status bit<br>occurred (clean<br>nas occurred<br>CM<2:0> = 11<br>imer Select bit<br>e for Compare | de<br>in CPU Idle m<br>red in hardwa<br>1)<br>x                                                                                   |                       |                 |       |  |

| bit 2-0                                               | OCM<2:0>:0<br>111 = PWM n<br>110 = PWM n<br>101 = Initializ<br>100 = Initializ<br>011 = Compa<br>010 = Initializ<br>001 = Initializ        | Output Compare<br>mode on OCx, F<br>mode on OCx, F<br>ze OCx pin low, g<br>are event toggles<br>ze OCx pin high,<br>ze OCx pin low, g<br>t compare chann                                                                                          | Mode Select b<br>ault pin enable<br>ault pin disable<br>generate contir<br>generate single<br>s OCx pin<br>compare event                   | oits<br>ed<br>huous output p<br>output pulse<br>t forces OCx p                                                                    | on OCx pin<br>bin low | bin             |       |  |

## REGISTER 18-1: UXMODE: UARTX MODE REGISTER (CONTINUED)

| bit 4   | URXINV: Receive Polarity Inversion bit                                                                                                                                             |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | 1 = UxRX Idle state is '0'<br>0 = UxRX Idle state is '1'                                                                                                                           |

| bit 3   | BRGH: High Baud Rate Enable bit                                                                                                                                                    |

|         | <ul> <li>1 = BRG generates 4 clocks per bit period (4x baud clock, High-Speed mode)</li> <li>0 = BRG generates 16 clocks per bit period (16x baud clock, Standard mode)</li> </ul> |

| bit 2-1 | PDSEL<1:0>: Parity and Data Selection bits                                                                                                                                         |

|         | <ul> <li>11 = 9-bit data, no parity</li> <li>10 = 8-bit data, odd parity</li> <li>01 = 8-bit data, even parity</li> <li>00 = 8-bit data, no parity</li> </ul>                      |

| bit 0   | STSEL: Stop Bit Selection bit<br>1 = Two Stop bits<br>0 = One Stop bit                                                                                                             |

|         |                                                                                                                                                                                    |

- **Note 1:** Refer to **Section 17. "UART**" (DS70232) in the *"dsPIC33F/PIC24H Family Reference Manual"* for information on enabling the UART module for receive or transmit operation.

- 2: This feature is only available for the 16x BRG mode (BRGH = 0).

| U-0             | R/W-x                                                                                                                                 | U-0             | U-0               | U-0              | R/W-x          | R/W-x                | R/W-x |  |  |  |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------|-----------------|-------------------|------------------|----------------|----------------------|-------|--|--|--|

| _               | WAKFIL                                                                                                                                | _               | _                 | _                |                | SEG2PH<2:0>          |       |  |  |  |

| bit 15          |                                                                                                                                       |                 |                   |                  |                |                      | bit   |  |  |  |

| -               |                                                                                                                                       |                 | <b>-</b>          |                  |                |                      |       |  |  |  |

| R/W-x           | R/W-x                                                                                                                                 | R/W-x           | R/W-x             | R/W-x            | R/W-x          | R/W-x                | R/W-x |  |  |  |

| SEG2PHTS        | SAM                                                                                                                                   |                 | SEG1PH<2:0>       | >                |                | PRSEG<2:0>           |       |  |  |  |

| bit 7           |                                                                                                                                       |                 |                   |                  |                |                      | bit   |  |  |  |

| Legend:         |                                                                                                                                       |                 |                   |                  |                |                      |       |  |  |  |

| R = Readable    | bit                                                                                                                                   | W = Writable    | e bit             | U = Unimple      | mented bit, re | ad as '0'            |       |  |  |  |

| -n = Value at F | POR                                                                                                                                   | '1' = Bit is se | et                | '0' = Bit is cle | eared          | x = Bit is unkno     | own   |  |  |  |

|                 |                                                                                                                                       |                 |                   |                  |                |                      |       |  |  |  |

| bit 15          | •                                                                                                                                     | ted: Read as    |                   |                  |                |                      |       |  |  |  |

| bit 14          |                                                                                                                                       |                 | Line Filter for W | /ake-up bit      |                |                      |       |  |  |  |

|                 |                                                                                                                                       | bus line filter |                   |                  |                |                      |       |  |  |  |

| L:1 40 44       |                                                                                                                                       |                 | ot used for wake  | e-up             |                |                      |       |  |  |  |

| bit 13-11       |                                                                                                                                       | ted: Read as    |                   |                  |                |                      |       |  |  |  |

| bit 10-8        | SEG2PH<2:0>: Phase Segment 2 bits<br>111 = Length is 8 x TQ                                                                           |                 |                   |                  |                |                      |       |  |  |  |

|                 |                                                                                                                                       |                 |                   |                  |                |                      |       |  |  |  |

|                 | •                                                                                                                                     |                 |                   |                  |                |                      |       |  |  |  |

|                 |                                                                                                                                       |                 |                   |                  |                |                      |       |  |  |  |

|                 | •                                                                                                                                     |                 |                   |                  |                |                      |       |  |  |  |

| bit 7           | 000 = Length                                                                                                                          |                 | ent 2 Time Sele   | ot hit           |                |                      |       |  |  |  |

|                 | 1 = Freely pro                                                                                                                        |                 |                   |                  |                |                      |       |  |  |  |

|                 |                                                                                                                                       |                 | hits or Informati | ion Processin    | a Time (IPT)   | whichever is greate  | ≥r    |  |  |  |

| bit 6           |                                                                                                                                       | e of the CAN b  |                   |                  | ge (ii),       | inicite for to grout |       |  |  |  |

| bit o           |                                                                                                                                       |                 |                   | sample point     |                |                      |       |  |  |  |

|                 | <ul> <li>1 = Bus line is sampled three times at the sample point</li> <li>0 = Bus line is sampled once at the sample point</li> </ul> |                 |                   |                  |                |                      |       |  |  |  |

| bit 5-3         |                                                                                                                                       | -               | -                 |                  |                |                      |       |  |  |  |

|                 | SEG1PH<2:0>: Phase Segment 1 bits<br>111 = Length is 8 x TQ                                                                           |                 |                   |                  |                |                      |       |  |  |  |

|                 | •                                                                                                                                     |                 |                   |                  |                |                      |       |  |  |  |

|                 | •                                                                                                                                     |                 |                   |                  |                |                      |       |  |  |  |

|                 | •                                                                                                                                     |                 |                   |                  |                |                      |       |  |  |  |

|                 | 000 = Length                                                                                                                          | is 1 x Tq       |                   |                  |                |                      |       |  |  |  |

| bit 2-0         | •                                                                                                                                     |                 | Time Segmen       | t bits           |                |                      |       |  |  |  |

|                 | 111 = Length                                                                                                                          |                 | 0                 |                  |                |                      |       |  |  |  |

|                 | •                                                                                                                                     |                 |                   |                  |                |                      |       |  |  |  |

|                 | •                                                                                                                                     |                 |                   |                  |                |                      |       |  |  |  |

|                 | •                                                                                                                                     |                 |                   |                  |                |                      |       |  |  |  |

|                 | 000 = Length                                                                                                                          | is 1 x Tq       |                   |                  |                |                      |       |  |  |  |

|                 | 5                                                                                                                                     |                 |                   |                  |                |                      |       |  |  |  |

# 20.0 10-BIT/12-BIT ANALOG-TO-DIGITAL CONVERTER (ADC1)

- Note 1: This data sheet summarizes the features PIC24HJ32GP302/304, of the PIC24HJ64GPX02/X04 and PIC24HJ128GPX02/X04 of families devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 16. "Analog-to-Digital Converter (ADC)" (DS70183) of the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com). 2: Some registers and associated bits

- described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The PIC24HJ32GP302/304, PIC24HJ64GPX02/X04 and PIC24HJ128GPX02/X04 devices have up to 13 ADC input channels.

The AD12B bit (AD1CON1<10>) allows each of the ADC modules to be configured by the user as either a 10-bit, 4-sample/hold ADC (default configuration) or a 12-bit, 1-sample/hold ADC.

Note: The ADC module needs to be disabled before modifying the AD12B bit.

# 20.1 Key Features

The 10-bit ADC configuration has the following key features:

- Successive Approximation (SAR) conversion

- Conversion speeds of up to 1.1 Msps

- Up to 13 analog input pins

- External voltage reference input pins

- Simultaneous sampling of up to four analog input pins

- Automatic Channel Scan mode

- Selectable conversion trigger source

- Selectable Buffer Fill modes

- · Operation during CPU Sleep and Idle modes

The 12-bit ADC configuration supports all the above features, except:

- In the 12-bit configuration, conversion speeds of up to 500 ksps are supported

- There is only one sample/hold amplifier in the 12-bit configuration, so simultaneous sampling of multiple channels is not supported.

Depending on the particular device pinout, the ADC can have up to 13 analog input pins, designated AN0 through AN12. In addition, there are two analog input pins for external voltage reference connections. These voltage reference inputs can be shared with other analog input pins. The actual number of analog input pins and external voltage reference input configuration depends on the specific device.

Block diagrams of the ADC module are shown in Figure 20-1 and Figure 20-2.

## 20.2 ADC Initialization

The following configuration steps should be performed.

- 1. Configure the ADC module:

- a) Select port pins as analog inputs (AD1PCFGH<15:0> or AD1PCFGL<15:0>)

- b) Select voltage reference source to match expected range on analog inputs (AD1CON2<15:13>)

- c) Select the analog conversion clock to match desired data rate with processor clock (AD1CON3<7:0>)

- d) Determine how many S/H channels are used (AD1CON2<9:8> and AD1PCFGH<15:0> or AD1PCFGL<15:0>)

- e) Select the appropriate sample/conversion sequence (AD1CON1<7:5> and AD1CON3<12:8>)

- f) Select how conversion results are presented in the buffer (AD1CON1<9:8>)

- g) Turn on ADC module (AD1CON1<15>)

- 2. Configure ADC interrupt (if required):

- a) Clear the AD1IF bit

- b) Select ADC interrupt priority

# 20.3 ADC and DMA

If more than one conversion result needs to be buffered before triggering an interrupt, DMA data transfers can be used. ADC1 can trigger a DMA data transfer. If ADC1 is selected as the DMA IRQ source, a DMA transfer occurs when the AD1IF bit gets set as a result of an ADC1 sample conversion sequence.

The SMPI<3:0> bits (AD1CON2<5:2>) are used to select how often the DMA RAM buffer pointer is incremented.

The ADDMABM bit (AD1CON1<12>) determines how the conversion results are filled in the DMA RAM buffer area being used for ADC. If this bit is set, DMA buffers are written in the order of conversion. The module provides an address to the DMA channel that is the same as the address used for the non-DMA stand-alone buffer. If the ADDMABM bit is cleared, then DMA buffers are written in Scatter/Gather mode. The module provides a scatter/gather address to the DMA channel, based on the index of the analog input and the size of the DMA buffer.

| R/W-0              | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | R/W-0                                                                                                                                                                                                                             | R/W-0                                                         | R/W-0                                                  | R/W-0                          | R/W-0             | R/W-0         |

|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|--------------------------------------------------------|--------------------------------|-------------------|---------------|

| ALRMEN             | CHIME                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                   | AMA                                                           | SK<3:0>                                                |                                | ALRMP             | TR<1:0>       |

| bit 15             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                   |                                                               |                                                        |                                |                   | bit 8         |

| R/W-0              | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | R/W-0                                                                                                                                                                                                                             | R/W-0                                                         | R/W-0                                                  | R/W-0                          | R/W-0             | R/W-0         |

|                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                   | ARP                                                           | T<7:0>                                                 |                                |                   |               |

| bit 7              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                   |                                                               |                                                        |                                |                   | bit C         |

| Legend:            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                   |                                                               |                                                        |                                |                   |               |