Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

⊡XFI

| 2 0 1 1 1 0                |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 40 MIPs                                                                        |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                   |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                     |

| Number of I/O              | 21                                                                             |

| Program Memory Size        | 128KB (43K x 24)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 8K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                      |

| Data Converters            | A/D 10x10b/12b                                                                 |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 28-VQFN Exposed Pad                                                            |

| Supplier Device Package    | 28-QFN-S (6x6)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24hj128gp502-e-mm |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 3.0 CPU

- Note 1: This data sheet summarizes the features of the PIC24HJ32GP302/304, PIC24HJ64GPX02/X04 and PIC24HJ128GPX02/X04 families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 2. "CPU" (DS70204) of the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

# 3.1 Overview

The PIC24HJ32GP302/304, PIC24HJ64GPX02/X04 and PIC24HJ128GPX02/X04 CPU module has a 16-bit (data) modified Harvard architecture with an enhanced instruction set and addressing modes. The CPU has a 24-bit instruction word with a variable length opcode field. The Program Counter (PC) is 23 bits wide and addresses up to 4M x 24 bits of user program memory space. The actual amount of program memory implemented varies by device. A single-cycle instruction prefetch mechanism is used to help maintain throughput and provides predictable execution. All instructions execute in a single cycle, with the exception of instructions that change the program flow, the double word move (MOV.D) instruction and the table instructions. Overhead-free, single-cycle program loop constructs are supported using the REPEAT instruction, which is interruptible at any point.

The PIC24HJ32GP302/304, PIC24HJ64GPX02/X04 and PIC24HJ128GPX02/X04 devices have sixteen, 16-bit working registers in the programmer's model. Each of the working registers can serve as a data, address or address offset register. The 16th working register (W15) operates as a software Stack Pointer (SP) for interrupts and calls.

The PIC24HJ32GP302/304, PIC24HJ64GPX02/X04 and PIC24HJ128GPX02/X04 instruction set includes many addressing modes and is designed for optimum C compiler efficiency. For most instructions, the PIC24HJ32GP302/304, PIC24HJ64GPX02/X04 and PIC24HJ128GPX02/X04 is capable of executing a data (or program data) memory read, a working register (data) read, a data memory write and a program (instruction) memory read per instruction cycle. As a result, three parameter instructions can be supported, allowing A + B = C operations to be executed in a single cycle.

A block diagram of the CPU is shown in Figure 3-1, and the programmer's model for the PIC24HJ32GP302/ 304, PIC24HJ64GPX02/X04 and PIC24HJ128GPX02/ X04 is shown in Figure 3-2.

# 3.2 Data Addressing Overview

The data space can be linearly addressed as 32K words or 64 Kbytes using an Address Generation Unit (AGU). The upper 32 Kbytes of the data space memory map can optionally be mapped into program space at any 16K program word boundary defined by the 8-bit Program Space Visibility Page (PSVPAG) register. The program to data space mapping feature lets any instruction access program space as if it were data space.

The data space also includes 2 Kbytes of DMA RAM, which is primarily used for DMA data transfers, but may be used as general purpose RAM.

# 3.6 Arithmetic Logic Unit (ALU)

The PIC24HJ32GP302/304, PIC24HJ64GPX02/X04 and PIC24HJ128GPX02/X04 ALU is 16 bits wide and is capable of addition, subtraction, bit shifts and logic operations. Unless otherwise mentioned, arithmetic operations are two's complement in nature. Depending on the operation, the ALU can affect the values of the Carry (C), Zero (Z), Negative (N), Overflow (OV) and Digit Carry (DC) Status bits in the SR register. The C and DC Status bits operate as Borrow and Digit Borrow bits, respectively, for subtraction operations.

The ALU can perform 8-bit or 16-bit operations, depending on the mode of the instruction that is used. Data for the ALU operation can come from the W register array or data memory, depending on the addressing mode of the instruction. Likewise, output data from the ALU can be written to the W register array or a data memory location.

For information on the SR bits affected by each instruction, refer to the *"16-bit MCU and DSC Programmer's Reference Manual"* (DS70157).

The PIC24HJ32GP302/304, PIC24HJ64GPX02/X04 and PIC24HJ128GPX02/X04 CPU incorporates hardware support for both multiplication and division. This includes a dedicated hardware multiplier and support hardware for 16-bit-divisor division.

# 3.6.1 MULTIPLIER

Using the high-speed 17-bit x 17-bit multiplier, the ALU supports unsigned, signed or mixed-sign operation in several MCU multiplication modes:

- 16-bit x 16-bit signed

- 16-bit x 16-bit unsigned

- 16-bit signed x 5-bit (literal) unsigned

- 16-bit unsigned x 16-bit unsigned

- 16-bit unsigned x 5-bit (literal) unsigned

- 16-bit unsigned x 16-bit signed

- 8-bit unsigned x 8-bit unsigned

# 3.6.2 DIVIDER

The divide block supports 32-bit/16-bit and 16-bit/16-bit signed and unsigned integer divide operations with the following data sizes:

- · 32-bit signed/16-bit signed divide

- 32-bit unsigned/16-bit unsigned divide

- 16-bit signed/16-bit signed divide

- 16-bit unsigned/16-bit unsigned divide

The quotient for all divide instructions ends up in W0 and the remainder in W1. 16-bit signed and unsigned DIV instructions can specify any W register for both the 16-bit divisor (Wn) and any W register (aligned) pair (W(m + 1):Wm) for the 32-bit dividend. The divide algorithm takes one cycle per bit of divisor, so both 32-bit/16-bit and 16-bit/16-bit instructions take the same number of cycles to execute.

# 3.6.3 MULTI-BIT DATA SHIFTER

The multi-bit data shifter is capable of performing up to 16-bit arithmetic or logic right shifts, or up to 16-bit left shifts in a single cycle. The source can be either a working register or a memory location.

The shifter requires a signed binary value to determine both the magnitude (number of bits) and direction of the shift operation. A positive value shifts the operand right. A negative value shifts the operand left. A value of '0' does not modify the operand.

# 4.2 Data Address Space

The PIC24HJ32GP302/304, PIC24HJ64GPX02/X04 and PIC24HJ128GPX02/X04 CPU has a separate 16-bit wide data memory space. The data space is accessed using separate Address Generation Units (AGUs) for read and write operations. The data memory maps are shown in Figure 4-3 and Figure 4-4.

All Effective Addresses (EAs) in the data memory space are 16 bits wide and point to bytes within the data space. This arrangement gives a data space address range of 64 Kbytes or 32K words. The lower half of the data memory space (that is, when EA<15> = 0) is used for implemented memory addresses, while the upper half (EA<15> = 1) is reserved for the Program Space Visibility area (see Section 4.6.3 "Reading Data from Program Memory Using Program Space Visibility").

PIC24HJ32GP302/304, PIC24HJ64GPX02/X04 and PIC24HJ128GPX02/X04 devices implement up to 8 Kbytes of data memory. Should an EA point to a location outside of this area, an all-zero word or byte is returned.

# 4.2.1 DATA SPACE WIDTH

The data memory space is organized in byte addressable, 16-bit wide blocks. Data is aligned in data memory and registers as 16-bit words, but all data space EAs resolve to bytes. The Least Significant Bytes (LSBs) of each word have even addresses, while the Most Significant Bytes (MSBs) have odd addresses.

## 4.2.2 DATA MEMORY ORGANIZATION AND ALIGNMENT

To maintain backward compatibility with PIC<sup>®</sup> MCU devices and improve data space memory usage efficiency, the PIC24HJ32GP302/304, PIC24HJ64GPX02/X04 and PIC24HJ128GPX02/X04 instruction set supports both word and byte operations. As a consequence of byte accessibility, all effective address calculations are internally scaled to step through word-aligned memory. For example, the core recognizes that Post-Modified Register Indirect Addressing mode [Ws++] results in a value of Ws + 1 for byte operations and Ws + 2 for word operations.

A data byte read, reads the complete word that contains the byte, using the LSB of any EA to determine which byte to select. The selected byte is placed onto the LSB of the data path. That is, data memory and registers are organized as two parallel byte-wide entities with shared (word) address decode but separate write lines. Data byte writes only write to the corresponding side of the array or register that matches the byte address. All word accesses must be aligned to an even address. Misaligned word data fetches are not supported, so care must be taken when mixing byte and word operations, or translating from 8-bit MCU code. If a misaligned read or write is attempted, an address error trap is generated. If the error occurred on a read, the instruction underway is completed. If the error occurred on a write, the instruction is executed but the write does not occur. In either case, a trap is then executed, allowing the system and/or user application to examine the machine state prior to execution of the address Fault.

All byte loads into any W register are loaded into the Least Significant Byte. The Most Significant Byte is not modified.

A sign-extend instruction (SE) is provided to allow user applications to translate 8-bit signed data to 16-bit signed values. Alternatively, for 16-bit unsigned data, user applications can clear the MSB of any W register by executing a zero-extend (ZE) instruction on the appropriate address.

# 4.2.3 SFR SPACE

The first 2 Kbytes of the Near Data Space, from 0x0000 to 0x07FF, is primarily occupied by Special Function Registers (SFRs). These are used by the PIC24HJ32GP302/304, PIC24HJ64GPX02/X04 and PIC24HJ128GPX02/X04 core and peripheral modules for controlling the operation of the device.

SFRs are distributed among the modules that they control, and are generally grouped together by module. Much of the SFR space contains unused addresses; these are read as '0'.

**Note:** The actual set of peripheral features and interrupts varies by the device. Refer to the corresponding device tables and pinout diagrams for device-specific information.

# 4.2.4 NEAR DATA SPACE

The 8 Kbyte area between 0x0000 and 0x1FFF is referred to as the near data space. Locations in this space are directly addressable via a 13-bit absolute address field within all memory direct instructions. Additionally, the whole data space is addressable using MOV instructions, which support Memory Direct Addressing mode with a 16-bit address field, or by using Indirect Addressing mode using a working register as an address pointer.

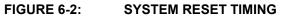

- **Note 1: POR:** A POR circuit holds the device in Reset when the power supply is turned on. The POR circuit is active until VDD crosses the VPOR threshold and the delay TPOR has elapsed.

- 2: BOR: The on-chip voltage regulator has a BOR circuit that keeps the device in Reset until VDD crosses the VBOR threshold and the delay TBOR has elapsed. The delay TBOR ensures the voltage regulator output becomes stable.

- **3: PWRT Timer:** The programmable power-up timer continues to hold the processor in Reset for a specific period of time (TPWRT) after a BOR. The delay TPWRT ensures that the system power supplies have stabilized at the appropriate level for full-speed operation. After the delay TPWRT has elapsed, the SYSRST becomes inactive, which in turn enables the selected oscillator to start generating clock cycles.

- 4: Oscillator Delay: The total delay for the clock to be ready for various clock source selections are given in Table 6-1. Refer to Section 9.0 "Oscillator Configuration" for more information.

- **5:** When the oscillator clock is ready, the processor begins execution from location 0x000000. The user application programs a GOTO instruction at the reset address, which redirects program execution to the appropriate start-up routine.

- 6: The Fail-Safe Clock Monitor (FSCM), if enabled, begins to monitor the system clock when the system clock is ready and the delay TFSCM elapsed.

# **REGISTER 8-3:** DMAXSTA: DMA CHANNEL x RAM START ADDRESS REGISTER A<sup>(1)</sup>

| R/W-0                             | R/W-0                                                         | R/W-0 | R/W-0                              | R/W-0  | R/W-0 | R/W-0 | R/W-0 |

|-----------------------------------|---------------------------------------------------------------|-------|------------------------------------|--------|-------|-------|-------|

|                                   |                                                               |       | STA                                | <15:8> |       |       |       |

| bit 15                            |                                                               |       |                                    |        |       |       | bit 8 |

|                                   |                                                               |       |                                    |        |       |       |       |

| R/W-0                             | R/W-0                                                         | R/W-0 | R/W-0                              | R/W-0  | R/W-0 | R/W-0 | R/W-0 |

|                                   |                                                               |       | STA                                | <7:0>  |       |       |       |

| bit 7                             |                                                               |       |                                    |        |       | bit 0 |       |

| r                                 |                                                               |       |                                    |        |       |       |       |

| Legend:                           |                                                               |       |                                    |        |       |       |       |

| R = Readable bit W = Writable bit |                                                               | bit   | U = Unimplemented bit, read as '0' |        |       |       |       |

| -n = Value at P                   | n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bi |       | x = Bit is unkr                    | nown   |       |       |       |

|                                   | R = Readable bit W = Writable bit                             |       |                                    |        |       |       | nown  |

bit 15-0 STA<15:0>: Primary DMA RAM Start Address bits (source or destination)

**Note 1:** A read of this address register returns the current contents of the DMA RAM Address register, not the contents written to STA<15:0>. If the channel is enabled (i.e., active), writes to this register may result in unpredictable behavior of the DMA channel and should be avoided.

# REGISTER 8-4: DMAxSTB: DMA CHANNEL x RAM START ADDRESS REGISTER B<sup>(1)</sup>

| R/W-0                              | R/W-0 | R/W-0 | R/W-0                                  | R/W-0   | R/W-0 | R/W-0 | R/W-0 |

|------------------------------------|-------|-------|----------------------------------------|---------|-------|-------|-------|

|                                    |       |       | STE                                    | 8<15:8> |       |       |       |

| bit 15                             |       |       |                                        |         |       |       | bit 8 |

|                                    |       |       |                                        |         |       |       |       |

| R/W-0                              | R/W-0 | R/W-0 | R/W-0                                  | R/W-0   | R/W-0 | R/W-0 | R/W-0 |

|                                    |       |       | ST                                     | 3<7:0>  |       |       |       |

| bit 7                              |       |       |                                        |         |       | bit 0 |       |

|                                    |       |       |                                        |         |       |       |       |

| Legend:                            |       |       |                                        |         |       |       |       |

| R = Readable bit W = Writable bit  |       | bit   | U = Unimplemented bit, read as '0'     |         |       |       |       |

| -n = Value at POR '1' = Bit is set |       |       | '0' = Bit is cleared x = Bit is unknow |         |       | nown  |       |

bit 15-0 STB<15:0>: Secondary DMA RAM Start Address bits (source or destination)

**Note 1:** A read of this address register returns the current contents of the DMA RAM Address register, not the contents written to STB<15:0>. If the channel is enabled (i.e., active), writes to this register may result in unpredictable behavior of the DMA channel and should be avoided.

# REGISTER 11-4: RPINR4: PERIPHERAL PIN SELECT INPUT REGISTER 4

| U-0          | U-0                                                        | U-0                                                                                   | R/W-1          | R/W-1            | R/W-1           | R/W-1          | R/W-1 |  |

|--------------|------------------------------------------------------------|---------------------------------------------------------------------------------------|----------------|------------------|-----------------|----------------|-------|--|

|              | —                                                          | — T5CKR<4:0>                                                                          |                |                  |                 |                |       |  |

| bit 15       |                                                            |                                                                                       | 1              |                  |                 |                | bit 8 |  |

| U-0          | U-0                                                        | U-0                                                                                   | R/W-1          | R/W-1            | R/W-1           | R/W-1          | R/W-1 |  |

| _            |                                                            |                                                                                       |                |                  | T4CKR<4:0       | >              |       |  |

| bit 7        | ·                                                          |                                                                                       |                |                  |                 |                | bit 0 |  |

|              |                                                            |                                                                                       |                |                  |                 |                |       |  |

| Legend:      |                                                            |                                                                                       |                |                  |                 |                |       |  |

| R = Readab   | le bit                                                     | W = Writable                                                                          | bit            | U = Unimpler     | mented bit, rea | ad as '0'      |       |  |

| -n = Value a | t POR                                                      | '1' = Bit is set                                                                      |                | '0' = Bit is cle | ared            | x = Bit is unk | nown  |  |

|              | •<br>•<br>00001 = Inpu                                     | ut tied to RP25<br>ut tied to RP1<br>ut tied to RP0                                   |                |                  |                 |                |       |  |

| bit 7-5      | Unimplemer                                                 | nted: Read as '                                                                       | 0'             |                  |                 |                |       |  |

| bit 4-0      | 11111 = Inpu<br>11001 = Inpu<br>•<br>•<br>•<br>•<br>•<br>• | Assign Timer<br>ut tied to Vss<br>ut tied to RP25<br>ut tied to RP1<br>ut tied to RP0 | 4 External Clo | ock (T4CK) to t  | he correspond   | ing RPn pin    |       |  |

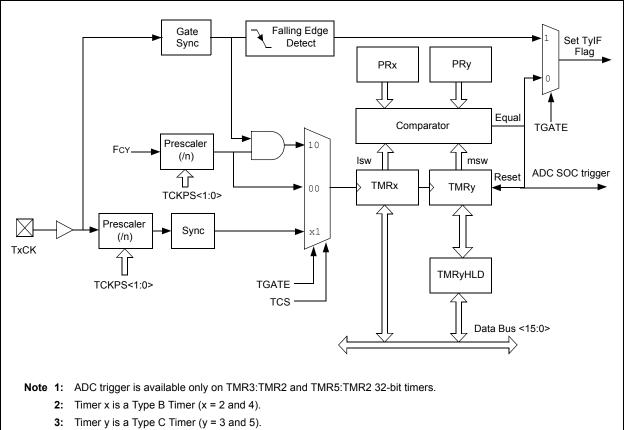

The Timer2/3 and Timer4/5 modules can operate in one of the following modes:

- Timer mode

- · Gated Timer mode

- Synchronous Counter mode

In Timer and Gated Timer modes, the input clock is derived from the internal instruction cycle clock (FcY). In Synchronous Counter mode, the input clock is derived from the external clock input at TxCK pin.

The timer modes are determined by the following bits:

- TCS (TxCON<1>): Timer Clock Source Control bit

- TGATE (TxCON<6>): Timer Gate Control bit

Timer control bit settings for different operating modes are given in the Table 13-1.

| TABLE 13-1:TIMER MODE SETTINGS |

|--------------------------------|

|--------------------------------|

| Mode                | TCS | TGATE |

|---------------------|-----|-------|

| Timer               | 0   | 0     |

| Gated timer         | 0   | 1     |

| Synchronous counter | 1   | Х     |

# 13.1 16-Bit Operation

To configure any of the timers for individual 16-bit operation:

- 1. Clear the T32 bit corresponding to that timer.

- 2. Select the timer prescaler ratio using the TCKPS<1:0> bits.

- 3. Set the Clock and Gating modes using the TCS and TGATE bits.

- 4. Load the timer period value into the PRx register.

- 5. If interrupts are required, set the interrupt enable bit, TxIE. Use the priority bits, TxIP<2:0>, to set the interrupt priority.

- 6. Set the TON bit.

| Note: | Only Timer2 and Timer3 can trigger a |

|-------|--------------------------------------|

|       | DMA data transfer.                   |

# 13.2 32-Bit Operation

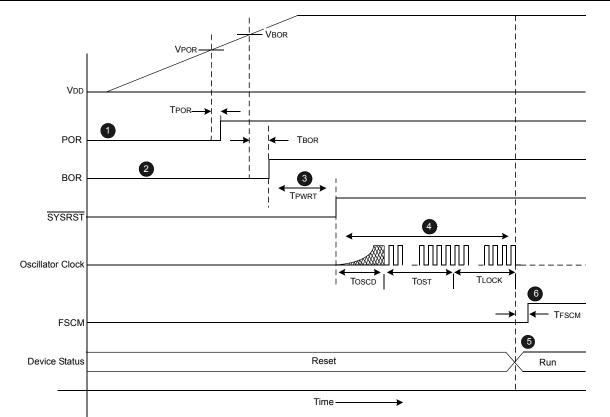

A 32-bit timer module can be formed by combining a Type B and a Type C 16-bit timer module. For 32-bit timer operation, the T32 control bit in the Type B Timer Control register (TxCON<3>) must be set. The Type C timer holds the most significant word (msw) and the Type B timer holds the least significant word (lsw) for 32-bit operation.

When configured for 32-bit operation, only the Type B Timer Control register (TxCON) bits are required for setup and control. Type C timer control register bits are ignored (except TSIDL bit).

For interrupt control, the combined 32-bit timer uses the interrupt enable, interrupt flag and interrupt priority control bits of the Type C timer. The interrupt control and status bits for the Type B timer are ignored during 32-bit timer operation.

The Type B and Type C timers that can be combined to form a 32-bit timer are listed in Table 13-2.

## TABLE 13-2: 32-BIT TIMER

| TYPE B Timer (Isw) | TYPE C Timer (msw) |

|--------------------|--------------------|

| Timer2             | Timer3             |

| Timer4             | Timer5             |

A block diagram representation of the 32-bit timer module is shown in Figure 13-3. The 32-timer module can operate in one of the following modes:

- Timer mode

- · Gated Timer mode

- · Synchronous Counter mode

To configure the features of Timer2/3 or Timer4/5 for 32-bit operation:

- 1. Set the T32 control bit.

- 2. Select the prescaler ratio for Timer2 or Timer4 using the TCKPS<1:0> bits.

- 3. Set the Clock and Gating modes using the corresponding TCS and TGATE bits.

- 4. Load the timer period value. PR3 or PR5 contains the most significant word of the value, while PR2 or PR4 contains the least significant word.

- If interrupts are required, set the interrupt enable bits, T3IE or T5IE. Use the priority bits, T3IP<2:0> or T5IP<2:0> to set the interrupt priority. While Timer2 or Timer4 controls the timer, the interrupt appears as a Timer3 or Timer5 interrupt.

- 6. Set the corresponding TON bit.

The timer value at any point is stored in the register pair, TMR3:TMR2 or TMR5:TMR4, which always contains the most significant word of the count, while TMR2 or TMR4 contains the least significant word.

# 13.3 Timer Resources

Many useful resources related to Timers are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

Note: In the event you are not able to access the product page using the link above, enter this URL in your browser: http://www.microchip.com/wwwproducts/ Devices.aspx?dDocName=en532315

# 13.3.1 KEY RESOURCES

- Section 11. "Timers" (DS70205)

- Code Samples

- Application Notes

- Software Libraries

- · Webinars

- All related dsPIC33F/PIC24H Family Reference Manuals Sections

- Development Tools

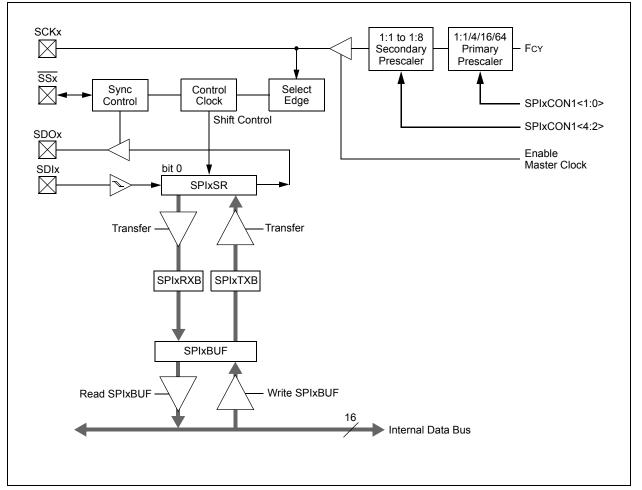

# 16.0 SERIAL PERIPHERAL INTERFACE (SPI)

- Note 1: This data sheet summarizes the features PIC24HJ32GP302/304, of the PIC24HJ64GPX02/X04 and PIC24HJ128GPX02/X04 families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 18. "Serial Peripheral Interface (SPI)" (DS70206) of the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Serial Peripheral Interface (SPI) module is a synchronous serial interface useful for communicating with other peripheral or microcontroller devices. These peripheral devices can be serial EEPROMs, shift registers, display drivers, analog-to-digital converters, etc. The SPI module is compatible with Motorola<sup>®</sup> SPI and SIOP.

Each SPI module consists of a 16-bit shift register, SPIxSR (where x = 1 or 2), used for shifting data in and out, and a buffer register, SPIxBUF. A control register, SPIxCON, configures the module. Additionally, a status register, SPIxSTAT, indicates status conditions.

The serial interface consists of 4 pins:

- · SDIx (serial data input)

- SDOx (serial data output)

- <u>SCKx</u> (shift clock input or output)

- SSx (active-low slave select)

In Master mode operation, SCK is a clock output. In Slave mode, it is a clock input.

#### FIGURE 16-1: SPI MODULE BLOCK DIAGRAM

# REGISTER 17-1: I2CxCON: I2Cx CONTROL REGISTER (CONTINUED)

| bit 5 | ACKDT: Acknowledge Data bit (when operating as I <sup>2</sup> C master, applicable during master receive)<br>Value that is transmitted when the software initiates an Acknowledge sequence.<br>1 = Send NACK during Acknowledge<br>0 = Send ACK during Acknowledge                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 4 | <b>ACKEN:</b> Acknowledge Sequence Enable bit (when operating as I <sup>2</sup> C master, applicable during master receive)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|       | <ul> <li>1 = Initiate Acknowledge sequence on SDAx and SCLx pins and transmit ACKDT data bit.</li> <li>Hardware clear at end of master Acknowledge sequence</li> <li>0 = Acknowledge sequence not in progress</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| bit 3 | <b>RCEN:</b> Receive Enable bit (when operating as I <sup>2</sup> C master)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|       | 1 = Enables Receive mode for $I^2C$ . Hardware clear at end of eighth bit of master receive data byte<br>0 = Receive sequence not in progress                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| bit 2 | <b>PEN:</b> Stop Condition Enable bit (when operating as I <sup>2</sup> C master)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|       | 1 = Initiate Stop condition on SDAx and SCLx pins. Hardware clear at end of master Stop sequence<br>0 = Stop condition not in progress                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| bit 1 | <b>RSEN:</b> Repeated Start Condition Enable bit (when operating as I <sup>2</sup> C master)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|       | <ul> <li>1 = Initiate Repeated Start condition on SDAx and SCLx pins. Hardware clear at end of<br/>master Repeated Start sequence</li> <li>2 Descent of the security of th</li></ul> |

| 1.1.0 | 0 = Repeated Start condition not in progress                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| bit 0 | <b>SEN:</b> Start Condition Enable bit (when operating as I <sup>2</sup> C master)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|       | <ul> <li>1 = Initiate Start condition on SDAx and SCLx pins. Hardware clear at end of master Start sequence</li> <li>0 = Start condition not in progress</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

# PIC24HJ32GP302/304, PIC24HJ64GPX02/X04 AND PIC24HJ128GPX02/X04

|                               |                                                                                                       | R/W-0                                                                                                               | U-0                                | U-0               | U-0               | U-0             | U-0   |  |  |

|-------------------------------|-------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|------------------------------------|-------------------|-------------------|-----------------|-------|--|--|

|                               | DMABS<2:0>                                                                                            |                                                                                                                     | —                                  | —                 | _                 | —               | —     |  |  |

| bit 15                        |                                                                                                       |                                                                                                                     |                                    |                   |                   |                 | bit 8 |  |  |

| U-0                           | U-0                                                                                                   | U-0                                                                                                                 | R/W-0                              | R/W-0             | R/W-0             | R/W-0           | R/W-0 |  |  |

| _                             | _                                                                                                     | _                                                                                                                   |                                    |                   | FSA<4:0>          |                 |       |  |  |

| bit 7                         |                                                                                                       |                                                                                                                     |                                    |                   |                   |                 | bit ( |  |  |

| Levende                       |                                                                                                       | C = M/rite able                                                                                                     |                                    | 'O' oon ho writte | ve to close the l | .:4             |       |  |  |

| <b>Legend:</b><br>R = Readabl | a hit                                                                                                 | W = Writable                                                                                                        | •                                  | '0' can be writte |                   |                 |       |  |  |

| -n = Value at                 |                                                                                                       | '1' = Bit is set                                                                                                    |                                    | 0 = Onimplen      | nented bit, read  | x = Bit is unkr |       |  |  |

|                               | FUR                                                                                                   |                                                                                                                     |                                    |                   | aleu              |                 | IOWIT |  |  |

| bit 12-5                      | 101 = 24 buffe<br>100 = 16 buffe<br>011 = 12 buffe<br>010 = 8 buffe<br>001 = 6 buffe<br>000 = 4 buffe | ers in DMA RA<br>ers in DMA RA<br>ers in DMA RA<br>ers in DMA RA<br>rs in DMA RAN<br>rs in DMA RAN<br>rs in DMA RAN | AM<br>AM<br>AM<br>A<br>A<br>A<br>A |                   |                   |                 |       |  |  |

| bit 4-0                       | Unimplemented: Read as '0'<br>FSA<4:0>: FIFO Area Starts with Buffer bits                             |                                                                                                                     |                                    |                   |                   |                 |       |  |  |

|                               | 11111 = Read<br>11110 = Read<br>•                                                                     | d buffer RB31                                                                                                       |                                    | 5113              |                   |                 |       |  |  |

| R/W-0                                         | R-0                                                                                                                                                     | R-0                           | R-0                   | R/W-0            | R/W-0             | R/W-0           | R/W-0         |  |  |  |  |

|-----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|-----------------------|------------------|-------------------|-----------------|---------------|--|--|--|--|

| TXENn                                         | TXABTn                                                                                                                                                  | TXLARBn                       | TXERRn                | TXREQn           | RTRENn            | TXnPRI<1:0>     |               |  |  |  |  |

| bit 15                                        |                                                                                                                                                         |                               |                       |                  |                   | •               | bit 8         |  |  |  |  |

|                                               |                                                                                                                                                         |                               |                       |                  |                   |                 |               |  |  |  |  |

| R/W-0                                         | R-0                                                                                                                                                     | R-0                           | R-0                   | R/W-0            | R/W-0             | R/W-0           | R/W-0         |  |  |  |  |

| TXENm                                         | TXABTm <sup>(1)</sup>                                                                                                                                   | TXLARBm <sup>(1)</sup>        | TXERRm <sup>(1)</sup> | TXREQm           | RTRENm            | TXmPF           | RI<1:0>       |  |  |  |  |

| bit 7                                         |                                                                                                                                                         |                               |                       |                  |                   |                 | bit (         |  |  |  |  |

| Legend:                                       |                                                                                                                                                         | C = Writeable                 | bit but only '(       | )' can be writte | en to clear the b | it              |               |  |  |  |  |

| R = Readab                                    | le bit                                                                                                                                                  | W = Writable                  | -                     |                  | nented bit, read  |                 |               |  |  |  |  |

| -n = Value a                                  |                                                                                                                                                         | '1' = Bit is set              |                       | '0' = Bit is cle |                   | x = Bit is unkr | nown          |  |  |  |  |

|                                               |                                                                                                                                                         |                               |                       |                  |                   |                 |               |  |  |  |  |

| bit 15-8                                      | See Definitior                                                                                                                                          | n for Bits 7-0, C             | Controls Buffer       | n                |                   |                 |               |  |  |  |  |

| bit 7                                         |                                                                                                                                                         | RX Buffer Sele                |                       |                  |                   |                 |               |  |  |  |  |

|                                               | 1 = Buffer TR                                                                                                                                           | Bn is a transm                | it buffer             |                  |                   |                 |               |  |  |  |  |

|                                               | 0 = Buffer TR                                                                                                                                           | Bn is a receive               | e buffer              |                  |                   |                 |               |  |  |  |  |

| bit 6                                         | TXABTm: Message Aborted bit <sup>(1)</sup>                                                                                                              |                               |                       |                  |                   |                 |               |  |  |  |  |

|                                               | 1 = Message was aborted                                                                                                                                 |                               |                       |                  |                   |                 |               |  |  |  |  |

|                                               | -                                                                                                                                                       | -                             | nsmission succ        | -                |                   |                 |               |  |  |  |  |

| bit 5                                         | TXLARBm: Message Lost Arbitration bit <sup>(1)</sup>                                                                                                    |                               |                       |                  |                   |                 |               |  |  |  |  |

|                                               |                                                                                                                                                         |                               | while being se        |                  |                   |                 |               |  |  |  |  |

| 1.1.4                                         |                                                                                                                                                         |                               | bitration while       |                  |                   |                 |               |  |  |  |  |

| bit 4                                         | <b>TXERRm:</b> Error Detected During Transmission bit <sup>(1)</sup>                                                                                    |                               |                       |                  |                   |                 |               |  |  |  |  |

|                                               | <ul> <li>1 = A bus error occurred while the message was being sent</li> <li>0 = A bus error did not occur while the message was being sent</li> </ul>   |                               |                       |                  |                   |                 |               |  |  |  |  |

| bit 3                                         | <ul> <li>0 = A bus error did not occur while the message was being sent</li> <li>TXREQm: Message Send Request bit</li> </ul>                            |                               |                       |                  |                   |                 |               |  |  |  |  |

|                                               |                                                                                                                                                         | -                             | -                     | bit automatica   | ally clears when  | the message i   | s successfull |  |  |  |  |

|                                               | 0 = Clearing t                                                                                                                                          | he bit to '0' wh              | ile set request       | s a message a    | abort             |                 |               |  |  |  |  |

| bit 2 RTRENm: Auto-Remote Transmit Enable bit |                                                                                                                                                         |                               |                       |                  |                   |                 |               |  |  |  |  |

|                                               | <ul> <li>1 = When a remote transmit is received, TXREQ will be set</li> <li>0 = When a remote transmit is received, TXREQ will be unaffected</li> </ul> |                               |                       |                  |                   |                 |               |  |  |  |  |

| bit 1-0                                       | TXmPRI<1:0>: Message Transmission Priority bits                                                                                                         |                               |                       |                  |                   |                 |               |  |  |  |  |

|                                               | 11 = Highest                                                                                                                                            | 11 = Highest message priority |                       |                  |                   |                 |               |  |  |  |  |

|                                               | •                                                                                                                                                       | ermediate mes                 | • • •                 |                  |                   |                 |               |  |  |  |  |

|                                               | 01 = Low intermediate message priority                                                                                                                  |                               |                       |                  |                   |                 |               |  |  |  |  |

|                                               |                                                                                                                                                         | message priori                |                       |                  |                   |                 |               |  |  |  |  |

#### ~ .

The buffers, SID, EID, DLC, Data Field and Receive Status registers are located in DMA RAM. Note:

| R/W-0                             | R/W-0 | R/W-0            | R/W-0        | R/W-0             | R/W-0    | R/W-0           | R/W-0 |

|-----------------------------------|-------|------------------|--------------|-------------------|----------|-----------------|-------|

| ADDR15                            | CS1   |                  | 10110        | -                 | R<13:8>  | 1011 0          |       |

| bit 15                            |       |                  |              |                   |          |                 | bit 8 |

| R/W-0                             | R/W-0 | R/W-0            | R/W-0        | R/W-0             | R/W-0    | R/W-0           | R/W-0 |

|                                   |       |                  | ADD          | R<7:0>            |          |                 |       |

| bit 7                             |       |                  |              |                   |          |                 | bit ( |

| Legend:                           |       |                  |              |                   |          |                 |       |

| R = Readable bit W = Writable bit |       | bit              | U = Unimplen | nented bit, rea   | d as '0' |                 |       |

| -n = Value at POR '1' = Bit is    |       | '1' = Bit is set |              | '0' = Bit is clea | ared     | x = Bit is unkr | nown  |

| bit 15   | ADDR15: Parallel Port Destination Address bits       |

|----------|------------------------------------------------------|

| bit 14   | CS1: Chip Select 1 bit                               |

|          | 1 = Chip select 1 is active                          |

|          | 0 = Chip select 1 is inactive                        |

| bit 13-0 | ADDR13:ADDR0: Parallel Port Destination Address bits |

# REGISTER 24-4: PMAEN: PARALLEL PORT ENABLE REGISTER

| U-0    | R/W-0  | U-0 | U-0 | U-0 | R/W-0 | R/W-0                     | R/W-0 |

|--------|--------|-----|-----|-----|-------|---------------------------|-------|

| —      | PTEN14 | —   | —   | —   | F     | PTEN<10:8> <sup>(1)</sup> |       |

| bit 15 |        |     |     |     |       |                           | bit 8 |

| R/W-0 | R/W-0 | R/W-0 | R/W-0               | R/W-0 | R/W-0 | R/W-0 | R/W-0  |

|-------|-------|-------|---------------------|-------|-------|-------|--------|

|       |       | PTEN< | 7:2> <sup>(1)</sup> |       |       | PTEN  | l<1:0> |

| bit 7 |       |       |                     |       |       |       | bit 0  |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

|                   |                  |                        |                    |

| bit 15    | Unimplemented: Read as '0'                                                                                                                       |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 14    | PTEN14: PMCS1 Strobe Enable bit                                                                                                                  |

|           | <ul> <li>1 = PMA14 functions as either PMA&lt;14&gt; bit or PMCS1</li> <li>0 = PMA14 pin functions as port I/O</li> </ul>                        |

| bit 13-11 | Unimplemented: Read as '0'                                                                                                                       |

| bit 10-2  | PTEN<10:2>: PMP Address Port Enable bits <sup>(1)</sup>                                                                                          |

|           | <ul><li>1 = PMA&lt;10:2&gt; function as PMP address lines</li><li>0 = PMA&lt;10:2&gt; function as port I/O</li></ul>                             |

| bit 1-0   | PTEN<1:0>: PMALH/PMALL Strobe Enable bits                                                                                                        |

|           | <ul> <li>1 = PMA1 and PMA0 function as either PMA&lt;1:0&gt; or PMALH and PMALL</li> <li>0 = PMA1 and PMA0 pads functions as port I/O</li> </ul> |

Note 1: Devices with 28 pins do not have PMA<10:2>.

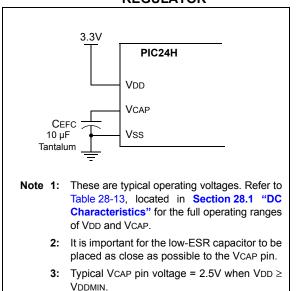

# 25.2 On-Chip Voltage Regulator

All of the PIC24HJ32GP302/304, PIC24HJ64GPX02/X04 and PIC24HJ128GPX02/X04 devices power their core digital logic at a nominal 2.5V. This can create a conflict for designs that are required to operate at a higher typical voltage, such as 3.3V. To simplify system design, all devices in the PIC24HJ32GP302/304, PIC24HJ64GPX02/X04 and PIC24HJ128GPX02/X04 family incorporate an on-chip regulator that allows the device to run its core logic from VDD.

The regulator provides power to the core from the other VDD pins. When the regulator is enabled, a low-ESR (less than 5 Ohms) capacitor (such as tantalum or ceramic) must be connected to the VCAP pin (Figure 25-1). This helps to maintain the stability of the regulator. The recommended value for the filter capacitor is provided in Table 28-13 located in Section 28.1 "DC Characteristics".

| Note: | It is important for the low-ESR capacitor to |

|-------|----------------------------------------------|

|       | be placed as close as possible to the VCAP   |

|       | pin.                                         |

On a POR, it takes approximately 20  $\mu$ s for the on-chip voltage regulator to generate an output voltage. During this time, designated as TSTARTUP, code execution is disabled. TSTARTUP is applied every time the device resumes operation after any power-down.

#### FIGURE 25-1: CONNECTIONS FOR THE ON-CHIP VOLTAGE REGULATOR<sup>(1,2,3)</sup>

# 25.3 Brown-out Reset (BOR)

The Brown-out Reset (BOR) module is based on an internal voltage reference circuit that monitors the regulated supply voltage VCAP. The main purpose of the BOR module is to generate a device Reset when a brown-out condition occurs. Brown-out conditions are generally caused by glitches on the AC mains (for example, missing portions of the AC cycle waveform due to bad power transmission lines, or voltage sags due to excessive current draw when a large inductive load is turned on).

A BOR generates a Reset pulse, which resets the device. The BOR selects the clock source, based on the device Configuration bit values (FNOSC<2:0> and POSCMD<1:0>).