Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 40 MIPs                                                                        |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                   |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                     |

| Number of I/O              | 21                                                                             |

| Program Memory Size        | 128KB (43K x 24)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 8K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                      |

| Data Converters            | A/D 10x10b/12b                                                                 |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                             |

| Mounting Type              | Through Hole                                                                   |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                        |

| Supplier Device Package    | 28-SPDIP                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24hj128gp502-e-sp |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 4.2 Data Address Space

The PIC24HJ32GP302/304, PIC24HJ64GPX02/X04 and PIC24HJ128GPX02/X04 CPU has a separate 16-bit wide data memory space. The data space is accessed using separate Address Generation Units (AGUs) for read and write operations. The data memory maps are shown in Figure 4-3 and Figure 4-4.

All Effective Addresses (EAs) in the data memory space are 16 bits wide and point to bytes within the data space. This arrangement gives a data space address range of 64 Kbytes or 32K words. The lower half of the data memory space (that is, when EA<15> = 0) is used for implemented memory addresses, while the upper half (EA<15> = 1) is reserved for the Program Space Visibility area (see Section 4.6.3 "Reading Data from Program Memory Using Program Space Visibility").

PIC24HJ32GP302/304, PIC24HJ64GPX02/X04 and PIC24HJ128GPX02/X04 devices implement up to 8 Kbytes of data memory. Should an EA point to a location outside of this area, an all-zero word or byte is returned.

#### 4.2.1 DATA SPACE WIDTH

The data memory space is organized in byte addressable, 16-bit wide blocks. Data is aligned in data memory and registers as 16-bit words, but all data space EAs resolve to bytes. The Least Significant Bytes (LSBs) of each word have even addresses, while the Most Significant Bytes (MSBs) have odd addresses.

#### 4.2.2 DATA MEMORY ORGANIZATION AND ALIGNMENT

To maintain backward compatibility with PIC<sup>®</sup> MCU devices and improve data space memory usage efficiency, the PIC24HJ32GP302/304, PIC24HJ64GPX02/X04 and PIC24HJ128GPX02/X04 instruction set supports both word and byte operations. As a consequence of byte accessibility, all effective address calculations are internally scaled to step through word-aligned memory. For example, the core recognizes that Post-Modified Register Indirect Addressing mode [Ws++] results in a value of Ws + 1 for byte operations and Ws + 2 for word operations.

A data byte read, reads the complete word that contains the byte, using the LSB of any EA to determine which byte to select. The selected byte is placed onto the LSB of the data path. That is, data memory and registers are organized as two parallel byte-wide entities with shared (word) address decode but separate write lines. Data byte writes only write to the corresponding side of the array or register that matches the byte address. All word accesses must be aligned to an even address. Misaligned word data fetches are not supported, so care must be taken when mixing byte and word operations, or translating from 8-bit MCU code. If a misaligned read or write is attempted, an address error trap is generated. If the error occurred on a read, the instruction underway is completed. If the error occurred on a write, the instruction is executed but the write does not occur. In either case, a trap is then executed, allowing the system and/or user application to examine the machine state prior to execution of the address Fault.

All byte loads into any W register are loaded into the Least Significant Byte. The Most Significant Byte is not modified.

A sign-extend instruction (SE) is provided to allow user applications to translate 8-bit signed data to 16-bit signed values. Alternatively, for 16-bit unsigned data, user applications can clear the MSB of any W register by executing a zero-extend (ZE) instruction on the appropriate address.

#### 4.2.3 SFR SPACE

The first 2 Kbytes of the Near Data Space, from 0x0000 to 0x07FF, is primarily occupied by Special Function Registers (SFRs). These are used by the PIC24HJ32GP302/304, PIC24HJ64GPX02/X04 and PIC24HJ128GPX02/X04 core and peripheral modules for controlling the operation of the device.

SFRs are distributed among the modules that they control, and are generally grouped together by module. Much of the SFR space contains unused addresses; these are read as '0'.

**Note:** The actual set of peripheral features and interrupts varies by the device. Refer to the corresponding device tables and pinout diagrams for device-specific information.

#### 4.2.4 NEAR DATA SPACE

The 8 Kbyte area between 0x0000 and 0x1FFF is referred to as the near data space. Locations in this space are directly addressable via a 13-bit absolute address field within all memory direct instructions. Additionally, the whole data space is addressable using MOV instructions, which support Memory Direct Addressing mode with a 16-bit address field, or by using Indirect Addressing mode using a working register as an address pointer.

#### **TABLE 4-5**: TIMER REGISTER MAP

| SFR<br>Name | SFR<br>Addr | Bit 15     | Bit 14                 | Bit 13  | Bit 12     | Bit 11      | Bit 10      | Bit 9        | Bit 8        | Bit 7          | Bit 6        | Bit 5 | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-------------|-------------|------------|------------------------|---------|------------|-------------|-------------|--------------|--------------|----------------|--------------|-------|--------|-------|-------|-------|-------|---------------|

| TMR1        | 0100        |            |                        |         |            |             |             |              | Timer1       | Register       |              |       |        |       |       |       |       | 0000          |

| PR1         | 0102        |            |                        |         |            |             |             |              | Period F     | Register 1     |              |       |        |       |       |       |       | FFFF          |

| T1CON       | 0104        | TON        | _                      | TSIDL   | —          | —           | _           | _            | _            | _              | TGATE        | TCKP  | S<1:0> | _     | TSYNC | TCS   | _     | 0000          |

| TMR2        | 0106        |            |                        |         |            |             |             |              | Timer2       | Register       |              |       |        |       |       |       |       | 0000          |

| TMR3HLD     | 0108        |            |                        |         |            |             | Tin         | ner3 Holding | Register (fo | r 32-bit timer | operations o | only) |        |       |       |       |       | XXXX          |

| TMR3        | 010A        |            |                        |         |            |             |             |              | Timer3       | Register       |              |       |        |       |       |       |       | 0000          |

| PR2         | 010C        |            |                        |         |            |             |             |              | Period F     | Register 2     |              |       |        |       |       |       |       | FFFF          |

| PR3         | 010E        |            |                        |         |            |             |             |              | Period F     | Register 3     |              |       |        |       |       |       |       | FFFF          |

| T2CON       | 0110        | TON        | _                      | TSIDL   | —          | —           | _           | _            | _            | _              | TGATE        | TCKP  | S<1:0> | T32   | _     | TCS   | _     | 0000          |

| T3CON       | 0112        | TON        | _                      | TSIDL   | _          | _           | _           | _            | _            | _              | TGATE        | TCKP  | S<1:0> | _     | _     | TCS   | _     | 0000          |

| TMR4        | 0114        |            |                        |         |            |             |             |              | Timer4       | Register       |              |       |        |       |       |       |       | 0000          |

| TMR5HLD     | 0116        |            |                        |         |            |             | Tin         | ner5 Holding | Register (fo | r 32-bit timer | operations o | only) |        |       |       |       |       | XXXX          |

| TMR5        | 0118        |            |                        |         |            |             |             |              | Timer5       | Register       |              |       |        |       |       |       |       | 0000          |

| PR4         | 011A        |            |                        |         |            |             |             |              | Period F     | Register 4     |              |       |        |       |       |       |       | FFFF          |

| PR5         | 011C        |            | Period Register 5 FFFF |         |            |             |             |              |              |                |              |       |        |       |       |       |       |               |

| T4CON       | 011E        | TON        | _                      | TSIDL   | _          |             | _           |              | _            | _              | TGATE        | TCKP  | S<1:0> | T32   |       | TCS   | _     | 0000          |

| T5CON       | 0120        | TON        | _                      | TSIDL   | _          | _           | _           | _            | _            | _              | TGATE        | TCKP  | S<1:0> | _     | _     | TCS   | _     | 0000          |

| Legend:     | v = 110     | known valu | e on Reset.            | = unimp | lemented r | ad as '0' F | Reset value | s are showr  | in hexader   | -<br>imal      | •            | •     |        | •     | •     |       | •     |               |

Legend: – = unimplemented, read as '0'. Reset values are shown in hexadecimal. x = unknown value on Reset,

#### **INPUT CAPTURE REGISTER MAP TABLE 4-6**:

| SFR<br>Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8      | Bit 7         | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1    | Bit 0 | All<br>Resets |

|-------------|-------------|--------|--------|--------|--------|--------|--------|-------|------------|---------------|-------|-------|-------|-------|-------|----------|-------|---------------|

| IC1BUF      | 0140        |        |        |        |        |        |        |       | Input 1 Ca | pture Registe | er    |       |       |       |       |          |       | XXXX          |

| IC1CON      | 0142        | _      | _      | ICSIDL | _      | _      | _      | _     | _          | ICTMR         | ICI<  | 1:0>  | ICOV  | ICBNE |       | ICM<2:0> |       | 0000          |

| IC2BUF      | 0144        |        |        |        |        |        |        |       | Input 2 Ca | pture Registe | er    |       |       |       |       |          |       | XXXX          |

| IC2CON      | 0146        | _      | _      | ICSIDL | _      | _      | _      | _     | _          | ICTMR         | ICI<  | 1:0>  | ICOV  | ICBNE |       | ICM<2:0> |       | 0000          |

| IC7BUF      | 0158        |        |        |        |        |        |        |       | Input 7 Ca | pture Registe | er    |       |       |       |       |          |       | XXXX          |

| IC7CON      | 015A        | _      | _      | ICSIDL | _      | _      | _      | _     | _          | ICTMR         | ICI<  | 1:0>  | ICOV  | ICBNE |       | ICM<2:0> |       | 0000          |

| IC8BUF      | 015C        |        |        |        |        |        |        |       | Input 8Ca  | pture Registe | er    |       |       |       |       |          |       | XXXX          |

| IC8CON      | 015E        | —      | _      | ICSIDL | -      | -      | _      | _     | -          | ICTMR         | ICI<  | 1:0>  | ICOV  | ICBNE |       | ICM<2:0> |       | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# TABLE 4-20:PERIPHERAL PIN SELECT OUTPUT REGISTER MAP FOR PIC24HJ128GP202/502, PIC24HJ64GP202/502 AND<br/>PIC24HJ32GP302

| File Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10    | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2      | Bit 1 | Bit 0 | All<br>Resets |

|-----------|------|--------|--------|--------|--------|--------|-----------|-------|-------|-------|-------|-------|-------|-------|------------|-------|-------|---------------|

| RPOR0     | 06C0 | -      | _      | —      |        |        | RP1R<4:0  | >     |       | —     | —     | —     |       |       | RP0R<4:0>  |       |       | 0000          |

| RPOR1     | 06C2 | _      | _      | _      |        |        | RP3R<4:0  | >     |       | _     | _     | _     |       |       | RP2R<4:0>  |       |       | 0000          |

| RPOR2     | 06C4 |        | —      | _      |        |        | RP5R<4:0> | >     |       | _     | _     | _     |       |       | RP4R<4:0>  |       |       | 0000          |

| RPOR3     | 06C6 |        | _      | _      |        |        | RP7R<4:0> | >     |       | _     | _     | _     |       |       | RP6R<4:0>  |       |       | 0000          |

| RPOR4     | 06C8 | -      | _      | _      |        |        | RP9R<4:0> | >     |       | —     | _     | _     |       |       | RP8R<4:0>  |       |       | 0000          |

| RPOR5     | 06CA | _      | _      | _      |        |        | RP11R<4:0 | >     |       | _     | _     | _     |       | I     | RP10R<4:0> |       |       | 0000          |

| RPOR6     | 06CC |        | —      | _      |        |        | RP13R<4:0 | >     |       | _     | —     | —     |       | I     | RP12R<4:0> |       |       | 0000          |

| RPOR7     | 06CE | -      | _      | _      |        |        | RP15R<4:0 | >     |       | _     | _     | _     |       | I     | RP14R<4:0> |       |       | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# TABLE 4-21:PERIPHERAL PIN SELECT OUTPUT REGISTER MAP FOR PIC24HJ128GP204/504, PIC24HJ64GP204/504 AND<br/>PIC24HJ32GP304

|           |      |        |        |        |        |        |           |          |       |       |       |       |       |       |            | -     |       |               |

|-----------|------|--------|--------|--------|--------|--------|-----------|----------|-------|-------|-------|-------|-------|-------|------------|-------|-------|---------------|

| File Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10    | Bit 9    | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2      | Bit 1 | Bit 0 | All<br>Resets |

| RPOR0     | 06C0 | _      | _      | _      |        |        | RP1R<4:0> | >        |       | _     | _     |       |       |       | RP0R<4:0>  |       |       | 0000          |

| RPOR1     | 06C2 | _      | _      | _      |        |        | RP3R<4:0> | >        |       | _     | _     | _     |       |       | RP2R<4:0>  |       |       | 0000          |

| RPOR2     | 06C4 | _      | _      | _      |        |        | RP5R<4:0> | >        |       | _     | _     | _     |       |       | RP4R<4:0>  |       |       | 0000          |

| RPOR3     | 06C6 | _      | _      | _      |        |        | RP7R<4:0> | <b>`</b> |       | _     | _     | _     |       |       | RP6R<4:0>  |       |       | 0000          |

| RPOR4     | 06C8 |        |        | _      |        |        | RP9R<4:0> | >        |       | _     |       | _     |       |       | RP8R<4:0>  |       |       | 0000          |

| RPOR5     | 06CA |        |        | _      |        |        | RP11R<4:0 | >        |       | _     |       | _     |       |       | RP10R<4:0> | >     |       | 0000          |

| RPOR6     | 06CC |        |        |        |        |        | RP13R<4:0 | >        |       | _     |       |       |       |       | RP12R<4:0> | >     |       | 0000          |

| RPOR7     | 06CE | _      | _      | _      |        |        | RP15R<4:0 | >        |       | _     | _     | _     |       |       | RP14R<4:0> | >     |       | 0000          |

| RPOR8     | 06D0 | _      | _      | _      |        |        | RP17R<4:0 | >        |       | _     | _     | _     |       |       | RP16R<4:0> | >     |       | 0000          |

| RPOR9     | 06D2 |        |        |        |        |        | RP19R<4:0 | >        |       | _     | _     |       |       |       | RP18R<4:0> | >     |       | 0000          |

| RPOR10    | 06D4 |        |        |        |        |        | RP21R<4:0 | >        |       | _     | _     |       |       |       | RP20R<4:0> | >     |       | 0000          |

| RPOR11    | 06D6 |        |        |        |        |        | RP23R<4:0 | >        |       | _     | _     |       |       |       | RP22R<4:0> | >     |       | 0000          |

| RPOR12    | 06D8 |        | _      | _      |        |        | RP25R<4:0 | >        |       | _     | _     |       |       |       | RP24R<4:0> | >     |       | 0000          |

Legend: x = unknown value on Reset, -- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

NVMCON: FLASH MEMORY CONTROL REGISTER

# 5.6 Flash Memory Control Registers

**REGISTER 5-1:**

| R/SO-0 <sup>(1)</sup> | R/W-0 <sup>(1)</sup>            | R/W-0 <sup>(1)</sup>            |                |                                                                          |                                       |                      |                      |

|-----------------------|---------------------------------|---------------------------------|----------------|--------------------------------------------------------------------------|---------------------------------------|----------------------|----------------------|

| WR                    | R/W-000                         | WRERR                           | U-0            | U-0                                                                      | U-0                                   | U-0                  | U-0                  |

|                       | WREN                            | WRERR                           | —              | _                                                                        | —                                     |                      |                      |

| bit 15                |                                 |                                 |                |                                                                          |                                       |                      | bit 8                |

| U-0                   | R/W-0 <sup>(1)</sup>            | U-0                             | U-0            | R/W-0 <sup>(1)</sup>                                                     | R/W-0 <sup>(1)</sup>                  | R/W-0 <sup>(1)</sup> | R/W-0 <sup>(1)</sup> |

| _                     | ERASE                           |                                 | _              |                                                                          | NVMOP                                 | <3:0> <sup>(2)</sup> |                      |

| bit 7                 | ·                               |                                 |                |                                                                          |                                       |                      | bit 0                |

| Legend:               |                                 | SO = Settal                     | ole only bit   |                                                                          |                                       |                      |                      |

| R = Readable          | bit                             | W = Writabl                     | e bit          | U = Unimpler                                                             | mented bit, read                      | as '0'               |                      |

| -n = Value at F       | POR                             | '1' = Bit is s                  | et             | '0' = Bit is cle                                                         | ared                                  | x = Bit is unkr      | nown                 |

| bit 15                | WR: Write Con                   | trol bit                        |                |                                                                          |                                       |                      |                      |

|                       | 1 = Initiates a                 | Flash memor                     | y program or   | erase operation                                                          | on. The operatio                      | on is self-timed     | and the bit is       |

|                       |                                 | hardware on                     |                |                                                                          |                                       |                      |                      |

|                       | 0 = Program of                  | •                               | tion is comple | ete and inactive                                                         | 9                                     |                      |                      |

| bit 14                | WREN: Write E                   |                                 |                |                                                                          |                                       |                      |                      |

|                       | 1 = Enable Fla                  |                                 |                |                                                                          |                                       |                      |                      |

| h:: 40                | 0 = Inhibit Flas                |                                 | -              | IS                                                                       |                                       |                      |                      |

| bit 13                | WRERR: Write                    | •                               | •              |                                                                          | · · · · · · · · · · · · · · · · · · · |                      |                      |

|                       |                                 | er program or<br>Illy on any se |                |                                                                          | termination has                       | occurred (bit i      | s set                |

|                       | 0 = The progra                  |                                 |                |                                                                          | /                                     |                      |                      |

| bit 12-7              | Unimplemente                    |                                 |                |                                                                          |                                       |                      |                      |

| bit 6                 | ERASE: Erase                    |                                 |                |                                                                          |                                       |                      |                      |

| 2.00                  |                                 | •                               |                | bv NVMOP </td <td>3:0&gt; on the next</td> <td>WR command</td> <td></td> | 3:0> on the next                      | WR command           |                      |

|                       |                                 |                                 |                |                                                                          | ><3:0> on the network                 |                      |                      |

| bit 5-4               | Unimplemente                    | d: Read as '                    | )'             |                                                                          |                                       |                      |                      |

| bit 3-0               | NVMOP<3:0>:                     | NVM Operati                     | on Select bits | <sub>S</sub> (2)                                                         |                                       |                      |                      |

|                       | If ERASE = 1:                   |                                 |                |                                                                          |                                       |                      |                      |

|                       | 1111 <b>= Memor</b>             | •                               | operation      |                                                                          |                                       |                      |                      |

|                       | 1110 = Reserv                   |                                 |                |                                                                          |                                       |                      |                      |

|                       | 1101 = Erase (                  | •                               |                |                                                                          |                                       |                      |                      |

|                       | 1100 = Erase S<br>1011 = Reserv |                                 | ent            |                                                                          |                                       |                      |                      |

|                       | 0011 = No ope                   |                                 |                |                                                                          |                                       |                      |                      |

|                       | 0010 = Memor                    |                                 | operation      |                                                                          |                                       |                      |                      |

|                       | 0001 = No ope                   |                                 |                |                                                                          |                                       |                      |                      |

|                       | 0000 <b>= Erase</b> a           | a single Confi                  | guration regis | ster byte                                                                |                                       |                      |                      |

|                       | If ERASE = 0:                   |                                 |                |                                                                          |                                       |                      |                      |

|                       | 1111 <b>= No ope</b>            |                                 |                |                                                                          |                                       |                      |                      |

|                       | 1110 = Reserv                   |                                 |                |                                                                          |                                       |                      |                      |

|                       | 1101 = No ope<br>1100 = No ope  |                                 |                |                                                                          |                                       |                      |                      |

|                       | 1011 = Reserv                   |                                 |                |                                                                          |                                       |                      |                      |

|                       | 0011 = Memor                    | y word progra                   | m operation    |                                                                          |                                       |                      |                      |

|                       | 0010 = No ope                   | ration                          |                |                                                                          |                                       |                      |                      |

|                       | 0001 = Memory                   |                                 |                |                                                                          |                                       |                      |                      |

|                       | 0000 <b>= Progra</b> r          | n a single Co                   | nfiguration re | gister byte                                                              |                                       |                      |                      |

| Note 1: The           | ese bits can only               | be reset on a                   | POR.           |                                                                          |                                       |                      |                      |

| 2: All                | other combination               | ns of NVMOF                     | <3:0> are un   | implemented                                                              |                                       |                      |                      |

2: All other combinations of NVMOP<3:0> are unimplemented.

## 6.0 RESETS

- **Note 1:** This data sheet summarizes the features PIC24HJ32GP302/304. of the PIC24HJ64GPX02/X04 and PIC24HJ128GPX02/X04 families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 8. "Reset" (DS70192) of the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

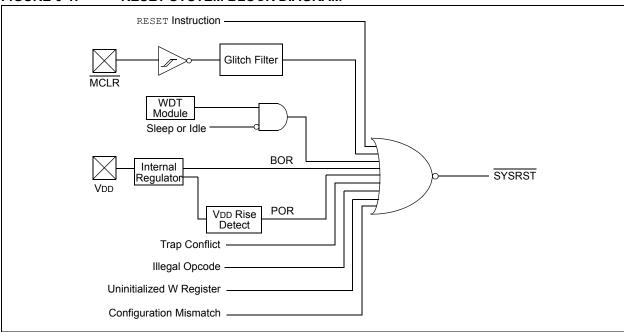

The Reset module combines all reset sources and controls the device Master Reset Signal, SYSRST. The following is a list of device Reset sources:

- POR: Power-on Reset

- BOR: Brown-out Reset

- MCLR: Master Clear Pin Reset

- SWR: RESET Instruction

- WDTO: Watchdog Timer Reset

- CM: Configuration Mismatch Reset

- TRAPR: Trap Conflict Reset

- · IOPUWR: Illegal Condition Device Reset

- Illegal Opcode Reset

- Uninitialized W Register Reset

- Security Reset

#### FIGURE 6-1:

#### RESET SYSTEM BLOCK DIAGRAM

A simplified block diagram of the Reset module is shown in Figure 6-1.

Any active source of reset will make the SYSRST signal active. On system Reset, some of the registers associated with the CPU and peripherals are forced to a known Reset state and some are unaffected.

Note: Refer to the specific peripheral section or Section 3.0 "CPU" of this manual for register Reset states.

All types of device Reset sets a corresponding status bit in the RCON register to indicate the type of Reset (see Register 6-1).

A POR clears all the bits, except for the POR bit (RCON<0>), that are set. The user application can set or clear any bit at any time during code execution. The RCON bits only serve as status bits. Setting a particular Reset status bit in software does not cause a device Reset to occur.

The RCON register also has other bits associated with the Watchdog Timer and device power-saving states. The function of these bits is discussed in other sections of this manual.

**Note:** The status bits in the RCON register should be cleared after they are read so that the next RCON register value after a device Reset is meaningful.

| TABLE 7-1:       | INTERRUPT VECT    | UKS               |                                    |

|------------------|-------------------|-------------------|------------------------------------|

| Vector<br>Number | IVT Address       | AIVT Address      | Interrupt Source                   |

| 0                | 0x000004          | 0x000104          | Reserved                           |

| 1                | 0x000006          | 0x000106          | Oscillator Failure                 |

| 2                | 0x00008           | 0x000108          | Address Error                      |

| 3                | 0x00000A          | 0x00010A          | Stack Error                        |

| 4                | 0x00000C          | 0x00010C          | Math Error                         |

| 5                | 0x00000E          | 0x00010E          | DMA Error                          |

| 6-7              | 0x000010-0x000012 | 0x000110-0x000112 | Reserved                           |

| 8                | 0x000014          | 0x000114          | INT0 – External Interrupt 0        |

| 9                | 0x000016          | 0x000116          | IC1 – Input Capture 1              |

| 10               | 0x000018          | 0x000118          | OC1 – Output Compare 1             |

| 11               | 0x00001A          | 0x00011A          | T1 – Timer1                        |

| 12               | 0x00001C          | 0x00011C          | DMA0 – DMA Channel 0               |

| 13               | 0x00001E          | 0x00011E          | IC2 – Input Capture 2              |

| 14               | 0x000020          | 0x000120          | OC2 – Output Compare 2             |

| 15               | 0x000022          | 0x000122          | T2 – Timer2                        |

| 16               | 0x000024          | 0x000124          | T3 – Timer3                        |

| 17               | 0x000026          | 0x000126          | SPI1E – SPI1 Error                 |

| 18               | 0x000028          | 0x000128          | SPI1 – SPI1 Transfer Done          |

| 19               | 0x00002A          | 0x00012A          | U1RX – UART1 Receiver              |

| 20               | 0x00002C          | 0x00012C          | U1TX – UART1 Transmitter           |

| 21               | 0x00002E          | 0x00012E          | ADC1 – ADC 1                       |

| 22               | 0x000030          | 0x000130          | DMA1 – DMA Channel 1               |

| 23               | 0x000032          | 0x000132          | Reserved                           |

| 24               | 0x000034          | 0x000134          | SI2C1 – I2C1 Slave Events          |

| 25               | 0x000036          | 0x000136          | MI2C1 – I2C1 Master Events         |

| 26               | 0x000038          | 0x000138          | CM – Comparator Interrupt          |

| 27               | 0x00003A          | 0x00013A          | CN – Change Notification Interrupt |

| 28               | 0x00003C          | 0x00013C          | INT1 – External Interrupt 1        |

| 29               | 0x00003E          | 0x00013E          | Reserved                           |

| 30               | 0x000040          | 0x000140          | IC7 – Input Capture 7              |

| 31               | 0x000042          | 0x000142          | IC8 – Input Capture 8              |

| 32               | 0x000044          | 0x000144          | DMA2 – DMA Channel 2               |

| 33               | 0x000046          | 0x000146          | OC3 – Output Compare 3             |

| 34               | 0x000048          | 0x000148          | OC4 – Output Compare 4             |

| 35               | 0x00004A          | 0x00014A          | T4 – Timer4                        |

| 36               | 0x00004C          | 0x00014C          | T5 – Timer5                        |

| 37               | 0x00004E          | 0x00014E          | INT2 – External Interrupt 2        |

| 38               | 0x000050          | 0x000150          | U2RX – UART2 Receiver              |

| 39               | 0x000052          | 0x000152          | U2TX – UART2 Transmitter           |

| 40               | 0x000054          | 0x000154          | SPI2E – SPI2 Error                 |

| 41               | 0x000056          | 0x000156          | SPI2 – SPI2 Transfer Done          |

| 42               | 0x000058          | 0x000158          | C1RX – ECAN1 RX Data Ready         |

| 43               | 0x00005A          | 0x00015A          | C1 – ECAN1 Event                   |

| 44               | 0x00005C          | 0x00015C          | DMA3 – DMA Channel 3               |

| 45-52            | 0x00005E-0x00006C | 0x00015E-0x00016C | Reserved                           |

| 53               | 0x00006E          | 0x00016E          | PMP – Parallel Master Port         |

| 54               | 0x000070          | 0x000170          | DMA – DMA Channel 4                |

TABLE 7-1: INTERRUPT VECTORS

| U-0          | R/W-1               | R/W-0                                  | R/W-0           | U-0              | R/W-1          | R/W-0           | R/W-0 |

|--------------|---------------------|----------------------------------------|-----------------|------------------|----------------|-----------------|-------|

| _            |                     | U1RXIP<2:0>                            |                 |                  |                | SPI1IP<2:0>     |       |

| bit 15       |                     |                                        |                 |                  |                |                 | bit 8 |

|              |                     |                                        |                 |                  |                |                 |       |

| U-0          | R/W-1               | R/W-0                                  | R/W-0           | U-0              | R/W-1          | R/W-0           | R/W-0 |

| —            |                     | SPI1EIP<2:0>                           |                 |                  |                | T3IP<2:0>       |       |

| bit 7        |                     |                                        |                 |                  |                |                 | bit C |

| Legend:      |                     |                                        |                 |                  |                |                 |       |

| R = Readab   | ole bit             | W = Writable                           | bit             | U = Unimplei     | mented bit, re | ad as '0'       |       |

| -n = Value a | It POR              | '1' = Bit is set                       |                 | '0' = Bit is cle |                | x = Bit is unkn | own   |

|              |                     |                                        |                 |                  |                |                 |       |

| bit 15       | Unimpleme           | nted: Read as '                        | 0'              |                  |                |                 |       |

| bit 14-12    | U1RXIP<2:0          | <b>)&gt;:</b> UART1 Rece               | eiver Interrupt | Priority bits    |                |                 |       |

|              | 111 = Interr        | upt is priority 7 (                    | highest priori  | ty interrupt)    |                |                 |       |

|              | •                   |                                        |                 |                  |                |                 |       |

|              | •                   |                                        |                 |                  |                |                 |       |

|              | 001 = Interr        | upt is priority 1                      |                 |                  |                |                 |       |

|              | 000 <b>= Interr</b> | upt source is dis                      | abled           |                  |                |                 |       |

| bit 11       | Unimpleme           | nted: Read as '                        | 0'              |                  |                |                 |       |

| bit 10-8     |                     | SPI1 Event In                          |                 | •                |                |                 |       |

|              | 111 = Interr        | upt is priority 7 (                    | highest priori  | ty interrupt)    |                |                 |       |

|              | •                   |                                        |                 |                  |                |                 |       |

|              | •                   |                                        |                 |                  |                |                 |       |

|              |                     | upt is priority 1                      |                 |                  |                |                 |       |

|              |                     | upt source is dis                      |                 |                  |                |                 |       |

| bit 7        | •                   | nted: Read as '                        |                 |                  |                |                 |       |

| bit 6-4      |                     | 0>: SPI1 Error Ir                      | -               | -                |                |                 |       |

|              | 111 = Interr<br>•   | upt is priority 7 (                    | nignest priori  | ty interrupt)    |                |                 |       |

|              | •                   |                                        |                 |                  |                |                 |       |

|              | •                   |                                        |                 |                  |                |                 |       |

|              |                     | upt is priority 1<br>upt source is dis | abled           |                  |                |                 |       |

| bit 3        |                     | nted: Read as '                        |                 |                  |                |                 |       |

| bit 2-0      | -                   | Timer3 Interrupt                       |                 |                  |                |                 |       |

|              |                     | upt is priority 7 (                    | -               | ty interrupt)    |                |                 |       |

|              | •                   |                                        |                 | • •              |                |                 |       |

|              | •                   |                                        |                 |                  |                |                 |       |

|              | •<br>001 = Interr   | upt is priority 1                      |                 |                  |                |                 |       |

|              |                     | upt is priority 1                      |                 |                  |                |                 |       |

000 = Interrupt source is disabled

| U-0           | R/W-1         | R/W-0                                  | R/W-0           | U-0              | R/W-1            | R/W-0           | R/W-0 |

|---------------|---------------|----------------------------------------|-----------------|------------------|------------------|-----------------|-------|

| _             |               | CRCIP<2:0>                             |                 | _                |                  | U2EIP<2:0>      |       |

| bit 15        |               |                                        |                 |                  |                  |                 | bit 8 |

|               |               |                                        |                 |                  |                  |                 |       |

| U-0           | R/W-1         | R/W-0                                  | R/W-0           | U-0              | U-0              | U-0             | U-0   |

|               |               | U1EIP<2:0>                             |                 |                  |                  |                 |       |

| bit 7         |               |                                        |                 |                  |                  |                 | bit   |

| Legend:       |               |                                        |                 |                  |                  |                 |       |

| R = Readabl   | e bit         | W = Writable                           | bit             | U = Unimple      | mented bit, read | d as '0'        |       |

| -n = Value at | POR           | '1' = Bit is set                       |                 | '0' = Bit is cle | eared            | x = Bit is unkr | nown  |

|               |               |                                        |                 |                  |                  |                 |       |

| bit 15        | -             | nted: Read as '                        |                 |                  |                  |                 |       |

| bit 14-12     |               | CRC Generate                           |                 |                  | ty bits          |                 |       |

|               | 111 = Interro | upt is priority 7 (                    | highest priorit | ty interrupt)    |                  |                 |       |

|               | •             |                                        |                 |                  |                  |                 |       |

|               | •             |                                        |                 |                  |                  |                 |       |

|               |               | upt is priority 1<br>upt source is dis | abled           |                  |                  |                 |       |

| bit 11        |               | nted: Read as '                        |                 |                  |                  |                 |       |

| bit 10-8      | -             | : UART2 Error I                        |                 | ity bite         |                  |                 |       |

| DIL 10-0      |               | upt is priority 7 (                    |                 | •                |                  |                 |       |

|               | •             |                                        | nightest phone  | ly interrupt)    |                  |                 |       |

|               | •             |                                        |                 |                  |                  |                 |       |

|               | •             |                                        |                 |                  |                  |                 |       |

|               |               | upt is priority 1<br>upt source is dis | abled           |                  |                  |                 |       |

| bit 7         |               | nted: Read as '                        |                 |                  |                  |                 |       |

| bit 6-4       | -             | UART1 Error I                          |                 | itv bits         |                  |                 |       |

|               |               | upt is priority 7 (                    | -               | -                |                  |                 |       |

|               | •             | · · · · · · · · · · · · · · ·          | 5               | - <b>J</b>       |                  |                 |       |

|               | •             |                                        |                 |                  |                  |                 |       |

|               |               |                                        |                 |                  |                  |                 |       |

|               | •             | upt is priority 1                      |                 |                  |                  |                 |       |

bit 3-0 Unimplemented: Read as '0'

# REGISTER 8-7: DMACS0: DMA CONTROLLER STATUS REGISTER 0 (CONTINUED)

| bit 3 | XWCOL3: Channel 3 DMA RAM Write Collision Flag bit |

|-------|----------------------------------------------------|

|       | 1 = Write collision detected                       |

|       | 0 = No write collision detected                    |

| bit 2 | XWCOL2: Channel 2 DMA RAM Write Collision Flag bit |

|       | 1 = Write collision detected                       |

|       | 0 = No write collision detected                    |

| bit 1 | XWCOL1: Channel 1 DMA RAM Write Collision Flag bit |

|       | 1 = Write collision detected                       |

|       | 0 = No write collision detected                    |

| bit 0 | XWCOL0: Channel 0 DMA RAM Write Collision Flag bit |

|       | 1 = Write collision detected                       |

|       | 0 = No write collision detected                    |

#### 9.4 Clock Switching Operation

Applications are free to switch among any of the four clock sources (Primary, LP, FRC and LPRC) under software control at any time. To limit the possible side effects of this flexibility, PIC24HJ32GP302/304, PIC24HJ64GPX02/X04 and PIC24HJ128GPX02/X04 devices have a safeguard lock built into the switch process.

Note: Primary Oscillator mode has three different submodes (XT, HS and EC), which are determined by the POSCMD<1:0> Configuration bits. While an application can switch to and from Primary Oscillator mode in software, it cannot switch among the different primary submodes without reprogramming the device.

#### 9.4.1 ENABLING CLOCK SWITCHING

To enable clock switching, the FCKSM1 Configuration bit in the Configuration register must be programmed to '0'. (Refer to **Section 25.1 "Configuration Bits"** for further details.) If the FCKSM1 Configuration bit is unprogrammed ('1'), the clock switching function and FSCM function are disabled. This is the default setting.

The NOSC<2:0> control bits (OSCCON<10:8>) do not control the clock selection when clock switching is disabled. However, the COSC<2:0> bits (OSC-CON<14:12>) reflect the clock source selected by the FNOSC<2:0> Configuration bits FOSCSEL<2:0>.

The OSWEN control bit (OSCCON<0>) has no effect when clock switching is disabled. It is held at '0' at all times.

#### 9.4.2 OSCILLATOR SWITCHING SEQUENCE

Performing a clock switch requires this basic sequence:

- 1. If required, read the COSC<2:0> bits to determine the current oscillator source.

- 2. Perform the unlock sequence to allow a write to the OSCCON register high byte.

- 3. Write the appropriate value to the NOSC<2:0> control bits for the new oscillator source.

- 4. Perform the unlock sequence to allow a write to the OSCCON register low byte.

- 5. Set the OSWEN bit to initiate the oscillator switch.

After the basic sequence is completed, the system clock hardware responds automatically as follows:

- The clock switching hardware compares the COSC<2:0> status bits with the new value of the NOSC<2:0> control bits. If they are the same, the clock switch is a redundant operation. In this case, the OSWEN bit is cleared automatically and the clock switch is aborted.

- 2. If a valid clock switch has been initiated, the LOCK (OSCCON<5>) and the CF

(OSCCON<3>) status bits are cleared.

- 3. The new oscillator is turned on by the hardware if it is not currently running. If a crystal oscillator must be turned on, the hardware waits until the Oscillator Start-up Timer (OST) expires. If the new source is using the PLL, the hardware waits until a PLL lock is detected (LOCK = 1).

- 4. The hardware waits for 10 clock cycles from the new clock source and then performs the clock switch.

- The hardware clears the OSWEN bit to indicate a successful clock transition. In addition, the NOSC bit values are transferred to the COSC<2:0> status bits.

- The old clock source is turned off at this time, with the exception of LPRC (if WDT or FSCM are enabled) or LP (if LPOSCEN remains set).

- Note 1: The processor continues to execute code throughout the clock switching sequence. Timing-sensitive code should not be executed during this time.

- 2: Direct clock switches between any primary oscillator mode with PLL and FRCPLL mode are not permitted. This applies to clock switches in either direction. In these instances, the application must switch to FRC mode as a transition clock source between the two PLL modes.

- 3: Refer to Section 39. "Oscillator (Part III)" (DS70308) in the "dsPIC33F/ PIC24H Family Reference Manual" for details.

# 9.5 Fail-Safe Clock Monitor (FSCM)

The Fail-Safe Clock Monitor (FSCM) allows the device to continue to operate even in the event of an oscillator failure. The FSCM function is enabled by programming. If the FSCM function is enabled, the LPRC internal oscillator runs at all times (except during Sleep mode) and is not subject to control by the Watchdog Timer.

If an oscillator fails, the FSCM generates a clock failure trap event and switches the system clock over to the FRC oscillator. Then the application program can either attempt to restart the oscillator or execute a controlled shutdown. The trap can be treated as a warm Reset by simply loading the Reset address into the oscillator fail trap vector.

If the PLL multiplier is used to scale the system clock, the internal FRC is also multiplied by the same factor on clock failure. Essentially, the device switches to FRC with PLL on a clock failure.

| U-0          | U-0                               | U-0                                                | R/W-1        | R/W-1            | R/W-1           | R/W-1           | R/W-1 |

|--------------|-----------------------------------|----------------------------------------------------|--------------|------------------|-----------------|-----------------|-------|

| _            | _                                 | _                                                  |              |                  | U1CTSR<4:0      | )>              |       |

| it 15        |                                   |                                                    |              |                  |                 |                 | bit 8 |

| U-0          | U-0                               | U-0                                                | R/W-1        | R/W-1            | R/W-1           | R/W-1           | R/W-1 |

| —            |                                   |                                                    |              |                  | U1RXR<4:0       | >               |       |

| pit 7        |                                   |                                                    |              |                  |                 |                 | bit ( |

| _egend:      |                                   |                                                    |              |                  |                 |                 |       |

| R = Readabl  | le bit                            | W = Writable                                       | bit          | U = Unimple      | mented bit, rea | ad as '0'       |       |

| n = Value at | t POR                             | '1' = Bit is set                                   |              | '0' = Bit is cle | eared           | x = Bit is unkr | nown  |

|              | •                                 |                                                    |              |                  |                 |                 |       |

|              | 00001 = Inpu<br>00000 = Inpu      |                                                    |              |                  |                 |                 |       |

| oit 7-5      | Unimplemen                        | ted: Read as '                                     | 0'           |                  |                 |                 |       |

| bit 4-0      | 11111 <b>= Inpu</b>               | : Assign UART<br>ut tied to Vss<br>ut tied to RP25 | 1 Receive (U | 1RX) to the co   | rresponding R   | Pn pin          |       |

|              | •<br>00001 = Inpu<br>00000 = Inpu |                                                    |              |                  |                 |                 |       |

## REGISTER 11-8: RPINR18: PERIPHERAL PIN SELECT INPUT REGISTER 18

| REGISTER     |                       | R19: PERIPHE                       | _     |                  |                 | -               |       |

|--------------|-----------------------|------------------------------------|-------|------------------|-----------------|-----------------|-------|

| U-0          | U-0                   | U-0                                | R/W-1 | R/W-1            | R/W-1           | R/W-1           | R/W-1 |

| —            | —                     | —                                  |       |                  | U2CTSR<4:       | )>              |       |

| bit 15       |                       |                                    |       |                  |                 |                 | bit 8 |

| U-0          | U-0                   | U-0                                | R/W-1 | R/W-1            | R/W-1           | R/W-1           | R/W-1 |

| _            | _                     | _                                  |       |                  | U2RXR<4:0       | >               |       |

| bit 7        |                       |                                    |       |                  |                 |                 | bit ( |

| Legend:      |                       |                                    |       |                  |                 |                 |       |

| R = Readab   | le bit                | W = Writable b                     | bit   | U = Unimple      | mented bit, rea | ad as '0'       |       |

| -n = Value a | t POR                 | '1' = Bit is set                   |       | '0' = Bit is cle | eared           | x = Bit is unkı | nown  |

|              | •<br>•<br>00001 = Inp | ut tied to RP25                    |       |                  |                 |                 |       |

| bit 7-5      | •                     | ut tied to RP0<br>nted: Read as '0 | ,     |                  |                 |                 |       |

| bit 4-0      | •                     | >: Assign UART2                    |       | 2RX) to the co   | rresponding R   | Pn nin          |       |

| 511 4-0      | 11111 <b>= Inp</b>    | ut tied to Vss<br>ut tied to RP25  |       |                  |                 | i ii piii       |       |

|              | •                     |                                    |       |                  |                 |                 |       |

|              | •                     |                                    |       |                  |                 |                 |       |

|              | •                     |                                    |       |                  |                 |                 |       |

|              |                       | ut tied to RP1                     |       |                  |                 |                 |       |

00000 = Input tied to RP0

#### 16.1 SPI Helpful Tips

ľ

- 1. In Frame mode, if there is a possibility that the master may not be initialized before the slave:

- a) If FRMPOL (SPIxCON2<13>) = 1, use a pull-down resistor on SSx.

- b) If FRMPOL = 0, use a pull-up resistor on  $\frac{1}{SSx}$ .

| Note: | This                  | insures | that  | the        | first | fra | ame |

|-------|-----------------------|---------|-------|------------|-------|-----|-----|

|       | transm                | nission | after | initializa | ation | is  | not |

|       | shifted or corrupted. |         |       |            |       |     |     |

- 2. In non-framed 3-wire mode, (i.e., not using SSx from a master):

- a) If CKP (SPIxCON1<6>) = 1, always place a pull-up resistor on SSx.

- b) If CKP = <u>0</u>, always place a pull-down resistor on SSx.

- **Note:** This will insure that during power-up and initialization the master/slave will not lose sync due to an errant SCK transition that would cause the slave to accumulate data shift errors for both transmit and receive appearing as corrupted data.

- FRMEN (SPIxCON2<15>) = 1 and SSEN (SPIxCON1<7>) = 1 are exclusive and invalid. In Frame mode, SCKx is continuous and the Frame sync pulse is active on the SSx pin, which indicates the start of a data frame.

**Note:** Not all third-party devices support Frame mode timing. Refer to the SPI electrical characteristics for details.

- In Master mode only, set the SMP bit (SPIxCON1<9>) to a '1' for the fastest SPI data rate possible. The SMP bit can only be set at the same time or after the MSTEN bit (SPIxCON1<5>) is set.

- 5. To avoid invalid slave read data to the master, the user's master software must guarantee enough time for slave software to fill its write buffer before the user application initiates a master write/read cycle. It is always advisable to preload the SPIxBUF transmit register in advance of the next master transaction cycle. SPIxBUF is transferred to the SPI shift register and is empty once the data transmission begins.

#### 16.2 SPI Resources

Many useful resources related to SPI are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

Note: In the event you are not able to access the product page using the link above, enter this URL in your browser: http://www.microchip.com/wwwproducts/ Devices.aspx?dDocName=en532315

#### 16.2.1 KEY RESOURCES

- Section 18. "Serial Peripheral Interface (SPI)" (DS70206)

- Code Samples

- · Application Notes

- Software Libraries

- Webinars

- All related dsPIC33F/PIC24H Family Reference Manuals Sections

- Development Tools

## REGISTER 18-1: UXMODE: UARTX MODE REGISTER (CONTINUED)

| bit 4   | URXINV: Receive Polarity Inversion bit                                                                                                                                             |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | 1 = UxRX Idle state is '0'<br>0 = UxRX Idle state is '1'                                                                                                                           |

| bit 3   | BRGH: High Baud Rate Enable bit                                                                                                                                                    |

|         | <ul> <li>1 = BRG generates 4 clocks per bit period (4x baud clock, High-Speed mode)</li> <li>0 = BRG generates 16 clocks per bit period (16x baud clock, Standard mode)</li> </ul> |

| bit 2-1 | PDSEL<1:0>: Parity and Data Selection bits                                                                                                                                         |

|         | <ul> <li>11 = 9-bit data, no parity</li> <li>10 = 8-bit data, odd parity</li> <li>01 = 8-bit data, even parity</li> <li>00 = 8-bit data, no parity</li> </ul>                      |

| bit 0   | STSEL: Stop Bit Selection bit<br>1 = Two Stop bits<br>0 = One Stop bit                                                                                                             |

|         |                                                                                                                                                                                    |

- **Note 1:** Refer to **Section 17. "UART**" (DS70232) in the *"dsPIC33F/PIC24H Family Reference Manual"* for information on enabling the UART module for receive or transmit operation.

- 2: This feature is only available for the 16x BRG mode (BRGH = 0).

# PIC24HJ32GP302/304, PIC24HJ64GPX02/X04 AND PIC24HJ128GPX02/X04

| R/W-0                          | R/W-0                                                                                              | R/W-0                                                                                                                                        | U-0                                | U-0               | U-0               | U-0                | U-0   |  |

|--------------------------------|----------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|-------------------|-------------------|--------------------|-------|--|

|                                | DMABS<2:0>                                                                                         |                                                                                                                                              | _                                  | —                 |                   | —                  | —     |  |

| bit 15                         |                                                                                                    |                                                                                                                                              |                                    |                   |                   |                    | bit 8 |  |

| U-0                            | U-0                                                                                                | U-0                                                                                                                                          | R/W-0                              | R/W-0             | R/W-0             | R/W-0              | R/W-0 |  |

| _                              | _                                                                                                  | _                                                                                                                                            |                                    |                   | FSA<4:0>          |                    |       |  |

| bit 7                          |                                                                                                    |                                                                                                                                              |                                    |                   |                   |                    | bit ( |  |

| Levende                        |                                                                                                    | $\Omega = M/rite able$                                                                                                                       |                                    | 'O' oon ho writte | ve to close the l | -:4                |       |  |

| L <b>egend:</b><br>R = Readabl | a hit                                                                                              | W = Writable                                                                                                                                 | •                                  | '0' can be writte |                   |                    |       |  |

| n = Value at                   |                                                                                                    | '1' = Bit is set                                                                                                                             |                                    | 0 = Onimplen      | nented bit, read  | x = Bit is unknown |       |  |

| -ii – value at                 | TOR                                                                                                | 1 - Dit 13 3et                                                                                                                               |                                    |                   | areu              |                    |       |  |

| bit 12-5                       | 101 = 24 buff<br>100 = 16 buff<br>011 = 12 buff<br>010 = 8 buffe<br>001 = 6 buffe<br>000 = 4 buffe | ers in DMA RA<br>ers in DMA RA<br>ers in DMA RA<br>ers in DMA RA<br>rs in DMA RAN<br>rs in DMA RAN<br>rs in DMA RAN<br><b>ted:</b> Read as ' | AM<br>AM<br>AM<br>A<br>A<br>A<br>A |                   |                   |                    |       |  |

| bit 4-0                        | -                                                                                                  | FO Area Starts                                                                                                                               |                                    | nite              |                   |                    |       |  |

| JIL <del>1</del> -U            | 11111 <b>= Rea</b>                                                                                 | d buffer RB31<br>d buffer RB30                                                                                                               |                                    | 5113              |                   |                    |       |  |

| REGISTER            | 24-5. FIVIST                                          |                                                                                                                                                                                                                                                                                 | LFURTS        | IATUS REGI       | SIER            |                    |       |  |  |  |

|---------------------|-------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|------------------|-----------------|--------------------|-------|--|--|--|

| R-0                 | R/W-0, HS                                             | U-0                                                                                                                                                                                                                                                                             | U-0           | R-0              | R-0             | R-0                | R-0   |  |  |  |

| IBF                 | IBOV                                                  | —                                                                                                                                                                                                                                                                               | _             | IB3F             | IB2F            | IB1F               | IB0F  |  |  |  |

| bit 15              |                                                       |                                                                                                                                                                                                                                                                                 |               |                  |                 |                    | bit 8 |  |  |  |

|                     |                                                       |                                                                                                                                                                                                                                                                                 |               |                  |                 |                    |       |  |  |  |

| R-1                 | R/W-0, HS                                             | U-0                                                                                                                                                                                                                                                                             | U-0           | R-1              | R-1             | R-1                | R-1   |  |  |  |

| OBE                 | OBUF                                                  | —                                                                                                                                                                                                                                                                               |               | OB3E             | OB2E            | OB1E               | OB0E  |  |  |  |

| bit 7               |                                                       |                                                                                                                                                                                                                                                                                 |               |                  |                 |                    | bit C |  |  |  |