Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 20 MIPS                                                                        |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                   |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                     |

| Number of I/O              | 21                                                                             |

| Program Memory Size        | 128KB (43K x 24)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                |                                                                                |

| RAM Size                   | 8K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                      |

| Data Converters            | A/D 10x10b/12b                                                                 |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 150°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                                 |

| Supplier Device Package    | 28-SOIC                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24hj128gp502-h-so |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

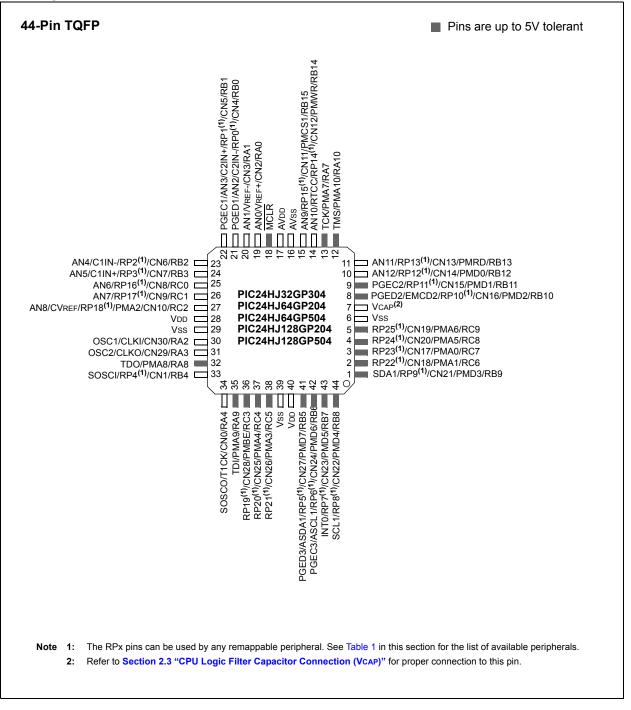

#### Pin Diagrams (Continued)

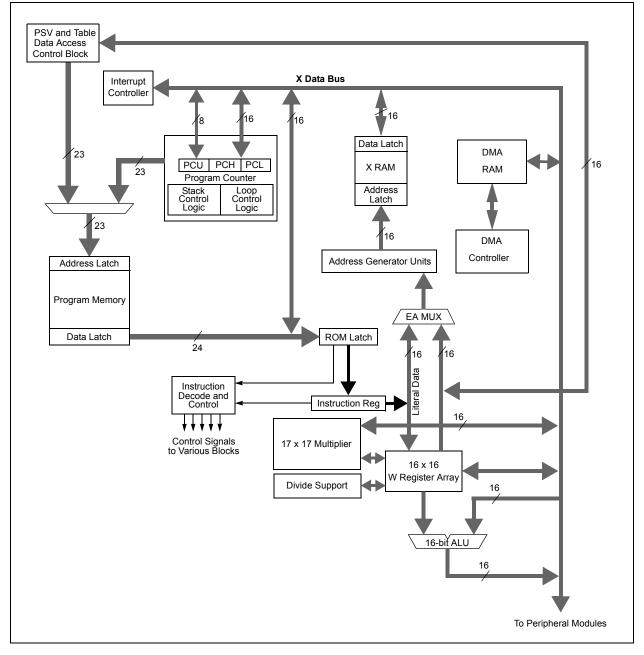

#### 3.3 Special MCU Features

The PIC24HJ32GP302/304, PIC24HJ64GPX02/X04 and PIC24HJ128GPX02/X04 features a 17-bit by 17bit, single-cycle multiplier. The multiplier can perform signed, unsigned and mixed-sign multiplication. Using a 17-bit by 17-bit multiplier for 16-bit by 16-bit multiplication makes mixed-sign multiplication possible. The PIC24HJ32GP302/304, PIC24HJ64GPX02/X04 and PIC24HJ128GPX02/X04 devices support 16/16 and 32/16 integer divide operations. All divide instructions are iterative operations. They must be executed within a REPEAT loop, resulting in a total execution time of 19 instruction cycles. The divide operation can be interrupted during any of those 19 cycles without loss of data.

A multi-bit data shifter is used to perform up to a 16-bit, left or right shift in a single cycle.

## FIGURE 3-1: PIC24HJ32GP302/304, PIC24HJ64GPX02/X04 AND PIC24HJ128GPX02/X04 CPU CORE BLOCK DIAGRAM

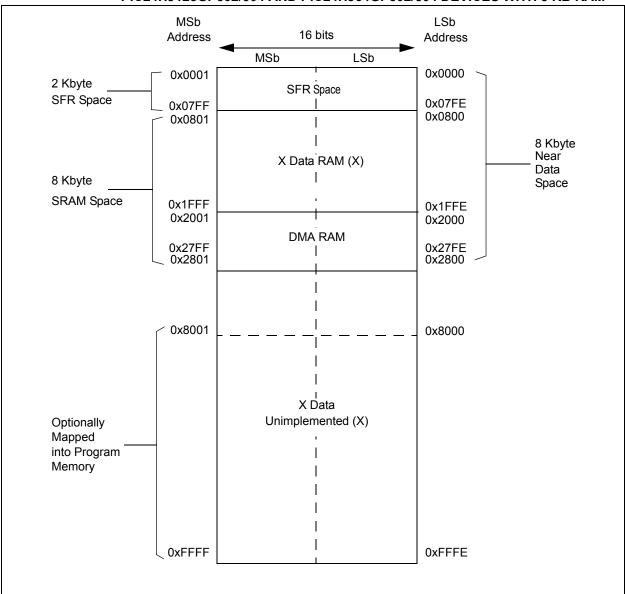

## FIGURE 4-4: DATA MEMORY MAP FOR PIC24HJ128GP202/204, PIC24HJ64GP202/204, PIC24HJ128GP502/504 AND PIC24HJ64GP502/504 DEVICES WITH 8 KB RAM

## 4.3 Memory Organization Resources

Many useful resources related to Memory Organization are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

Note: In the event you are not able to access the product page using the link above, enter this URL in your browser: http://www.microchip.com/wwwprod-ucts/Devices.aspx?dDoc-Name=en534555

## 4.3.1 KEY RESOURCES

- Section 4. "Program Memory" (DS70203)

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All related dsPIC33F/PIC24H Family Reference Manuals Sections

- Development Tools

## 4.4 Special Function Register Maps

### TABLE 4-1: CPU CORE REGISTERS MAP

|             | <b>T</b> I. |        |        |        |        |        |        |         |                |                |            |           |                |              |             |        |       |               |

|-------------|-------------|--------|--------|--------|--------|--------|--------|---------|----------------|----------------|------------|-----------|----------------|--------------|-------------|--------|-------|---------------|

| SFR<br>Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9   | Bit 8          | Bit 7          | Bit 6      | Bit 5     | Bit 4          | Bit 3        | Bit 2       | Bit 1  | Bit 0 | All<br>Resets |

| WREG0       | 0000        |        |        |        |        |        |        |         | Working Re     | gister 0       |            |           |                |              |             |        |       | 0000          |

| WREG1       | 0002        |        |        |        |        |        |        |         | Working Re     | gister 1       |            |           |                |              |             |        |       | 0000          |

| WREG2       | 0004        |        |        |        |        |        |        |         | Working Re     | egister 2      |            |           |                |              |             |        |       | 0000          |

| WREG3       | 0006        |        |        |        |        |        |        |         | Working Re     | egister 3      |            |           |                |              |             |        |       | 0000          |

| WREG4       | 8000        |        |        |        |        |        |        |         | Working Re     | egister 4      |            |           |                |              |             |        |       | 0000          |

| WREG5       | 000A        |        |        |        |        |        |        |         | Working Re     | egister 5      |            |           |                |              |             |        |       | 0000          |

| WREG6       | 000C        |        |        |        |        |        |        |         | Working Re     | egister 6      |            |           |                |              |             |        |       | 0000          |

| WREG7       | 000E        |        |        |        |        |        |        |         | Working Re     | egister 7      |            |           |                |              |             |        |       | 0000          |

| WREG8       | 0010        |        |        |        |        |        |        |         | Working Re     | egister 8      |            |           |                |              |             |        |       | 0000          |

| WREG9       | 0012        |        |        |        |        |        |        |         | Working Re     | egister 9      |            |           |                |              |             |        |       | 0000          |

| WREG10      | 0014        |        |        |        |        |        |        |         | Working Reg    | gister 10      |            |           |                |              |             |        |       | 0000          |

| WREG11      | 0016        |        |        |        |        |        |        |         | Working Reg    | gister 11      |            |           |                |              |             |        |       | 0000          |

| WREG12      | 0018        |        |        |        |        |        |        |         | Working Reg    | gister 12      |            |           |                |              |             |        |       | 0000          |

| WREG13      | 001A        |        |        |        |        |        |        |         | Working Reg    | gister 13      |            |           |                |              |             |        |       | 0000          |

| WREG14      | 001C        |        |        |        |        |        |        |         | Working Reg    | gister 14      |            |           |                |              |             |        |       | 0000          |

| WREG15      | 001E        |        |        |        |        |        |        |         | Working Reg    | gister 15      |            |           |                |              |             |        |       | 0800          |

| SPLIM       | 0020        |        |        |        |        |        |        | Sta     | ack Pointer Li | mit Register   |            |           |                |              |             |        |       | XXXX          |

| PCL         | 002E        |        |        |        |        |        |        | Program | m Counter Lo   | w Word Regi    | ster       |           |                |              |             |        |       | 0000          |

| PCH         | 0030        | _      |        | —      | _      | _      | _      |         | _              |                |            | Progra    | am Counter     | High Byte Re | egister     |        |       | 0000          |

| TBLPAG      | 0032        | _      |        | —      | —      | _      |        |         | —              |                |            | Table     | Page Addre     | ss Pointer R | egister     |        |       | 0000          |

| PSVPAG      | 0034        | -      |        | —      | _      | _      |        |         | _              |                | Prog       | ram Memor | y Visibility P | age Address  | Pointer Reg | gister |       | 0000          |

| RCOUNT      | 0036        |        |        |        |        |        |        | Rep     | eat Loop Cou   | unter Register | r          |           |                |              |             |        |       | XXXX          |

| SR          | 0042        | _      |        | —      | —      | _      | _      |         | DC             | IPL2           | IPL1       | IPL0      | RA             | Ν            | OV          | Z      | С     | 0000          |

| CORCON      | 0044        | _      | _      | _      | —      | _      | _      | _       | -              | _              | _          | _         | _              | IPL3         | PSV         | _      | _     | 0000          |

| DISICNT     | 0052        | _      |        |        |        |        |        |         | Disab          | le Interrupts  | Counter Re | egister   |                |              |             |        |       | XXXX          |

|             |             |        |        |        |        |        |        |         |                |                |            |           |                |              |             |        |       |               |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## TABLE 4-15: DMA REGISTER MAP (CONTINUED)

|           |      |        |        |        |        |        | /      |           |       |           |        |        |        |           |        |        |        |               |

|-----------|------|--------|--------|--------|--------|--------|--------|-----------|-------|-----------|--------|--------|--------|-----------|--------|--------|--------|---------------|

| File Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 B   | Bit 8 | Bit 7     | Bit 6  | Bit 5  | Bit 4  | Bit 3     | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

| DMA5PAD   | 03C4 |        |        |        |        |        |        |           | PA    | AD<15:0>  |        |        |        |           |        |        |        | 0000          |

| DMA5CNT   | 03C6 | _      | _      | _      | _      | _      | _      |           |       |           |        | CNT    | <9:0>  |           |        |        |        | 0000          |

| DMA6CON   | 03C8 | CHEN   | SIZE   | DIR    | HALF   | NULLW  | _      | —         | —     | _         | _      | AMOD   | E<1:0> | _         | _      | MODE   | <1:0>  | 0000          |

| DMA6REQ   | 03CA | FORCE  | _      | _      | _      | _      | _      | —         | —     | _         |        |        | I      | RQSEL<6:0 | >      |        |        | 0000          |

| DMA6STA   | 03CC |        |        |        |        |        |        |           | S     | TA<15:0>  |        |        |        |           |        |        |        | 0000          |

| DMA6STB   | 03CE |        |        |        |        |        |        |           | ST    | TB<15:0>  |        |        |        |           |        |        |        | 0000          |

| DMA6PAD   | 03D0 |        |        |        |        |        |        |           | PA    | AD<15:0>  |        |        |        |           |        |        |        | 0000          |

| DMA6CNT   | 03D2 | —      | _      | —      | _      | _      | _      |           |       |           |        | CNT    | <9:0>  |           |        |        |        | 0000          |

| DMA7CON   | 03D4 | CHEN   | SIZE   | DIR    | HALF   | NULLW  | _      | _         | _     | _         | —      | AMOD   | E<1:0> | _         | _      | MODE   | <1:0>  | 0000          |

| DMA7REQ   | 03D6 | FORCE  | _      | _      | _      | _      | _      | —         | —     | _         |        |        | I      | RQSEL<6:0 | >      |        |        | 0000          |

| DMA7STA   | 03D8 |        |        |        |        |        |        |           | S     | TA<15:0>  |        |        |        |           |        |        |        | 0000          |

| DMA7STB   | 03DA |        |        |        |        |        |        |           | ST    | TB<15:0>  |        |        |        |           |        |        |        | 0000          |

| DMA7PAD   | 03DC |        |        |        |        |        |        |           | PA    | AD<15:0>  |        |        |        |           |        |        |        | 0000          |

| DMA7CNT   | 03DE | _      | _      | _      | _      | _      | _      |           |       |           |        | CNT    | <9:0>  |           |        |        |        | 0000          |

| DMACS0    | 03E0 | PWCOL7 | PWCOL6 | PWCOL5 | PWCOL4 | PWCOL3 | PWCOL2 | PWCOL1 PW | VCOL0 | XWCOL7    | XWCOL6 | XWCOL5 | XWCOL4 | XWCOL3    | XWCOL2 | XWCOL1 | XWCOL0 | 0000          |

| DMACS1    | 03E2 | —      | _      | —      | _      |        | LSTCH  | H<3:0>    |       | PPST7     | PPST6  | PPST5  | PPST4  | PPST3     | PPST2  | PPST1  | PPST0  | 0000          |

| DSADR     | 03E4 |        |        |        |        |        |        |           | DSA   | ADR<15:0> |        |        |        |           |        |        |        | 0000          |

|           |      |        |        |        |        |        |        |           |       |           |        |        |        |           |        |        |        |               |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-24: REAL-TIME CLOCK AND CALENDAR REGISTER MAP

| File Name | Addr | Bit 15 | Bit 14 | Bit 13  | Bit 12  | Bit 11  | Bit 10 | Bit 9           | Bit 8         | Bit 7      | Bit 6    | Bit 5 | Bit 4 | Bit 3  | Bit 2 | Bit 1    | Bit 0  | All<br>Resets |

|-----------|------|--------|--------|---------|---------|---------|--------|-----------------|---------------|------------|----------|-------|-------|--------|-------|----------|--------|---------------|

| ALRMVAL   | 0620 |        |        |         |         |         | Alar   | m Value Regis   | ter Window ba | ased on AP | TR<1:0>  |       |       |        |       |          |        | XXXX          |

| ALCFGRPT  | 0622 | ALRMEN | CHIME  |         | AMASK   | <3:0>   |        | ALRMP           | [R<1:0>       |            |          |       | ARP   | T<7:0> |       |          |        | 0000          |

| RTCVAL    | 0624 |        |        |         |         |         | RTCC   | C Value Registe | er Window bas | sed on RTC | PTR<1:0> |       |       |        |       |          |        | XXXX          |

| RCFGCAL   | 0626 | RTCEN  | _      | RTCWREN | RTCSYNC | HALFSEC | RTCOE  | RTCPT           | R<1:0>        |            |          |       | CAL   | .<7:0> |       |          |        | 0000          |

| PADCFG1   | 02FC | _      | —      | —       | _       | _       | _      | —               | —             | —          | —        | -     | -     | _      | —     | RTSECSEL | PMPTTL | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-25: CRC REGISTER MAP

| File Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10    | Bit 9 | Bit 8       | Bit 7         | Bit 6  | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-----------|------|--------|--------|--------|--------|--------|-----------|-------|-------------|---------------|--------|-------|-------|-------|-------|-------|-------|---------------|

|           |      |        |        |        |        |        |           |       |             |               |        |       |       |       |       |       |       | Resels        |

| CRCCON    | 0640 | —      | _      | CSIDL  |        | N      | /WORD<4:0 | >     |             | CRCFUL        | CRCMPT | _     | CRCGO |       | PLEN  | <3:0> |       | 0000          |

| CRCXOR    | 0642 |        |        |        |        |        |           |       | X<1         | 5:0>          |        |       |       |       |       |       |       | 0000          |

| CRCDAT    | 0644 |        |        |        |        |        |           |       | CRC Data Ir | nput Register | -      |       |       |       |       |       |       | 0000          |

| CRCWDAT   | 0646 |        |        |        |        |        |           |       | CRC Resu    | ult Register  |        |       |       |       |       |       |       | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-26: DUAL COMPARATOR REGISTER MAP

| File Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9   | Bit 8   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-----------|------|--------|--------|--------|--------|--------|--------|---------|---------|-------|-------|-------|-------|-------|-------|-------|-------|---------------|

| CMCON     | 0630 | CMIDL  | -      | C2EVT  | C1EVT  | C2EN   | C1EN   | C2OUTEN | C10UTEN | C2OUT | C10UT | C2INV | C1INV | C2NEG | C2POS | C1NEG | C1POS | 0000          |

| CVRCON    | 0632 | _      | -      | -      | _      |        | -      | _       | _       | CVREN | CVROE | CVRR  | CVRSS |       | CVR   | <3:0> |       | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-27: PORTA REGISTER MAP FOR PIC24HJ128GP202/502, PIC24HJ64GP202/502 AND PIC24HJ32GP302

| File Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|-----------|------|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|--------|--------|--------|--------|--------|---------------|

| TRISA     | 02C0 | _      | —      | _      | _      | —      | _      | _     | _     | _     | _     | _     | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 001F          |

| PORTA     | 02C2 | _      | —      | _      | —      | —      | _      | _     | _     | -     | -     | _     | RA4    | RA3    | RA2    | RA1    | RA0    | XXXX          |

| LATA      | 02C4 |        | _      | _      |        | —      | _      | _     | —     | —     |       | _     | LATA4  | LATA3  | LATA2  | LATA1  | LATA0  | XXXX          |

| ODCA      | 02C6 | -      | _      | -      | _      | —      | _      | -     | _     | _     | -     | -     | —      | -      | -      | -      | —      | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

© 2007-2012 Microchip Technology Inc.

### 6.9 Configuration Mismatch Reset

To maintain the integrity of the peripheral pin select control registers, they are constantly monitored with shadow registers in hardware. If an unexpected change in any of the registers occur (such as cell disturbances caused by ESD or other external events), a configuration mismatch Reset occurs.

The Configuration Mismatch Flag bit (CM) in the Reset Control register (RCON<9>) is set to indicate the configuration mismatch Reset. Refer to **Section 11.0 "I/O Ports"** for more information on the configuration mismatch Reset.

Note: The configuration mismatch feature and associated reset flag is not available on all devices.

### 6.10 Illegal Condition Device Reset

An illegal condition device Reset occurs due to the following sources:

- Illegal Opcode Reset

- Uninitialized W Register Reset

- · Security Reset

The Illegal Opcode or Uninitialized W Access Reset Flag bit (IOPUWR) in the Reset Control register (RCON<14>) is set to indicate the illegal condition device Reset.

#### 6.10.1 ILLEGAL OPCODE RESET

A device Reset is generated if the device attempts to execute an illegal opcode value that is fetched from program memory.

The illegal opcode Reset function can prevent the device from executing program memory sections that are used to store constant data. To take advantage of the illegal opcode Reset, use only the lower 16 bits of

each program memory section to store the data values. The upper 8 bits should be programmed with 3Fh, which is an illegal opcode value.

#### 6.10.2 UNINITIALIZED W REGISTER RESET

Any attempts to use the uninitialized W register as an address pointer will Reset the device. The W register array (with the exception of W15) is cleared during all resets and is considered uninitialized until written to.

#### 6.10.3 SECURITY RESET

If a Program Flow Change (PFC) or Vector Flow Change (VFC) targets a restricted location in a protected segment (Boot and Secure Segment), that operation will cause a security Reset.

The PFC occurs when the Program Counter is reloaded as a result of a Call, Jump, Computed Jump, Return, Return from Subroutine, or other form of branch instruction.

The VFC occurs when the Program Counter is reloaded with an Interrupt or Trap vector.

Refer to Section 25.8 "Code Protection and CodeGuard™ Security" for more information on Security Reset.

## 6.11 Using the RCON Status Bits

The user application can read the Reset Control register (RCON) after any device Reset to determine the cause of the reset.

**Note:** The status bits in the RCON register should be cleared after they are read so that the next RCON register value after a device Reset will be meaningful.

Table 6-3 provides a summary of the reset flag bit operation.

| Flag Bit         | Set by:                                                                | Cleared by:                                         |

|------------------|------------------------------------------------------------------------|-----------------------------------------------------|

| TRAPR (RCON<15>) | Trap conflict event                                                    | POR, BOR                                            |

| IOPWR (RCON<14>) | Illegal opcode or uninitialized<br>W register access or Security Reset | POR, BOR                                            |

| CM (RCON<9>)     | Configuration Mismatch                                                 | POR, BOR                                            |

| EXTR (RCON<7>)   | MCLR Reset                                                             | POR                                                 |

| SWR (RCON<6>)    | RESET instruction                                                      | POR, BOR                                            |

| WDTO (RCON<4>)   | WDT time-out                                                           | PWRSAV instruction,<br>CLRWDT instruction, POR, BOR |

| SLEEP (RCON<3>)  | PWRSAV #SLEEP instruction                                              | POR, BOR                                            |

| IDLE (RCON<2>)   | PWRSAV #IDLE instruction                                               | POR, BOR                                            |

| BOR (RCON<1>)    | POR, BOR                                                               | —                                                   |

| POR (RCON<0>)    | POR                                                                    | —                                                   |

TABLE 6-3: RESET FLAG BIT OPERATION

**Note:** All Reset flag bits can be set or cleared by user software.

| U-0          | U-0               | U-0                 | U-0             | U-0               | R/W-1             | R/W-0           | R/W-0 |

|--------------|-------------------|---------------------|-----------------|-------------------|-------------------|-----------------|-------|

| 0-0          | 0-0               | 0-0                 | 0-0             | 0-0               | R/W-I             |                 | R/W-0 |

|              | —                 | _                   |                 | _                 |                   | DMA1IP<2:0>     |       |

| bit 15       |                   |                     |                 |                   |                   |                 | bit   |

| U-0          | R/W-1             | R/W-0               | R/W-0           | U-0               | R/W-1             | R/W-0           | R/W-0 |

| _            |                   | AD1IP<2:0>          |                 | _                 |                   | U1TXIP<2:0>     |       |

| bit 7        |                   |                     |                 |                   | •                 |                 | bit   |

| Legend:      |                   |                     |                 |                   |                   |                 |       |

| R = Readab   | ole bit           | W = Writable        | bit             | U = Unimpler      | mented bit, rea   | d as '0'        |       |

| -n = Value a | at POR            | '1' = Bit is set    |                 | '0' = Bit is cle  | ared              | x = Bit is unkr | iown  |

|              |                   |                     |                 |                   |                   |                 |       |

| bit 15-11    | Unimpleme         | ented: Read as '    | 0'              |                   |                   |                 |       |

| bit 10-8     | DMA1IP<2:         | 0>: DMA Chann       | el 1 Data Tra   | nsfer Complete    | e Interrupt Prior | ity bits        |       |

|              | 111 = Interr      | upt is priority 7 ( | highest priorit | ty interrupt)     |                   |                 |       |

|              | •                 |                     |                 |                   |                   |                 |       |

|              | •                 |                     |                 |                   |                   |                 |       |

|              | 001 = Interr      | upt is priority 1   |                 |                   |                   |                 |       |

|              |                   | upt source is dis   | abled           |                   |                   |                 |       |

| bit 7        | Unimpleme         | nted: Read as '     | 0'              |                   |                   |                 |       |

| bit 6-4      | AD1IP<2:0>        | -: ADC1 Conver      | sion Complet    | e Interrupt Prio  | rity bits         |                 |       |

|              |                   | upt is priority 7 ( | •               | •                 | 2                 |                 |       |

|              | •                 |                     |                 |                   |                   |                 |       |

|              | •                 |                     |                 |                   |                   |                 |       |

|              | •<br>001 = Interr | upt is priority 1   |                 |                   |                   |                 |       |

|              |                   | upt source is dis   | abled           |                   |                   |                 |       |

| bit 3        |                   | nted: Read as '     |                 |                   |                   |                 |       |

| bit 2-0      | -                 | )>: UART1 Trans     |                 | upt Priority bits |                   |                 |       |

|              |                   | upt is priority 7 ( |                 |                   |                   |                 |       |

|              | •                 |                     | 5               | ,                 |                   |                 |       |

|              | •                 |                     |                 |                   |                   |                 |       |

|              | •                 |                     |                 |                   |                   |                 |       |

|              | 001 = Interr      | upt is priority 1   |                 |                   |                   |                 |       |

#### PRIORITY CONTROL REGISTER

001 = Interrupt is priority 1 000 = Interrupt source is disabled

| REGISTER 8-2: DMAxREQ: DMA CHANNEL x IRQ SELECT REGIST |

|--------------------------------------------------------|

|--------------------------------------------------------|

| -                    |       |                                 |       |                  |                  |                 |       |

|----------------------|-------|---------------------------------|-------|------------------|------------------|-----------------|-------|

| R/W-0                | U-0   | U-0                             | U-0   | U-0              | U-0              | U-0             | U-0   |

| FORCE <sup>(1)</sup> | —     | —                               |       | —                |                  |                 | —     |

| bit 15               |       |                                 |       |                  |                  |                 | bit 8 |

|                      |       |                                 |       |                  |                  |                 |       |

| U-0                  | R/W-0 | R/W-0                           | R/W-0 | U-0              | U-0              | R/W-0           | R/W-0 |

|                      |       |                                 |       | IRQSEL<6:0>      | (2)              |                 |       |

| bit 7                | •     |                                 |       |                  |                  |                 | bit 0 |

|                      |       |                                 |       |                  |                  |                 |       |

| Legend:              |       |                                 |       |                  |                  |                 |       |

| R = Readable         | bit   | W = Writable I                  | bit   | U = Unimpler     | mented bit, read | as '0'          |       |

| -n = Value at P      | OR    | '1' = Bit is set                |       | '0' = Bit is cle | ared             | x = Bit is unkr | nown  |

|                      |       |                                 |       |                  |                  |                 |       |

| bit 15               |       | e DMA Transfe                   |       |                  |                  |                 |       |

|                      |       | ingle DMA trans<br>DMA transfer |       |                  |                  |                 |       |

bit 14-7 Unimplemented: Read as '0'

## bit 6-0 IRQSEL<6:0>: DMA Peripheral IRQ Number Select bits<sup>(2)</sup>

0000000-1111111 = DMAIRQ0-DMAIRQ127 selected to be Channel DMAREQ

**Note 1:** The FORCE bit cannot be cleared by the user. The FORCE bit is cleared by hardware when the forced DMA transfer is complete.

2: Refer to Table 7-1 for a complete listing of IRQ numbers for all interrupt sources.

NOTES:

NOTES:

| U-0                 | U-0                                               | U-0                                | R/W-0           | R/W-0             | R/W-0                                    | R/W-0           | R/W-0                |

|---------------------|---------------------------------------------------|------------------------------------|-----------------|-------------------|------------------------------------------|-----------------|----------------------|

| _                   | _                                                 | _                                  | DISSCK          | DISSDO            | MODE16                                   | SMP             | CKE <sup>(1)</sup>   |

| bit 15              |                                                   |                                    |                 |                   |                                          |                 | bit                  |

|                     |                                                   |                                    |                 |                   |                                          |                 |                      |

| R/W-0               | R/W-0                                             | R/W-0                              | R/W-0           | R/W-0             | R/W-0                                    | R/W-0           | R/W-0                |

| SSEN <sup>(3)</sup> | CKP                                               | MSTEN                              |                 | SPRE<2:0>(2       | 2)                                       | PPRE-           | <1:0> <sup>(2)</sup> |

| bit 7               |                                                   |                                    |                 |                   |                                          |                 | bit                  |

| Legend:             |                                                   |                                    |                 |                   |                                          |                 |                      |

| R = Readable        | e bit                                             | W = Writable                       | bit             | U = Unimpler      | nented bit, read                         | as '0'          |                      |

| -n = Value at       | POR                                               | '1' = Bit is se                    | t               | '0' = Bit is cle  | ared                                     | x = Bit is unkr | nown                 |

|                     |                                                   |                                    |                 |                   |                                          |                 |                      |

| bit 15-13           | Unimpleme                                         | nted: Read as                      | 0'              |                   |                                          |                 |                      |

| oit 12              |                                                   | sable SCKx pin                     |                 |                   |                                          |                 |                      |

|                     |                                                   | SPI clock is disa                  |                 | tions as I/O      |                                          |                 |                      |

| -:- 11              |                                                   | SPI clock is ena                   |                 |                   |                                          |                 |                      |

| bit 11              |                                                   | sable SDOx pin<br>n is not used by |                 | unctions as I/O   | )                                        |                 |                      |

|                     |                                                   | n is controlled b                  |                 |                   | ,<br>,                                   |                 |                      |

| bit 10              | MODE16: W                                         | /ord/Byte Comn                     | nunication Sele | ect bit           |                                          |                 |                      |

|                     |                                                   | nication is word                   |                 |                   |                                          |                 |                      |

|                     |                                                   | nication is byte-                  |                 |                   |                                          |                 |                      |

| bit 9               |                                                   | Data Input Sam                     | ole Phase bit   |                   |                                          |                 |                      |

|                     | $\frac{\text{Master mode}}{1 = \text{Input dat}}$ | <u>e:</u><br>ta sampled at e       | nd of data outr | out time          |                                          |                 |                      |

|                     |                                                   | ta sampled at m                    |                 |                   |                                          |                 |                      |

|                     | Slave mode:                                       |                                    |                 | -                 |                                          |                 |                      |

|                     |                                                   | e cleared when                     |                 | n Slave mode.     |                                          |                 |                      |

| bit 8               |                                                   | Clock Edge Sele                    |                 | <i>.</i>          |                                          |                 |                      |

|                     |                                                   |                                    |                 |                   | clock state to Idl<br>ock state to activ |                 |                      |

| bit 7               |                                                   | e Select Enable                    |                 |                   |                                          |                 |                      |

|                     |                                                   | used for Slave                     | •               |                   |                                          |                 |                      |

|                     |                                                   | not used by mo                     |                 | rolled by port fu | unction                                  |                 |                      |

| bit 6               | CKP: Clock                                        | Polarity Select                    | bit             |                   |                                          |                 |                      |

|                     |                                                   | e for clock is a h                 |                 |                   |                                          |                 |                      |

|                     |                                                   | e for clock is a l                 |                 | e state is a high | n level                                  |                 |                      |

|                     | MSTEN: Ma                                         | ster Mode Enal                     | ole bit         |                   |                                          |                 |                      |

| bit 5               | 1 = Master n                                      |                                    |                 |                   |                                          |                 |                      |

(FRMEN = 1).

- 2: Do not set both Primary and Secondary prescalers to a value of 1:1.

- 3: This bit must be cleared when FRMEN = 1.

## REGISTER 18-1: UXMODE: UARTX MODE REGISTER (CONTINUED)

| bit 4   | URXINV: Receive Polarity Inversion bit                                                                                                                                             |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | 1 = UxRX Idle state is '0'<br>0 = UxRX Idle state is '1'                                                                                                                           |

| bit 3   | BRGH: High Baud Rate Enable bit                                                                                                                                                    |

|         | <ul> <li>1 = BRG generates 4 clocks per bit period (4x baud clock, High-Speed mode)</li> <li>0 = BRG generates 16 clocks per bit period (16x baud clock, Standard mode)</li> </ul> |

| bit 2-1 | PDSEL<1:0>: Parity and Data Selection bits                                                                                                                                         |

|         | <ul> <li>11 = 9-bit data, no parity</li> <li>10 = 8-bit data, odd parity</li> <li>01 = 8-bit data, even parity</li> <li>00 = 8-bit data, no parity</li> </ul>                      |

| bit 0   | STSEL: Stop Bit Selection bit<br>1 = Two Stop bits<br>0 = One Stop bit                                                                                                             |

|         |                                                                                                                                                                                    |

- **Note 1:** Refer to **Section 17. "UART**" (DS70232) in the *"dsPIC33F/PIC24H Family Reference Manual"* for information on enabling the UART module for receive or transmit operation.

- 2: This feature is only available for the 16x BRG mode (BRGH = 0).

## PIC24HJ32GP302/304, PIC24HJ64GPX02/X04 AND PIC24HJ128GPX02/X04

| U-0                                 | U-0        | U-0            | U-0                                     | U-0              | U-0               | U-0      | U-0   |

|-------------------------------------|------------|----------------|-----------------------------------------|------------------|-------------------|----------|-------|

|                                     |            | _              | —                                       |                  |                   |          |       |

| bit 15                              |            |                |                                         |                  |                   |          | bit 8 |

|                                     |            |                |                                         |                  |                   |          |       |

| U-0                                 | U-0        | U-0            | R-0                                     | R-0              | R-0               | R-0      | R-0   |

|                                     |            |                |                                         |                  | DNCNT<4:0>        |          |       |

| bit 7                               |            |                |                                         |                  |                   |          | bit 0 |

| Legend: C = Writeable bit, but only |            |                |                                         | 0' can be writte | en to clear the b | pit      |       |

| R = Readable bit W = Writable bi    |            |                | bit                                     | U = Unimpler     | nented bit, read  | d as '0' |       |

| -n = Value at POR (1' = Bit is set  |            |                | '0' = Bit is cleared x = Bit is unknown |                  | iown              |          |       |

|                                     |            |                |                                         |                  |                   |          |       |

| bit 15-5                            | Unimplemen | ted: Read as ' | כ'                                      |                  |                   |          |       |

| h:+ 4 0                             | DNONT      |                |                                         | har hita         |                   |          |       |

| bit 4-0 | DNCNT<4:0>: DeviceNet <sup>™</sup> Filter Bit Number bits                                 |

|---------|-------------------------------------------------------------------------------------------|

|         | 10010-11111 = Invalid selection<br>10001 = Compare up to data byte 3, bit 6 with EID<17>  |

|         | •                                                                                         |

|         | •                                                                                         |

|         | •                                                                                         |

|         | 00001 = Compare up to data byte 1, bit 7 with EID<0><br>00000 = Do not compare data bytes |

|                                                                            | n (n =                           | 0-15)                                                  |               |                   |                   |          |       |

|----------------------------------------------------------------------------|----------------------------------|--------------------------------------------------------|---------------|-------------------|-------------------|----------|-------|

| R/W-x                                                                      | R/W-x                            | R/W-x                                                  | R/W-x         | R/W-x             | R/W-x             | R/W-x    | R/W-x |

| SID10                                                                      | SID9                             | SID8                                                   | SID7          | SID6              | SID5              | SID4     | SID3  |

| bit 15                                                                     |                                  |                                                        |               |                   |                   |          | bit 8 |

|                                                                            |                                  |                                                        |               |                   |                   |          |       |

| R/W-x                                                                      | R/W-x                            | R/W-x                                                  | U-0           | R/W-x             | U-0               | R/W-x    | R/W-x |

| SID2                                                                       | SID1                             | SID0                                                   | —             | EXIDE             | —                 | EID17    | EID16 |

| bit 7                                                                      |                                  |                                                        |               |                   |                   |          | bit 0 |

|                                                                            |                                  |                                                        |               |                   |                   |          |       |

| Legend:                                                                    |                                  | C = Writeable                                          | bit, but only | '0' can be writte | en to clear the b | bit      |       |

| R = Readable                                                               | e bit                            | W = Writable                                           | bit           | U = Unimpler      | nented bit, read  | d as '0' |       |

| -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown |                                  |                                                        |               |                   |                   | nown     |       |

| bit 15-5                                                                   | 1 = Message                      | Standard Identif<br>address bit SII<br>address bit SII | Dx must be '1 |                   |                   |          |       |

| bit 4                                                                      | bit 4 Unimplemented: Read as '0' |                                                        |               |                   |                   |          |       |

# REGISTER 19-16: CIRXFnSID: ECAN™ ACCEPTANCE FILTER STANDARD IDENTIFIER REGISTER n (n = 0-15)

| bit 3 <b>EXIDE:</b> Extended Identifier Enable bi |

|---------------------------------------------------|

|                                                   |

If MIDE = 1, then:

1 = Match only messages with extended identifier addresses

0 = Match only messages with standard identifier addresses

$\frac{\text{If MIDE} = 0, \text{ then:}}{\text{Ignore the EXIDE bit.}}$

Unimplemented: Read as '0'

bit 2

bit 1-0 **EID<17:16>:** Extended Identifier bits

1 = Message address bit EIDx must be '1' to match filter

0 = Message address bit EIDx must be '0' to match filter

#### 22.1 RTCC Module Registers

The RTCC module registers are organized into three categories:

- RTCC Control Registers

- RTCC Value Registers

- Alarm Value Registers

#### 22.1.1 REGISTER MAPPING

To limit the register interface, the RTCC Timer and Alarm Time registers are accessed through corresponding register pointers. The RTCC Value register window (RTCVALH and RTCVALL) uses the RTCPTR bits (RCFGCAL<9:8>) to select the desired timer register pair (see Table 22-1).

By writing the RTCVALH byte, the RTCC Pointer value, RTCPTR<1:0> bits, decrement by one until they reach '00'. Once they reach '00', the MINUTES and SECONDS value will be accessible through RTCVALH and RTCVALL until the pointer value is manually changed.

TABLE 22-1: RTCVAL REGISTER MAPPING

| RTCPTR | RTCC Value Register Window |             |  |  |

|--------|----------------------------|-------------|--|--|

| <1:0>  | RTCVAL<15:8>               | RTCVAL<7:0> |  |  |

| 0 0    | MINUTES                    | SECONDS     |  |  |

| 01     | WEEKDAY                    | HOURS       |  |  |

| 10     | MONTH                      | DAY         |  |  |

| 11     | —                          | YEAR        |  |  |

The Alarm Value register window (ALRMVALH and ALRMVALL) uses the ALRMPTR bits (ALCFGRPT<9:8>) to select the desired Alarm register pair (see Table 22-2).

By writing the ALRMVALH byte, the Alarm Pointer value, ALRMPTR<1:0> bits, decrement by one until they reach '00'. Once they reach '00', the ALRMMIN and ALRMSEC value will be accessible through ALRMVALH and ALRMVALL until the pointer value is manually changed.

#### TABLE 22-2: ALRMVAL REGISTER MAPPING

| ALRMPTR | Alarm Value Register Window |              |  |  |

|---------|-----------------------------|--------------|--|--|

| <1:0>   | ALRMVAL<15:8>               | ALRMVAL<7:0> |  |  |

| 00      | ALRMMIN                     | ALRMSEC      |  |  |

| 01      | ALRMWD                      | ALRMHR       |  |  |

| 10      | ALRMMNTH                    | ALRMDAY      |  |  |

| 11      | —                           | —            |  |  |

Considering that the 16-bit core does not distinguish between 8-bit and 16-bit read operations, the user must be aware that when reading either the ALRMVALH or ALRMVALL bytes will decrement the ALRMPTR<1:0> value. The same applies to the RTCVALH or RTCVALL bytes with the RTCPTR<1:0> being decremented.

| Note: | This only applies to read operations and |  |  |  |  |  |  |

|-------|------------------------------------------|--|--|--|--|--|--|

|       | not write operations.                    |  |  |  |  |  |  |

### 22.1.2 WRITE LOCK

In order to perform a write to any of the RTCC Timer registers, the RTCWREN bit (RCFGCAL<13>) must be set (refer to Example 22-1).

Note: To avoid accidental writes to the timer, it is recommended that the RTCWREN bit (RCFGCAL<13>) is kept clear at any other time. For the RTCWREN bit to be set, there is only 1 instruction cycle time window allowed between the 55h/AA sequence and the setting of RTCWREN; therefore, it is recommended that code follow the procedure in Example 22-1.

#### EXAMPLE 22-1: SETTING THE RTCWREN BIT

| MOV  | #NVMKEY, W1  | ;move the address of NVMKEY into W1 |

|------|--------------|-------------------------------------|

| MOV  | #0x55, W2    |                                     |

| MOV  | #0xAA, W3    |                                     |

| MOV  | W2, [W1]     | ;start 55/AA sequence               |

| MOV  | W3, [W1]     |                                     |

| BSET | RCFGCAL, #13 | ;set the RTCWREN bit                |

|      |              |                                     |

## **REGISTER 22-1:** RCFGCAL: RTCC CALIBRATION AND CONFIGURATION REGISTER<sup>(1)</sup> (CONTINUED)

| bit 7-0 | CAL<7:0>: RTC Drift Calibration bits                                                                                                                                          |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | 11111111 = Minimum negative adjustment; subtracts 4 RTC clock pulses every one minute                                                                                         |

|         | •                                                                                                                                                                             |

|         | •                                                                                                                                                                             |

|         | •                                                                                                                                                                             |

|         | 10000000 = Maximum negative adjustment; subtracts 512 RTC clock pulses every one minute<br>01111111 = Maximum positive adjustment; adds 508 RTC clock pulses every one minute |

|         | •                                                                                                                                                                             |

|         | •                                                                                                                                                                             |

|         | •                                                                                                                                                                             |

|         | 00000001 = Minimum positive adjustment; adds 4 RTC clock pulses every one minute<br>00000000 = No adjustment                                                                  |

#### Note 1: The RCFGCAL register is only affected by a POR.

- 2: A write to the RTCEN bit is only allowed when RTCWREN = 1.

- 3: This bit is read-only. It is cleared to '0' on a write to the lower half of the MINSEC register.

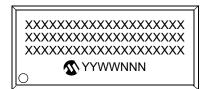

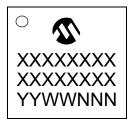

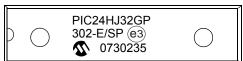

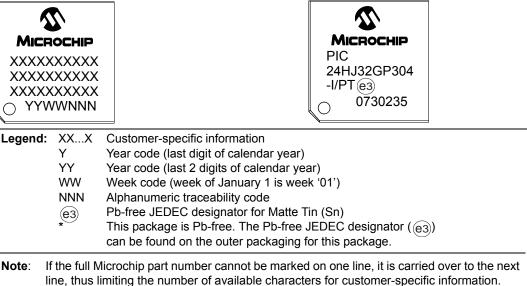

#### 33.0 PACKAGING INFORMATION

28-Lead SPDIP

28-Lead SOIC (.300")

28-Lead QFN-S

44-Lead QFN

44-Lead TQFP

Example

Example

Example

Example

Example

© 2007-2012 Microchip Technology Inc.

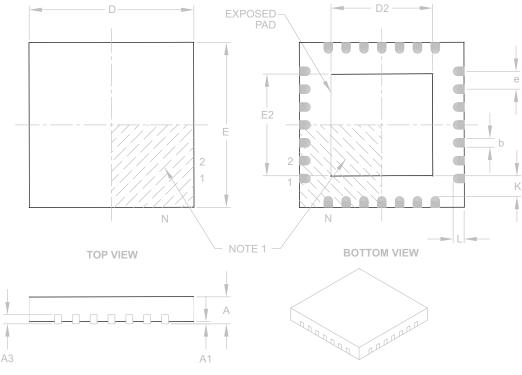

# 28-Lead Plastic Quad Flat, No Lead Package (MM) – 6x6x0.9 mm Body [QFN-S] with 0.40 mm Contact Length

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                        | MILLIMETERS      |                   |      |      |  |

|------------------------|------------------|-------------------|------|------|--|

| Dimensio               | Dimension Limits |                   | NOM  | MAX  |  |

| Number of Pins N       |                  |                   | 28   |      |  |

| Pitch                  | е                | 0.65 BSC          |      |      |  |

| Overall Height         | А                | 0.80              | 0.90 | 1.00 |  |

| Standoff               | A1               | 0.00              | 0.02 | 0.05 |  |

| Contact Thickness      | A3               | 0.20 REF          |      |      |  |

| Overall Width          | E 6.00 BSC       |                   |      |      |  |

| Exposed Pad Width      | E2               | E2 3.65 3.70 4.70 |      | 4.70 |  |

| Overall Length         | D                | 6.00 BSC          |      |      |  |

| Exposed Pad Length     | D2               | 3.65              | 3.70 | 4.70 |  |

| Contact Width          | b                | 0.23              | 0.38 | 0.43 |  |

| Contact Length         | L                | 0.30              | 0.40 | 0.50 |  |

| Contact-to-Exposed Pad |                  | 0.20              | -    | -    |  |

#### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package is saw singulated.

3. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-124B

NOTES: