#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | PIC                                                                             |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 40 MIPs                                                                         |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                    |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                      |

| Number of I/O              | 21                                                                              |

| Program Memory Size        | 128KB (43K x 24)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | ·                                                                               |

| RAM Size                   | 8K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 10x10b/12b                                                                  |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                                  |

| Supplier Device Package    | 28-SOIC                                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24hj128gp502t-i-so |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### TABLE 4-28: PORTA REGISTER MAP FOR PIC24HJ128GP204/504, PIC24HJ64GP204/504 AND PIC24HJ32GP304

| File Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10  | Bit 9  | Bit 8  | Bit 7  | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|-----------|------|--------|--------|--------|--------|--------|---------|--------|--------|--------|-------|-------|--------|--------|--------|--------|--------|---------------|

| TRISA     | 02C0 | _      | _      | _      | _      | _      | TRISA10 | TRISA9 | TRISA8 | TRISA7 | -     | —     | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 079F          |

| PORTA     | 02C2 | _      | _      | _      | _      | _      | RA10    | RA9    | RA8    | RA7    | _     | _     | RA4    | RA3    | RA2    | RA1    | RA0    | XXXX          |

| LATA      | 02C4 | _      | _      | _      | _      | _      | LATA10  | LATA9  | LATA8  | LATA7  | _     | _     | LATA4  | LATA3  | LATA2  | LATA1  | LATA0  | XXXX          |

| ODCA      | 02C6 | —      | —      | —      | —      | _      | ODCA10  | ODCA9  | ODCA8  | ODCA7  | -     | —     | _      | -      | _      | _      | _      | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-29: PORTB REGISTER MAP

| File Name | Addr | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11  | Bit 10  | Bit 9  | Bit 8  | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|-----------|------|---------|---------|---------|---------|---------|---------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|---------------|

| TRISB     | 02C8 | TRISB15 | TRISB14 | TRISB13 | TRISB12 | TRISB11 | TRISB10 | TRISB9 | TRISB8 | TRISB7 | TRISB6 | TRISB5 | TRISB4 | TRISB3 | TRISB2 | TRISB1 | TRISB0 | FFFF          |

| PORTB     | 02CA | RB15    | RB14    | RB13    | RB12    | RB11    | RB10    | RB9    | RB8    | RB7    | RB6    | RB5    | RB4    | RB3    | RB2    | RB1    | RB0    | XXXX          |

| LATB      | 02CC | LATB15  | LATB14  | LATB13  | LATB12  | LATB11  | LATB10  | LATB9  | LATB8  | LATB7  | LATB6  | LATB5  | LATB4  | LATB3  | LATB2  | LATB1  | LATB0  | XXXX          |

| ODCB      | 02CE | _       | —       | -       | —       | ODCB11  | ODCB10  | ODCB9  | ODCB8  | ODCB7  | ODCB6  | ODCB5  | —      | _      | -      | —      | —      | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-30: PORTC REGISTER MAP FOR PIC24HJ128GP204/504, PIC24HJ64GP204/504 AND PIC24HJ32GP304

| File Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|-----------|------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|---------------|

| TRISC     | 02D0 | —      | _      | —      | _      | —      | —      | TRISC9 | TRISC8 | TRISC7 | TRISC6 | TRISC5 | TRISC4 | TRISC3 | TRISC2 | TRISC1 | TRISC0 | 03FF          |

| PORTC     | 02D2 | _      | _      | _      | _      | _      | _      | RC9    | RC8    | RC7    | RC6    | RC5    | RC4    | RC3    | RC2    | RC1    | RC0    | XXXX          |

| LATC      | 02D4 | _      | _      | _      | _      | _      | _      | LATC9  | LATC8  | LATC7  | LATC6  | LATC5  | LATC4  | LATC3  | LATC2  | LATC1  | LATC0  | XXXX          |

| ODCC      | 02D6 | _      | _      | _      | _      | _      | _      | ODCC9  | ODCC8  | ODCC7  | ODCC6  | ODCC5  | ODCC4  | ODCC3  | _      | _      | _      | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-31: SYSTEM CONTROL REGISTER MAP

| File Name | Addr | Bit 15 | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9     | Bit 8 | Bit 7   | Bit 6   | Bit 5  | Bit 4    | Bit 3 | Bit 2    | Bit 1   | Bit 0 | All<br>Resets       |

|-----------|------|--------|--------|---------|--------|--------|--------|-----------|-------|---------|---------|--------|----------|-------|----------|---------|-------|---------------------|

| RCON      | 0740 | TRAPR  | IOPUWR | _       | _      | _      |        | CM        | VREGS | EXTR    | SWR     | SWDTEN | WDTO     | SLEEP | IDLE     | BOR     | POR   | <sub>XXXX</sub> (1) |

| OSCCON    | 0742 | —      |        | COSC<2  | 0>     | —      | N      | OSC<2:0>  |       | CLKLOCK | IOLOCK  | LOCK   | _        | CF    | _        | LPOSCEN | OSWEN | 0300 <b>(2)</b>     |

| CLKDIV    | 0744 | ROI    |        | DOZE<2: | 0>     | DOZEN  | FR     | RCDIV<2:0 | >     | PLLPOS  | ST<1:0> | _      |          | F     | PLLPRE<4 | 4:0>    |       | 3040                |

| PLLFBD    | 0746 | _      | _      | _       | _      | _      | _      | _         |       |         |         | P      | LDIV<8:0 | >     |          |         |       | 0030                |

| OSCTUN    | 0748 | _      | —      | _       | _      | _      | -      | _         | _     | _       | -       |        |          | TUN   | <5:0>    |         |       | 0000                |

Legend: x = unknown value on Reset, -- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: RCON register Reset values dependent on type of Reset.

2: OSCCON register Reset values dependent on the FOSC Configuration bits and by type of Reset.

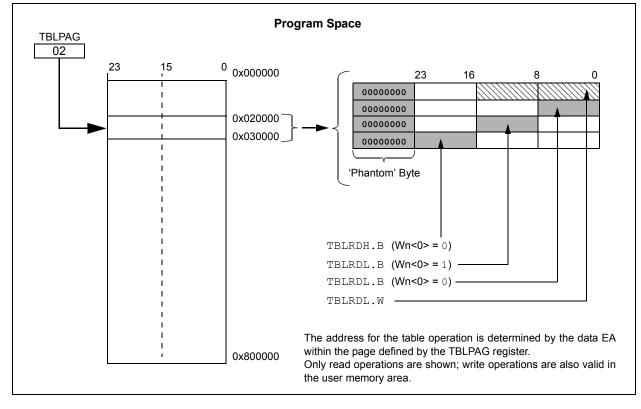

#### 4.6.2 DATA ACCESS FROM PROGRAM MEMORY USING TABLE INSTRUCTIONS

The TBLRDL and TBLWTL instructions offer a direct method of reading or writing the lower word of any address within the program space without going through data space. The TBLRDH and TBLWTH instructions are the only method to read or write the upper 8 bits of a program space word as data.

The PC is incremented by two for each successive 24-bit program word. This allows program memory addresses to directly map to data space addresses. Program memory can thus be regarded as two 16-bit wide word address spaces, residing side by side, each with the same address range. TBLRDL and TBLWTL access the space that contains the least significant data word. TBLRDH and TBLWTH access the space that contains the upper data byte.

Two table instructions are provided to move byte or word-sized (16-bit) data to and from program space. Both function as either byte or word operations.

- TBLRDL (Table Read Low):

- In Word mode, this instruction maps the lower word of the program space location (P<15:0>) to a data address (D<15:0>).

- In Byte mode, either the upper or lower byte of the lower program word is mapped to the lower byte of a data address. The upper byte is selected when Byte Select is '1'; the lower byte is selected when it is '0'.

- TBLRDH (Table Read High):

- In Word mode, this instruction maps the entire upper word of a program address (P<23:16>) to a data address. The 'phantom' byte (D<15:8>), is always '0'.

- In Byte mode, this instruction maps the upper or lower byte of the program word to D<7:0> of the data address, in the TBLRDL instruction. The data is always '0' when the upper 'phantom' byte is selected (Byte Select = 1).

Similarly, two table instructions, TBLWTH and TBLWTL, are used to write individual bytes or words to a program space address. The details of their operation are explained in Section 5.0 "Flash Program Memory".

For all table operations, the area of program memory space to be accessed is determined by the Table Page register (TBLPAG). TBLPAG covers the entire program memory space of the device, including user application and configuration spaces. When TBLPAG<7> = 0, the table page is located in the user memory space. When TBLPAG<7> = 1, the page is located in configuration space.

### FIGURE 4-7: ACCESSING PROGRAM MEMORY WITH TABLE INSTRUCTIONS

|                  |                   | · · /             |                               |

|------------------|-------------------|-------------------|-------------------------------|

| Vector<br>Number | IVT Address       | AIVT Address      | Interrupt Source              |

| 55-68            | 0x000072-0x00008C | 0x000172-0x00018C | Reserved                      |

| 69               | 0x00008E          | 0x00018E          | DMA5 – DMA Channel 5          |

| 70               | 0x000090          | 0x000190          | RTCC – Real Time Clock        |

| 71-72            | 0x000092-0x000094 | 0x000192-0x000194 | Reserved                      |

| 73               | 0x000096          | 0x000196          | U1E – UART1 Error             |

| 74               | 0x000098          | 0x000198          | U2E – UART2 Error             |

| 75               | 0x00009A          | 0x00019A          | CRC – CRC Generator Interrupt |

| 76               | 0x00009C          | 0x00019C          | DMA6 – DMA Channel 6          |

| 77               | 0x00009E          | 0x00019E          | DMA7 – DMA Channel 7          |

| 78               | 0x0000A0          | 0x0001A0          | C1TX – ECAN1 TX Data Request  |

| 79-126           | 0x0000A2-0x0000FE | 0x0001A2-0x0001FE | Reserved                      |

### TABLE 7-1: INTERRUPT VECTORS (CONTINUED)

| U-0          | R/W-1                | R/W-0                                  | R/W-0          | U-0              | R/W-1            | R/W-0           | R/W-0 |

|--------------|----------------------|----------------------------------------|----------------|------------------|------------------|-----------------|-------|

| —            |                      | T4IP<2:0>                              |                | —                |                  | OC4IP<2:0>      |       |

| bit 15       |                      |                                        |                |                  |                  |                 | bit 8 |

| U-0          | R/W-1                | R/W-0                                  | R/W-0          | U-0              | R/W-1            | R/W-0           | R/W-0 |

| _            |                      | OC3IP<2:0>                             |                | —                |                  | DMA2IP<2:0>     |       |

| bit 7        |                      |                                        |                |                  |                  |                 | bit 0 |

| Legend:      |                      |                                        |                |                  |                  |                 |       |

| R = Readab   | le bit               | W = Writable                           | bit            | U = Unimple      | mented bit, rea  | ad as '0'       |       |

| -n = Value a | t POR                | '1' = Bit is set                       |                | '0' = Bit is cle | eared            | x = Bit is unkn | own   |

| bit 15       | Unimpleme            | nted: Read as '                        | )'             |                  |                  |                 |       |

| bit 14-12    | T4IP<2:0>:           | Fimer4 Interrupt                       | Priority bits  |                  |                  |                 |       |

|              | 111 <b>= Interru</b> | upt is priority 7 (I                   | highest priori | y interrupt)     |                  |                 |       |

|              | •                    |                                        |                |                  |                  |                 |       |

|              | •                    |                                        |                |                  |                  |                 |       |

|              |                      | upt is priority 1                      |                |                  |                  |                 |       |

|              |                      | upt source is dis                      |                |                  |                  |                 |       |

| bit 11       | -                    | nted: Read as '                        |                |                  |                  |                 |       |

| bit 10-8     |                      | : Output Compa                         |                | -                | rity bits        |                 |       |

|              | 111 = Interru        | upt is priority 7 (I                   | highest priori | y interrupt)     |                  |                 |       |

|              | •                    |                                        |                |                  |                  |                 |       |

|              | •                    |                                        |                |                  |                  |                 |       |

|              |                      | upt is priority 1<br>upt source is dis | ablad          |                  |                  |                 |       |

| bit 7        |                      | nted: Read as '                        |                |                  |                  |                 |       |

| bit 6-4      | -                    | : Output Compa                         |                | Interrunt Prio   | rity bits        |                 |       |

|              |                      | upt is priority 7 (I                   |                | -                |                  |                 |       |

|              | •                    |                                        | 5 1            | , ,              |                  |                 |       |

|              | •                    |                                        |                |                  |                  |                 |       |

|              |                      | upt is priority 1<br>upt source is dis | abled          |                  |                  |                 |       |

| bit 3        |                      | •<br>nted: Read as '(                  |                |                  |                  |                 |       |

| bit 2-0      | -                    | >: DMA Chann                           |                | nsfer Complete   | e Interrupt Prio | rity bits       |       |

|              |                      | upt is priority 7 (I                   |                | -                | ·                | -               |       |

|              | •                    |                                        |                |                  |                  |                 |       |

|              | •                    |                                        |                |                  |                  |                 |       |

|              | 001 = Interru        | pt is priority 1                       |                |                  |                  |                 |       |

|              | 000 = Interri        | pt source is dis                       | ahlad          |                  |                  |                 |       |

| U-0          | R/W-1        | R/W-0                                     | R/W-0          | U-0                    | R/W-1                       | R/W-0           | R/W-0 |

|--------------|--------------|-------------------------------------------|----------------|------------------------|-----------------------------|-----------------|-------|

| _            |              | C1IP<2:0> <sup>(1)</sup>                  |                | _                      |                             | C1RXIP<2:0>(1)  |       |

| bit 15       | •            |                                           |                |                        |                             |                 | bit 8 |

|              |              |                                           |                |                        |                             |                 |       |

| U-0          | R/W-1        | R/W-0                                     | R/W-0          | U-0                    | R/W-1                       | R/W-0           | R/W-0 |

| —            |              | SPI2IP<2:0>                               |                | _                      |                             | SPI2EIP<2:0>    |       |

| bit 7        |              |                                           |                |                        |                             |                 | bit C |

| Legend:      |              |                                           |                |                        |                             |                 |       |

| R = Readab   | le bit       | W = Writable b                            | oit            | U = Unimple            | mented bit, re              | ead as '0'      |       |

| -n = Value a | t POR        | '1' = Bit is set                          |                | '0' = Bit is cle       |                             | x = Bit is unkn | own   |

|              |              |                                           |                |                        |                             |                 |       |

| bit 15       | Unimpleme    | ented: Read as '0                         | ,              |                        |                             |                 |       |

| bit 14-12    | C1IP<2:0>:   | ECAN1 Event In                            | terrupt Priori | ty bits <sup>(1)</sup> |                             |                 |       |

|              | 111 = Interr | rupt is priority 7 (h                     | nighest priori | ty interrupt)          |                             |                 |       |

|              | •            |                                           |                |                        |                             |                 |       |

|              | •            |                                           |                |                        |                             |                 |       |

|              |              | rupt is priority 1                        |                |                        |                             |                 |       |

|              |              | rupt source is disa                       |                |                        |                             |                 |       |

| bit 11       |              | ented: Read as '0                         |                |                        |                             |                 |       |

| bit 10-8     |              | 0>: ECAN1 Rece                            |                |                        | riority bits <sup>(1)</sup> |                 |       |

|              | 111 = Interr | rupt is priority 7 (h                     | highest priori | ty interrupt)          |                             |                 |       |

|              | •            |                                           |                |                        |                             |                 |       |

|              | •            |                                           |                |                        |                             |                 |       |

|              |              | rupt is priority 1                        |                |                        |                             |                 |       |

| h:+ 7        |              | rupt source is disa                       |                |                        |                             |                 |       |

| bit 7        | -            | ented: Read as '0                         |                | . hite                 |                             |                 |       |

| bit 6-4      |              | SPI2 Event Int<br>rupt is priority 7 (h   | -              | -                      |                             |                 |       |

|              | •            |                                           | lighest phon   | ly interrupt)          |                             |                 |       |

|              | •            |                                           |                |                        |                             |                 |       |

|              | •            | unt in priority 1                         |                |                        |                             |                 |       |

|              |              | rupt is priority 1<br>rupt source is disa | abled          |                        |                             |                 |       |

| bit 3        |              | ented: Read as '0                         |                |                        |                             |                 |       |

| bit 2-0      | -            | :0>: SPI2 Error In                        |                | tv bits                |                             |                 |       |

|              |              | rupt is priority 7 (h                     |                | •                      |                             |                 |       |

|              | •            |                                           | -              |                        |                             |                 |       |

|              | •            |                                           |                |                        |                             |                 |       |

|              | 001 = Interr | rupt is priority 1                        |                |                        |                             |                 |       |

|              |              | rupt io priority i<br>rupt course is die  |                |                        |                             |                 |       |

## 000 = Interrupt source is disabled

Note 1: Interrupts disabled on devices without ECAN<sup>™</sup> modules.

| U-0           | R/W-1         | R/W-0                                  | R/W-0           | U-0              | R/W-1            | R/W-0           | R/W-0 |

|---------------|---------------|----------------------------------------|-----------------|------------------|------------------|-----------------|-------|

| _             |               | CRCIP<2:0>                             |                 | _                |                  | U2EIP<2:0>      |       |

| bit 15        |               |                                        |                 |                  |                  |                 | bit 8 |

|               |               |                                        |                 |                  |                  |                 |       |

| U-0           | R/W-1         | R/W-0                                  | R/W-0           | U-0              | U-0              | U-0             | U-0   |

|               |               | U1EIP<2:0>                             |                 |                  |                  |                 |       |

| bit 7         |               |                                        |                 |                  |                  |                 | bit   |

| Legend:       |               |                                        |                 |                  |                  |                 |       |

| R = Readabl   | e bit         | W = Writable                           | bit             | U = Unimple      | mented bit, read | d as '0'        |       |

| -n = Value at | POR           | '1' = Bit is set                       |                 | '0' = Bit is cle | eared            | x = Bit is unkr | nown  |

|               |               |                                        |                 |                  |                  |                 |       |

| bit 15        | -             | nted: Read as '                        |                 |                  |                  |                 |       |

| bit 14-12     |               | CRC Generate                           |                 |                  | ty bits          |                 |       |

|               | 111 = Interro | upt is priority 7 (                    | highest priorit | ty interrupt)    |                  |                 |       |

|               | •             |                                        |                 |                  |                  |                 |       |

|               | •             |                                        |                 |                  |                  |                 |       |

|               |               | upt is priority 1<br>upt source is dis | abled           |                  |                  |                 |       |

| bit 11        |               | nted: Read as '                        |                 |                  |                  |                 |       |

| bit 10-8      | -             | : UART2 Error I                        |                 | ity bite         |                  |                 |       |

| DIL 10-0      |               | upt is priority 7 (                    |                 | •                |                  |                 |       |

|               | •             |                                        | nightest phone  | ly interrupt)    |                  |                 |       |

|               | •             |                                        |                 |                  |                  |                 |       |

|               | •             |                                        |                 |                  |                  |                 |       |

|               |               | upt is priority 1<br>upt source is dis | abled           |                  |                  |                 |       |

| bit 7         |               | nted: Read as '                        |                 |                  |                  |                 |       |

| bit 6-4       | -             | UART1 Error I                          |                 | itv bits         |                  |                 |       |

|               |               | upt is priority 7 (                    | -               | -                |                  |                 |       |

|               | •             | · · · · · · · · · · · · · · ·          | 5               | - <b>J</b>       |                  |                 |       |

|               | •             |                                        |                 |                  |                  |                 |       |

|               |               |                                        |                 |                  |                  |                 |       |

|               | •             | upt is priority 1                      |                 |                  |                  |                 |       |

bit 3-0 Unimplemented: Read as '0'

## **10.0 POWER-SAVING FEATURES**

- **Note 1:** This data sheet summarizes the features the PIC24HJ32GP302/304. of PIC24HJ64GPX02/X04 and of PIC24HJ128GPX02/X04 families devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet. refer to Section 9. "Watchdog Timer and Power-Saving Modes" (DS70196) of the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The PIC24HJ32GP302/304, PIC24HJ64GPX02/X04 and PIC24HJ128GPX02/X04 devices provide the ability to manage power consumption by selectively managing clocking to the CPU and the peripherals. In general, a lower clock frequency and a reduction in the number of circuits being clocked constitutes lower consumed power. PIC24HJ32GP302/304, PIC24HJ64GPX02/X04 and PIC24HJ128GPX02/X04 devices can manage power consumption in four ways:

- Clock frequency

- Instruction-based Sleep and Idle modes

- Software-controlled Doze mode

- Selective peripheral control in software

Combinations of these methods can be used to selectively tailor an application's power consumption while still maintaining critical application features, such as timing-sensitive communications.

## 10.1 Clock Frequency and Clock Switching

PIC24HJ32GP302/304, PIC24HJ64GPX02/X04 and PIC24HJ128GPX02/X04 devices allow a wide range of clock frequencies to be selected under application control. If the system clock configuration is not locked, users can choose low-power or high-precision oscillators by simply changing the NOSC bits (OSCCON<10:8>). The process of changing a system clock during operation, as well as limitations to the process, are discussed in more detail in Section 9.0 "Oscillator Configuration".

### 10.2 Instruction-Based Power-Saving Modes

PIC24HJ32GP302/304, PIC24HJ64GPX02/X04 and PIC24HJ128GPX02/X04 devices have two special power-saving modes that are entered through the execution of a special PWRSAV instruction. Sleep mode stops clock operation and halts all code execution. Idle mode halts the CPU and code execution, but allows peripheral modules to continue operation. The assembler syntax of the PWRSAV instruction is shown in Example 10-1.

Note: SLEEP\_MODE and IDLE\_MODE are constants defined in the assembler include file for the selected device.

Sleep and Idle modes can be exited as a result of an enabled interrupt, WDT time-out or a device Reset. When the device exits these modes, it is said to wake up.

## 10.2.1 SLEEP MODE

The following occur in Sleep mode:

- The system clock source is shut down. If an on-chip oscillator is used, it is turned off.

- The device current consumption is reduced to a minimum, provided that no I/O pin is sourcing current.

- The Fail-Safe Clock Monitor does not operate, since the system clock source is disabled.

- The LPRC clock continues to run in Sleep mode if the WDT is enabled.

- The WDT, if enabled, is automatically cleared prior to entering Sleep mode.

- Some device features or peripherals can continue to operate. This includes items such as the input change notification on the I/O ports, or peripherals that use an external clock input.

- Any peripheral that requires the system clock source for its operation is disabled.

The device wakes up from Sleep mode on any of the these events:

- · Any interrupt source that is individually enabled

- Any form of device Reset

- A WDT time-out

On wake-up from Sleep mode, the processor restarts with the same clock source that was active when Sleep mode was entered.

#### EXAMPLE 10-1: PWRSAV INSTRUCTION SYNTAX

PWRSAV #SLEEP\_MODE ; Put the device into SLEEP mode

PWRSAV #IDLE\_MODE ; Put the device into IDLE mode

#### 11.6.3 CONTROLLING CONFIGURATION CHANGES

Because peripheral remapping can be changed during run time, some restrictions on peripheral remapping are needed to prevent accidental configuration changes. PIC24H devices include three features to prevent alterations to the peripheral map:

- Control register lock sequence

- · Continuous state monitoring

- Configuration bit pin select lock

#### 11.6.3.1 Control Register Lock

Under normal operation, writes to the RPINRx and RPORx registers are not allowed. Attempted writes appear to execute normally, but the contents of the registers remain unchanged. To change these registers, they must be unlocked in hardware. The register lock is controlled by the IOLOCK bit (OSCCON<6>). Setting IOLOCK prevents writes to the control registers; clearing IOLOCK allows writes.

To set or clear IOLOCK, a specific command sequence must be executed:

- 1. Write 0x46 to OSCCON<7:0>.

- 2. Write 0x57 to OSCCON<7:0>.

- 3. Clear (or set) the IOLOCK bit as a single operation.

| Note: | MPLAB <sup>®</sup> C30 provides built-in C language functions for unlocking the OSCCON register: |

|-------|--------------------------------------------------------------------------------------------------|

|       | builtin_write_OSCCONL(value)<br>builtin_write_OSCCONH(value)                                     |

|       | See MPLAB Help for more information.                                                             |

Unlike the similar sequence with the oscillator's LOCK bit, IOLOCK remains in one state until changed. This allows all of the peripheral pin selects to be configured with a single unlock sequence followed by an update to all control registers, then locked with a second lock sequence.

#### 11.6.3.2 Continuous State Monitoring

In addition to being protected from direct writes, the contents of the RPINRx and RPORx registers are constantly monitored in hardware by shadow registers. If an unexpected change in any of the registers occurs (such as cell disturbances caused by ESD or other external events), a configuration mismatch Reset is triggered.

#### 11.6.3.3 Configuration Bit Pin Select Lock

As an additional level of safety, the device can be configured to prevent more than one write session to the RPINRx and RPORx registers. The IOL1WAY Configuration bit (FOSC<5>) blocks the IOLOCK bit from being cleared after it has been set once. If IOLOCK remains set, the register unlock procedure does not execute, and the peripheral pin select control registers cannot be written to. The only way to clear the bit and re-enable peripheral remapping is to perform a device Reset.

In the default (unprogrammed) state, IOL1WAY is set, restricting users to one write session. Programming IOL1WAY allows user applications unlimited access (with the proper use of the unlock sequence) to the peripheral pin select registers.

| REGISTER     | 11-3: RPIN            | R3: PERIPHE                               | RAL PIN SI | ELECT INPU       | T REGISTER      | 83              |       |

|--------------|-----------------------|-------------------------------------------|------------|------------------|-----------------|-----------------|-------|

| U-0          | U-0                   | U-0                                       | R/W-1      | R/W-1            | R/W-1           | R/W-1           | R/W-1 |

| _            | _                     | _                                         |            |                  | T3CKR<4:0       | )>              |       |

| bit 15       | ·                     | ·                                         | •          |                  |                 |                 | bit 8 |

| U-0          | U-0                   | U-0                                       | R/W-1      | R/W-1            | R/W-1           | R/W-1           | R/W-1 |

| _            | —                     | —                                         |            |                  | T2CKR<4:0       | )>              |       |

| bit 7        | ·                     | ·                                         |            |                  |                 |                 | bit ( |

| Legend:      |                       |                                           |            |                  |                 |                 |       |

| R = Readab   | le bit                | W = Writable                              | bit        | U = Unimple      | mented bit, rea | ad as '0'       |       |

| -n = Value a | t POR                 | '1' = Bit is set                          |            | '0' = Bit is cle | eared           | x = Bit is unki | nown  |

|              | •<br>•<br>00001 = Inp | but tied to RP25                          |            |                  |                 |                 |       |

| bit 7-5      | •                     | out tied to RP0<br><b>nted:</b> Read as ' | n <b>'</b> |                  |                 |                 |       |

| bit 4-0      | •                     | >: Assign Timer                           |            | ock (T2CK) to t  | the correspond  | lina RPn nin    |       |

| 511 4-0      | 11111 <b>= Inp</b>    | out tied to Vss<br>out tied to RP25       |            |                  |                 |                 |       |

|              | •                     |                                           |            |                  |                 |                 |       |

|              | •                     |                                           |            |                  |                 |                 |       |

|              | •                     | ut find to DD1                            |            |                  |                 |                 |       |

|              |                       | but tied to RP1                           |            |                  |                 |                 |       |

00000 = Input tied to RP0

## 12.1 Timer Resources

Many useful resources related to Timers are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the |

|-------|---------------------------------------------|

|       | product page using the link above, enter    |

|       | this URL in your browser:                   |

|       | http://www.microchip.com/wwwproducts/       |

|       | Devices.aspx?dDocName=en532315              |

#### 12.1.1 KEY RESOURCES

- Section 11. "Timers" (DS70205)

- · Code Samples

- Application Notes

- Software Libraries

- Webinars

- All related dsPIC33F/PIC24H Family Reference Manuals Sections

- Development Tools

# PIC24HJ32GP302/304, PIC24HJ64GPX02/X04 AND PIC24HJ128GPX02/X04

| U-0          | U-0                                                        | R-0                                                                          | R-0           | R-0              | R-0    | R-0             | R-0   |

|--------------|------------------------------------------------------------|------------------------------------------------------------------------------|---------------|------------------|--------|-----------------|-------|

|              |                                                            |                                                                              |               | FBF              | P<5:0> |                 |       |

| bit 15       |                                                            |                                                                              |               |                  |        |                 | bit 8 |

| U-0          | U-0                                                        | R-0                                                                          | R-0           | R-0              | R-0    | R-0             | R-0   |

| _            |                                                            |                                                                              |               |                  | B<5:0> |                 |       |

| bit 7        |                                                            |                                                                              |               |                  |        |                 | bit ( |

|              |                                                            |                                                                              |               |                  |        |                 |       |

| Legend:      |                                                            |                                                                              | -             | ' can be writter |        |                 |       |

| R = Readab   |                                                            | W = Writable                                                                 |               | U = Unimpler     |        | ad as '0'       |       |

| -n = Value a | t POR                                                      | '1' = Bit is set                                                             |               | '0' = Bit is cle | ared   | x = Bit is unkr | nown  |

| bit 7-6      | •<br>•<br>•<br>000001 = 7<br>000000 = 7                    | RB30 buffer<br>IRB1 buffer<br>IRB0 buffer<br>ented: Read as '0               | ۰ <b>،</b>    |                  |        |                 |       |

| bit 5-0      | -                                                          | FIFO Next Read                                                               |               | ter hits         |        |                 |       |

| dit 5-0      | 011111 = F<br>011110 = F<br>•<br>•<br>•<br>•<br>000001 = T | >: FIFO Next Rea<br>RB31 buffer<br>RB30 buffer<br>IRB1 buffer<br>IRB1 buffer | id Buπer Poin | ter dits         |        |                 |       |

## REGISTER 20-1: AD1CON1: ADC1 CONTROL REGISTER 1 (CONTINUED)

| bit 3 | <b>SIMSAM:</b> Simultaneous Sample Select bit (only applicable when CHPS<1:0> = $01$ or $1x$ )                                                                                                                                                                                                                                                                                                                  |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 5 | <ul> <li>When AD12B = 1, SIMSAM is: U-0, Unimplemented, Read as '0'</li> <li>1 = Samples CH0, CH1, CH2, CH3 simultaneously (when CHPS&lt;1:0&gt; = 1x); or<br/>Samples CH0 and CH1 simultaneously (when CHPS&lt;1:0&gt; = 01)</li> <li>0 = Samples multiple channels individually in sequence</li> </ul>                                                                                                        |

| bit 2 | ASAM: ADC Sample Auto-Start bit                                                                                                                                                                                                                                                                                                                                                                                 |

|       | <ul> <li>1 = Sampling begins immediately after last conversion. SAMP bit is auto-set</li> <li>0 = Sampling begins when SAMP bit is set</li> </ul>                                                                                                                                                                                                                                                               |

| bit 1 | SAMP: ADC Sample Enable bit                                                                                                                                                                                                                                                                                                                                                                                     |

|       | <ul> <li>1 = ADC sample/hold amplifiers are sampling</li> <li>0 = ADC sample/hold amplifiers are holding</li> <li>If ASAM = 0, software can write '1' to begin sampling. Automatically set by hardware if ASAM = 1.</li> <li>If SSRC = 000, software can write '0' to end sampling and start conversion. If SSRC ≠ 000, automatically cleared by hardware to end sampling and start conversion.</li> </ul>      |

| bit 0 | DONE: ADC Conversion Status bit                                                                                                                                                                                                                                                                                                                                                                                 |

|       | <ul> <li>1 = ADC conversion cycle is completed</li> <li>0 = ADC conversion not started or in progress</li> <li>Automatically set by hardware when ADC conversion is complete. Software can write '0' to clear</li> <li>DONE status (software not allowed to write '1'). Clearing this bit does NOT affect any operation in progress. Automatically cleared by hardware at start of a new conversion.</li> </ul> |

## PIC24HJ32GP302/304, PIC24HJ64GPX02/X04 AND PIC24HJ128GPX02/X04

### **REGISTER 22-6: RTCVAL (WHEN RTCPTR<1:0> =** 01): **WKDYHR: WEEKDAY AND HOURS VALUE REGISTER<sup>(1)</sup>**

| U-0    | U-0 | U-0   | U-0   | U-0   | R/W-x   | R/W-x     | R/W-x   |

|--------|-----|-------|-------|-------|---------|-----------|---------|

| 0-0    | 0-0 | 0-0   | 0-0   | 0-0   | N/ VV-X |           | FV/VV-X |

| —      | —   |       | _     | _     |         | WDAY<2:0> |         |

| bit 15 |     |       |       |       |         |           | bit 8   |

|        |     |       |       |       |         |           |         |

| U-0    | U-0 | R/W-x | R/W-x | R/W-x | R/W-x   | R/W-x     | R/W-x   |

| U-0   | U-0 | R/W-x | R/W-x  | R/W-x | R/W-x | R/W-x  | R/W-x |

|-------|-----|-------|--------|-------|-------|--------|-------|

| —     | —   | HRTEN | N<1:0> |       | HRON  | E<3:0> |       |

| bit 7 |     |       |        |       |       |        | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-11 | Unimplemented: Read as '0'                                                                |

|-----------|-------------------------------------------------------------------------------------------|

| bit 10-8  | WDAY<2:0>: Binary Coded Decimal Value of Weekday Digit; contains a value from 0 to 6      |

| bit 7-6   | Unimplemented: Read as '0'                                                                |

| bit 5-4   | HRTEN<1:0>: Binary Coded Decimal Value of Hour's Tens Digit; contains a value from 0 to 2 |

| bit 3-0   | HRONE<3:0>: Binary Coded Decimal Value of Hour's Ones Digit; contains a value from 0 to 9 |

**Note 1:** A write to this register is only allowed when RTCWREN = 1.

## **REGISTER 22-7: RTCVAL (WHEN RTCPTR<1:0> =** 00): **MINUTES AND SECONDS VALUE REGISTER**

| U-0    | R/W-x       | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x   | R/W-x |

|--------|-------------|-------|-------|-------|-------|---------|-------|

| —      | MINTEN<2:0> |       |       |       | MINON | IE<3:0> |       |

| bit 15 |             |       |       |       |       |         | bit 8 |

|        |             |       |       |       |       |         |       |

| U-0    | R/W-x       | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x   | R/W-x |

|        | SECTEN<2:0> |       |       |       | SECON | IE<3:0> |       |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 15    | Unimplemented: Read as '0'                                                                   |

|-----------|----------------------------------------------------------------------------------------------|

| bit 14-12 | MINTEN<2:0>: Binary Coded Decimal Value of Minute's Tens Digit; contains a value from 0 to 5 |

| bit 11-8  | MINONE<3:0>: Binary Coded Decimal Value of Minute's Ones Digit; contains a value from 0 to 9 |

| bit 7     | Unimplemented: Read as '0'                                                                   |

| bit 6-4   | SECTEN<2:0>: Binary Coded Decimal Value of Second's Tens Digit; contains a value from 0 to 5 |

| bit 3-0   | SECONE<3:0>: Binary Coded Decimal Value of Second's Ones Digit; contains a value from 0 to 9 |

bit 7

bit 0

| TABLE 25-2:             | PIC24H CONFIGURATION BITS DESCRIPTION |             |                                                                                                                                                                                                                 |  |  |

|-------------------------|---------------------------------------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Bit Field               | Register                              | RTSP Effect | Description                                                                                                                                                                                                     |  |  |

| BWRP                    | FBS                                   | Immediate   | Boot Segment Program Flash Write Protection<br>1 = Boot segment can be written<br>0 = Boot segment is write-protected                                                                                           |  |  |

| BSS<2:0>                | FBS                                   | Immediate   | Boot Segment Program Flash Code Protection Size<br>X11 = No Boot program Flash segment                                                                                                                          |  |  |

|                         |                                       |             | Boot space is 1K Instruction Words (except interrupt vectors)<br>110 = Standard security; boot program Flash segment ends<br>at 0x0007FE<br>010 = High security; boot program Flash segment ends at<br>0x0007FE |  |  |

|                         |                                       |             | Boot space is 4K Instruction Words (except interrupt vectors)<br>101 = Standard security; boot program Flash segment, ends<br>at 0x001FFE                                                                       |  |  |

|                         |                                       |             | 001 = High security; boot program Flash segment ends at<br>0x001FFE                                                                                                                                             |  |  |

|                         |                                       |             | Boot space is 8K Instruction Words (except interrupt vectors)<br>100 = Standard security; boot program Flash segment ends<br>at 0x003FFE                                                                        |  |  |

|                         |                                       |             | 000 = High security; boot program Flash segment ends at<br>0x003FFE                                                                                                                                             |  |  |

| RBS<1:0> <sup>(1)</sup> | FBS                                   | Immediate   | Boot Segment RAM Code Protection Size<br>11 = No Boot RAM defined<br>10 = Boot RAM is 128 bytes<br>01 = Boot RAM is 256 bytes<br>00 = Boot RAM is 1024 bytes                                                    |  |  |

| SWRP <sup>(1)</sup>     | FSS <sup>(1)</sup>                    | Immediate   | Secure Segment Program Flash Write-Protect bit<br>1 = Secure Segment can bet written<br>0 = Secure Segment is write-protected                                                                                   |  |  |

| SSS<2:0> <sup>(1)</sup> | FSS <sup>(1)</sup>                    | Immediate   | Secure Segment Program Flash Code Protection Size<br>(Secure segment is not implemented on 32K devices)<br>X11 = No Secure program flash segment                                                                |  |  |

|                         |                                       |             | Secure space is 4K IW less BS<br>110 = Standard security; secure program flash segment starts<br>at End of BS, ends at 0x001FFE                                                                                 |  |  |

|                         |                                       |             | 010 = High security; secure program flash segment starts at<br>End of BS, ends at 0x001FFE                                                                                                                      |  |  |

|                         |                                       |             | Secure space is 8K IW less BS<br>101 = Standard security; secure program flash segment starts<br>at End of BS, ends at 0x003FFE<br>001 = High security; secure program flash segment starts at                  |  |  |

|                         |                                       |             | End of BS, ends at 0x003FFE<br>Secure space is 16K IW less BS<br>100 = Standard security; secure program flash segment starts                                                                                   |  |  |

|                         |                                       |             | at End of BS, ends at 007FFEh<br>000 = High security; secure program flash segment starts at<br>End of BS, ends at 0x007FFE                                                                                     |  |  |

## TABLE 25-2: PIC24H CONFIGURATION BITS DESCRIPTION

**Note 1:** This Configuration register is not available on PIC24HJ32GP302/304 devices.

## 28.0 ELECTRICAL CHARACTERISTICS

This section provides an overview of PIC24HJ32GP302/304, PIC24HJ64GPX02/X04 and PIC24HJ128GPX02/X04 electrical characteristics. Additional information is provided in future revisions of this document as it becomes available.

Absolute maximum ratings for the PIC24HJ32GP302/304, PIC24HJ64GPX02/X04 and PIC24HJ128GPX02/X04 family are listed below. Exposure to these maximum rating conditions for extended periods can affect device reliability. Functional operation of the device at these or any other conditions above the parameters indicated in the operation listings of this specification is not implied.

## Absolute Maximum Ratings<sup>(1)</sup>

| Ambient temperature under bias                                                    | 40°C to +125°C       |

|-----------------------------------------------------------------------------------|----------------------|

| Storage temperature                                                               | 65°C to +160°C       |

| Voltage on VDD with respect to Vss                                                | 0.3V to +4.0V        |

| Voltage on any pin that is not 5V tolerant with respect to Vss <sup>(4)</sup>     | 0.3V to (VDD + 0.3V) |

| Voltage on any 5V tolerant pin with respect to Vss when VDD $\ge 3.0V^{(4)}$      | 0.3V to +5.6V        |

| Voltage on any 5V tolerant pin with respect to Vss when VDD < 3.0V <sup>(4)</sup> | 0.3V to 3.6V         |

| Maximum current out of Vss pin                                                    |                      |

| Maximum current into Vod pin <sup>(2)</sup>                                       | 250 mA               |

| Maximum current sourced/sunk by any 2x I/O pin <sup>(3)</sup>                     | 8 mA                 |

| Maximum current sourced/sunk by any 4x I/O pin <sup>(3)</sup>                     | 15 mA                |

| Maximum current sourced/sunk by any 8x I/O pin <sup>(3)</sup>                     | 25 mA                |

| Maximum current sunk by all ports                                                 | 200 mA               |

| Maximum current sourced by all ports <sup>(2)</sup>                               | 200 mA               |

**Note 1:** Stresses above those listed under "Absolute Maximum Ratings" can cause permanent damage to the device. This is a stress rating only, and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods can affect device reliability.

- 2: Maximum allowable current is a function of device maximum power dissipation (see Table 28-2).

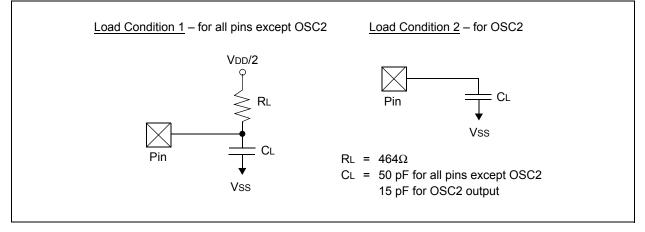

- **3:** Exceptions are CLKOUT, which is able to sink/source 25 mA, and the VREF+, VREF-, SCLx, SDAx, PGECx and PGEDx pins, which are able to sink/source 12 mA.

- 4: See the "Pin Diagrams" section for 5V tolerant pins.

## 29.2 AC Characteristics and Timing Parameters

The information contained in this section defines PIC24HJ32GP302/304, PIC24HJ64GPX02/X04 and PIC24HJ128GPX02/X04 AC characteristics and timing parameters for high temperature devices. However, all AC timing specifications in this section are the same as those in Section 28.2 "AC Characteristics and Timing Parameters", with the exception of the parameters listed in this section.

Parameters in this section begin with an H, which denotes High temperature. For example, parameter OS53 in Section 28.2 "AC Characteristics and Timing Parameters" is the Industrial and Extended temperature equivalent of HOS53.

### TABLE 29-8: TEMPERATURE AND VOLTAGE SPECIFICATIONS – AC

|                    | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated) |

|--------------------|-----------------------------------------------------------------------|

| AC CHARACTERISTICS | Operating temperature  -40°C ≤TA ≤+150°C for High Temperature         |

|                    | Operating voltage VDD range as described in Table 29-1.               |

### FIGURE 29-1: LOAD CONDITIONS FOR DEVICE TIMING SPECIFICATIONS

### TABLE 29-9: PLL CLOCK TIMING SPECIFICATIONS

| AC<br>CHARACTERISTICS |        | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated)         Operating temperature       -40°C ≤TA ≤+150°C for High Temperature |     |     |     |       |                             |  |

|-----------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|-------|-----------------------------|--|

| Param<br>No.          | Symbol | Characteristic                                                                                                                                   | Min | Тур | Max | Units | Conditions                  |  |

| HOS53                 | DCLK   | CLKO Stability (Jitter) <sup>(1)</sup>                                                                                                           | -5  | 0.5 | 5   | %     | Measured over 100 ms period |  |

Note 1: These parameters are characterized, but are not tested in manufacturing.

| Section Name                                                        | Update Description                                                                                                                                                                                                                             |

|---------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Section 10.0 "Power-Saving                                          | Added the following registers:                                                                                                                                                                                                                 |

| Features"                                                           | <ul> <li>PMD1: Peripheral Module Disable Control Register 1 (Register 10-1)</li> <li>PMD2: Peripheral Module Disable Control Register 2 (Register 10-2)</li> <li>PMD3: Peripheral Module Disable Control Register 3 (Register 10-3)</li> </ul> |

| Section 11.0 "I/O Ports"                                            | Removed Table 11-1 and added reference to pin diagrams for I/O pin availability and functionality.                                                                                                                                             |

|                                                                     | Added paragraph on ADPCFG register default values to Section 11.3<br>"Configuring Analog Port Pins".                                                                                                                                           |

|                                                                     | Added Note box regarding PPS functionality with input mapping to <b>Section 11.6.2.1 "Input Mapping"</b> .                                                                                                                                     |

| Section 16.0 "Serial Peripheral<br>Interface (SPI)"                 | Added Note 2 and 3 to the SPIxCON1 register (see Register 16-2).                                                                                                                                                                               |

| Section 18.0 "Universal                                             | Updated the Notes in the UxMode register (see Register 18-1).                                                                                                                                                                                  |

| Asynchronous Receiver Transmitter<br>(UART)"                        | Updated the UTXINV bit settings in the UxSTA register (see Register 18-2).                                                                                                                                                                     |

| Section 19.0 "Enhanced CAN<br>(ECAN™) Module"                       | Changed bit 11 in the ECAN Control Register 1 (CiCTRL1) to Reserved (see Register 19-1).                                                                                                                                                       |

| Section 20.0 "10-bit/12-bit Analog-to-<br>Digital Converter (ADC1)" | Replaced the ADC1 Module Block Diagrams with new diagrams (see Figure 20-1 and Figure 20-2).                                                                                                                                                   |

|                                                                     | Updated bit values for ADCS<7:0> and added Notes 1 and 2 to the ADC1 Control Register 3 (AD1CON3) (see Register 20-3).                                                                                                                         |

|                                                                     | Added Note 2 to the ADC1 Input Scan Select Register Low (AD1CSSL) (see Register 20-7).                                                                                                                                                         |

|                                                                     | Added Note 2 to the ADC1 Port Configuration Register Low (AD1PCFGL) (see Register 20-8).                                                                                                                                                       |

| Section 21.0 "Comparator Module"                                    | Updated the Comparator Voltage Reference Block Diagram (see Figure 21-2).                                                                                                                                                                      |

| Section 22.0 "Real-Time Clock and Calendar (RTCC)"                  | Updated the minimum positive adjust value for CAL<7:0> in the RTCC Calibration and Configuration (RCFGCAL) Register (see Register 22-1).                                                                                                       |

| Section 25.0 "Special Features"                                     | Added Note 1 to the Device Configuration Register Map (see Table 25-1).                                                                                                                                                                        |

|                                                                     | Updated Note 1 in the PIC24H Configuration Bits Description (see Table 25-2).                                                                                                                                                                  |

## TABLE A-2: MAJOR SECTION UPDATES (CONTINUED)

## **Revision D (November 2009)**

The revision includes the following global update:

• Added Note 2 to the shaded table that appears at the beginning of each chapter. This new note provides information regarding the availability of registers and their associated bits

This revision also includes minor typographical and formatting changes throughout the data sheet text.

All other major changes are referenced by their respective section in the following table.

## TABLE A-3: MAJOR SECTION UPDATES

| Section Name                                                      | Update Description                                                                                                                                 |

|-------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| "High-Performance, 16-bit<br>Microcontrollers"                    | Added information on high temperature operation (see <b>"Operating Range:</b> ").                                                                  |

| Section 11.0 "I/O Ports"                                          | Changed the reference to digital-only pins to 5V tolerant pins in the second paragraph of <b>Section 11.2</b> " <b>Open-Drain Configuration</b> ". |

| Section 18.0 "Universal Asynchronous Receiver Transmitter (UART)" | Updated the two baud rate range features to: 10 Mbps to 38 bps at 40 MIPS.                                                                         |

| Section 20.0 "10-bit/12-bit Analog-to-Digital Converter (ADC1)"   | Updated the ADC block diagrams (see Figure 20-1 and Figure 20-2).                                                                                  |

| Section 25.0 "Special Features"                                   | Updated the second paragraph and removed the fourth paragraph in <b>Section 25.1 "Configuration Bits"</b> .                                        |

|                                                                   | Updated the Device Configuration Register Map (see Table 28-1).                                                                                    |

| Section 28.0 "Electrical Characteristics"                         | Updated the Absolute Maximum Ratings for high temperature and added Note 4.                                                                        |

|                                                                   | Removed parameters DI26, DI28 and DI29 from the I/O Pin Input Specifications (see Table 28-9).                                                     |

|                                                                   | Updated the SPIx Module Slave Mode (CKE = 1) Timing Characteristics (see Figure 28-12).                                                            |

| Section 29.0 "High Temperature Electrical Characteristics"        | Added new chapter with high temperature specifications.                                                                                            |

| "Product Identification System"                                   | Added the "H" definition for high temperature.                                                                                                     |

| Peripheral Module Disable (PMD)      | 130    |

|--------------------------------------|--------|

| Pinout I/O Descriptions              | 11     |

| PMD Module                           |        |

| Register Map                         |        |

| PORTA                                |        |

| Register Map                         | 44, 45 |

| PORTB                                |        |

| Register Map                         | 45     |

| Power-on Reset (POR)                 | 65     |

| Power-Saving Features                | 129    |

| Clock Frequency and Switching        | 129    |

| Program Address Space                |        |

| Construction                         |        |

| Data Access from Program Memory      |        |

| Using Program Space Visibility       | 52     |

| Data Access from Program Memory      |        |

| Using Table Instructions             | 51     |

| Data Access from, Address Generation | 50     |

| Memory Map                           |        |

| Table Read Instructions              |        |

| TBLRDH                               |        |

| TBLRDL                               | 51     |

| Visibility Operation                 | 52     |

| Program Memory                       |        |

| Interrupt Vector                     |        |

| Organization                         |        |

| Reset Vector                         |        |

|                                      |        |

## R

| Reader Response                               | . 388            |

|-----------------------------------------------|------------------|

| Register Map                                  |                  |

| CRC                                           | 44               |

| Dual Comparator                               |                  |

| Parallel Master/Slave Port                    | 43               |

| Real-Time Clock and Calendar                  |                  |

| Registers                                     |                  |

| AD1CHS0 (ADC1 Input Channel 0 Select          | . 238            |

| AD1CHS123 (ADC1 Input Channel 1, 2, 3 Select) | . 237            |

| AD1CON1 (ADC1 Control 1)                      |                  |

| AD1CON2 (ADC1 Control 2)                      |                  |

| AD1CON3 (ADC1 Control 3)                      |                  |

| AD1CON4 (ADC1 Control 4)                      | . 236            |

| AD1CSSL (ADC1 Input Scan Select Low)          | . 239            |

| AD1PCFGL (ADC1 Port Configuration Low)        | . 239            |

| CiBUFPNT1 (ECAN Filter 0-3 Buffer Pointer)    | . 213            |

| CiBUFPNT2 (ECAN Filter 4-7 Buffer Pointer)    | . 214            |

| CiBUFPNT3 (ECAN Filter 8-11 Buffer Pointer)   | . 214            |

| CiBUFPNT4 (ECAN Filter 12-15 Buffer Pointer)  | . 215            |

| CiCFG1 (ECAN Baud Rate Configuration 1)       | . 211            |

| CiCFG2 (ECAN Baud Rate Configuration 2)       | . 212            |

| CiCTRL1 (ECAN Control 1)                      | . 204            |

| CiCTRL2 (ECAN Control 2)                      | . 205            |

| CIEC (ECAN Transmit/Receive Error Count)      |                  |

| CIFCTRL (ECAN FIFO Control)                   | . 207            |

| CiFEN1 (ECAN Acceptance Filter Enable)        | . 213            |

| CiFIFO (ECAN FIFO Status)                     |                  |

| CiFMSKSEL1 (ECAN Filter 7-0 Mask Selection)   |                  |

|                                               | 040              |

| CilNTE (ECAN Interrupt Enable)                |                  |

| CiINTF (ECAN Interrupt Flag)                  | . 209            |

| CiRXFnEID (ECAN Acceptance Filter n           | o 1 <del>-</del> |

| Extended Identifier)                          | .217             |

| CiRXFnSID (ECAN Acceptance Filter n           |                  |

| Standard Identifier)                          |                  |

| CiRXFUL1 (ECAN Receive Buffer Full 1)         |                  |

| CiRXFUL2 (ECAN Receive Buffer Full 2)         | . 220            |

| CiRXMnEID (ECAN Acceptance Filter Mask n      |                  |

| Extended Identifier)                                                       | 219    |

|----------------------------------------------------------------------------|--------|

| CiRXMnSID (ECAN Acceptance Filter Mask n                                   |        |

| Standard Identifier)                                                       | 219    |

| CiRXOVF1 (ECAN Receive Buffer Overflow 1)                                  | 221    |

| CiRXOVF2 (ECAN Receive Buffer Overflow 2)                                  | 221    |

| CiTRBnSID (ECAN Buffer n Standard Identifier)                              | 223,   |

| 224, 226                                                                   |        |

| CiTRmnCON (ECAN TX/RX Buffer m Control)                                    | 222    |

| CiVEC (ECAN Interrupt Code)                                                |        |