Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Active                                                                        |

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 40 MIPs                                                                       |

| Connectivity               | I <sup>2</sup> C, PMP, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                    |

| Number of I/O              | 21                                                                            |

| Program Memory Size        | 32KB (11K x 24)                                                               |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 4K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                     |

| Data Converters            | A/D 10x10b/12b                                                                |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 28-VQFN Exposed Pad                                                           |

| Supplier Device Package    | 28-QFN-S (6x6)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24hj32gp302-e-mm |

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Pin Diagrams (Continued)

| 44-Pin QFN <sup>(2)</sup>                                                                                                                                                                                                                                                                                                          | Pins are up to 5V tolerant                                                                                                                                                                                                                                                                                                                                                                                                |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AN4/C1IN-/RP2 <sup>(1</sup> )/CN6/RB2<br>AN5/C1IN+/RP3 <sup>(1</sup> )/CN7/RB3<br>AN6/RP16 <sup>(1</sup> )/CN8/RC0<br>AN7/RP17 <sup>(1</sup> )/CN9/RC1<br>C2<br>AN5/C1IN+/RP3 <sup>(1)</sup> /CN9/RC1<br>C2<br>AN5/C1IN+/RP3 <sup>(1)</sup> /CN9/RC1<br>C2<br>C2<br>C2<br>C2<br>C2<br>C2<br>C2<br>C2<br>C2<br>C2<br>C2<br>C2<br>C2 | AN11/RP13 <sup>(1)</sup> /CN13/PMRD/RB13<br>AN12/RP12 <sup>(1)</sup> /CN14/PMD0/RB12<br>9 PGEC2/RP11 <sup>(1)</sup> /CN15/PMD1/RB11<br>PGED2/RP10 <sup>(1)</sup> /CN15/PMD2/RB10<br>VCAP <sup>(3)</sup><br>VSS<br>P204 5 RP25 <sup>(1)</sup> /CN19/PMA6/RC9<br>RP24 <sup>(1)</sup> /CN20/PMA5/RC8<br>RP23 <sup>(1)</sup> /CN17/PMA0/RC7<br>2 RP22 <sup>(1)</sup> /CN18/PMA1/RC6<br>SDA1/RP9 <sup>(1)</sup> /CN21/PMD3/RB9 |

|                                                                                                                                                                                                                                                                                                                                    | I. See Table 1 in this section for the list of available peripherals.<br>ed to any pins and is recommended to be connected to Vss externally.<br><b>Section (VCAP)</b> " for proper connection to this pin.                                                                                                                                                                                                               |

#### 6.9 Configuration Mismatch Reset

To maintain the integrity of the peripheral pin select control registers, they are constantly monitored with shadow registers in hardware. If an unexpected change in any of the registers occur (such as cell disturbances caused by ESD or other external events), a configuration mismatch Reset occurs.

The Configuration Mismatch Flag bit (CM) in the Reset Control register (RCON<9>) is set to indicate the configuration mismatch Reset. Refer to **Section 11.0 "I/O Ports"** for more information on the configuration mismatch Reset.

Note: The configuration mismatch feature and associated reset flag is not available on all devices.

## 6.10 Illegal Condition Device Reset

An illegal condition device Reset occurs due to the following sources:

- Illegal Opcode Reset

- Uninitialized W Register Reset

- · Security Reset

The Illegal Opcode or Uninitialized W Access Reset Flag bit (IOPUWR) in the Reset Control register (RCON<14>) is set to indicate the illegal condition device Reset.

#### 6.10.1 ILLEGAL OPCODE RESET

A device Reset is generated if the device attempts to execute an illegal opcode value that is fetched from program memory.

The illegal opcode Reset function can prevent the device from executing program memory sections that are used to store constant data. To take advantage of the illegal opcode Reset, use only the lower 16 bits of

each program memory section to store the data values. The upper 8 bits should be programmed with 3Fh, which is an illegal opcode value.

#### 6.10.2 UNINITIALIZED W REGISTER RESET

Any attempts to use the uninitialized W register as an address pointer will Reset the device. The W register array (with the exception of W15) is cleared during all resets and is considered uninitialized until written to.

#### 6.10.3 SECURITY RESET

If a Program Flow Change (PFC) or Vector Flow Change (VFC) targets a restricted location in a protected segment (Boot and Secure Segment), that operation will cause a security Reset.

The PFC occurs when the Program Counter is reloaded as a result of a Call, Jump, Computed Jump, Return, Return from Subroutine, or other form of branch instruction.

The VFC occurs when the Program Counter is reloaded with an Interrupt or Trap vector.

Refer to Section 25.8 "Code Protection and CodeGuard™ Security" for more information on Security Reset.

# 6.11 Using the RCON Status Bits

The user application can read the Reset Control register (RCON) after any device Reset to determine the cause of the reset.

**Note:** The status bits in the RCON register should be cleared after they are read so that the next RCON register value after a device Reset will be meaningful.

Table 6-3 provides a summary of the reset flag bit operation.

| Flag Bit         | Set by:                                                                | Cleared by:                                         |

|------------------|------------------------------------------------------------------------|-----------------------------------------------------|

| TRAPR (RCON<15>) | Trap conflict event                                                    | POR, BOR                                            |

| IOPWR (RCON<14>) | Illegal opcode or uninitialized<br>W register access or Security Reset | POR, BOR                                            |

| CM (RCON<9>)     | Configuration Mismatch                                                 | POR, BOR                                            |

| EXTR (RCON<7>)   | MCLR Reset                                                             | POR                                                 |

| SWR (RCON<6>)    | RESET instruction                                                      | POR, BOR                                            |

| WDTO (RCON<4>)   | WDT time-out                                                           | PWRSAV instruction,<br>CLRWDT instruction, POR, BOR |

| SLEEP (RCON<3>)  | PWRSAV #SLEEP instruction                                              | POR, BOR                                            |

| IDLE (RCON<2>)   | PWRSAV #IDLE instruction                                               | POR, BOR                                            |

| BOR (RCON<1>)    | POR, BOR                                                               | _                                                   |

| POR (RCON<0>)    | POR                                                                    | —                                                   |

TABLE 6-3: RESET FLAG BIT OPERATION

**Note:** All Reset flag bits can be set or cleared by user software.

# FIGURE 7-1: PIC24HJ32GP302/304, PIC24HJ64GPX02/X04 and PIC24HJ128GPX02/X04 INTERRUPT VECTOR TABLE

|                                   |                                       | _                 |                                                        |

|-----------------------------------|---------------------------------------|-------------------|--------------------------------------------------------|

|                                   | Reset – GOTO Instruction              | 0x000000          |                                                        |

|                                   | Reset – GOTO Address                  | 0x000002          |                                                        |

|                                   | Reserved                              | 0x000004          |                                                        |

|                                   | Oscillator Fail Trap Vector           |                   |                                                        |

|                                   | Address Error Trap Vector             |                   |                                                        |

|                                   | Stack Error Trap Vector               |                   |                                                        |

|                                   | Math Error Trap Vector                |                   |                                                        |

|                                   | DMA Error Trap Vector                 |                   |                                                        |

|                                   | Reserved                              |                   |                                                        |

|                                   | Reserved                              |                   |                                                        |

|                                   | Interrupt Vector 0                    | 0x000014          |                                                        |

|                                   | Interrupt Vector 1                    |                   |                                                        |

|                                   | ~                                     |                   |                                                        |

|                                   | ~                                     | 1                 |                                                        |

|                                   | ~                                     |                   |                                                        |

|                                   | Interrupt Vector 52                   | 0x00007C          | $l_{1}$                                                |

|                                   | Interrupt Vector 53                   | 0x00007E          | Interrupt Vector Table (IVT) <sup>(1)</sup>            |

| ity                               | Interrupt Vector 54                   | 0x000080          |                                                        |

| ior                               | ~                                     |                   |                                                        |

| ā                                 | ~                                     |                   |                                                        |

| dei                               | ~                                     |                   |                                                        |

| Decreasing Natural Order Priority | Interrupt Vector 116                  | 0x0000FC          |                                                        |

| ral                               | Interrupt Vector 117                  | 0x0000FE          | •                                                      |

| atu                               | Reserved                              | 0x000100          |                                                        |

| ž                                 | Reserved                              | 0x000102          |                                                        |

| ing                               | Reserved                              |                   |                                                        |

| as                                | Oscillator Fail Trap Vector           |                   |                                                        |

| cre                               | Address Error Trap Vector             |                   |                                                        |

| De                                | Stack Error Trap Vector               | -                 |                                                        |

|                                   | Math Error Trap Vector                | _                 |                                                        |

|                                   | DMA Error Trap Vector                 | _                 |                                                        |

|                                   | Reserved                              |                   |                                                        |

|                                   | Reserved                              |                   |                                                        |

|                                   | Interrupt Vector 0                    | 0x000114          |                                                        |

|                                   | Interrupt Vector 1                    |                   |                                                        |

|                                   | ~                                     | -                 |                                                        |

|                                   | ~                                     |                   |                                                        |

|                                   | ~                                     |                   | Alternate Interrupt Vector Table (AIVT) <sup>(1)</sup> |

|                                   | Interrupt Vector 52                   | 0x00017C          |                                                        |

|                                   | Interrupt Vector 53                   | 0x00017E          |                                                        |

|                                   | Interrupt Vector 54                   | 0x000180          |                                                        |

|                                   | ~                                     |                   |                                                        |

|                                   | ~                                     |                   |                                                        |

|                                   | ~                                     |                   |                                                        |

|                                   | Interrupt Vector 116                  | 1 –               | -                                                      |

|                                   | Interrupt Vector 117                  | 0x0001FE          |                                                        |

| V                                 | Start of Code                         | 0x000200          |                                                        |

|                                   |                                       | -                 |                                                        |

|                                   |                                       |                   |                                                        |

|                                   |                                       |                   |                                                        |

| Note 1: S                         | See Table 7-1 for the list of impleme | ented interrupt v | vectors.                                               |

|                                   |                                       |                   |                                                        |

|                                   |                                       |                   |                                                        |

| U-0          | U-0                    | U-0                                    | U-0            | U-0               | R/W-1                      | R/W-0      | R/W-0 |

|--------------|------------------------|----------------------------------------|----------------|-------------------|----------------------------|------------|-------|

| —            | —                      | —                                      | _              | —                 |                            | RTCIP<2:0> |       |

| bit 15       |                        |                                        |                |                   |                            |            | bit   |

| U-0          | R/W-1                  | R/W-0                                  | R/W-0          | U-0               | U-0                        | U-0        | U-0   |

|              |                        | DMA5IP<2:0>                            | 1011 0         |                   |                            | _          | _     |

| bit 7        |                        |                                        |                |                   |                            |            | bit   |

|              |                        |                                        |                |                   |                            |            |       |

| Legend:      |                        |                                        |                |                   |                            |            |       |

| R = Readab   | ole bit                | W = Writable                           | bit            | U = Unimplen      | nented bit, read           | 1 as '0'   |       |

| -n = Value a | It POR                 | '1' = Bit is set                       |                | '0' = Bit is clea | cleared x = Bit is unknown |            |       |

|              |                        |                                        |                |                   |                            |            |       |

| bit 15-11    | Unimpleme              | ented: Read as '                       | )'             |                   |                            |            |       |

| bit 10-8     |                        | Real-Time Clo                          |                | •                 | ag Status bits             |            |       |

|              | 111 = Interr           | upt is priority 7 (I                   | highest priori | ty interrupt)     |                            |            |       |

|              | •                      |                                        |                |                   |                            |            |       |

|              | •                      |                                        |                |                   |                            |            |       |

|              |                        | upt is priority 1<br>upt source is dis | abled          |                   |                            |            |       |

| bit 7        | Unimpleme              | ented: Read as '                       | כי             |                   |                            |            |       |

| bit 6-4      | DMA5IP<2:              | 0>: DMA Channe                         | el 5 Data Tra  | nsfer Complete    | Interrupt Priori           | ty bits    |       |

|              | 111 = Interr           | upt is priority 7 (I                   | highest priori | ty interrupt)     |                            |            |       |

|              |                        |                                        |                |                   |                            |            |       |

|              | •                      |                                        |                |                   |                            |            |       |

|              | •<br>•                 |                                        |                |                   |                            |            |       |

|              | •<br>•<br>001 = Interr | upt is priority 1                      |                |                   |                            |            |       |

# REGISTER 7-26: IPC15: INTERRUPT PRIORITY CONTROL REGISTER 15

bit 3-0

Unimplemented: Read as '0'

| U-0                            | U-0                                                                                                                                                                                      | U-0                                                       | U-0                                                                                                                                                                              | R-1                                                                                                           | R-1              | R-1             | R-1                                                                                                                                                                                                                       |  |  |  |  |  |

|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|------------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 0-0                            | 0-0                                                                                                                                                                                      | 0-0                                                       | 0-0                                                                                                                                                                              | N-1                                                                                                           |                  |                 | N-1                                                                                                                                                                                                                       |  |  |  |  |  |

| <br>bit 15                     | LSTCH<3:0>                                                                                                                                                                               |                                                           |                                                                                                                                                                                  |                                                                                                               |                  |                 | bit                                                                                                                                                                                                                       |  |  |  |  |  |

|                                |                                                                                                                                                                                          |                                                           |                                                                                                                                                                                  |                                                                                                               |                  |                 | DIL                                                                                                                                                                                                                       |  |  |  |  |  |

| R-0                            | R-0                                                                                                                                                                                      | R-0                                                       | R-0                                                                                                                                                                              | R-0                                                                                                           | R-0              | R-0             | R-0                                                                                                                                                                                                                       |  |  |  |  |  |

| PPST7                          | PPST6                                                                                                                                                                                    | PPST5                                                     | PPST4                                                                                                                                                                            | PPST3                                                                                                         | PPST2            | PPST1           | PPST0                                                                                                                                                                                                                     |  |  |  |  |  |

| pit 7                          |                                                                                                                                                                                          |                                                           |                                                                                                                                                                                  |                                                                                                               |                  |                 | bit                                                                                                                                                                                                                       |  |  |  |  |  |

|                                |                                                                                                                                                                                          |                                                           |                                                                                                                                                                                  |                                                                                                               |                  |                 |                                                                                                                                                                                                                           |  |  |  |  |  |

| _egend:                        |                                                                                                                                                                                          |                                                           |                                                                                                                                                                                  |                                                                                                               |                  |                 |                                                                                                                                                                                                                           |  |  |  |  |  |

| R = Readabl                    | e bit                                                                                                                                                                                    | W = Writable                                              | bit                                                                                                                                                                              | U = Unimplem                                                                                                  | nented bit, read | as '0'          |                                                                                                                                                                                                                           |  |  |  |  |  |

| n = Value at                   | t POR                                                                                                                                                                                    | '1' = Bit is set                                          |                                                                                                                                                                                  | '0' = Bit is clea                                                                                             | ared             | x = Bit is unkr | nown                                                                                                                                                                                                                      |  |  |  |  |  |

| bit 15-12<br>bit 11-8<br>bit 7 | LSTCH<3:0><br>1111 = No DI<br>1110-1000 =<br>0111 = Last of<br>0101 = Last of<br>0100 = Last of<br>0010 = Last of<br>0010 = Last of<br>0001 = Last of<br>0000 = Last of<br>PPST7: Chan   |                                                           | annel Active t<br>s occurred sin<br>as by DMA Ch<br>as by DMA Ch | ce system Res<br>nannel 7<br>nannel 6<br>nannel 5<br>nannel 4<br>nannel 3<br>nannel 2<br>nannel 1<br>nannel 0 | et               |                 |                                                                                                                                                                                                                           |  |  |  |  |  |

| oit 6                          | 0 = DMA7STA<br><b>PPST6:</b> Chan<br>1 = DMA6STE                                                                                                                                         | A register select<br>anel 6 Ping-Por<br>3 register select | eted<br>ng Mode Statu<br>eted                                                                                                                                                    | s Flag bit                                                                                                    |                  |                 |                                                                                                                                                                                                                           |  |  |  |  |  |

| pit 5                          | <ul> <li>0 = DMA6STA register selected</li> <li>PPST5: Channel 5 Ping-Pong Mode Status Flag bit</li> <li>1 = DMA5STB register selected</li> <li>0 = DMA5STA register selected</li> </ul> |                                                           |                                                                                                                                                                                  |                                                                                                               |                  |                 |                                                                                                                                                                                                                           |  |  |  |  |  |

| oit 4                          | <ul> <li>PPST4: Channel 4 Ping-Pong Mode Status Flag bit</li> <li>1 = DMA4STB register selected</li> <li>0 = DMA4STA register selected</li> </ul>                                        |                                                           |                                                                                                                                                                                  |                                                                                                               |                  |                 |                                                                                                                                                                                                                           |  |  |  |  |  |

| pit 3                          | <b>PPST3:</b> Channel 3 Ping-Pong Mode Status Flag bit<br>1 = DMA3STB register selected<br>0 = DMA3STA register selected                                                                 |                                                           |                                                                                                                                                                                  |                                                                                                               |                  |                 |                                                                                                                                                                                                                           |  |  |  |  |  |

| bit 2                          | 1 = DMA2STE                                                                                                                                                                              | nel 2 Ping-Por<br>3 register selec<br>4 register selec    | cted                                                                                                                                                                             | s Flag bit                                                                                                    |                  |                 |                                                                                                                                                                                                                           |  |  |  |  |  |

| oit 1                          | 1 = DMA1STE                                                                                                                                                                              | nel 1 Ping-Por<br>3 register selec<br>4 register selec    | cted                                                                                                                                                                             | s Flag bit                                                                                                    |                  |                 |                                                                                                                                                                                                                           |  |  |  |  |  |

| oit O                          | 1 = DMA0STE                                                                                                                                                                              | B register seled                                          | cted                                                                                                                                                                             | s Flag bit                                                                                                    |                  |                 | <ul> <li>a DMATSTB register selected</li> <li>b DMATSTA register selected</li> <li>b PPST0: Channel 0 Ping-Pong Mode Status Flag bit</li> <li>c DMA0STB register selected</li> <li>c DMA0STA register selected</li> </ul> |  |  |  |  |  |

| Oscillator Mode                                  | Oscillator Source | POSCMD<1:0> | FNOSC<2:0> | See<br>Note |  |  |  |

|--------------------------------------------------|-------------------|-------------|------------|-------------|--|--|--|

| Fast RC Oscillator with Divide-by-N<br>(FRCDIVN) | Internal          | XX          | 111        | 1, 2        |  |  |  |

| Fast RC Oscillator with Divide-by-16 (FRCDIV16)  | Internal          | XX          | 110        | 1           |  |  |  |

| Low-Power RC Oscillator (LPRC)                   | Internal          | XX          | 101        | 1           |  |  |  |

| Secondary (Timer1) Oscillator (Sosc)             | Secondary         | XX          | 100        | 1           |  |  |  |

| Primary Oscillator (HS) with PLL<br>(HSPLL)      | Primary           | 10          | 011        | -           |  |  |  |

| Primary Oscillator (XT) with PLL<br>(XTPLL)      | Primary           | 01          | 011        | -           |  |  |  |

| Primary Oscillator (EC) with PLL<br>(ECPLL)      | Primary           | 00          | 011        | 1           |  |  |  |

| Primary Oscillator (HS)                          | Primary           | 10          | 010        | _           |  |  |  |

| Primary Oscillator (XT)                          | Primary           | 01          | 010        | _           |  |  |  |

| Primary Oscillator (EC)                          | Primary           | 00          | 010        | 1           |  |  |  |

| Fast RC Oscillator with PLL (FRCPLL)             | Internal          | XX          | 001        | 1           |  |  |  |

| Fast RC Oscillator (FRC)                         | Internal          | XX          | 000        | 1           |  |  |  |

**Note 1:** OSC2 pin function is determined by the OSCIOFNC Configuration bit.

2: This is the default oscillator mode for an unprogrammed (erased) device.

# 9.2 Oscillator Resources

Many useful resources related to Oscillators are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

Note: In the event you are not able to access the product page using the link above, enter this URL in your browser: http://www.microchip.com/wwwproducts/ Devices.aspx?dDocName=en532315

#### 9.2.1 KEY RESOURCES

- Section 39. "Oscillator (Part III)" (DS70216)

- Code Samples

- Application Notes

- · Software Libraries

- Webinars

- All related dsPIC33F/PIC24H Family Reference Manuals Sections

- Development Tools

# **10.0 POWER-SAVING FEATURES**

- **Note 1:** This data sheet summarizes the features the PIC24HJ32GP302/304. of PIC24HJ64GPX02/X04 and of PIC24HJ128GPX02/X04 families devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet. refer to Section 9. "Watchdog Timer and Power-Saving Modes" (DS70196) of the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The PIC24HJ32GP302/304, PIC24HJ64GPX02/X04 and PIC24HJ128GPX02/X04 devices provide the ability to manage power consumption by selectively managing clocking to the CPU and the peripherals. In general, a lower clock frequency and a reduction in the number of circuits being clocked constitutes lower consumed power. PIC24HJ32GP302/304, PIC24HJ64GPX02/X04 and PIC24HJ128GPX02/X04 devices can manage power consumption in four ways:

- Clock frequency

- Instruction-based Sleep and Idle modes

- Software-controlled Doze mode

- Selective peripheral control in software

Combinations of these methods can be used to selectively tailor an application's power consumption while still maintaining critical application features, such as timing-sensitive communications.

## 10.1 Clock Frequency and Clock Switching

PIC24HJ32GP302/304, PIC24HJ64GPX02/X04 and PIC24HJ128GPX02/X04 devices allow a wide range of clock frequencies to be selected under application control. If the system clock configuration is not locked, users can choose low-power or high-precision oscillators by simply changing the NOSC bits (OSCCON<10:8>). The process of changing a system clock during operation, as well as limitations to the process, are discussed in more detail in Section 9.0 "Oscillator Configuration".

#### 10.2 Instruction-Based Power-Saving Modes

PIC24HJ32GP302/304, PIC24HJ64GPX02/X04 and PIC24HJ128GPX02/X04 devices have two special power-saving modes that are entered through the execution of a special PWRSAV instruction. Sleep mode stops clock operation and halts all code execution. Idle mode halts the CPU and code execution, but allows peripheral modules to continue operation. The assembler syntax of the PWRSAV instruction is shown in Example 10-1.

Note: SLEEP\_MODE and IDLE\_MODE are constants defined in the assembler include file for the selected device.

Sleep and Idle modes can be exited as a result of an enabled interrupt, WDT time-out or a device Reset. When the device exits these modes, it is said to wake up.

#### 10.2.1 SLEEP MODE

The following occur in Sleep mode:

- The system clock source is shut down. If an on-chip oscillator is used, it is turned off.

- The device current consumption is reduced to a minimum, provided that no I/O pin is sourcing current.

- The Fail-Safe Clock Monitor does not operate, since the system clock source is disabled.

- The LPRC clock continues to run in Sleep mode if the WDT is enabled.

- The WDT, if enabled, is automatically cleared prior to entering Sleep mode.

- Some device features or peripherals can continue to operate. This includes items such as the input change notification on the I/O ports, or peripherals that use an external clock input.

- Any peripheral that requires the system clock source for its operation is disabled.

The device wakes up from Sleep mode on any of the these events:

- · Any interrupt source that is individually enabled

- Any form of device Reset

- A WDT time-out

On wake-up from Sleep mode, the processor restarts with the same clock source that was active when Sleep mode was entered.

#### EXAMPLE 10-1: PWRSAV INSTRUCTION SYNTAX

PWRSAV #SLEEP\_MODE ; Put the device into SLEEP mode

PWRSAV #IDLE\_MODE ; Put the device into IDLE mode

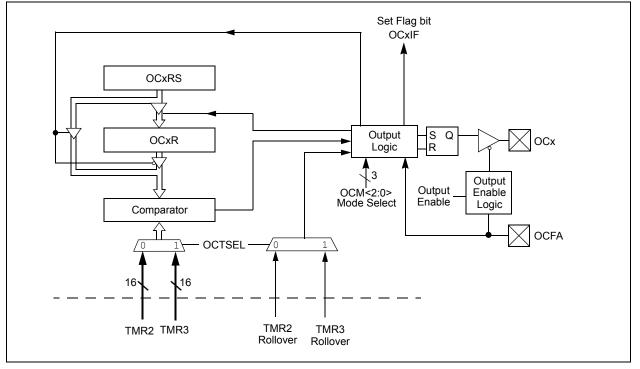

# 15.0 OUTPUT COMPARE

- Note 1: This data sheet summarizes the features of the PIC24HJ32GP302/304, PIC24HJ64GPX02/X04 and PIC24HJ128GPX02/X04 families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 13. "Output Compare" (DS70209) of the "dsPIC33F/ PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Output Compare module can select either Timer2 or Timer3 for its time base. The module compares the value of the timer with the value of one or two compare registers depending on the operating mode selected. The state of the output pin changes when the timer value matches the compare register value. The Output Compare module generates either a single output pulse or a sequence of output pulses, by changing the state of the output pin on the compare match events. The Output Compare module can also generate interrupts on compare match events.

The Output Compare module has multiple operating modes:

- Active-Low One-Shot mode

- Active-High One-Shot mode

- Toggle mode

- · Delayed One-Shot mode

- · Continuous Pulse mode

- PWM mode without fault protection

- · PWM mode with fault protection

## FIGURE 15-1: OUTPUT COMPARE MODULE BLOCK DIAGRAM

| R/W-0           | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | R/W-0                                                                                     | U-0                                                                   | R/W-0 HC                                                 | R/W-0                                                            | R-0              | R-1            |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|----------------------------------------------------------|------------------------------------------------------------------|------------------|----------------|

| UTXISEL1        | UTXINV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | UTXISEL0                                                                                  |                                                                       | UTXBRK                                                   | UTXEN <sup>(1)</sup>                                             | UTXBF            | TRMT           |

| bit 15          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                           |                                                                       |                                                          |                                                                  |                  | bit 8          |

|                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                           |                                                                       |                                                          |                                                                  |                  |                |

| R/W-0           | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | R/W-0                                                                                     | R-1                                                                   | R-0                                                      | R-0                                                              | R/C-0            | R-0            |

| URXISI          | EL<1:0>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ADDEN                                                                                     | RIDLE                                                                 | PERR                                                     | FERR                                                             | OERR             | URXDA          |

| bit 7           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                           |                                                                       |                                                          |                                                                  |                  | bit            |

|                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                           |                                                                       |                                                          |                                                                  |                  |                |

| Legend:         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | HC = Hardwa                                                                               |                                                                       | C = Clear on                                             | ,                                                                |                  |                |

| R = Readable    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | W = Writable                                                                              | bit                                                                   | -                                                        | mented bit, read                                                 |                  |                |

| -n = Value at F | POR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | '1' = Bit is set                                                                          |                                                                       | '0' = Bit is cle                                         | ared                                                             | x = Bit is unkr  | nown           |

| bit 15,13       | 11 = Reserve<br>10 = Interrupt<br>transmit<br>01 = Interrupt<br>operatio<br>00 = Interrupt                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | t when a charac<br>buffer become<br>t when the last<br>ons are complet<br>t when a charac | cter is transfe<br>s empty<br>character is s<br>ed<br>cter is transfe | rred to the Trai<br>hifted out of th<br>rred to the Trai | bits<br>nsmit Shift Regi<br>e Transmit Shift<br>nsmit Shift Regi | Register; all tr | ansmit         |

| bit 14          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | one character c<br>nsmit Polarity Ir                                                      | •                                                                     | insmit buller)                                           |                                                                  |                  |                |

|                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                           |                                                                       |                                                          |                                                                  |                  |                |

| bit 12          | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                           |                                                                       |                                                          |                                                                  |                  |                |

| bit 11          | <ul> <li>UTXBRK: Transmit Break bit</li> <li>1 = Send Sync Break on next transmission – Start bit, followed by twelve '0' bits, followed by Stop to cleared by hardware upon completion</li> <li>0 = Sync Break transmission disabled or completed</li> </ul>                                                                                                                                                                                                                                                                                                          |                                                                                           |                                                                       |                                                          |                                                                  |                  | ed by Stop bit |

| bit 10          | UTXEN: Tran                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | smit Enable bit                                                                           | (1)                                                                   |                                                          |                                                                  |                  |                |

|                 | <ul> <li>1 = Transmit enabled, UxTX pin controlled by UARTx</li> <li>0 = Transmit disabled, any pending transmission is aborted and buffer is reset. UxTX pin controller<br/>by port</li> </ul>                                                                                                                                                                                                                                                                                                                                                                        |                                                                                           |                                                                       |                                                          |                                                                  |                  |                |

| bit 9           | <ul> <li>UTXBF: Transmit Buffer Full Status bit (read-only)</li> <li>1 = Transmit buffer is full</li> <li>0 = Transmit buffer is not full, at least one more character can be written</li> </ul>                                                                                                                                                                                                                                                                                                                                                                       |                                                                                           |                                                                       |                                                          |                                                                  |                  |                |

| bit 8           | 1 = Transmit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                           | s empty and tr                                                        | ansmit buffer is                                         | s empty (the last<br>is in progress o                            |                  | as completed   |

| bit 7-6         | <ul> <li>0 = Transmit Shift Register is not empty, a transmission is in progress or queued</li> <li>URXISEL&lt;1:0&gt;: Receive Interrupt Mode Selection bits</li> <li>11 = Interrupt is set on UxRSR transfer making the receive buffer full (i.e., has 4 data characters)</li> <li>10 = Interrupt is set on UxRSR transfer making the receive buffer 3/4 full (i.e., has 3 data characters)</li> <li>0x = Interrupt is set when any character is received and transferred from the UxRSR to the receive buffer. Receive buffer has one or more characters</li> </ul> |                                                                                           |                                                                       |                                                          |                                                                  |                  | ta characters  |

| Note 1: Pot     | fer to Section 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                           | 270232) in th                                                         | - "deDIC33E/D                                            | IC24H Eamily E                                                   | Poforonco Mon    | ual" for       |

**Note 1:** Refer to **Section 17. "UART"** (DS70232) in the *"dsPIC33F/PIC24H Family Reference Manual"* for information on enabling the UART module for transmit operation.

| R/W-0        | R-0                                                                                                                                                     | R-0                    | R-0                              | R/W-0            | R/W-0             | R/W-0           | R/W-0         |  |  |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|----------------------------------|------------------|-------------------|-----------------|---------------|--|--|

| TXENn        | TXABTn                                                                                                                                                  | TXLARBn                | TXERRn                           | TXREQn           | RTRENn            | TXnPRI<1:0>     |               |  |  |

| bit 15       |                                                                                                                                                         |                        |                                  |                  |                   | •               | bit 8         |  |  |

|              |                                                                                                                                                         |                        |                                  |                  |                   |                 |               |  |  |

| R/W-0        | R-0                                                                                                                                                     | R-0                    | R-0                              | R/W-0            | R/W-0             | R/W-0           | R/W-0         |  |  |

| TXENm        | TXABTm <sup>(1)</sup>                                                                                                                                   | TXLARBm <sup>(1)</sup> | TXERRm <sup>(1)</sup>            | TXREQm           | RTRENm            | TXmPF           | RI<1:0>       |  |  |

| bit 7        |                                                                                                                                                         |                        |                                  |                  |                   |                 | bit (         |  |  |

| Legend:      |                                                                                                                                                         | C = Writeable          | bit but only '(                  | )' can be writte | en to clear the b | it              |               |  |  |

| R = Readab   | le bit                                                                                                                                                  | W = Writable           | -                                |                  | nented bit, read  |                 |               |  |  |

| -n = Value a |                                                                                                                                                         | '1' = Bit is set       |                                  | '0' = Bit is cle |                   | x = Bit is unkr | nown          |  |  |

|              |                                                                                                                                                         |                        |                                  |                  |                   |                 |               |  |  |

| bit 15-8     | See Definitior                                                                                                                                          | n for Bits 7-0, C      | Controls Buffer                  | n                |                   |                 |               |  |  |

| bit 7        |                                                                                                                                                         | RX Buffer Sele         |                                  |                  |                   |                 |               |  |  |

|              | 1 = Buffer TR                                                                                                                                           | Bn is a transm         | it buffer                        |                  |                   |                 |               |  |  |

|              | 0 = Buffer TR                                                                                                                                           | Bn is a receive        | e buffer                         |                  |                   |                 |               |  |  |

| bit 6        | TXABTm: Me                                                                                                                                              | essage Aborted         | d bit <sup>(1)</sup>             |                  |                   |                 |               |  |  |

|              | 1 = Message was aborted                                                                                                                                 |                        |                                  |                  |                   |                 |               |  |  |

|              | -                                                                                                                                                       | -                      | nsmission succ                   | -                |                   |                 |               |  |  |

| bit 5        |                                                                                                                                                         | 0                      | Arbitration bit <sup>(1)</sup>   |                  |                   |                 |               |  |  |

|              | <ul> <li>1 = Message lost arbitration while being sent</li> <li>0 = Message did not lose arbitration while being sent</li> </ul>                        |                        |                                  |                  |                   |                 |               |  |  |

| 1.1.4        |                                                                                                                                                         |                        |                                  |                  |                   |                 |               |  |  |

| bit 4        |                                                                                                                                                         |                        | uring Transmis                   |                  |                   |                 |               |  |  |

|              |                                                                                                                                                         |                        | ile the messag<br>r while the me |                  |                   |                 |               |  |  |

| bit 3        |                                                                                                                                                         | essage Send F          |                                  | sage was bei     | ng sent           |                 |               |  |  |

|              |                                                                                                                                                         | -                      | -                                | bit automatica   | ally clears when  | the message i   | s successfull |  |  |

|              | 0 = Clearing t                                                                                                                                          | he bit to '0' wh       | ile set request                  | s a message a    | abort             |                 |               |  |  |

| bit 2        | RTRENm: Au                                                                                                                                              | ito-Remote Tra         | ansmit Enable I                  | bit              |                   |                 |               |  |  |