Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Active                                                                        |

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 40 MIPs                                                                       |

| Connectivity               | I <sup>2</sup> C, PMP, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                    |

| Number of I/O              | 21                                                                            |

| Program Memory Size        | 32KB (11K x 24)                                                               |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 4K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                     |

| Data Converters            | A/D 10x10b/12b                                                                |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                                |

| Supplier Device Package    | 28-SOIC                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24hj32gp302-e-so |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Table of Contents**

| PIC2  | 4HJ32GP302/304, PIC24HJ64GPX02/X04 and PIC24HJ128GPX02/X04 Product Families |     |

|-------|-----------------------------------------------------------------------------|-----|

| 1.0   | Device Overview                                                             |     |

| 2.0   | Guidelines for Getting Started with 16-bit Microcontrollers                 |     |

| 3.0   | СРИ                                                                         |     |

| 4.0   | Memory Organization                                                         |     |

| 5.0   | Flash Program Memory                                                        |     |

| 6.0   | Resets                                                                      |     |

| 7.0   | Interrupt Controller                                                        |     |

| 8.0   | Direct Memory Access (DMA)                                                  | 107 |

| 9.0   | Oscillator Configuration                                                    | 119 |

| 10.0  | Power-Saving Features                                                       | 129 |

| 11.0  | I/O Ports                                                                   | 135 |

| 12.0  | Timer1                                                                      | 161 |

| 13.0  |                                                                             |     |

| 14.0  | Input Capture                                                               |     |

| 15.0  | Output Compare                                                              | 175 |

| 16.0  | Serial Peripheral Interface (SPI)                                           | 179 |

| 17.0  | Inter-Integrated Circuit™ (I <sup>2</sup> C™)                               | 185 |

| 18.0  | Universal Asynchronous Receiver Transmitter (UART)                          | 193 |

| 19.0  | Enhanced CAN (ECAN™) Module                                                 | 199 |

| 20.0  | 10-bit/12-bit Analog-to-Digital Converter (ADC1)                            |     |

| 21.0  | Comparator Module                                                           |     |

| 22.0  | Real-Time Clock and Calendar (RTCC)                                         |     |

| 23.0  | Programmable Cyclic Redundancy Check (CRC) Generator                        |     |

| 24.0  | Parallel Master Port (PMP)                                                  |     |

|       | Special Features                                                            |     |

| 26.0  | Instruction Set Summary                                                     |     |

| 27.0  | Development Support                                                         |     |

|       | Electrical Characteristics                                                  |     |

| 29.0  | High Temperature Electrical Characteristics                                 |     |

| 32.0  | DC and AC Device Characteristics Graphs                                     |     |

| 33.0  | Packaging Information                                                       |     |

| Appe  | endix A: Revision History                                                   |     |

| The I | Microchip Web Site                                                          |     |

| Custo | omer Change Notification Service                                            |     |

| Custo | omer Support                                                                |     |

| Read  | ler Response                                                                |     |

| Prod  | uct Identification System                                                   |     |

| TABLE       | 4-4:        | INTER  |        | ONTRO       | LLER R | EGISTER | R MAP  |            |                     |       |                       |             |         |                     |                       |            |         |               |

|-------------|-------------|--------|--------|-------------|--------|---------|--------|------------|---------------------|-------|-----------------------|-------------|---------|---------------------|-----------------------|------------|---------|---------------|

| SFR<br>Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13      | Bit 12 | Bit 11  | Bit 10 | Bit 9      | Bit 8               | Bit 7 | Bit 6                 | Bit 5       | Bit 4   | Bit 3               | Bit 2                 | Bit 1      | Bit 0   | All<br>Resets |

| INTCON1     | 0080        | NSTDIS | —      | —           | _      |         | _      | —          | _                   | _     | DIV0ERR               | DMACERR     | MATHERR | ADDRERR             | STKERR                | OSCFAIL    | -       | 0000          |

| INTCON2     | 0082        | ALTIVT | DISI   |             |        | _       |        | _          | _                   | _     | _                     |             |         | _                   | INT2EP                | INT1EP     | INT0EP  | 0000          |

| IFS0        | 0084        | _      | DMA1IF | AD1IF       | U1TXIF | U1RXIF  | SPI1IF | SPI1EIF    | T3IF                | T2IF  | OC2IF                 | IC2IF       | DMA0IF  | T1IF                | OC1IF                 | IC1IF      | INT0IF  | 0000          |

| IFS1        | 0086        | U2TXIF | U2RXIF | INT2IF      | T5IF   | T4IF    | OC4IF  | OC3IF      | DMA2IF              | IC8IF | IC7IF                 | _           | INT1IF  | CNIF                | CMIF                  | MI2C1IF    | SI2C1IF | 0000          |

| IFS2        | 0088        | _      | DMA4IF | PMPIF       | _      | _       | _      | _          | _                   | _     | _                     | _           | DMA3IF  | C1IF <sup>(1)</sup> | C1RXIF <sup>(1)</sup> | SPI2IF     | SPI2EIF | 0000          |

| IFS3        | 008A        | _      | RTCIF  | DMA5IF      | _      | _       | _      | —          | _                   | _     | —                     | _           | _       | —                   | _                     | _          | _       | 0000          |

| IFS4        | 008C        | _      | _      | _           | _      | —       | _      | —          | —                   | _     | C1TXIF <sup>(1)</sup> | DMA7IF      | DMA6IF  | CRCIF               | U2EIF                 | U1EIF      | _       | 0000          |

| IEC0        | 0094        | _      | DMA1IE | AD1IE       | U1TXIE | U1RXIE  | SPI1IE | SPI1EIE    | T3IE                | T2IE  | OC2IE                 | IC2IE       | DMA0IE  | T1IE                | OC1IE                 | IC1IE      | INT0IE  | 0000          |

| IEC1        | 0096        | U2TXIE | U2RXIE | INT2IE      | T5IE   | T4IE    | OC4IE  | OC3IE      | DMA2IE              | IC8IE | IC7IE                 | _           | INT1IE  | CNIE                | CMIE                  | MI2C1IE    | SI2C1IE | 0000          |

| IEC2        | 0098        | _      | DMA4IE | PMPIE       | _      | _       | _      | _          | _                   | _     | _                     | _           | DMA3IE  | C1IE <sup>(1)</sup> | C1RXIE <sup>(1)</sup> | SPI2IE     | SPI2EIE | 0000          |

| IEC3        | 009A        | _      | RTCIE  | DMA5IE      | _      | _       | _      | _          | _                   | _     | _                     | _           | _       | _                   | _                     | _          | _       | 0000          |

| IEC4        | 009C        | _      | _      | _           | _      | _       | _      | _          | _                   | _     | C1TXIE <sup>(1)</sup> | DMA7IE      | DMA6IE  | CRCIE               | U2EIE                 | U1EIE      | _       | 0000          |

| IPC0        | 00A4        | _      |        | T1IP<2:0>   |        | _       | (      | OC1IP<2:0  | >                   | _     |                       | IC1IP<2:0>  |         | _                   | IN                    | IT0IP<2:0> |         | 4444          |

| IPC1        | 00A6        | —      |        | T2IP<2:0>   |        |         | (      | OC2IP<2:0  | >                   | —     |                       | IC2IP<2:0>  |         | —                   | DN                    | /A0IP<2:0  | >       | 4444          |

| IPC2        | 00A8        | _      | U      | 1RXIP<2:0   | >      | _       | Ş      | SPI1IP<2:0 | >                   | _     | SPI1EIP<2:0>          |             | _       | T3IP<2:0>           |                       |            | 4444    |               |

| IPC3        | 00AA        | _      | _      | _           | _      | _       | D      | MA1IP<2:   | )>                  | _     | AD1IP<2:0>            |             |         | _                   | U1TXIP<2:0>           |            | >       | 0444          |

| IPC4        | 00AC        | _      | (      | CNIP<2:0>   |        | _       |        | CMIP<2:0   | <b>`</b>            | _     | I                     | MI2C1IP<2:0 | >       | _                   | SI                    | 2C1IP<2:0  | >       | 4444          |

| IPC5        | 00AE        | _      | I      | C8IP<2:0>   |        | _       |        | IC7IP<2:0  | <b>`</b>            | _     | _                     | _           | _       | _                   | IN                    | IT1IP<2:0> |         | 4404          |

| IPC6        | 00B0        | —      |        | T4IP<2:0>   |        |         | (      | OC4IP<2:0  | >                   | —     |                       | OC3IP<2:0>  |         | —                   | DN                    | /A2IP<2:0  | >       | 4444          |

| IPC7        | 00B2        | —      | U      | 2TXIP<2:0>  | >      |         | L      | J2RXIP<2:( | )>                  | —     |                       | INT2IP<2:0> | •       | —                   | ٦                     | [5IP<2:0>  |         | 4444          |

| IPC8        | 00B4        | —      | С      | 1IP<2:0>(1) | )      |         | C,     | 1RXIP<2:0  | <sub>&gt;</sub> (1) | —     |                       | SPI2IP<2:0> | •       | —                   | SF                    | PI2EIP<2:0 | >       | 4444          |

| IPC9        | 00B6        | —      | —      |             |        |         | —      | —          |                     | —     | —                     |             |         | —                   | DN                    | /A3IP<2:0  | >       | 0004          |

| IPC11       | 00BA        | —      | —      |             |        |         | D      | MA4IP<2:   | )>                  | —     |                       | PMPIP<2:0>  | •       | —                   | _                     | —          | _       | 0440          |

| IPC15       | 00C2        | —      | _      | —           |        |         |        | RTCIP<2:0  | >                   | —     |                       | DMA5IP<2:0  | >       | -                   | _                     | _          | —       | 0440          |

| IPC16       | 00C4        | —      | С      | RCIP<2:0>   |        |         |        | U2EIP<2:0  | >                   | —     |                       | U1EIP<2:0>  |         | -                   | _                     | —          | —       | 4440          |

| IPC17       | 00C6        | —      | _      | —           |        |         | C      | 1TXIP<2:0  | <b>(</b> 1)         | —     |                       | DMA7IP<2:0  | >       | -                   | — DMA6IP<2:0>         |            | 0444    |               |

| INTTREG     | 00E0        | —      | _      | —           |        |         | ILR<   | 3:0>       |                     | —     |                       |             | VEC     | CNUM<6:0>           |                       |            |         | 4444          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: Interrupts disabled on devices without ECAN™ modules.

# TABLE 4-20:PERIPHERAL PIN SELECT OUTPUT REGISTER MAP FOR PIC24HJ128GP202/502, PIC24HJ64GP202/502 AND<br/>PIC24HJ32GP302

| File Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11     | Bit 10    | Bit 9 | Bit 8 | Bit 7 | Bit 6     | Bit 5 | Bit 4      | Bit 3 | Bit 2      | Bit 1 | Bit 0 | All<br>Resets |

|-----------|------|--------|--------|--------|--------|------------|-----------|-------|-------|-------|-----------|-------|------------|-------|------------|-------|-------|---------------|

| RPOR0     | 06C0 | -      | _      | —      |        | RP1R<4:0>  |           |       |       |       | —         | —     | RP0R<4:0>  |       |            |       |       | 0000          |

| RPOR1     | 06C2 | _      | _      | _      |        |            | RP3R<4:0  | _     | _     | _     | RP2R<4:0> |       |            |       |            | 0000  |       |               |

| RPOR2     | 06C4 |        | —      | _      |        |            | RP5R<4:0> | >     |       | _     | —         | _     | RP4R<4:0>  |       |            |       |       | 0000          |

| RPOR3     | 06C6 |        | _      | _      |        |            | RP7R<4:0> | >     |       | _     | _         | _     |            |       | RP6R<4:0>  |       |       | 0000          |

| RPOR4     | 06C8 | -      | _      | _      |        |            | RP9R<4:0> | >     |       | —     | _         | _     | RP8R<4:0>  |       |            |       | 0000  |               |

| RPOR5     | 06CA | _      | _      | _      |        | RP11R<4:0> |           |       |       |       | _         | _     | RP10R<4:0> |       |            |       | 0000  |               |

| RPOR6     | 06CC |        | —      | _      |        | RP13R<4:0> |           |       |       |       | —         | —     | RP12R<4:0> |       |            |       |       | 0000          |

| RPOR7     | 06CE | -      | _      | _      |        | RP15R<4:0> |           |       |       | _     | _         | _     |            | I     | RP14R<4:0> |       |       | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# TABLE 4-21:PERIPHERAL PIN SELECT OUTPUT REGISTER MAP FOR PIC24HJ128GP204/504, PIC24HJ64GP204/504 AND<br/>PIC24HJ32GP304

|           |      |        |        |        |                             |                       |           |       |       |       |       |       |            |       |            | -     |       |               |

|-----------|------|--------|--------|--------|-----------------------------|-----------------------|-----------|-------|-------|-------|-------|-------|------------|-------|------------|-------|-------|---------------|

| File Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12                      | Bit 11                | Bit 10    | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4      | Bit 3 | Bit 2      | Bit 1 | Bit 0 | All<br>Resets |

| RPOR0     | 06C0 | _      | _      | _      |                             |                       | RP1R<4:0> | >     |       | _     | —     |       |            |       | RP0R<4:0>  |       |       | 0000          |

| RPOR1     | 06C2 | _      | _      | _      |                             | RP3R<4:0>             |           |       |       |       | _     | _     | RP2R<4:0>  |       |            |       | 0000  |               |

| RPOR2     | 06C4 | _      | _      | _      |                             | RP5R<4:0>             |           |       |       |       | _     | _     | RP4R<4:0>  |       |            |       |       | 0000          |

| RPOR3     | 06C6 | _      | _      | _      |                             | RP7R<4:0>             |           |       |       |       | _     | _     | RP6R<4:0>  |       |            |       |       | 0000          |

| RPOR4     | 06C8 |        |        | _      |                             | RP9R<4:0>             |           |       |       |       |       | _     | RP8R<4:0>  |       |            |       |       | 0000          |

| RPOR5     | 06CA |        |        | _      |                             | RP11R<4:0>            |           |       |       | _     |       | _     | RP10R<4:0> |       |            |       |       | 0000          |

| RPOR6     | 06CC |        |        |        |                             |                       | RP13R<4:0 | >     |       | _     |       |       | RP12R<4:0> |       |            |       | 0000  |               |

| RPOR7     | 06CE | _      | _      | _      |                             |                       | RP15R<4:0 | >     |       | _     | _     | _     | RP14R<4:0> |       |            |       |       | 0000          |

| RPOR8     | 06D0 | _      | _      | _      |                             |                       | RP17R<4:0 | >     |       | _     | _     | _     | RP16R<4:0> |       |            |       | 0000  |               |

| RPOR9     | 06D2 |        |        |        |                             |                       | RP19R<4:0 | >     |       | _     | _     |       |            |       | RP18R<4:0> | >     |       | 0000          |

| RPOR10    | 06D4 |        |        |        |                             | RP21R<4:0>            |           |       |       | _     | _     |       | RP20R<4:0> |       |            |       | 0000  |               |

| RPOR11    | 06D6 |        |        |        | RP23R<4:0> — — — RP22R<4:0> |                       |           |       |       |       | 0000  |       |            |       |            |       |       |               |

| RPOR12    | 06D8 |        | _      | _      |                             | RP25R<4:0> RP24R<4:0> |           |       |       |       |       | 0000  |            |       |            |       |       |               |

Legend: x = unknown value on Reset, -- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

NVMCON: FLASH MEMORY CONTROL REGISTER

## 5.6 Flash Memory Control Registers

**REGISTER 5-1:**

| R/SO-0 <sup>(1)</sup> | R/W-0 <sup>(1)</sup>            | R/W-0 <sup>(1)</sup>            |                |                                                                          |                                       |                      |                      |

|-----------------------|---------------------------------|---------------------------------|----------------|--------------------------------------------------------------------------|---------------------------------------|----------------------|----------------------|

| WR                    | R/W-000                         | WRERR                           | U-0            | U-0                                                                      | U-0                                   | U-0                  | U-0                  |

|                       | WREN                            | WRERR                           | —              | _                                                                        | —                                     |                      |                      |

| bit 15                |                                 |                                 |                |                                                                          |                                       |                      | bit 8                |

| U-0                   | R/W-0 <sup>(1)</sup>            | U-0                             | U-0            | R/W-0 <sup>(1)</sup>                                                     | R/W-0 <sup>(1)</sup>                  | R/W-0 <sup>(1)</sup> | R/W-0 <sup>(1)</sup> |

| _                     | ERASE                           |                                 | _              |                                                                          | NVMOP                                 | <3:0> <sup>(2)</sup> |                      |

| bit 7                 | ·                               |                                 |                |                                                                          |                                       |                      | bit 0                |

| Legend:               |                                 | SO = Settal                     | ole only bit   |                                                                          |                                       |                      |                      |

| R = Readable          | bit                             | W = Writabl                     | e bit          | U = Unimpler                                                             | mented bit, read                      | as '0'               |                      |

| -n = Value at F       | POR                             | '1' = Bit is s                  | et             | '0' = Bit is cle                                                         | ared                                  | x = Bit is unkr      | nown                 |

| bit 15                | WR: Write Con                   | trol bit                        |                |                                                                          |                                       |                      |                      |

|                       | 1 = Initiates a                 | Flash memor                     | y program or   | erase operation                                                          | on. The operatio                      | on is self-timed     | and the bit is       |

|                       |                                 | hardware on                     |                |                                                                          |                                       |                      |                      |

|                       | 0 = Program of                  | •                               | tion is comple | ete and inactive                                                         | 9                                     |                      |                      |

| bit 14                | WREN: Write E                   |                                 |                |                                                                          |                                       |                      |                      |

|                       | 1 = Enable Fla                  |                                 |                |                                                                          |                                       |                      |                      |

| h:: 40                | 0 = Inhibit Flas                |                                 | -              | IS                                                                       |                                       |                      |                      |

| bit 13                | WRERR: Write                    | •                               | •              |                                                                          | · · · · · · · · · · · · · · · · · · · |                      |                      |

|                       |                                 | er program or<br>ally on any se |                |                                                                          | termination has                       | occurred (bit i      | s set                |

|                       | 0 = The progra                  |                                 |                |                                                                          | /                                     |                      |                      |

| bit 12-7              | Unimplemente                    |                                 |                |                                                                          |                                       |                      |                      |

| bit 6                 | ERASE: Erase                    |                                 |                |                                                                          |                                       |                      |                      |

| 2.00                  |                                 | •                               |                | bv NVMOP </td <td>3:0&gt; on the next</td> <td>WR command</td> <td></td> | 3:0> on the next                      | WR command           |                      |

|                       |                                 |                                 |                |                                                                          | ><3:0> on the network                 |                      |                      |

| bit 5-4               | Unimplemente                    | d: Read as '                    | )'             |                                                                          |                                       |                      |                      |

| bit 3-0               | NVMOP<3:0>:                     | NVM Operati                     | on Select bits | <sub>S</sub> (2)                                                         |                                       |                      |                      |

|                       | If ERASE = 1:                   |                                 |                |                                                                          |                                       |                      |                      |

|                       | 1111 <b>= Memor</b>             | •                               | operation      |                                                                          |                                       |                      |                      |

|                       | 1110 = Reserv                   |                                 |                |                                                                          |                                       |                      |                      |

|                       | 1101 = Erase (                  | •                               |                |                                                                          |                                       |                      |                      |

|                       | 1100 = Erase S<br>1011 = Reserv |                                 | ent            |                                                                          |                                       |                      |                      |

|                       | 0011 = No ope                   |                                 |                |                                                                          |                                       |                      |                      |

|                       | 0010 = Memor                    |                                 | operation      |                                                                          |                                       |                      |                      |

|                       | 0001 = No ope                   |                                 |                |                                                                          |                                       |                      |                      |

|                       | 0000 <b>= Erase</b> a           | a single Confi                  | guration regis | ster byte                                                                |                                       |                      |                      |

|                       | If ERASE = 0:                   |                                 |                |                                                                          |                                       |                      |                      |

|                       | 1111 <b>= No ope</b>            |                                 |                |                                                                          |                                       |                      |                      |

|                       | 1110 = Reserv                   |                                 |                |                                                                          |                                       |                      |                      |

|                       | 1101 = No ope<br>1100 = No ope  |                                 |                |                                                                          |                                       |                      |                      |

|                       | 1011 = Reserv                   |                                 |                |                                                                          |                                       |                      |                      |

|                       | 0011 = Memor                    | y word progra                   | m operation    |                                                                          |                                       |                      |                      |

|                       | 0010 = No ope                   | ration                          |                |                                                                          |                                       |                      |                      |

|                       | 0001 = Memory                   |                                 |                |                                                                          |                                       |                      |                      |

|                       | 0000 <b>= Progra</b> r          | n a single Co                   | nfiguration re | gister byte                                                              |                                       |                      |                      |

| Note 1: The           | ese bits can only               | be reset on a                   | POR.           |                                                                          |                                       |                      |                      |

| 2: All                | other combination               | ns of NVMOF                     | <3:0> are un   | implemented                                                              |                                       |                      |                      |

2: All other combinations of NVMOP<3:0> are unimplemented.

## **REGISTER 6-1: RCON: RESET CONTROL REGISTER<sup>(1)</sup> (CONTINUED)**

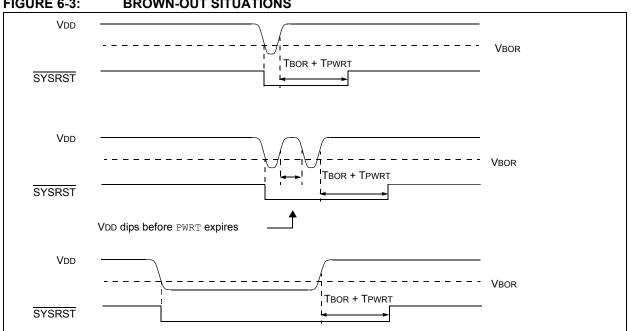

- bit 1BOR: Brown-out Reset Flag bit1 = A Brown-out Reset has occurred0 = A Brown-out Reset has not occurredbit 0POR: Power-on Reset Flag bit

- 1 = A Power-on Reset has occurred

0 = A Power-on Reset has not occurred

- **Note 1:** All of the Reset status bits can be set or cleared in software. Setting one of these bits in software does not cause a device Reset.

- 2: If the FWDTEN Configuration bit is '1' (unprogrammed), the WDT is always enabled, regardless of the SWDTEN bit setting.

#### **BROWN-OUT SITUATIONS** FIGURE 6-3:

#### 6.5 **External Reset (EXTR)**

The external Reset is generated by driving the MCLR pin low. The MCLR pin is a Schmitt trigger input with an additional glitch filter. Reset pulses that are longer than the minimum pulse width will generate a Reset. Refer to Section 28.0 "Electrical Characteristics" for minimum pulse width specifications. The External Reset (MCLR) Pin (EXTR) bit in the Reset Control (RCON) register is set to indicate the MCLR Reset.

#### 6.5.1 EXTERNAL SUPERVISORY CIRCUIT

Many systems have external supervisory circuits that generate reset signals to reset multiple devices in the system. This external Reset signal can be directly connected to the MCLR pin to reset the device when the rest of system is Reset.

#### 6.5.2 INTERNAL SUPERVISORY CIRCUIT

When using the internal power supervisory circuit to reset the device, the external reset pin (MCLR) should be tied directly or resistively to VDD. In this case, the MCLR pin will not be used to generate a Reset. The external reset pin (MCLR) does not have an internal pull-up and must not be left unconnected.

#### 6.6 Software RESET Instruction (SWR)

Whenever the RESET instruction is executed, the device will assert SYSRST, placing the device in a special Reset state. This Reset state will not reinitialize the clock. The clock source in effect prior to the RESET instruction will remain. SYSRST is released at the next instruction cycle, and the reset vector fetch will commence.

The Software Reset (Instruction) Flag bit (SWR) in the Reset Control register (RCON<6>) is set to indicate the software Reset.

#### 6.7 Watchdog Time-out Reset (WDTO)

Whenever a Watchdog time-out occurs, the device will asynchronously assert SYSRST. The clock source will remain unchanged. A WDT time-out during Sleep or Idle mode will wake-up the processor, but will not reset the processor.

The Watchdog Timer Time-out Flag bit (WDTO) in the Reset Control register (RCON<4>) is set to indicate the Watchdog Reset. Refer to Section 25.4 "Watchdog Timer (WDT)" for more information on Watchdog Reset.

#### 6.8 Trap Conflict Reset

If a lower-priority hard trap occurs while a higher-priority trap is being processed, a hard trap conflict Reset occurs. The hard traps include exceptions of priority level 13 through level 15, inclusive. The address error (level 13) and oscillator error (level 14) traps fall into this category.

The Trap Reset Flag bit (TRAPR) in the Reset Control register (RCON<15>) is set to indicate the Trap Conflict Reset. Refer to Section 7.0 "Interrupt Controller" for more information on trap conflict Resets.

| REGISTER 7              | -5: IFS0:                                                                                                                                                        | INTERRUPT                                                                                                                                   | FLAG STAT                                                                                                                                             | US REGISTE        | R U              |                 |        |

|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|------------------|-----------------|--------|

| U-0                     | R/W-0                                                                                                                                                            | R/W-0                                                                                                                                       | R/W-0                                                                                                                                                 | R/W-0             | R/W-0            | R/W-0           | R/W-0  |

| —                       | DMA1IF                                                                                                                                                           | AD1IF                                                                                                                                       | U1TXIF                                                                                                                                                | U1RXIF            | SPI1IF           | SPI1EIF         | T3IF   |

| pit 15                  |                                                                                                                                                                  |                                                                                                                                             |                                                                                                                                                       |                   |                  |                 | bit    |

| R/W-0                   | R/W-0                                                                                                                                                            | R/W-0                                                                                                                                       | R/W-0                                                                                                                                                 | R/W-0             | R/W-0            | R/W-0           | R/W-0  |

| T2IF                    | OC2IF                                                                                                                                                            | IC2IF                                                                                                                                       | DMA0IF                                                                                                                                                | T1IF              | OC1IF            | IC1IF           | INTOIF |

| bit 7                   | 00211                                                                                                                                                            | 10211                                                                                                                                       | Division                                                                                                                                              |                   | 00111            | 10111           | bit    |

| Legend:                 |                                                                                                                                                                  |                                                                                                                                             |                                                                                                                                                       |                   |                  |                 |        |

| R = Readable            | bit                                                                                                                                                              | W = Writable                                                                                                                                | bit                                                                                                                                                   | U = Unimplem      | nented bit, read | d as '0'        |        |

| -n = Value at P         |                                                                                                                                                                  | '1' = Bit is set                                                                                                                            |                                                                                                                                                       | '0' = Bit is clea |                  | x = Bit is unkn | own    |

|                         |                                                                                                                                                                  |                                                                                                                                             |                                                                                                                                                       |                   |                  |                 |        |

| bit 15                  | Unimplemer                                                                                                                                                       | nted: Read as '                                                                                                                             | 0'                                                                                                                                                    |                   |                  |                 |        |

| bit 14                  | DMA1IF: DM                                                                                                                                                       | 1A Channel 1 D                                                                                                                              | ata Transfer C                                                                                                                                        | omplete Interru   | upt Flag Status  | bit             |        |

|                         | 1 = Interrupt                                                                                                                                                    | request has oc<br>request has no                                                                                                            | curred                                                                                                                                                |                   |                  |                 |        |

| bit 13                  | AD1IF: ADC                                                                                                                                                       | 1 Conversion C                                                                                                                              | complete Interr                                                                                                                                       | upt Flag Status   | bit              |                 |        |

|                         |                                                                                                                                                                  | request has oc<br>request has no                                                                                                            |                                                                                                                                                       |                   |                  |                 |        |

| bit 12                  | •                                                                                                                                                                | RT1 Transmitte                                                                                                                              |                                                                                                                                                       | s Status hit      |                  |                 |        |

| 21C 12                  |                                                                                                                                                                  | request has oc                                                                                                                              |                                                                                                                                                       | g olalas bit      |                  |                 |        |

|                         |                                                                                                                                                                  | request has no                                                                                                                              |                                                                                                                                                       |                   |                  |                 |        |

| bit 11                  | U1RXIF: UA                                                                                                                                                       | RT1 Receiver I                                                                                                                              | nterrupt Flag S                                                                                                                                       | Status bit        |                  |                 |        |

|                         | •                                                                                                                                                                | request has oc                                                                                                                              |                                                                                                                                                       |                   |                  |                 |        |

|                         | -                                                                                                                                                                | request has no                                                                                                                              |                                                                                                                                                       |                   |                  |                 |        |

| oit 10                  |                                                                                                                                                                  | Event Interrup                                                                                                                              | •                                                                                                                                                     | bit               |                  |                 |        |

|                         |                                                                                                                                                                  | request has oc<br>request has no                                                                                                            |                                                                                                                                                       |                   |                  |                 |        |

| bit 9                   | -                                                                                                                                                                | 11 Error Interru                                                                                                                            |                                                                                                                                                       | bit               |                  |                 |        |

|                         |                                                                                                                                                                  | request has oc                                                                                                                              |                                                                                                                                                       |                   |                  |                 |        |

|                         | 0 = Interrupt                                                                                                                                                    | request has no                                                                                                                              | t occurred                                                                                                                                            |                   |                  |                 |        |

| bit 8                   |                                                                                                                                                                  | Interrupt Flag                                                                                                                              |                                                                                                                                                       |                   |                  |                 |        |

|                         |                                                                                                                                                                  | request has oc                                                                                                                              |                                                                                                                                                       |                   |                  |                 |        |

| hit 7                   |                                                                                                                                                                  | request has no                                                                                                                              |                                                                                                                                                       |                   |                  |                 |        |

| bit 7                   |                                                                                                                                                                  | Interrupt Flag                                                                                                                              | Status Dit                                                                                                                                            |                   |                  |                 |        |

|                         |                                                                                                                                                                  | rogulaet hae on                                                                                                                             |                                                                                                                                                       |                   |                  |                 |        |

|                         |                                                                                                                                                                  | request has oc<br>request has no                                                                                                            | curred                                                                                                                                                |                   |                  |                 |        |

| bit 6                   | 0 = Interrupt                                                                                                                                                    |                                                                                                                                             | curred<br>t occurred                                                                                                                                  | upt Flag Status   | bit              |                 |        |

| bit 6                   | 0 = Interrupt<br>OC2IF: Outp                                                                                                                                     | request has no                                                                                                                              | curred<br>t occurred<br>nannel 2 Interro                                                                                                              | upt Flag Status   | bit              |                 |        |

|                         | <ul> <li>0 = Interrupt</li> <li>OC2IF: Outp</li> <li>1 = Interrupt</li> <li>0 = Interrupt</li> </ul>                                                             | request has no<br>out Compare Ch<br>request has oc<br>request has no                                                                        | curred<br>t occurred<br>hannel 2 Interru<br>curred<br>t occurred                                                                                      |                   | bit              |                 |        |

|                         | 0 = Interrupt<br>OC2IF: Outp<br>1 = Interrupt<br>0 = Interrupt<br>IC2IF: Input                                                                                   | request has no<br>out Compare Ch<br>request has oc<br>request has no<br>Capture Chann                                                       | curred<br>t occurred<br>nannel 2 Interro<br>curred<br>t occurred<br>el 2 Interrupt F                                                                  |                   | bit              |                 |        |

|                         | <ul> <li>0 = Interrupt</li> <li>OC2IF: Outp</li> <li>1 = Interrupt</li> <li>0 = Interrupt</li> <li>IC2IF: Input</li> <li>1 = Interrupt</li> </ul>                | request has no<br>out Compare Ch<br>request has oc<br>request has no<br>Capture Chann<br>request has oc                                     | curred<br>t occurred<br>hannel 2 Intern<br>curred<br>t occurred<br>el 2 Interrupt F<br>curred                                                         |                   | bit              |                 |        |

| bit 5                   | 0 = Interrupt<br><b>OC2IF:</b> Outp<br>1 = Interrupt<br>0 = Interrupt<br><b>IC2IF:</b> Input 0<br>1 = Interrupt<br>0 = Interrupt                                 | request has no<br>out Compare Ch<br>request has oc<br>request has no<br>Capture Chann<br>request has oc<br>request has no                   | curred<br>t occurred<br>hannel 2 Intern<br>curred<br>t occurred<br>el 2 Interrupt F<br>curred<br>t occurred                                           | lag Status bit    |                  | bit             |        |

| bit 5                   | 0 = Interrupt<br>OC2IF: Outp<br>1 = Interrupt<br>0 = Interrupt<br>IC2IF: Input<br>1 = Interrupt<br>0 = Interrupt<br>DMA0IF: DM                                   | request has no<br>out Compare Ch<br>request has no<br>Capture Chann<br>request has no<br>request has no<br>IA Channel 0 D                   | curred<br>t occurred<br>hannel 2 Interru<br>curred<br>t occurred<br>el 2 Interrupt F<br>curred<br>t occurred<br>hata Transfer C                       | lag Status bit    |                  | bit             |        |

| bit 6<br>bit 5<br>bit 4 | 0 = Interrupt<br>OC2IF: Outp<br>1 = Interrupt<br>0 = Interrupt<br>IC2IF: Input<br>1 = Interrupt<br>0 = Interrupt<br>DMA0IF: DM<br>1 = Interrupt                  | request has no<br>out Compare Ch<br>request has oc<br>request has no<br>Capture Chann<br>request has oc<br>request has no                   | curred<br>t occurred<br>hannel 2 Interru<br>curred<br>t occurred<br>el 2 Interrupt F<br>curred<br>t occurred<br>hata Transfer C<br>curred             | lag Status bit    |                  | bit             |        |

| bit 5                   | 0 = Interrupt<br>OC2IF: Outp<br>1 = Interrupt<br>0 = Interrupt<br>IC2IF: Input<br>1 = Interrupt<br>0 = Interrupt<br>DMA0IF: DM<br>1 = Interrupt<br>0 = Interrupt | request has no<br>out Compare Ch<br>request has no<br>Capture Chann<br>request has no<br>request has no<br>IA Channel 0 D<br>request has no | curred<br>t occurred<br>hannel 2 Intern<br>curred<br>t occurred<br>el 2 Interrupt F<br>curred<br>t occurred<br>ata Transfer C<br>curred<br>t occurred | lag Status bit    |                  | bit             |        |

#### IEGA, INTERDURT EL AC STATUS DECISTER A

| REGISTER 8      | -7: DMAC                          | S0: DMA CO                                             | NTROLLER        | STATUS RE                          | GISTER 0    |                 |        |  |  |  |

|-----------------|-----------------------------------|--------------------------------------------------------|-----------------|------------------------------------|-------------|-----------------|--------|--|--|--|

| R/C-0           | R/C-0                             | R/C-0                                                  | R/C-0           | R/C-0                              | R/C-0       | R/C-0           | R/C-0  |  |  |  |

| PWCOL7          | PWCOL6                            | PWCOL5                                                 | PWCOL4          | PWCOL3                             | PWCOL2      | PWCOL1          | PWCOL0 |  |  |  |

| bit 15          |                                   |                                                        |                 |                                    |             |                 | bit 8  |  |  |  |

| R/C-0           | R/C-0                             | R/C-0                                                  | R/C-0           | R/C-0                              | R/C-0       | R/C-0           | R/C-0  |  |  |  |

| XWCOL7          | XWCOL6                            | XWCOL5                                                 | XWCOL4          | XWCOL3                             | XWCOL2      | XWCOL1          | XWCOL0 |  |  |  |

| bit 7           |                                   |                                                        |                 |                                    |             |                 | bit    |  |  |  |

| Legend:         |                                   |                                                        |                 | C = Cle                            | ar only bit |                 |        |  |  |  |

| R = Readable    | bit                               | W = Writable                                           | bit             | U = Unimplemented bit, read as '0' |             |                 |        |  |  |  |

| -n = Value at I |                                   | '1' = Bit is set                                       |                 | '0' = Bit is cle                   |             | x = Bit is unkr | าดพท   |  |  |  |

|                 |                                   |                                                        |                 |                                    |             |                 |        |  |  |  |

| bit 15          | 1 = Write colli                   | nannel 7 Periph<br>ision detected<br>collision detecte |                 | llision Flag bit                   |             |                 |        |  |  |  |

| bit 14          | 1 = Write colli                   | nannel 6 Periph<br>ision detected<br>collision detecte |                 | llision Flag bit                   |             |                 |        |  |  |  |

| bit 13          | 1 = Write colli                   | nannel 5 Periph<br>ision detected<br>collision detecte |                 | llision Flag bit                   |             |                 |        |  |  |  |

| bit 12          | PWCOL4: Ch                        | nannel 4 Periph                                        | neral Write Co  | llision Flag bit                   |             |                 |        |  |  |  |

|                 |                                   | ision detected collision detected                      | ed              |                                    |             |                 |        |  |  |  |

| bit 11          | PWCOL3: Ch                        | nannel 3 Periph                                        | neral Write Col | llision Flag bit                   |             |                 |        |  |  |  |

|                 |                                   | ision detected collision detected                      | ed              |                                    |             |                 |        |  |  |  |

| bit 10          | 1 = Write colli                   | nannel 2 Periph<br>ision detected<br>collision detecte |                 | llision Flag bit                   |             |                 |        |  |  |  |

| bit 9           | 1 = Write colli                   | nannel 1 Periph<br>ision detected<br>collision detecte |                 | llision Flag bit                   |             |                 |        |  |  |  |

| bit 8           | 1 = Write colli                   | nannel 0 Periph<br>ision detected<br>collision detecte |                 | llision Flag bit                   |             |                 |        |  |  |  |

| bit 7           |                                   | nannel 7 DMA I                                         | RAM Write Co    | Ilision Flag bit                   |             |                 |        |  |  |  |

|                 |                                   | ision detected<br>collision detecte                    | ed              |                                    |             |                 |        |  |  |  |

| bit 6           | XWCOL6: Ch                        | nannel 6 DMA I                                         | RAM Write Co    | Ilision Flag bit                   |             |                 |        |  |  |  |

|                 |                                   | ision detected collision detected                      | ed              |                                    |             |                 |        |  |  |  |

| bit 5           | XWCOL5: Ch                        | nannel 5 DMA I                                         | RAM Write Co    | Ilision Flag bit                   |             |                 |        |  |  |  |

|                 | 1 = Write colli<br>0 = No write c | ision detected collision detected                      | ed              |                                    |             |                 |        |  |  |  |

| bit 4           | XWCOL4: Cr                        | nannel 4 DMA I                                         | RAM Write Co    | Ilision Flag bit                   |             |                 |        |  |  |  |

|                 |                                   | ision detected<br>collision detecte                    | ed              | -                                  |             |                 |        |  |  |  |

## PIC24HJ32GP302/304, PIC24HJ64GPX02/X04 AND PIC24HJ128GPX02/X04

| R/W-0        | R/W-0                                     | U-0                                                                                                                                                        | U-0                    | U-0               | U-0              | R/W-0           | R/W-0 |  |  |  |  |  |  |  |

|--------------|-------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|-------------------|------------------|-----------------|-------|--|--|--|--|--|--|--|

| IC8MD        | IC7MD                                     |                                                                                                                                                            | _                      | —                 | _                | IC2MD           | IC1MD |  |  |  |  |  |  |  |

| bit 15       |                                           |                                                                                                                                                            |                        |                   |                  |                 | bit 8 |  |  |  |  |  |  |  |

|              |                                           |                                                                                                                                                            |                        |                   |                  |                 |       |  |  |  |  |  |  |  |

| U-0          | U-0                                       | U-0                                                                                                                                                        | U-0                    | R/W-0             | R/W-0            | R/W-0           | R/W-0 |  |  |  |  |  |  |  |

|              | —                                         | —                                                                                                                                                          | —                      | OC4MD             | OC3MD            | OC2MD           | OC1MD |  |  |  |  |  |  |  |

| bit 7        |                                           |                                                                                                                                                            |                        |                   |                  |                 | bit   |  |  |  |  |  |  |  |

| Legend:      |                                           |                                                                                                                                                            |                        |                   |                  |                 |       |  |  |  |  |  |  |  |

| R = Readab   | le bit                                    | W = Writable                                                                                                                                               | bit                    | U = Unimplen      | nented bit, read | d as '0'        |       |  |  |  |  |  |  |  |

| -n = Value a | t POR                                     | '1' = Bit is se                                                                                                                                            | t                      | '0' = Bit is clea |                  | x = Bit is unkr | nown  |  |  |  |  |  |  |  |

|              |                                           |                                                                                                                                                            |                        |                   |                  |                 |       |  |  |  |  |  |  |  |

| bit 15       | IC8MD: Inpu                               | it Capture 8 Mo                                                                                                                                            | dule Disable bi        | it                |                  |                 |       |  |  |  |  |  |  |  |

|              |                                           | pture 8 module                                                                                                                                             |                        |                   |                  |                 |       |  |  |  |  |  |  |  |

|              | •                                         | pture 8 module                                                                                                                                             |                        |                   |                  |                 |       |  |  |  |  |  |  |  |

| bit 14       |                                           |                                                                                                                                                            |                        |                   |                  |                 |       |  |  |  |  |  |  |  |

|              |                                           |                                                                                                                                                            |                        |                   |                  |                 |       |  |  |  |  |  |  |  |

| bit 13-10    | •                                         | IC7MD: Input Capture 2 Module Disable bit<br>1 = Input Capture 7 module is disabled<br>0 = Input Capture 7 module is enabled<br>Unimplemented: Read as '0' |                        |                   |                  |                 |       |  |  |  |  |  |  |  |

| bit 9        | •                                         | It Capture 2 Mo                                                                                                                                            |                        | t                 |                  |                 |       |  |  |  |  |  |  |  |

| bit 9        | •                                         | pture 2 module                                                                                                                                             |                        | it.               |                  |                 |       |  |  |  |  |  |  |  |

|              |                                           | pture 2 module                                                                                                                                             |                        |                   |                  |                 |       |  |  |  |  |  |  |  |

| bit 8        | IC1MD: Input Capture 1 Module Disable bit |                                                                                                                                                            |                        |                   |                  |                 |       |  |  |  |  |  |  |  |

|              |                                           | 1 = Input Capture 1 module is disabled                                                                                                                     |                        |                   |                  |                 |       |  |  |  |  |  |  |  |

|              | 0 = Input Ca                              | pture 1 module                                                                                                                                             | is enabled             |                   |                  |                 |       |  |  |  |  |  |  |  |

| bit 7-4      | Unimpleme                                 | nted: Read as                                                                                                                                              | '0'                    |                   |                  |                 |       |  |  |  |  |  |  |  |

| bit 3        |                                           | tput Compare 4                                                                                                                                             |                        | le bit            |                  |                 |       |  |  |  |  |  |  |  |

|              |                                           | Compare 4 mod<br>Compare 4 mod                                                                                                                             |                        |                   |                  |                 |       |  |  |  |  |  |  |  |

| bit 2        | •                                         | tput Compare 3                                                                                                                                             |                        | le hit            |                  |                 |       |  |  |  |  |  |  |  |

|              |                                           | Compare 3 mod                                                                                                                                              |                        |                   |                  |                 |       |  |  |  |  |  |  |  |

|              |                                           | Compare 3 mod                                                                                                                                              |                        |                   |                  |                 |       |  |  |  |  |  |  |  |

| bit 1        | OC2MD: Ou                                 | tput Compare 2                                                                                                                                             | 2 Module Disab         | le bit            |                  |                 |       |  |  |  |  |  |  |  |

|              | 1 = Output C                              | Compare 2 mod                                                                                                                                              | ule is disabled        |                   |                  |                 |       |  |  |  |  |  |  |  |

|              | 0 = Output C                              | Compare 2 mod                                                                                                                                              | ule is enabled         |                   |                  |                 |       |  |  |  |  |  |  |  |