# E·XFL

#### Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

# Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Active                                                                        |

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 40 MIPs                                                                       |

| Connectivity               | I <sup>2</sup> C, PMP, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                    |

| Number of I/O              | 21                                                                            |

| Program Memory Size        | 32KB (11K x 24)                                                               |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 4K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                     |

| Data Converters            | A/D 10x10b/12b                                                                |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                            |

| Mounting Type              | Through Hole                                                                  |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                       |

| Supplier Device Package    | 28-SPDIP                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24hj32gp302-e-sp |

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Table of Contents**

| PIC2  | 4HJ32GP302/304, PIC24HJ64GPX02/X04 and PIC24HJ128GPX02/X04 Product Families |     |

|-------|-----------------------------------------------------------------------------|-----|

| 1.0   | Device Overview                                                             |     |

| 2.0   | Guidelines for Getting Started with 16-bit Microcontrollers                 |     |

| 3.0   | СРИ                                                                         |     |

| 4.0   | Memory Organization                                                         |     |

| 5.0   | Flash Program Memory                                                        |     |

| 6.0   | Resets                                                                      |     |

| 7.0   | Interrupt Controller                                                        |     |

| 8.0   | Direct Memory Access (DMA)                                                  | 107 |

| 9.0   | Oscillator Configuration                                                    | 119 |

| 10.0  | Power-Saving Features                                                       | 129 |

| 11.0  | I/O Ports                                                                   | 135 |

| 12.0  | Timer1                                                                      | 161 |

| 13.0  |                                                                             |     |

| 14.0  | Input Capture                                                               |     |

| 15.0  | Output Compare                                                              | 175 |

| 16.0  | Serial Peripheral Interface (SPI)                                           | 179 |

| 17.0  | Inter-Integrated Circuit™ (I <sup>2</sup> C™)                               | 185 |

| 18.0  | Universal Asynchronous Receiver Transmitter (UART)                          | 193 |

| 19.0  | Enhanced CAN (ECAN™) Module                                                 | 199 |

| 20.0  | 10-bit/12-bit Analog-to-Digital Converter (ADC1)                            |     |

| 21.0  | Comparator Module                                                           |     |

| 22.0  | Real-Time Clock and Calendar (RTCC)                                         |     |

| 23.0  | Programmable Cyclic Redundancy Check (CRC) Generator                        |     |

| 24.0  | Parallel Master Port (PMP)                                                  |     |

|       | Special Features                                                            |     |

| 26.0  | Instruction Set Summary                                                     |     |

| 27.0  | Development Support                                                         |     |

|       | Electrical Characteristics                                                  |     |

| 29.0  | High Temperature Electrical Characteristics                                 |     |

| 32.0  | DC and AC Device Characteristics Graphs                                     |     |

| 33.0  | Packaging Information                                                       |     |

| Appe  | endix A: Revision History                                                   |     |

| The I | Microchip Web Site                                                          |     |

| Custo | omer Change Notification Service                                            |     |

| Custo | omer Support                                                                |     |

| Read  | ler Response                                                                |     |

| Prod  | uct Identification System                                                   |     |

# TABLE 4-7: OUTPUT COMPARE REGISTER MAP

|          |             |        |                                                                                  |                                          |        |        |        |       |             |             |              |       |       |        |       |          |       | -             |

|----------|-------------|--------|----------------------------------------------------------------------------------|------------------------------------------|--------|--------|--------|-------|-------------|-------------|--------------|-------|-------|--------|-------|----------|-------|---------------|

| SFR Name | SFR<br>Addr | Bit 15 | Bit 14                                                                           | Bit 13                                   | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8       | Bit 7       | Bit 6        | Bit 5 | Bit 4 | Bit 3  | Bit 2 | Bit 1    | Bit 0 | All<br>Resets |

| OC1RS    | 0180        |        |                                                                                  |                                          |        |        |        | Ou    | tput Compar | e 1 Seconda | ary Register |       |       |        |       |          |       | xxxx          |

| OC1R     | 0182        |        |                                                                                  |                                          |        |        |        |       | Output Co   | ompare 1 Re | gister       |       |       |        |       |          |       | XXXX          |

| OC1CON   | 0184        | _      | - OCSIDL OCFLT OCTSEL OCM<2:0> 0000                                              |                                          |        |        |        |       |             |             |              |       |       |        |       |          |       |               |

| OC2RS    | 0186        |        |                                                                                  | Output Compare 2 Secondary Register xxxx |        |        |        |       |             |             |              |       |       |        |       |          |       |               |

| OC2R     | 0188        |        | Output Compare 2 Register                                                        |                                          |        |        |        |       |             |             |              |       |       |        |       |          |       |               |

| OC2CON   | 018A        | _      | _                                                                                | OCSIDL                                   | _      | _      |        | _     | —           | _           | _            | _     | OCFLT | OCTSEL |       | OCM<2:0> |       | 0000          |

| OC3RS    | 018C        |        |                                                                                  |                                          |        |        |        | Ou    | tput Compar | e 3 Seconda | ary Register |       |       |        |       |          |       | XXXX          |

| OC3R     | 018E        |        |                                                                                  |                                          |        |        |        |       | Output Co   | ompare 3 Re | gister       |       |       |        |       |          |       | XXXX          |

| OC3CON   | 0190        | _      | _                                                                                | OCSIDL                                   | _      | _      |        | _     | —           | _           | _            | _     | OCFLT | OCTSEL |       | OCM<2:0> |       | 0000          |

| OC4RS    | 0192        |        |                                                                                  |                                          |        |        |        | Ou    | tput Compar | e 4 Seconda | ary Register |       |       |        |       |          |       | XXXX          |

| OC4R     | 0194        |        | Output Compare 4 Register                                                        |                                          |        |        |        |       |             |             |              | XXXX  |       |        |       |          |       |               |

| OC4CON   | 0196        | _      | - OCSIDL OCFLT OCTSEL OCM<2:0> 0000                                              |                                          |        |        |        |       |             |             |              |       |       |        |       |          |       |               |

| l edend. | v = unk     |        | ue on Reset _ = unimplemented read as '0'. Reset values are shown in havadecimal |                                          |        |        |        |       |             |             |              |       |       |        |       |          |       |               |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# TABLE 4-8: I2C1 REGISTER MAP

| SFR Name | SFR<br>Addr | Bit 15  | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8                   | Bit 7                        | Bit 6 | Bit 5 | Bit 4    | Bit 3    | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|----------|-------------|---------|--------|---------|--------|--------|--------|--------|-------------------------|------------------------------|-------|-------|----------|----------|-------|-------|-------|---------------|

| I2C1RCV  | 0200        | _       | _      | -       | _      | _      | -      | -      | _                       | Receive Register             |       |       |          |          |       |       | 0000  |               |

| I2C1TRN  | 0202        | _       | _      | _       | _      | _      | _      | _      | _                       |                              |       |       | Transmit | Register |       |       |       | OOFF          |

| I2C1BRG  | 0204        | _       | _      | _       | _      | _      | _      | _      |                         | Baud Rate Generator Register |       |       |          |          |       |       | 0000  |               |

| I2C1CON  | 0206        | I2CEN   | _      | I2CSIDL | SCLREL | IPMIEN | A10M   | DISSLW | SMEN                    | GCEN                         | STREN | ACKDT | ACKEN    | RCEN     | PEN   | RSEN  | SEN   | 1000          |

| I2C1STAT | 0208        | ACKSTAT | TRSTAT | _       | _      | _      | BCL    | GCSTAT | ADD10                   | IWCOL                        | I2COV | D_A   | Р        | S        | R_W   | RBF   | TBF   | 0000          |

| I2C1ADD  | 020A        | _       | _      | _       | _      | _      | _      |        |                         | Address Register 0           |       |       |          |          |       | 0000  |       |               |

| I2C1MSK  | 020C        | _       | _      | _       | _      | _      | -      |        | Address Mask Register 0 |                              |       |       |          |          |       | 0000  |       |               |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# TABLE 4-9: UART1 REGISTER MAP

| SFR Name | SFR<br>Addr | Bit 15   | Bit 14                             | Bit 13   | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7                    | Bit 6   | Bit 5 | Bit 4      | Bit 3        | Bit 2 | Bit 1  | Bit 0 | All<br>Resets |

|----------|-------------|----------|------------------------------------|----------|--------|--------|--------|-------|-------|--------------------------|---------|-------|------------|--------------|-------|--------|-------|---------------|

| U1MODE   | 0220        | UARTEN   | _                                  | USIDL    | IREN   | RTSMD  | _      | UEN1  | UEN0  | WAKE                     | LPBACK  | ABAUD | URXINV     | BRGH         | PDSEI | _<1:0> | STSEL | 0000          |

| U1STA    | 0222        | UTXISEL1 | UTXINV                             | UTXISEL0 | -      | UTXBRK | UTXEN  | UTXBF | TRMT  | URXISE                   | EL<1:0> | ADDEN | RIDLE      | PERR         | FERR  | OERR   | URXDA | 0110          |

| U1TXREG  | 0224        | _        | _                                  | _        | _      | _      | —      | _     | UTX8  |                          |         | U     | ART Transm | nit Register |       |        |       | XXXX          |

| U1RXREG  | 0226        | _        | _                                  | _        | _      | _      | _      | _     | URX8  | 8 UART Received Register |         |       |            |              |       | 0000   |       |               |

| U1BRG    | 0228        |          | Baud Rate Generator Prescaler 0000 |          |        |        |        |       |       |                          |         |       | 0000       |              |       |        |       |               |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

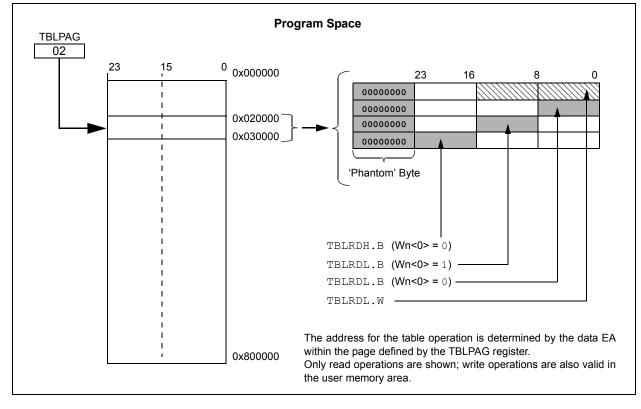

# 4.6.2 DATA ACCESS FROM PROGRAM MEMORY USING TABLE INSTRUCTIONS

The TBLRDL and TBLWTL instructions offer a direct method of reading or writing the lower word of any address within the program space without going through data space. The TBLRDH and TBLWTH instructions are the only method to read or write the upper 8 bits of a program space word as data.

The PC is incremented by two for each successive 24-bit program word. This allows program memory addresses to directly map to data space addresses. Program memory can thus be regarded as two 16-bit wide word address spaces, residing side by side, each with the same address range. TBLRDL and TBLWTL access the space that contains the least significant data word. TBLRDH and TBLWTH access the space that contains the upper data byte.

Two table instructions are provided to move byte or word-sized (16-bit) data to and from program space. Both function as either byte or word operations.

- TBLRDL (Table Read Low):

- In Word mode, this instruction maps the lower word of the program space location (P<15:0>) to a data address (D<15:0>).

- In Byte mode, either the upper or lower byte of the lower program word is mapped to the lower byte of a data address. The upper byte is selected when Byte Select is '1'; the lower byte is selected when it is '0'.

- TBLRDH (Table Read High):

- In Word mode, this instruction maps the entire upper word of a program address (P<23:16>) to a data address. The 'phantom' byte (D<15:8>), is always '0'.

- In Byte mode, this instruction maps the upper or lower byte of the program word to D<7:0> of the data address, in the TBLRDL instruction. The data is always '0' when the upper 'phantom' byte is selected (Byte Select = 1).

Similarly, two table instructions, TBLWTH and TBLWTL, are used to write individual bytes or words to a program space address. The details of their operation are explained in Section 5.0 "Flash Program Memory".

For all table operations, the area of program memory space to be accessed is determined by the Table Page register (TBLPAG). TBLPAG covers the entire program memory space of the device, including user application and configuration spaces. When TBLPAG<7> = 0, the table page is located in the user memory space. When TBLPAG<7> = 1, the page is located in configuration space.

# FIGURE 4-7: ACCESSING PROGRAM MEMORY WITH TABLE INSTRUCTIONS

NVMCON: FLASH MEMORY CONTROL REGISTER

# 5.6 Flash Memory Control Registers

**REGISTER 5-1:**

| R/SO-0 <sup>(1)</sup> | R/W-0 <sup>(1)</sup>            | R/W-0 <sup>(1)</sup>            |                |                                                                          |                                       |                      |                      |

|-----------------------|---------------------------------|---------------------------------|----------------|--------------------------------------------------------------------------|---------------------------------------|----------------------|----------------------|

| WR                    | R/W-000                         | WRERR                           | U-0            | U-0                                                                      | U-0                                   | U-0                  | U-0                  |

|                       | WREN                            | WRERR                           | —              | _                                                                        | —                                     |                      |                      |

| bit 15                |                                 |                                 |                |                                                                          |                                       |                      | bit 8                |

| U-0                   | R/W-0 <sup>(1)</sup>            | U-0                             | U-0            | R/W-0 <sup>(1)</sup>                                                     | R/W-0 <sup>(1)</sup>                  | R/W-0 <sup>(1)</sup> | R/W-0 <sup>(1)</sup> |

| _                     | ERASE                           |                                 | _              |                                                                          | NVMOP                                 | <3:0> <sup>(2)</sup> |                      |

| bit 7                 | ·                               |                                 |                |                                                                          |                                       |                      | bit 0                |

| Legend:               |                                 | SO = Settal                     | ole only bit   |                                                                          |                                       |                      |                      |

| R = Readable          | bit                             | W = Writabl                     | e bit          | U = Unimpler                                                             | mented bit, read                      | as '0'               |                      |

| -n = Value at F       | POR                             | '1' = Bit is s                  | et             | '0' = Bit is cle                                                         | ared                                  | x = Bit is unkr      | nown                 |

| bit 15                | WR: Write Con                   | trol bit                        |                |                                                                          |                                       |                      |                      |

|                       | 1 = Initiates a                 | Flash memor                     | y program or   | erase operation                                                          | on. The operatio                      | on is self-timed     | and the bit is       |

|                       |                                 | hardware on                     |                |                                                                          |                                       |                      |                      |

|                       | 0 = Program of                  | •                               | tion is comple | ete and inactive                                                         | 9                                     |                      |                      |

| bit 14                | WREN: Write E                   |                                 |                |                                                                          |                                       |                      |                      |

|                       | 1 = Enable Fla                  |                                 |                |                                                                          |                                       |                      |                      |

| h:: 40                | 0 = Inhibit Flas                |                                 | -              | IS                                                                       |                                       |                      |                      |

| bit 13                | WRERR: Write                    | •                               | •              |                                                                          | · · · · · · · · · · · · · · · · · · · |                      |                      |

|                       |                                 | er program or<br>ally on any se |                |                                                                          | termination has                       | occurred (bit i      | s set                |

|                       | 0 = The progra                  |                                 |                |                                                                          | /                                     |                      |                      |

| bit 12-7              | Unimplemente                    |                                 |                |                                                                          |                                       |                      |                      |

| bit 6                 | ERASE: Erase                    |                                 |                |                                                                          |                                       |                      |                      |

| 2.00                  |                                 | •                               |                | bv NVMOP </td <td>3:0&gt; on the next</td> <td>WR command</td> <td></td> | 3:0> on the next                      | WR command           |                      |

|                       |                                 |                                 |                |                                                                          | ><3:0> on the network                 |                      |                      |

| bit 5-4               | Unimplemente                    | d: Read as '                    | )'             |                                                                          |                                       |                      |                      |

| bit 3-0               | NVMOP<3:0>:                     | NVM Operati                     | on Select bits | <sub>S</sub> (2)                                                         |                                       |                      |                      |

|                       | If ERASE = 1:                   |                                 |                |                                                                          |                                       |                      |                      |

|                       | 1111 <b>= Memor</b>             | •                               | operation      |                                                                          |                                       |                      |                      |

|                       | 1110 = Reserv                   |                                 |                |                                                                          |                                       |                      |                      |

|                       | 1101 = Erase (                  | •                               |                |                                                                          |                                       |                      |                      |

|                       | 1100 = Erase S<br>1011 = Reserv |                                 | ent            |                                                                          |                                       |                      |                      |

|                       | 0011 = No ope                   |                                 |                |                                                                          |                                       |                      |                      |

|                       | 0010 = Memor                    |                                 | operation      |                                                                          |                                       |                      |                      |

|                       | 0001 = No ope                   |                                 |                |                                                                          |                                       |                      |                      |

|                       | 0000 <b>= Erase</b> a           | a single Confi                  | guration regis | ster byte                                                                |                                       |                      |                      |

|                       | If ERASE = 0:                   |                                 |                |                                                                          |                                       |                      |                      |

|                       | 1111 <b>= No ope</b>            |                                 |                |                                                                          |                                       |                      |                      |

|                       | 1110 = Reserv                   |                                 |                |                                                                          |                                       |                      |                      |

|                       | 1101 = No ope<br>1100 = No ope  |                                 |                |                                                                          |                                       |                      |                      |

|                       | 1011 = Reserv                   |                                 |                |                                                                          |                                       |                      |                      |

|                       | 0011 = Memor                    | y word progra                   | m operation    |                                                                          |                                       |                      |                      |

|                       | 0010 = No ope                   | ration                          |                |                                                                          |                                       |                      |                      |

|                       | 0001 = Memory                   |                                 |                |                                                                          |                                       |                      |                      |

|                       | 0000 <b>= Progra</b> r          | n a single Co                   | nfiguration re | gister byte                                                              |                                       |                      |                      |

| Note 1: The           | ese bits can only               | be reset on a                   | POR.           |                                                                          |                                       |                      |                      |

| 2: All                | other combination               | ns of NVMOF                     | <3:0> are un   | implemented                                                              |                                       |                      |                      |

2: All other combinations of NVMOP<3:0> are unimplemented.

# FIGURE 7-1: PIC24HJ32GP302/304, PIC24HJ64GPX02/X04 and PIC24HJ128GPX02/X04 INTERRUPT VECTOR TABLE

|                                   |                                       | _                 |                                                        |

|-----------------------------------|---------------------------------------|-------------------|--------------------------------------------------------|

|                                   | Reset – GOTO Instruction              | 0x000000          |                                                        |

|                                   | Reset – GOTO Address                  | 0x000002          |                                                        |

|                                   | Reserved                              | 0x000004          |                                                        |

|                                   | Oscillator Fail Trap Vector           |                   |                                                        |

|                                   | Address Error Trap Vector             |                   |                                                        |

|                                   | Stack Error Trap Vector               |                   |                                                        |

|                                   | Math Error Trap Vector                |                   |                                                        |

|                                   | DMA Error Trap Vector                 |                   |                                                        |

|                                   | Reserved                              |                   |                                                        |

|                                   | Reserved                              |                   |                                                        |

|                                   | Interrupt Vector 0                    | 0x000014          |                                                        |

|                                   | Interrupt Vector 1                    |                   |                                                        |

|                                   | ~                                     |                   |                                                        |

|                                   | ~                                     | 1                 |                                                        |

|                                   | ~                                     |                   |                                                        |

|                                   | Interrupt Vector 52                   | 0x00007C          | $l_{1}$                                                |

|                                   | Interrupt Vector 53                   | 0x00007E          | Interrupt Vector Table (IVT) <sup>(1)</sup>            |

| ity                               | Interrupt Vector 54                   | 0x000080          |                                                        |

| ior                               | ~                                     |                   |                                                        |

| ā                                 | ~                                     |                   |                                                        |

| dei                               | ~                                     |                   |                                                        |

| Decreasing Natural Order Priority | Interrupt Vector 116                  | 0x0000FC          |                                                        |

| ral                               | Interrupt Vector 117                  | 0x0000FE          | •                                                      |

| atu                               | Reserved                              | 0x000100          |                                                        |

| ž                                 | Reserved                              | 0x000102          |                                                        |

| ing                               | Reserved                              |                   |                                                        |

| as                                | Oscillator Fail Trap Vector           |                   |                                                        |

| cre                               | Address Error Trap Vector             |                   |                                                        |

| De                                | Stack Error Trap Vector               | -                 |                                                        |

|                                   | Math Error Trap Vector                | _                 |                                                        |

|                                   | DMA Error Trap Vector                 | _                 |                                                        |

|                                   | Reserved                              |                   | ]                                                      |

|                                   | Reserved                              |                   |                                                        |

|                                   | Interrupt Vector 0                    | 0x000114          |                                                        |

|                                   | Interrupt Vector 1                    |                   |                                                        |

|                                   | ~                                     | -                 |                                                        |

|                                   | ~                                     |                   |                                                        |

|                                   | ~                                     |                   | Alternate Interrupt Vector Table (AIVT) <sup>(1)</sup> |

|                                   | Interrupt Vector 52                   | 0x00017C          |                                                        |

|                                   | Interrupt Vector 53                   | 0x00017E          |                                                        |

|                                   | Interrupt Vector 54                   | 0x000180          |                                                        |

|                                   | ~                                     |                   |                                                        |

|                                   | ~                                     |                   |                                                        |

|                                   | ~                                     |                   |                                                        |

|                                   | Interrupt Vector 116                  | 1 –               | -                                                      |

|                                   | Interrupt Vector 117                  | 0x0001FE          |                                                        |

| V                                 | Start of Code                         | 0x000200          |                                                        |

|                                   |                                       | -                 |                                                        |

|                                   |                                       |                   |                                                        |

|                                   |                                       |                   |                                                        |

| Note 1: S                         | See Table 7-1 for the list of impleme | ented interrupt v | vectors.                                               |

|                                   |                                       |                   |                                                        |

|                                   |                                       |                   |                                                        |

# 7.5 Interrupt Control Registers

# **REGISTER 7-1:** SR: CPU STATUS REGISTER<sup>(1)</sup>

| U-0                  | U-0                     | U-0                  | U-0 | U-0   | U-0   | U-0   | R/W-0 |

|----------------------|-------------------------|----------------------|-----|-------|-------|-------|-------|

| _                    | —                       | —                    | —   | —     | —     | —     | DC    |

| bit 15               |                         |                      |     |       |       |       | bit 8 |

|                      |                         |                      |     |       |       |       |       |

| R/W-0 <sup>(3)</sup> | R/W-0 <sup>(3)</sup>    | R/W-0 <sup>(3)</sup> | R-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|                      | IPL<2:0> <sup>(2)</sup> |                      | RA  | N     | OV    | Z     | С     |

| Ь  | :4 | 7 |

|----|----|---|

| 1) | ш  | 1 |

|    |    |   |

| Legend:            |                      |                                    |  |

|--------------------|----------------------|------------------------------------|--|

| C = Clear only bit | R = Readable bit     | U = Unimplemented bit, read as '0' |  |

| S = Set only bit   | W = Writable bit     | -n = Value at POR                  |  |

| '1' = Bit is set   | '0' = Bit is cleared | x = Bit is unknown                 |  |

bit 7-5

## IPL<2:0>: CPU Interrupt Priority Level Status bits<sup>(2)</sup>

111 = CPU Interrupt Priority Level is 7 (15), user interrupts disabled

- 110 = CPU Interrupt Priority Level is 6 (14)

- 101 = CPU Interrupt Priority Level is 5 (13)

- 100 = CPU Interrupt Priority Level is 4 (12)

- 011 = CPU Interrupt Priority Level is 3 (11)

- 010 = CPU Interrupt Priority Level is 2 (10)

- 001 = CPU Interrupt Priority Level is 1 (9)

- 000 = CPU Interrupt Priority Level is 0 (8)

**Note 1:** For complete register details, see Register 3-1.

- 2: The IPL<2:0> bits are concatenated with the IPL<3> bit (CORCON<3>) to form the CPU Interrupt Priority Level. The value in parentheses indicates the IPL if IPL<3> = 1. User interrupts are disabled when IPL<3> = 1.

- 3: The IPL<2:0> Status bits are read-only when the NSTDIS bit (INTCON1<15>) = 1.

# REGISTER 7-2: CORCON: CORE CONTROL REGISTER<sup>(1)</sup>

| U-0               | U-0           | U-0               | U-0              | U-0                 | U-0              | U-0              | U-0   |

|-------------------|---------------|-------------------|------------------|---------------------|------------------|------------------|-------|

| _                 | —             | —                 | —                | —                   | —                | —                | —     |

| bit 15            |               |                   |                  |                     |                  |                  | bit 8 |

|                   |               |                   |                  |                     |                  |                  |       |

| U-0               | U-0           | U-0               | U-0              | R/C-0               | R/W-0            | U-0              | U-0   |

|                   | —             | —                 | —                | IPL3 <sup>(2)</sup> | PSV              | —                | —     |

| bit 7             |               |                   |                  |                     |                  |                  | bit 0 |

|                   |               |                   |                  |                     |                  |                  |       |

| Legend:           |               | C = Clear only    | / bit            |                     |                  |                  |       |

| R = Readable I    | oit           | W = Writable      | bit              | -n = Value at       | POR              | '1' = Bit is set |       |

| 0' = Bit is clear | ed            | 'x = Bit is unkr  | nown             | U = Unimpler        | nented bit, read | as '0'           |       |

|                   |               |                   |                  | (0)                 |                  |                  |       |

| bit 3             | IPL3: CPU Int | terrupt Priority  | Level Status b   | it 3 <sup>(2)</sup> |                  |                  |       |

|                   | 1 = CPU inter | rupt priority lev | el is greater th | nan 7               |                  |                  |       |

|                   | 0 = CPU inter | rupt priority lev | el is 7 or less  |                     |                  |                  |       |

|                   |               |                   |                  |                     |                  |                  |       |

**Note 1:** For complete register details, see Register 3-2.

2: The IPL3 bit is concatenated with the IPL<2:0> bits (SR<7:5>) to form the CPU Interrupt Priority Level.

bit 0

| REGISTER 8      | -7: DMAC                          | S0: DMA CO                                             | NTROLLER        | STATUS RE        | GISTER 0        |                 |        |  |  |  |  |  |

|-----------------|-----------------------------------|--------------------------------------------------------|-----------------|------------------|-----------------|-----------------|--------|--|--|--|--|--|

| R/C-0           | R/C-0                             | R/C-0                                                  | R/C-0           | R/C-0            | R/C-0           | R/C-0           | R/C-0  |  |  |  |  |  |

| PWCOL7          | PWCOL6                            | PWCOL5                                                 | PWCOL4          | PWCOL3           | PWCOL2          | PWCOL1          | PWCOL0 |  |  |  |  |  |

| bit 15          |                                   |                                                        |                 |                  |                 |                 | bit 8  |  |  |  |  |  |

| R/C-0           | R/C-0                             | R/C-0                                                  | R/C-0           | R/C-0            | R/C-0           | R/C-0           | R/C-0  |  |  |  |  |  |

| XWCOL7          | XWCOL6                            | XWCOL5                                                 | XWCOL4          | XWCOL3           | XWCOL2          | XWCOL1          | XWCOL0 |  |  |  |  |  |

| bit 7           |                                   |                                                        |                 |                  |                 |                 | bit    |  |  |  |  |  |

| Legend:         |                                   |                                                        |                 | C = Clea         | ar only bit     |                 |        |  |  |  |  |  |

| R = Readable    | bit                               | W = Writable                                           | bit             |                  | nented bit, rea | d as '0'        |        |  |  |  |  |  |

| -n = Value at I |                                   | '1' = Bit is set                                       |                 | '0' = Bit is cle |                 | x = Bit is unkr | าดพท   |  |  |  |  |  |

|                 |                                   |                                                        |                 |                  |                 |                 |        |  |  |  |  |  |

| bit 15          | 1 = Write colli                   | nannel 7 Periph<br>ision detected<br>collision detecte |                 | llision Flag bit |                 |                 |        |  |  |  |  |  |

| bit 14          | 1 = Write colli                   | nannel 6 Periph<br>ision detected<br>collision detecte |                 | llision Flag bit |                 |                 |        |  |  |  |  |  |

| bit 13          | 1 = Write colli                   | nannel 5 Periph<br>ision detected<br>collision detecte |                 | llision Flag bit |                 |                 |        |  |  |  |  |  |

| bit 12          | PWCOL4: Ch                        | PWCOL4: Channel 4 Peripheral Write Collision Flag bit  |                 |                  |                 |                 |        |  |  |  |  |  |

|                 |                                   | ision detected collision detected                      | ed              |                  |                 |                 |        |  |  |  |  |  |

| bit 11          | PWCOL3: Ch                        | nannel 3 Periph                                        | neral Write Col | llision Flag bit |                 |                 |        |  |  |  |  |  |

|                 |                                   | ision detected collision detected                      | ed              |                  |                 |                 |        |  |  |  |  |  |

| bit 10          | 1 = Write colli                   | nannel 2 Periph<br>ision detected<br>collision detecte |                 | llision Flag bit |                 |                 |        |  |  |  |  |  |

| bit 9           | 1 = Write colli                   | nannel 1 Periph<br>ision detected<br>collision detecte |                 | llision Flag bit |                 |                 |        |  |  |  |  |  |

| bit 8           | 1 = Write colli                   | nannel 0 Periph<br>ision detected<br>collision detecte |                 | llision Flag bit |                 |                 |        |  |  |  |  |  |

| bit 7           |                                   | nannel 7 DMA I                                         | RAM Write Co    | Ilision Flag bit |                 |                 |        |  |  |  |  |  |

|                 |                                   | ision detected<br>collision detecte                    | ed              |                  |                 |                 |        |  |  |  |  |  |

| bit 6           | XWCOL6: Ch                        | nannel 6 DMA I                                         | RAM Write Co    | llision Flag bit |                 |                 |        |  |  |  |  |  |

|                 |                                   | ision detected collision detected                      | ed              |                  |                 |                 |        |  |  |  |  |  |

| bit 5           | XWCOL5: Ch                        | nannel 5 DMA I                                         | RAM Write Co    | Ilision Flag bit |                 |                 |        |  |  |  |  |  |

|                 | 1 = Write colli<br>0 = No write c | ision detected collision detected                      | ed              |                  |                 |                 |        |  |  |  |  |  |

| bit 4           | XWCOL4: Cr                        | nannel 4 DMA I                                         | RAM Write Co    | Ilision Flag bit |                 |                 |        |  |  |  |  |  |

|                 |                                   | ision detected<br>collision detecte                    | ed              | -                |                 |                 |        |  |  |  |  |  |

| U-0                            | U-0                                                                                                                                                                                    | U-0                                                                            | U-0                                                                                                                                                                              | R-1                                                                                                           | R-1              | R-1             | R-1   |

|--------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|------------------|-----------------|-------|

| 0-0                            | 0-0                                                                                                                                                                                    | 0-0                                                                            | 0-0                                                                                                                                                                              | N-1                                                                                                           | LSTCH            |                 | N-1   |

| <br>bit 15                     |                                                                                                                                                                                        | _                                                                              | _                                                                                                                                                                                |                                                                                                               | LOTOF            | 1<3.02          | bit   |

|                                |                                                                                                                                                                                        |                                                                                |                                                                                                                                                                                  |                                                                                                               |                  |                 | Dit   |

| R-0                            | R-0                                                                                                                                                                                    | R-0                                                                            | R-0                                                                                                                                                                              | R-0                                                                                                           | R-0              | R-0             | R-0   |

| PPST7                          | PPST6                                                                                                                                                                                  | PPST5                                                                          | PPST4                                                                                                                                                                            | PPST3                                                                                                         | PPST2            | PPST1           | PPST0 |

| pit 7                          |                                                                                                                                                                                        |                                                                                |                                                                                                                                                                                  |                                                                                                               |                  |                 | bit   |

|                                |                                                                                                                                                                                        |                                                                                |                                                                                                                                                                                  |                                                                                                               |                  |                 |       |

| _egend:                        |                                                                                                                                                                                        |                                                                                |                                                                                                                                                                                  |                                                                                                               |                  |                 |       |

| R = Readabl                    | e bit                                                                                                                                                                                  | W = Writable                                                                   | bit                                                                                                                                                                              | U = Unimplem                                                                                                  | nented bit, read | as '0'          |       |

| n = Value at                   | t POR                                                                                                                                                                                  | '1' = Bit is set                                                               |                                                                                                                                                                                  | '0' = Bit is clea                                                                                             | ared             | x = Bit is unkr | nown  |

| bit 15-12<br>bit 11-8<br>bit 7 | LSTCH<3:0><br>1111 = No DI<br>1110-1000 =<br>0111 = Last of<br>0101 = Last of<br>0100 = Last of<br>0010 = Last of<br>0010 = Last of<br>0001 = Last of<br>0000 = Last of<br>PPST7: Chan |                                                                                | annel Active t<br>s occurred sin<br>as by DMA Ch<br>as by DMA Ch | ce system Res<br>nannel 7<br>nannel 6<br>nannel 5<br>nannel 4<br>nannel 3<br>nannel 2<br>nannel 1<br>nannel 0 | et               |                 |       |

| oit 6                          | 0 = DMA7STA<br><b>PPST6:</b> Chan<br>1 = DMA6STE                                                                                                                                       | A register select<br>Inel 6 Ping-Por<br>3 register select<br>A register select | eted<br>ng Mode Statu<br>eted                                                                                                                                                    | s Flag bit                                                                                                    |                  |                 |       |

| pit 5                          | <b>PPST5:</b> Chan<br>1 = DMA5STE                                                                                                                                                      | inel 5 Ping-Por<br>3 register selec<br>A register selec                        | ng Mode Statu<br>cted                                                                                                                                                            | s Flag bit                                                                                                    |                  |                 |       |

| oit 4                          | 1 = DMA4STE                                                                                                                                                                            | nnel 4 Ping-Por<br>3 register selec<br>A register selec                        | cted                                                                                                                                                                             | s Flag bit                                                                                                    |                  |                 |       |

| pit 3                          | 1 = DMA3STE                                                                                                                                                                            | nel 3 Ping-Por<br>3 register selec<br>A register selec                         | cted                                                                                                                                                                             | s Flag bit                                                                                                    |                  |                 |       |

| bit 2                          | 1 = DMA2STE                                                                                                                                                                            | nel 2 Ping-Por<br>3 register selec<br>4 register selec                         | cted                                                                                                                                                                             | s Flag bit                                                                                                    |                  |                 |       |

| oit 1                          | 1 = DMA1STE                                                                                                                                                                            | nel 1 Ping-Por<br>3 register selec<br>4 register selec                         | cted                                                                                                                                                                             | s Flag bit                                                                                                    |                  |                 |       |

| oit O                          | 1 = DMA0STE                                                                                                                                                                            | nel 0 Ping-Por<br>3 register selec<br>A register selec                         | cted                                                                                                                                                                             | s Flag bit                                                                                                    |                  |                 |       |

# 11.6.3 CONTROLLING CONFIGURATION CHANGES

Because peripheral remapping can be changed during run time, some restrictions on peripheral remapping are needed to prevent accidental configuration changes. PIC24H devices include three features to prevent alterations to the peripheral map:

- Control register lock sequence

- · Continuous state monitoring

- Configuration bit pin select lock

# 11.6.3.1 Control Register Lock

Under normal operation, writes to the RPINRx and RPORx registers are not allowed. Attempted writes appear to execute normally, but the contents of the registers remain unchanged. To change these registers, they must be unlocked in hardware. The register lock is controlled by the IOLOCK bit (OSCCON<6>). Setting IOLOCK prevents writes to the control registers; clearing IOLOCK allows writes.

To set or clear IOLOCK, a specific command sequence must be executed:

- 1. Write 0x46 to OSCCON<7:0>.

- 2. Write 0x57 to OSCCON<7:0>.

- 3. Clear (or set) the IOLOCK bit as a single operation.

| Note:                                | MPLAB <sup>®</sup> C30 provides built-in C language functions for unlocking the OSCCON register: |  |  |  |  |  |  |  |  |

|--------------------------------------|--------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

|                                      | builtin_write_OSCCONL(value)<br>builtin_write_OSCCONH(value)                                     |  |  |  |  |  |  |  |  |

| See MPLAB Help for more information. |                                                                                                  |  |  |  |  |  |  |  |  |

Unlike the similar sequence with the oscillator's LOCK bit, IOLOCK remains in one state until changed. This allows all of the peripheral pin selects to be configured with a single unlock sequence followed by an update to all control registers, then locked with a second lock sequence.

# 11.6.3.2 Continuous State Monitoring

In addition to being protected from direct writes, the contents of the RPINRx and RPORx registers are constantly monitored in hardware by shadow registers. If an unexpected change in any of the registers occurs (such as cell disturbances caused by ESD or other external events), a configuration mismatch Reset is triggered.

# 11.6.3.3 Configuration Bit Pin Select Lock

As an additional level of safety, the device can be configured to prevent more than one write session to the RPINRx and RPORx registers. The IOL1WAY Configuration bit (FOSC<5>) blocks the IOLOCK bit from being cleared after it has been set once. If IOLOCK remains set, the register unlock procedure does not execute, and the peripheral pin select control registers cannot be written to. The only way to clear the bit and re-enable peripheral remapping is to perform a device Reset.

In the default (unprogrammed) state, IOL1WAY is set, restricting users to one write session. Programming IOL1WAY allows user applications unlimited access (with the proper use of the unlock sequence) to the peripheral pin select registers.

# REGISTER 11-13: RPINR23: PERIPHERAL PIN SELECT INPUT REGISTER 23

| U-0                                                                        | U-0 | U-0 | U-0   | U-0                                | U-0       | U-0   | U-0   |  |

|----------------------------------------------------------------------------|-----|-----|-------|------------------------------------|-----------|-------|-------|--|

| _                                                                          | —   | —   | -     |                                    | —         | —     | —     |  |

| bit 15                                                                     |     |     |       |                                    |           |       | bit 8 |  |

|                                                                            |     |     |       |                                    |           |       |       |  |

| U-0                                                                        | U-0 | U-0 | R/W-1 | R/W-1                              | R/W-1     | R/W-1 | R/W-1 |  |

| _                                                                          | —   | —   |       |                                    | SS2R<4:0> |       |       |  |

| bit 7                                                                      |     | •   |       |                                    |           |       | bit 0 |  |

|                                                                            |     |     |       |                                    |           |       |       |  |

| Legend:                                                                    |     |     |       |                                    |           |       |       |  |

| R = Readable bit W = Writable bit                                          |     |     |       | U = Unimplemented bit, read as '0' |           |       |       |  |

| -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown |     |     |       |                                    | nown      |       |       |  |

| -                                                                          |     |     |       |                                    |           |       |       |  |

bit 15-5 Unimplemented: Read as '0'

bit 4-0

SS2R<4:0>: Assign SPI2 Slave Select Input (SS2) to the corresponding RPn pin

11111 = Input tied to Vss

11001 = Input tied to RP25

.

00001 = Input tied to RP1 00000 = Input tied to RP0

#### U-0 U-0 U-0 U-0 U-0 U-0 U-0 U-0 \_ \_\_\_\_ \_ \_\_\_\_ \_\_\_\_ \_\_\_ \_ \_ bit 15 bit 8 U-0 U-0 U-0 R/W-1 R/W-1 R/W-1 R/W-1 R/W-1 C1RXR<4:0> \_\_\_ bit 7 bit 0 Legend: R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

'0' = Bit is cleared

REGISTER 11-14: RPINR26: PERIPHERAL PIN SELECT INPUT REGISTER 26<sup>(1)</sup>

bit 15-5 Unimplemented: Read as '0'

-n = Value at POR

Note 1: This register is disabled on devices without ECAN™ modules.

'1' = Bit is set

x = Bit is unknown

# PIC24HJ32GP302/304, PIC24HJ64GPX02/X04 AND PIC24HJ128GPX02/X04

| U-0                            | U-0                                                               | U-0                                 | R-0          | R-0              | R-0                                   | R-0             | R-0  |  |  |  |  |  |

|--------------------------------|-------------------------------------------------------------------|-------------------------------------|--------------|------------------|---------------------------------------|-----------------|------|--|--|--|--|--|

| —                              | —                                                                 | —                                   |              |                  | FILHIT<4:0>                           |                 |      |  |  |  |  |  |

| oit 15                         |                                                                   |                                     |              |                  |                                       |                 | bit  |  |  |  |  |  |

| U-0                            | R-1                                                               | R-0                                 | R-0          | R-0              | R-0                                   | R-0             | R-0  |  |  |  |  |  |

|                                | 112-1                                                             | 14-0                                | 11-0         | ICODE<6:0        |                                       | 11-0            | 11-0 |  |  |  |  |  |

| pit 7                          |                                                                   |                                     |              | 10002 0.0        |                                       |                 | bit  |  |  |  |  |  |

|                                |                                                                   | $\Omega = M/rite eble$              | hit hut only | (O' con he writt | an to alcor the b                     | :4              |      |  |  |  |  |  |

| L <b>egend:</b><br>R = Readabl | o hit                                                             | C = Writable<br>W = Writable        | -            |                  | en to clear the b<br>mented bit, read |                 |      |  |  |  |  |  |

| n = Value at                   |                                                                   | '1' = Bit is set                    |              | '0' = Bit is cle |                                       | x = Bit is unkr | NOWD |  |  |  |  |  |

|                                |                                                                   |                                     |              |                  |                                       |                 |      |  |  |  |  |  |

| bit 15-13                      | Unimplemen                                                        | ted: Read as '                      | 0'           |                  |                                       |                 |      |  |  |  |  |  |

| oit 12-8                       | FILHIT<4:0>:                                                      | : Filter Hit Num                    | ber bits     |                  |                                       |                 |      |  |  |  |  |  |

|                                |                                                                   | 1 = Reserved                        |              |                  |                                       |                 |      |  |  |  |  |  |

|                                | 01111 = Filte                                                     | er 15                               |              |                  |                                       |                 |      |  |  |  |  |  |

|                                | •                                                                 |                                     |              |                  |                                       |                 |      |  |  |  |  |  |

|                                | •                                                                 |                                     |              |                  |                                       |                 |      |  |  |  |  |  |

|                                | •<br>00001 = Filter 1                                             |                                     |              |                  |                                       |                 |      |  |  |  |  |  |

|                                | 00001 = Filter 1<br>00000 = Filter 0                              |                                     |              |                  |                                       |                 |      |  |  |  |  |  |

| bit 7                          | Unimplemented: Read as '0'                                        |                                     |              |                  |                                       |                 |      |  |  |  |  |  |

| bit 6-0                        | ICODE<6:0>                                                        | : Interrupt Flag                    | Code bits    |                  |                                       |                 |      |  |  |  |  |  |

|                                |                                                                   | 11111 = Rese                        |              |                  |                                       |                 |      |  |  |  |  |  |

|                                |                                                                   | IFO almost full<br>Receiver overflo |              |                  |                                       |                 |      |  |  |  |  |  |

|                                |                                                                   | Vake-up interru                     |              |                  |                                       |                 |      |  |  |  |  |  |

|                                | 1000001 = Error interrupt                                         |                                     |              |                  |                                       |                 |      |  |  |  |  |  |

|                                | 1000000 = No interrupt                                            |                                     |              |                  |                                       |                 |      |  |  |  |  |  |

|                                | •                                                                 |                                     |              |                  |                                       |                 |      |  |  |  |  |  |

|                                | •                                                                 |                                     |              |                  |                                       |                 |      |  |  |  |  |  |

|                                | •                                                                 |                                     |              |                  |                                       |                 |      |  |  |  |  |  |

|                                | 0010000-0111111 = Reserved<br>0001111 = RB15 buffer Interrupt     |                                     |              |                  |                                       |                 |      |  |  |  |  |  |