# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Detalls                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Active                                                                        |

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 40 MIPs                                                                       |

| Connectivity               | I <sup>2</sup> C, PMP, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                    |

| Number of I/O              | 21                                                                            |

| Program Memory Size        | 32KB (11K x 24)                                                               |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 4K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                     |

| Data Converters            | A/D 10x10b/12b                                                                |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                                |

| Supplier Device Package    | 28-SOIC                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24hj32gp302-i-so |

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 3.0 CPU

- Note 1: This data sheet summarizes the features of the PIC24HJ32GP302/304, PIC24HJ64GPX02/X04 and PIC24HJ128GPX02/X04 families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 2. "CPU" (DS70204) of the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

## 3.1 Overview

The PIC24HJ32GP302/304, PIC24HJ64GPX02/X04 and PIC24HJ128GPX02/X04 CPU module has a 16-bit (data) modified Harvard architecture with an enhanced instruction set and addressing modes. The CPU has a 24-bit instruction word with a variable length opcode field. The Program Counter (PC) is 23 bits wide and addresses up to 4M x 24 bits of user program memory space. The actual amount of program memory implemented varies by device. A single-cycle instruction prefetch mechanism is used to help maintain throughput and provides predictable execution. All instructions execute in a single cycle, with the exception of instructions that change the program flow, the double word move (MOV.D) instruction and the table instructions. Overhead-free, single-cycle program loop constructs are supported using the REPEAT instruction, which is interruptible at any point.

The PIC24HJ32GP302/304, PIC24HJ64GPX02/X04 and PIC24HJ128GPX02/X04 devices have sixteen, 16-bit working registers in the programmer's model. Each of the working registers can serve as a data, address or address offset register. The 16th working register (W15) operates as a software Stack Pointer (SP) for interrupts and calls.

The PIC24HJ32GP302/304, PIC24HJ64GPX02/X04 and PIC24HJ128GPX02/X04 instruction set includes many addressing modes and is designed for optimum C compiler efficiency. For most instructions, the PIC24HJ32GP302/304, PIC24HJ64GPX02/X04 and PIC24HJ128GPX02/X04 is capable of executing a data (or program data) memory read, a working register (data) read, a data memory write and a program (instruction) memory read per instruction cycle. As a result, three parameter instructions can be supported, allowing A + B = C operations to be executed in a single cycle.

A block diagram of the CPU is shown in Figure 3-1, and the programmer's model for the PIC24HJ32GP302/ 304, PIC24HJ64GPX02/X04 and PIC24HJ128GPX02/ X04 is shown in Figure 3-2.

# 3.2 Data Addressing Overview

The data space can be linearly addressed as 32K words or 64 Kbytes using an Address Generation Unit (AGU). The upper 32 Kbytes of the data space memory map can optionally be mapped into program space at any 16K program word boundary defined by the 8-bit Program Space Visibility Page (PSVPAG) register. The program to data space mapping feature lets any instruction access program space as if it were data space.

The data space also includes 2 Kbytes of DMA RAM, which is primarily used for DMA data transfers, but may be used as general purpose RAM.

NOTES:

# 4.0 MEMORY ORGANIZATION

| Note: | This data sheet summarizes the features      |

|-------|----------------------------------------------|

|       | of the PIC24HJ32GP302/304,                   |

|       | PIC24HJ64GPX02/X04 and                       |

|       | PIC24HJ128GPX02/X04 families of              |

|       | devices. It is not intended to be a compre-  |

|       | hensive reference source. To complement      |

|       | the information in this data sheet, refer to |

|       | Section 4. "Program Memory"                  |

|       | (DS70203) of the "dsPIC33F/PIC24H            |

|       | Family Reference Manual", which is avail-    |

|       | able from the Microchip web site             |

|       | (www.microchip.com).                         |

The PIC24HJ32GP302/304, PIC24HJ64GPX02/X04 and PIC24HJ128GPX02/X04 architecture features separate program and data memory spaces and buses. This architecture also allows the direct access of program memory from the data space during code execution.

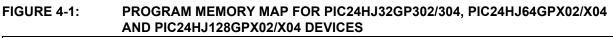

# 4.1 Program Address Space

The program address memory space of the PIC24HJ32GP302/304, PIC24HJ64GPX02/X04 and PIC24HJ128GPX02/X04 devices is 4M instructions. The space is addressable by a 24-bit value derived either from the 23-bit Program Counter (PC) during program execution, or from table operation or data space remapping as described in Section 4.6 "Interfacing Program and Data Memory Spaces".

User application access to the program memory space is restricted to the lower half of the address range (0x000000 to 0x7FFFFF). The exception is the use of TBLRD/TBLWT operations, which use TBLPAG<7> to permit access to the Configuration bits and Device ID sections of the configuration memory space.

The memory map for the PIC24HJ32GP302/304, PIC24HJ64GPX02/X04 and PIC24HJ128GPX02/X04 devices is shown in Figure 4-1.

|                            | PIC24HJ32GP302/304                                   | PIC24HJ64GPX02/X04                | PIC24HJ128GPX02/X04                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|----------------------------|------------------------------------------------------|-----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4                          | GOTO Instruction                                     | GOTO Instruction                  | GOTO Instruction 0x000000<br>Reset Address 0x000002                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                            | Reset Address                                        | Reset Address                     | 0x000004                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                            | Interrupt Vector Table                               | Interrupt Vector Table            | Interrupt Vector Table 0x0000FE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                            | Reserved                                             | Reserved                          | <u>Reserved</u> 0x000100<br>0x000104                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                            | Alternate Vector Table                               | Alternate Vector Table            | Alternate vector rable 0x0001FE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| User Memory Space          | User Program<br>Flash Memory<br>(11264 instructions) | User Program<br>Flash Memory      | 0x000200<br>0x0057FE<br>0x0057FE<br>0x005800                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                            | Unimplemented                                        |                                   | User Program<br>Flash Memory<br>(44032 instructions)<br>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                            | (Read '0's)                                          | Unimplemented                     | 0x0157FE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                            |                                                      | (Read '0's)                       | 0x015800                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                            |                                                      |                                   | Unimplemented<br>(Read '0's)<br>0x7FFFE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                            | Reserved                                             | Reserved                          | 0x800000<br>Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                            | Device Configuration<br>Registers                    | Device Configuration<br>Registers | Device Configuration 0xF7FFE<br>Device Configuration 0xF80000<br>Registers 0xF80017                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Conriguration Memory Space | Reserved                                             | Reserved                          | Care Control C |

| 0                          |                                                      |                                   | DEVID (2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                            | Reserved                                             | Reserved                          | 0xFF0002           Reserved           0xFFFFE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

#### REGISTER 7-10: IEC0: INTERRUPT ENABLE CONTROL REGISTER 0 (CONTINUED)

| bit 2 | OC1IE: Output Compare Channel 1 Interrupt Enable bit |

|-------|------------------------------------------------------|

|-------|------------------------------------------------------|

- 1 = Interrupt request enabled

- 0 = Interrupt request not enabled

- bit 1 IC1IE: Input Capture Channel 1 Interrupt Enable bit

- 1 = Interrupt request enabled

- 0 = Interrupt request not enabled

- bit 0 INTOIE: External Interrupt 0 Flag Status bit

- 1 = Interrupt request enabled

- 0 = Interrupt request not enabled

#### REGISTER 7-11: IEC1: INTERRUPT ENABLE CONTROL REGISTER 1 (CONTINUED)

- 1 = Interrupt request enabled

- 0 = Interrupt request not enabled

- bit 1 MI2C1IE: I2C1 Master Events Interrupt Enable bit

- 1 = Interrupt request enabled

- 0 = Interrupt request not enabled

- bit 0 SI2C1IE: I2C1 Slave Events Interrupt Enable bit

- 1 = Interrupt request enabled

- 0 = Interrupt request not enabled

| U-0          | R/W-1                                                                                                                                   | R/W-0                                                                     | R/W-0         | U-0              | R/W-1           | R/W-0           | R/W-0 |  |  |  |  |  |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|---------------|------------------|-----------------|-----------------|-------|--|--|--|--|--|

| —            |                                                                                                                                         | T4IP<2:0>                                                                 |               | —                |                 | OC4IP<2:0>      |       |  |  |  |  |  |

| bit 15       |                                                                                                                                         |                                                                           |               |                  |                 |                 | bit 8 |  |  |  |  |  |

| U-0          | R/W-1                                                                                                                                   | R/W-0                                                                     | R/W-0         | U-0              | R/W-1           | R/W-0           | R/W-0 |  |  |  |  |  |

| _            |                                                                                                                                         | OC3IP<2:0>                                                                |               | —                |                 | DMA2IP<2:0>     |       |  |  |  |  |  |

| bit 7        |                                                                                                                                         |                                                                           |               |                  |                 |                 | bit 0 |  |  |  |  |  |

| Legend:      |                                                                                                                                         |                                                                           |               |                  |                 |                 |       |  |  |  |  |  |

| R = Readab   | le bit                                                                                                                                  | W = Writable                                                              | bit           | U = Unimple      | mented bit, rea | ad as '0'       |       |  |  |  |  |  |

| -n = Value a | t POR                                                                                                                                   | '1' = Bit is set                                                          |               | '0' = Bit is cle | eared           | x = Bit is unkn | own   |  |  |  |  |  |

| bit 15       | Unimpleme                                                                                                                               | nted: Read as '                                                           | )'            |                  |                 |                 |       |  |  |  |  |  |

| bit 14-12    | T4IP<2:0>:                                                                                                                              | Fimer4 Interrupt                                                          | Priority bits |                  |                 |                 |       |  |  |  |  |  |

|              | 111 <b>= Interru</b>                                                                                                                    | 111 = Interrupt is priority 7 (highest priority interrupt)                |               |                  |                 |                 |       |  |  |  |  |  |

|              | •                                                                                                                                       |                                                                           |               |                  |                 |                 |       |  |  |  |  |  |

|              | •                                                                                                                                       | •                                                                         |               |                  |                 |                 |       |  |  |  |  |  |

|              | 001 = Interrupt is priority 1                                                                                                           |                                                                           |               |                  |                 |                 |       |  |  |  |  |  |

|              |                                                                                                                                         | upt source is dis                                                         |               |                  |                 |                 |       |  |  |  |  |  |

| bit 11       | -                                                                                                                                       | nted: Read as '                                                           |               |                  |                 |                 |       |  |  |  |  |  |

| bit 10-8     | OC4IP<2:0>: Output Compare Channel 4 Interrupt Priority bits                                                                            |                                                                           |               |                  |                 |                 |       |  |  |  |  |  |

|              | <ul> <li>111 = Interrupt is priority 7 (highest priority interrupt)</li> </ul>                                                          |                                                                           |               |                  |                 |                 |       |  |  |  |  |  |

|              | •                                                                                                                                       | •                                                                         |               |                  |                 |                 |       |  |  |  |  |  |

|              | •                                                                                                                                       |                                                                           |               |                  |                 |                 |       |  |  |  |  |  |

|              | 001 = Interrupt is priority 1<br>000 = Interrupt source is disabled                                                                     |                                                                           |               |                  |                 |                 |       |  |  |  |  |  |

| bit 7        |                                                                                                                                         | nted: Read as '                                                           |               |                  |                 |                 |       |  |  |  |  |  |

| bit 6-4      | -                                                                                                                                       |                                                                           |               | Interrunt Prior  | rity bits       |                 |       |  |  |  |  |  |

|              | <b>OC3IP&lt;2:0&gt;:</b> Output Compare Channel 3 Interrupt Priority bits<br>111 = Interrupt is priority 7 (highest priority interrupt) |                                                                           |               |                  |                 |                 |       |  |  |  |  |  |

|              | •                                                                                                                                       |                                                                           | 5 1           | , ,              |                 |                 |       |  |  |  |  |  |

|              | •                                                                                                                                       |                                                                           |               |                  |                 |                 |       |  |  |  |  |  |

|              |                                                                                                                                         | upt is priority 1<br>upt source is dis                                    | abled         |                  |                 |                 |       |  |  |  |  |  |

| bit 3        |                                                                                                                                         | •<br>nted: Read as '                                                      |               |                  |                 |                 |       |  |  |  |  |  |

| bit 2-0      | -                                                                                                                                       | DMA2IP<2:0>: DMA Channel 2 Data Transfer Complete Interrupt Priority bits |               |                  |                 |                 |       |  |  |  |  |  |

|              |                                                                                                                                         | upt is priority 7 (I                                                      |               | -                | ·               | -               |       |  |  |  |  |  |

|              | •                                                                                                                                       |                                                                           |               |                  |                 |                 |       |  |  |  |  |  |

|              | •                                                                                                                                       |                                                                           |               |                  |                 |                 |       |  |  |  |  |  |

|              | 001 = Interru                                                                                                                           | pt is priority 1                                                          |               |                  |                 |                 |       |  |  |  |  |  |

|              | 000 = Interri                                                                                                                           | pt source is dis                                                          | ahlad         |                  |                 |                 |       |  |  |  |  |  |

| REGISTER 8-5: | DMAxPAD: DMA CHANNEL x PERIPHERAL ADDRESS REGISTER <sup>(1)</sup> |

|---------------|-------------------------------------------------------------------|

|               |                                                                   |

| R/W-0                              | R/W-0 | R/W-0 | R/W-0 | R/W-0                              | R/W-0 | R/W-0           | R/W-0 |

|------------------------------------|-------|-------|-------|------------------------------------|-------|-----------------|-------|

|                                    |       |       | PAD   | <15:8>                             |       |                 |       |

| bit 15                             |       |       |       |                                    |       |                 | bit 8 |

|                                    |       |       |       |                                    |       |                 |       |

| R/W-0                              | R/W-0 | R/W-0 | R/W-0 | R/W-0                              | R/W-0 | R/W-0           | R/W-0 |

|                                    |       |       | PAE   | )<7:0>                             |       |                 |       |

| bit 7                              |       |       |       |                                    |       |                 | bit 0 |

|                                    |       |       |       |                                    |       |                 |       |

| Legend:                            |       |       |       |                                    |       |                 |       |

| R = Readable bit W = Writable bit  |       |       |       | U = Unimplemented bit, read as '0' |       |                 |       |

| -n = Value at POR '1' = Bit is set |       |       |       | '0' = Bit is cle                   | ared  | x = Bit is unkr | nown  |

|                                    |       |       |       |                                    |       |                 |       |

bit 15-0 PAD<15:0>: Peripheral Address Register bits

**Note 1:** If the channel is enabled (i.e., active), writes to this register may result in unpredictable behavior of the DMA channel and should be avoided.

#### REGISTER 8-6: DMAxCNT: DMA CHANNEL x TRANSFER COUNT REGISTER<sup>(1)</sup>

| U-0                                | U-0   | U-0   | U-0                                    | U-0                                | U-0   | R/W-0 | R/W-0               |

|------------------------------------|-------|-------|----------------------------------------|------------------------------------|-------|-------|---------------------|

| —                                  |       | —     | _                                      | —                                  | —     | CNT<  | 9:8> <sup>(2)</sup> |

| bit 15                             |       |       |                                        |                                    |       | ·     | bit 8               |

|                                    |       |       |                                        |                                    |       |       |                     |

| R/W-0                              | R/W-0 | R/W-0 | R/W-0                                  | R/W-0                              | R/W-0 | R/W-0 | R/W-0               |

|                                    |       |       | CNT                                    | <7:0> <sup>(2)</sup>               |       |       |                     |

| bit 7                              |       |       |                                        |                                    |       |       | bit 0               |

|                                    |       |       |                                        |                                    |       |       |                     |

| Legend:                            |       |       |                                        |                                    |       |       |                     |

| R = Readable bit W = Writable bit  |       |       | bit                                    | U = Unimplemented bit, read as '0' |       |       |                     |

| -n = Value at POR '1' = Bit is set |       |       | '0' = Bit is cleared x = Bit is unknow |                                    |       | nown  |                     |

bit 15-10 Unimplemented: Read as '0'

bit 9-0 CNT<9:0>: DMA Transfer Count Register bits<sup>(2)</sup>

**Note 1:** If the channel is enabled (i.e., active), writes to this register may result in unpredictable behavior of the DMA channel and should be avoided.

2: Number of DMA transfers = CNT<9:0> + 1.

| REGISTER 8-7: DMACS0: DMA CONTROLLER STATUS REGISTER 0 |                                                       |                                                        |                 |                  |                 |                 |        |  |  |

|--------------------------------------------------------|-------------------------------------------------------|--------------------------------------------------------|-----------------|------------------|-----------------|-----------------|--------|--|--|

| R/C-0                                                  | R/C-0                                                 | R/C-0                                                  | R/C-0           | R/C-0            | R/C-0           | R/C-0           | R/C-0  |  |  |

| PWCOL7                                                 | PWCOL6                                                | PWCOL5                                                 | PWCOL4          | PWCOL3           | PWCOL2          | PWCOL1          | PWCOL0 |  |  |

| bit 15                                                 |                                                       |                                                        |                 |                  |                 |                 | bit 8  |  |  |

| R/C-0                                                  | R/C-0                                                 | R/C-0                                                  | R/C-0           | R/C-0            | R/C-0           | R/C-0           | R/C-0  |  |  |

| XWCOL7                                                 | XWCOL6                                                | XWCOL5                                                 | XWCOL4          | XWCOL3           | XWCOL2          | XWCOL1          | XWCOL0 |  |  |

| bit 7                                                  |                                                       |                                                        |                 |                  |                 |                 | bit    |  |  |

| Legend:                                                |                                                       |                                                        |                 | C = Clea         | ar only bit     |                 |        |  |  |

| R = Readable                                           | bit                                                   | W = Writable                                           | bit             |                  | nented bit, rea | d as '0'        |        |  |  |

| -n = Value at I                                        |                                                       | '1' = Bit is set                                       |                 | '0' = Bit is cle |                 | x = Bit is unkr | าดพท   |  |  |

|                                                        |                                                       |                                                        |                 |                  |                 |                 |        |  |  |

| bit 15                                                 | 1 = Write colli                                       | nannel 7 Periph<br>ision detected<br>collision detecte |                 | llision Flag bit |                 |                 |        |  |  |

| bit 14                                                 | 1 = Write colli                                       | nannel 6 Periph<br>ision detected<br>collision detecte |                 | llision Flag bit |                 |                 |        |  |  |

| bit 13                                                 | 1 = Write colli                                       | nannel 5 Periph<br>ision detected<br>collision detecte |                 | llision Flag bit |                 |                 |        |  |  |

| bit 12                                                 | PWCOL4: Channel 4 Peripheral Write Collision Flag bit |                                                        |                 |                  |                 |                 |        |  |  |

|                                                        |                                                       | ision detected collision detected                      | ed              |                  |                 |                 |        |  |  |

| bit 11                                                 | PWCOL3: Ch                                            | nannel 3 Periph                                        | neral Write Col | llision Flag bit |                 |                 |        |  |  |

|                                                        |                                                       | ision detected collision detected                      | ed              |                  |                 |                 |        |  |  |

| bit 10                                                 | 1 = Write colli                                       | nannel 2 Periph<br>ision detected<br>collision detecte |                 | llision Flag bit |                 |                 |        |  |  |

| bit 9                                                  | 1 = Write colli                                       | nannel 1 Periph<br>ision detected<br>collision detecte |                 | llision Flag bit |                 |                 |        |  |  |

| bit 8                                                  | 1 = Write colli                                       | nannel 0 Periph<br>ision detected<br>collision detecte |                 | llision Flag bit |                 |                 |        |  |  |

| bit 7                                                  | XWCOL7: Channel 7 DMA RAM Write Collision Flag bit    |                                                        |                 |                  |                 |                 |        |  |  |

|                                                        |                                                       | ision detected<br>collision detecte                    | ed              |                  |                 |                 |        |  |  |

| bit 6                                                  | XWCOL6: Channel 6 DMA RAM Write Collision Flag bit    |                                                        |                 |                  |                 |                 |        |  |  |

|                                                        |                                                       | ision detected collision detected                      | ed              |                  |                 |                 |        |  |  |

| bit 5                                                  | XWCOL5: Ch                                            | nannel 5 DMA I                                         | RAM Write Co    | Ilision Flag bit |                 |                 |        |  |  |

|                                                        | 1 = Write colli<br>0 = No write c                     | ision detected collision detected                      | ed              |                  |                 |                 |        |  |  |

| bit 4                                                  | XWCOL4: Cr                                            | nannel 4 DMA I                                         | RAM Write Co    | Ilision Flag bit |                 |                 |        |  |  |

|                                                        |                                                       | ision detected<br>collision detecte                    | ed              | -                |                 |                 |        |  |  |

NOTES:

#### **REGISTER 9-1:** OSCCON: OSCILLATOR CONTROL REGISTER<sup>(1,3)</sup> (CONTINUED)

- bit 3 CF: Clock Fail Detect bit (read/clear by application)

- 1 = FSCM has detected clock failure

- 0 = FSCM has not detected clock failure

- bit 2 Unimplemented: Read as '0'

- bit 1 LPOSCEN: Secondary (LP) Oscillator Enable bit

- 1 = Enable secondary oscillator

- 0 = Disable secondary oscillator

- bit 0 OSWEN: Oscillator Switch Enable bit

- 1 = Request oscillator switch to selection specified by NOSC<2:0> bits

- 0 = Oscillator switch is complete

- Note 1: Writes to this register require an unlock sequence. Refer to Section 39. "Oscillator (Part III)" (DS70308) in the "dsPIC33F/PIC24H Family Reference Manual" (available from the Microchip web site) for details.

- 2: Direct clock switches between any primary oscillator mode with PLL and FRCPLL mode are not permitted. This applies to clock switches in either direction. In these instances, the application must switch to FRC mode as a transition clock source between the two PLL modes.

- **3:** This register is reset only on a Power-on Reset (POR).

# REGISTER 11-1: RPINR0: PERIPHERAL PIN SELECT INPUT REGISTER 0

| U-0          | U-0                        | U-0              | R/W-1                                   | R/W-1          | R/W-1            | R/W-1    | R/W-1 |  |  |  |

|--------------|----------------------------|------------------|-----------------------------------------|----------------|------------------|----------|-------|--|--|--|

| _            | _                          | _                |                                         |                | INT1R<4:0>       |          |       |  |  |  |

| bit 15       |                            |                  |                                         |                |                  |          | bit 8 |  |  |  |

|              |                            |                  |                                         |                |                  |          |       |  |  |  |

| U-0          | U-0                        | U-0              | U-0                                     | U-0            | U-0              | U-0      | U-0   |  |  |  |

| _            | —                          | —                | _                                       | —              | —                | —        | —     |  |  |  |

| bit 7        |                            |                  |                                         |                |                  |          | bit 0 |  |  |  |

|              |                            |                  |                                         |                |                  |          |       |  |  |  |

| Legend:      |                            |                  |                                         |                |                  |          |       |  |  |  |

| R = Readab   | le bit                     | W = Writable     | oit                                     | U = Unimpler   | mented bit, read | d as '0' |       |  |  |  |

| -n = Value a | t POR                      | '1' = Bit is set | '0' = Bit is cleared x = Bit is unknown |                |                  |          | nown  |  |  |  |

|              |                            |                  |                                         |                |                  |          |       |  |  |  |

| bit 15-13    | Unimplemented: Read as '0' |                  |                                         |                |                  |          |       |  |  |  |

| bit 12-8     | INT1R<4:0>:                | Assign Externa   | al Interrupt 1                          | (INTR1) to the | corresponding I  | RPn pin  |       |  |  |  |

|              | 11111 <b>– I</b> nnu       | t tigd to V/00   | -                                       |                | -                |          |       |  |  |  |

| 11111 = Input tied to Vss<br>11001 = Input tied to RP25 | , | , | · |  |

|---------------------------------------------------------|---|---|---|--|

| •                                                       |   |   |   |  |

| •                                                       |   |   |   |  |

| 00001 = Input tied to RP1<br>00000 = Input tied to RP0  |   |   |   |  |

| <br>Unimulamented: Deed on (o)                          |   |   |   |  |

#### bit 7-0 Unimplemented: Read as '0'

#### REGISTER 11-2: RPINR1: PERIPHERAL PIN SELECT INPUT REGISTER 1

| U-0                        | U-0                       | U-0              | U-0             | U-0                                | U-0             | U-0                | U-0   |  |

|----------------------------|---------------------------|------------------|-----------------|------------------------------------|-----------------|--------------------|-------|--|

| _                          | —                         | —                | —               | —                                  | —               | —                  | —     |  |

| bit 15                     |                           |                  |                 |                                    |                 |                    | bit 8 |  |

|                            |                           |                  |                 |                                    |                 |                    |       |  |

| U-0                        | U-0                       | U-0              | R/W-1           | R/W-1                              | R/W-1           | R/W-1              | R/W-1 |  |

|                            | —                         | —                |                 |                                    | INT2R<4:0>      |                    |       |  |

| bit 7                      |                           | •                |                 |                                    |                 |                    | bit 0 |  |

|                            |                           |                  |                 |                                    |                 |                    |       |  |

| Legend:                    |                           |                  |                 |                                    |                 |                    |       |  |

| R = Readab                 | le bit                    | W = Writable     | bit             | U = Unimplemented bit, read as '0' |                 |                    |       |  |

| -n = Value a               | It POR                    | '1' = Bit is set |                 | '0' = Bit is cle                   | eared           | x = Bit is unknown |       |  |

|                            |                           |                  |                 |                                    |                 |                    |       |  |

| bit 15-5                   | Unimplemen                | ted: Read as '   | 0'              |                                    |                 |                    |       |  |

| bit 4-0                    | INTR2R<4:0>               | . Assign Exter   | nal Interrupt 2 | 2 (INTR2) to the                   | e corresponding | RPn pin            |       |  |

|                            | 11111 = Input tied to Vss |                  |                 |                                    |                 |                    |       |  |

| 11001 = Input tied to RP25 |                           |                  |                 |                                    |                 |                    |       |  |

| •                          |                           |                  |                 |                                    |                 |                    |       |  |

|                            | •                         |                  |                 |                                    |                 |                    |       |  |

|                            | •                         |                  |                 |                                    |                 |                    |       |  |

|                            | 00001 = Input tied to RP1 |                  |                 |                                    |                 |                    |       |  |

00000 = Input tied to RP0

#### 19.3 Modes of Operation

The ECAN module can operate in one of several operation modes selected by the user. These modes include:

- Initialization mode

- Disable mode

- Normal Operation mode

- Listen Only mode

- Listen All Messages mode

- · Loopback mode

Modes are requested by setting the REQOP<2:0> bits (CiCTRL1<10:8>). Entry into a mode is Acknowledged by monitoring the OPMODE<2:0> bits (CiCTRL1<7:5>). The module does not change the mode and the OPMODE bits until a change in mode is acceptable, generally during bus Idle time, which is defined as at least 11 consecutive recessive bits.

#### 19.3.1 INITIALIZATION MODE

In the Initialization mode, the module does not transmit or receive. The error counters are cleared and the interrupt flags remain unchanged. The user application has access to Configuration registers that are access restricted in other modes. The module protects the user from accidentally violating the CAN protocol through programming errors. All registers which control the configuration of the module cannot be modified while the module is on-line. The ECAN module is not allowed to enter the Configuration mode while a transmission is taking place. The Configuration mode serves as a lock to protect the following registers:

- · All Module Control registers

- Baud Rate and Interrupt Configuration registers

- Bus Timing registers

- Identifier Acceptance Filter registers

- Identifier Acceptance Mask registers

# 19.3.2 DISABLE MODE

In Disable mode, the ECAN module does not transmit or receive. The module can set the WAKIF bit due to bus activity, however, any pending interrupts remains and the error counters retains their value.