Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Active                                                                        |

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 40 MIPs                                                                       |

| Connectivity               | I <sup>2</sup> C, PMP, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                    |

| Number of I/O              | 21                                                                            |

| Program Memory Size        | 32KB (11K x 24)                                                               |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 4K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                     |

| Data Converters            | A/D 10x10b/12b                                                                |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

| Mounting Type              | Through Hole                                                                  |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                       |

| Supplier Device Package    | 28-SPDIP                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24hj32gp302-i-sp |

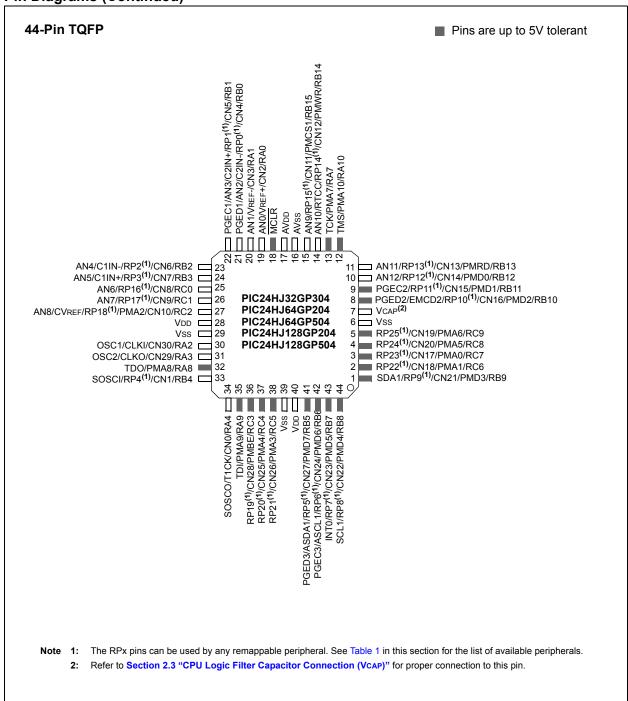

# Pin Diagrams (Continued)

# TABLE 4-15: DMA REGISTER MAP (CONTINUED)

| File Name | Addr | Bit 15                                                       | Bit 14    | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7     | Bit 6  | Bit 5  | Bit 4  | Bit 3     | Bit 2  | Bit 1  | Bit 0  | AII<br>Resets |

|-----------|------|--------------------------------------------------------------|-----------|--------|--------|--------|--------|--------|--------|-----------|--------|--------|--------|-----------|--------|--------|--------|---------------|

| DMA5PAD   | 03C4 |                                                              |           |        |        |        |        |        | P      | AD<15:0>  |        |        |        |           |        |        |        | 0000          |

| DMA5CNT   | 03C6 | -                                                            | _         | _      | _      | -      | -      |        |        |           |        | CNT    | <9:0>  |           |        |        |        | 0000          |

| DMA6CON   | 03C8 | CHEN                                                         | SIZE      | DIR    | HALF   | NULLW  | -      | -      | _      | _         | _      | AMOD   | E<1:0> | _         | _      | MODE   | <1:0>  | 0000          |

| DMA6REQ   | 03CA | FORCE                                                        | _         | _      | _      | -      | -      | -      | _      | _         |        |        | I      | RQSEL<6:0 | >      |        |        | 0000          |

| DMA6STA   | 03CC |                                                              |           |        |        |        |        |        | S      | TA<15:0>  |        |        |        |           |        |        |        | 0000          |

| DMA6STB   | 03CE |                                                              | STB<15:0> |        |        |        |        |        |        |           |        | 0000   |        |           |        |        |        |               |

| DMA6PAD   | 03D0 | PAD<15:0>                                                    |           |        |        |        |        |        |        |           |        | 0000   |        |           |        |        |        |               |

| DMA6CNT   | 03D2 | -                                                            | _         | _      | _      | -      | -      |        |        |           |        | CNT    | <9:0>  |           |        |        |        | 0000          |

| DMA7CON   | 03D4 | CHEN                                                         | SIZE      | DIR    | HALF   | NULLW  | -      | -      | _      | _         | _      | AMOD   | E<1:0> | _         | _      | MODE   | <1:0>  | 0000          |

| DMA7REQ   | 03D6 | FORCE                                                        | -         | _      | ı      | _      | _      | I      | _      | -         |        |        | I      | RQSEL<6:0 | >      |        |        | 0000          |

| DMA7STA   | 03D8 |                                                              |           |        |        |        |        |        | S      | TA<15:0>  |        |        |        |           |        |        |        | 0000          |

| DMA7STB   | 03DA |                                                              |           |        |        |        |        |        | S      | TB<15:0>  |        |        |        |           |        |        |        | 0000          |

| DMA7PAD   | 03DC |                                                              |           |        |        |        |        |        | P      | AD<15:0>  |        |        |        |           |        |        |        | 0000          |

| DMA7CNT   | 03DE | -                                                            | _         | _      | _      | -      | -      |        |        |           |        | CNT    | <9:0>  |           |        |        |        | 0000          |

| DMACS0    | 03E0 | PWCOL7                                                       | PWCOL6    | PWCOL5 | PWCOL4 | PWCOL3 | PWCOL2 | PWCOL1 | PWCOL0 | XWCOL7    | XWCOL6 | XWCOL5 | XWCOL4 | XWCOL3    | XWCOL2 | XWCOL1 | XWCOL0 | 0000          |

| DMACS1    | 03E2 | LSTCH<3:0> PPST7 PPST6 PPST5 PPST4 PPST3 PPST2 PPST1 PPST0 0 |           |        |        |        |        |        |        | 0000      |        |        |        |           |        |        |        |               |

| DSADR     | 03E4 |                                                              |           |        |        |        |        |        | DS     | ADR<15:0> |        |        |        |           |        |        |        | 0000          |

PIC24HJ32GP302/304, PIC24HJ64GPX02/X04 AND PIC24HJ128GPX02/X04

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# 6.3 System Reset

The PIC24HJ32GP302/304, PIC24HJ64GPX02/X04 and PIC24HJ128GPX02/X04 family of devices have two types of Reset:

- · Cold Reset

- · Warm Reset

A cold Reset is the result of a Power-on Reset (POR) or a Brown-out Reset (BOR). On a cold Reset, the FNOSC configuration bits in the FOSC device configuration register selects the device clock source.

A warm Reset is the result of all other reset sources, including the RESET instruction. On warm Reset, the device will continue to operate from the current clock source as indicated by the Current Oscillator Selection bits (COSC<2:0>) in the Oscillator Control register (OSCCON<14:12>).

The device is kept in a Reset state until the system power supplies have stabilized at appropriate levels and the oscillator clock is ready. A description of the sequence in which this occurs and is shown in Figure 6-2.

TABLE 6-1: OSCILLATOR DELAY

| Oscillator Mode           | Oscillator<br>Startup Delay | Oscillator Startup<br>Timer | PLL Lock Time | Total Delay          |

|---------------------------|-----------------------------|-----------------------------|---------------|----------------------|

| FRC, FRCDIV16,<br>FRCDIVN | Toscd                       | _                           | _             | Toscd                |

| FRCPLL                    | Tosco                       | _                           | TLOCK         | Toscd + Tlock        |

| XT                        | Tosco                       | Tost                        | _             | Toscd + Tost         |

| HS                        | Toscd                       | Tost                        | _             | Toscd + Tost         |

| EC                        | _                           | _                           | _             | _                    |

| XTPLL                     | Tosco                       | Tost                        | TLOCK         | Toscd + Tost + Tlock |

| HSPLL                     | Toscd                       | Tost                        | TLOCK         | Toscd + Tost + Tlock |

| ECPLL                     | _                           | _                           | TLOCK         | TLOCK                |

| Sosc                      | Tosco                       | Tost                        | _             | Toscd + Tost         |

| LPRC                      | Toscd                       | _                           | _             | Toscd                |

- **Note 1:** Toscd = Oscillator Start-up Delay (1.1 μs max for FRC, 70 μs max for LPRC). Crystal Oscillator start-up times vary with crystal characteristics, load capacitance, etc.

- 2: Tost = Oscillator Start-up Timer Delay (1024 oscillator clock period). For example, Tost = 102.4 μs for a 10 MHz crystal and Tost = 32 ms for a 32 kHz crystal.

- 3: TLOCK = PLL lock time (1.5 ms nominal), if PLL is enabled.

#### REGISTER 11-17: RPOR2: PERIPHERAL PIN SELECT OUTPUT REGISTERS 2

| U-0    | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0     | R/W-0 | R/W-0 |

|--------|-----|-----|-------|-------|-----------|-------|-------|

| _      | _   | _   |       |       | RP5R<4:0> |       |       |

| bit 15 |     |     |       |       |           |       | bit 8 |

| U-0   | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0     | R/W-0 | R/W-0 |

|-------|-----|-----|-------|-------|-----------|-------|-------|

| _     | _   | _   |       |       | RP4R<4:0> |       |       |

| bit 7 |     |     |       |       |           |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-13 **Unimplemented:** Read as '0'

bit 12-8 RP5R<4:0>: Peripheral Output Function is Assigned to RP5 Output Pin bits (see Table 11-2 for

peripheral function numbers)

bit 7-5 **Unimplemented:** Read as '0'

bit 4-0 RP4R<4:0>: Peripheral Output Function is Assigned to RP4 Output Pin bits (see Table 11-2 for

peripheral function numbers)

### REGISTER 11-18: RPOR3: PERIPHERAL PIN SELECT OUTPUT REGISTERS 3

| U-0    | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0     | R/W-0 | R/W-0 |

|--------|-----|-----|-------|-------|-----------|-------|-------|

| _      | _   | _   |       |       | RP7R<4:0> |       |       |

| bit 15 |     |     |       |       |           |       | bit 8 |

| U-0   | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0     | R/W-0 | R/W-0 |

|-------|-----|-----|-------|-------|-----------|-------|-------|

| _     | _   | _   |       |       | RP6R<4:0> |       |       |

| bit 7 |     |     |       |       |           |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-13 Unimplemented: Read as '0'

bit 12-8 RP7R<4:0>: Peripheral Output Function is Assigned to RP7 Output Pin bits (see Table 11-2 for

peripheral function numbers)

bit 7-5 **Unimplemented:** Read as '0'

bit 4-0 RP6R<4:0>: Peripheral Output Function is Assigned to RP6 Output Pin bits (see Table 11-2 for

peripheral function numbers)

# 16.0 SERIAL PERIPHERAL INTERFACE (SPI)

Note 1: This data sheet summarizes the features of the PIC24HJ32GP302/304, PIC24HJ64GPX02/X04 and PIC24HJ128GPX02/X04 families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 18. "Serial Peripheral Interface (SPI)" (DS70206) of the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Serial Peripheral Interface (SPI) module is a synchronous serial interface useful for communicating with other peripheral or microcontroller devices. These peripheral devices can be serial EEPROMs, shift registers, display drivers, analog-to-digital converters, etc. The SPI module is compatible with Motorola® SPI and SIOP.

Each SPI module consists of a 16-bit shift register, SPIxSR (where x = 1 or 2), used for shifting data in and out, and a buffer register, SPIxBUF. A control register, SPIxCON, configures the module. Additionally, a status register, SPIxSTAT, indicates status conditions.

The serial interface consists of 4 pins:

- · SDIx (serial data input)

- SDOx (serial data output)

- SCKx (shift clock input or output)

- SSx (active-low slave select)

In Master mode operation, SCK is a clock output. In Slave mode, it is a clock input.

FIGURE 16-1: SPI MODULE BLOCK DIAGRAM

# REGISTER 16-3: SPIXCON2: SPIX CONTROL REGISTER 2

| R/W-0  | R/W-0  | R/W-0  | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|--------|--------|-----|-----|-----|-----|-------|

| FRMEN  | SPIFSD | FRMPOL | _   | _   | _   | _   | _     |

| bit 15 |        |        |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0  | U-0   |

|-------|-----|-----|-----|-----|-----|--------|-------|

| _     | _   | _   | _   | _   | _   | FRMDLY | _     |

| bit 7 |     |     |     |     |     |        | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 FRMEN: Framed SPIx Support bit

1 = Framed SPIx support enabled ( $\overline{SSx}$  pin used as frame sync pulse input/output)

0 = Framed SPIx support disabled

bit 14 SPIFSD: Frame Sync Pulse Direction Control bit

1 = Frame sync pulse input (slave)0 = Frame sync pulse output (master)

bit 13 FRMPOL: Frame Sync Pulse Polarity bit

1 = Frame sync pulse is active-high

0 = Frame sync pulse is active-low

bit 12-2 **Unimplemented:** Read as '0'

bit 1 FRMDLY: Frame Sync Pulse Edge Select bit

1 = Frame sync pulse coincides with first bit clock0 = Frame sync pulse precedes first bit clock

bit 0 **Unimplemented:** This bit must not be set to '1' by the user application

# REGISTER 19-11: CIFEN1: ECAN™ ACCEPTANCE FILTER ENABLE REGISTER

| R/W-1   | R/W-1   | R/W-1   | R/W-1   | R/W-1   | R/W-1   | R/W-1  | R/W-1  |

|---------|---------|---------|---------|---------|---------|--------|--------|

| FLTEN15 | FLTEN14 | FLTEN13 | FLTEN12 | FLTEN11 | FLTEN10 | FLTEN9 | FLTEN8 |

| bit 15  |         |         |         |         |         |        | bit 8  |

| R/W-1  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| FLTEN7 | FLTEN6 | FLTEN5 | FLTEN4 | FLTEN3 | FLTEN2 | FLTEN1 | FLTEN0 |

| bit 7  |        |        |        |        |        |        | bit 0  |

Legend:C = Writeable bit, but only '0' can be written to clear the bitR = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

bit 15-0 FLTENn: Enable Filter n to Accept Messages bits

1 = Enable Filter n0 = Disable Filter n

### REGISTER 19-12: CIBUFPNT1: ECAN™ FILTER 0-3 BUFFER POINTER REGISTER

| R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|--------|-------|-------|-------|-------|-------|-------|-------|

|        | F3BP< | <3:0> |       |       | F2BP  | <3:0> |       |

| bit 15 |       |       |       |       |       |       | bit 8 |

| R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0     | R/W-0 | R/W-0 |  |

|-------|-------|-------|-------|-------|-----------|-------|-------|--|

|       | F1BP< | <3:0> |       |       | F0BP<3:0> |       |       |  |

| bit 7 |       |       |       |       |           |       | bit 0 |  |

Legend:C = Writeable bit, but only '0' can be written to clear the bitR = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

bit 15-12 F3BP<3:0>: RX Buffer mask for Filter 3

1111 = Filter hits received in RX FIFO buffer

1110 = Filter hits received in RX Buffer 14

•

•

0001 = Filter hits received in RX Buffer 1

0000 = Filter hits received in RX Buffer 0

bit 11-8 F2BP<3:0>: RX Buffer mask for Filter 2 (same values as bit 15-12) bit 7-4 F1BP<3:0>: RX Buffer mask for Filter 1 (same values as bit 15-12) bit 3-0 F0BP<3:0>: RX Buffer mask for Filter 0 (same values as bit 15-12)

# REGISTER 19-16: CIRXFnSID: ECAN™ ACCEPTANCE FILTER STANDARD IDENTIFIER REGISTER n (n = 0-15)

| R/W-x  | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x |

|--------|-------|-------|-------|-------|-------|-------|-------|

| SID10  | SID9  | SID8  | SID7  | SID6  | SID5  | SID4  | SID3  |

| bit 15 |       |       |       |       |       |       | bit 8 |

| R/W-x | R/W-x | R/W-x | U-0 | R/W-x | U-0 | R/W-x | R/W-x |

|-------|-------|-------|-----|-------|-----|-------|-------|

| SID2  | SID1  | SID0  | _   | EXIDE | _   | EID17 | EID16 |

| bit 7 |       |       |     |       |     |       | bit 0 |

| Legend:           | C = Writeable bit, but only | C = Writeable bit, but only '0' can be written to clear the bit |                    |  |  |  |  |

|-------------------|-----------------------------|-----------------------------------------------------------------|--------------------|--|--|--|--|

| R = Readable bit  | W = Writable bit            | U = Unimplemented bit, read                                     | d as '0'           |  |  |  |  |

| -n = Value at POR | '1' = Bit is set            | '0' = Bit is cleared                                            | x = Bit is unknown |  |  |  |  |

bit 15-5 SID<10:0>: Standard Identifier bits

1 = Message address bit SIDx must be '1' to match filter 0 = Message address bit SIDx must be '0' to match filter

bit 4 Unimplemented: Read as '0'

bit 3 **EXIDE:** Extended Identifier Enable bit

If MIDE = 1, then:

1 = Match only messages with extended identifier addresses0 = Match only messages with standard identifier addresses

$\frac{\text{If MIDE = 0, then:}}{\text{Ignore the EXIDE bit.}}$

bit 2 Unimplemented: Read as '0'

bit 1-0 **EID<17:16>:** Extended Identifier bits

1 = Message address bit EIDx must be '1' to match filter 0 = Message address bit EIDx must be '0' to match filter

# Register 24-2: PMMODE: PARALLEL PORT MODE REGISTER

Legend:

| R-0    | R/W-0 | R/W-0  | R/W-0 | R/W-0  | R/W-0  | R/W-0 | R/W-0  |

|--------|-------|--------|-------|--------|--------|-------|--------|

| BUSY   | IRQM  | l<1:0> | INCM  | l<1:0> | MODE16 | MODE  | E<1:0> |

| bit 15 |       |        |       |        |        |       | bit 8  |

| R/W-0 | R/W-0                     | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 | R/W-0                |

|-------|---------------------------|-------|-------|--------|-------|-------|----------------------|

| WAITB | WAITB<1:0> <sup>(1)</sup> |       | WAIT  | M<3:0> |       | WAITE | <1:0> <sup>(1)</sup> |

| bit 7 |                           |       |       |        |       |       | bit 0                |

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknownbit 15 **BUSY:** Busy bit (Master mode only) 1 = Port is busy (not useful when the processor stall is active) 0 = Port is not busy bit 14-13 IRQM<1:0>: Interrupt Request Mode bits 11 = Interrupt generated when Read Buffer 3 is read or Write Buffer 3 is written (Buffered PSP mode) or on a read or write operation when PMA<1:0> = 11 (Addressable PSP mode only) 10 = No interrupt generated, processor stall activated 01 = Interrupt generated at the end of the read/write cycle 00 = No interrupt generated bit 12-11 INCM<1:0>: Increment Mode bits 11 = PSP read and write buffers auto-increment (Legacy PSP mode only) 10 = Decrement ADDR<10:0> by 1 every read/write cycle 01 = Increment ADDR<10:0> by 1 every read/write cycle 00 = No increment or decrement of address bit 10 MODE16: 8/16-bit Mode bit 1 = 16-bit mode: data register is 16 bits, a read or write to the data register invokes two 8-bit transfers 0 = 8-bit mode: data register is 8 bits, a read or write to the data register invokes one 8-bit transfer bit 9-8 MODE<1:0>: Parallel Port Mode Select bits 11 =Master mode 1 (PMCS1, PMRD/PMWR, PMENB, PMBE, PMA<x:0> and PMD<7:0>) 10 =Master mode 2 (PMCS1, PMRD, PMWR, PMBE, PMA<x:0> and PMD<7:0>) 01 =Enhanced PSP, control signals (PMRD, PMWR, PMCS1, PMD<7:0> and PMA<1:0>) 00 =Legacy Parallel Slave Port, control signals (PMRD, PMWR, PMCS1 and PMD<7:0>) WAITB<1:0>: Data Setup to Read/Write Wait State Configuration bits(1) bit 7-6 11 = Data wait of 4 Tcy; multiplexed address phase of 4 Tcy 10 = Data wait of 3 Tcy; multiplexed address phase of 3 Tcy 01 = Data wait of 2 Tcy; multiplexed address phase of 2 Tcy 00 = Data wait of 1 Tcy; multiplexed address phase of 1 Tcy bit 5-2 WAITM<3:0>: Read to Byte Enable Strobe Wait State Configuration bits 1111 = Wait of additional 15 Tcy

Note 1: WAITB and WAITE bits are ignored whenever WAITM3:WAITM0 = 0000.

0000 = No additional wait cycles (operation forced into one Tcy)

**WAITE<1:0>:** Data Hold After Strobe Wait State Configuration bits<sup>(1)</sup>

0001 = Wait of additional 1 Tcy

11 = Wait of 4 Tcy 10 = Wait of 3 Tcy 01 = Wait of 2 Tcy 00 = Wait of 1 Tcy

bit 1-0

TABLE 25-2: PIC24H CONFIGURATION BITS DESCRIPTION (CONTINUED)

| Bit Field               | Register           | RTSP Effect                                                                                         | Description                                                                                                                                                                                                                                                                                                                                                                         |

|-------------------------|--------------------|-----------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RSS<1:0> <sup>(1)</sup> | FSS <sup>(1)</sup> | Immediate                                                                                           | Secure Segment RAM Code Protection  11 = No Secure RAM defined  10 = Secure RAM is 256 Bytes less BS RAM  01 = Secure RAM is 2048 Bytes less BS RAM  00 = Secure RAM is 4096 Bytes less BS RAM                                                                                                                                                                                      |

| GSS<1:0>                | FGS                | Immediate                                                                                           | General Segment Code-Protect bit  11 = User program memory is not code-protected  10 = Standard security  0x = High security                                                                                                                                                                                                                                                        |

| GWRP                    | FGS                | Immediate                                                                                           | General Segment Write-Protect bit  1 = User program memory is not write-protected  0 = User program memory is write-protected                                                                                                                                                                                                                                                       |

| IESO                    | FOSCSEL            | Immediate                                                                                           | Two-speed Oscillator Start-up Enable bit  1 = Start-up device with FRC, then automatically switch to the user-selected oscillator source when ready  0 = Start-up device with user-selected oscillator source                                                                                                                                                                       |

| FNOSC<2:0>              | FOSCSEL            | If clock switch is<br>enabled, RTSP<br>effect is on any<br>device Reset;<br>otherwise,<br>Immediate | Initial Oscillator Source Selection bits  111 = Internal Fast RC (FRC) oscillator with postscaler  110 = Internal Fast RC (FRC) oscillator with divide-by-16  101 = LPRC oscillator  100 = Secondary (LP) oscillator  011 = Primary (XT, HS, EC) oscillator with PLL  010 = Primary (XT, HS, EC) oscillator  001 = Internal Fast RC (FRC) oscillator with PLL  000 = FRC oscillator |

| FCKSM<1:0>              | FOSC               | Immediate                                                                                           | Clock Switching Mode bits $1x = \text{Clock}$ switching is disabled, Fail-Safe Clock Monitor is disabled $01 = \text{Clock}$ switching is enabled, Fail-Safe Clock Monitor is disabled $00 = \text{Clock}$ switching is enabled, Fail-Safe Clock Monitor is enabled                                                                                                                 |

| IOL1WAY                 | FOSC               | Immediate                                                                                           | Peripheral pin select configuration  1 = Allow only one reconfiguration  0 = Allow multiple reconfigurations                                                                                                                                                                                                                                                                        |

| OSCIOFNC                | FOSC               | Immediate                                                                                           | OSC2 Pin Function bit (except in XT and HS modes)  1 = OSC2 is clock output  0 = OSC2 is general purpose digital I/O pin                                                                                                                                                                                                                                                            |

| POSCMD<1:0>             | FOSC               | Immediate                                                                                           | Primary Oscillator Mode Select bits  11 = Primary oscillator disabled  10 = HS Crystal Oscillator mode  01 = XT Crystal Oscillator mode  00 = EC (External Clock) mode                                                                                                                                                                                                              |

| FWDTEN                  | FWDT               | Immediate                                                                                           | Watchdog Timer Enable bit  1 = Watchdog Timer always enabled (LPRC oscillator cannot be disabled. Clearing the SWDTEN bit in the RCON register has no effect.)  0 = Watchdog Timer enabled/disabled by user software (LPRC can be disabled by clearing the SWDTEN bit in the RCON register)                                                                                         |

| WINDIS                  | FWDT               | Immediate                                                                                           | Watchdog Timer Window Enable bit  1 = Watchdog Timer in Non-Window mode  0 = Watchdog Timer in Window mode                                                                                                                                                                                                                                                                          |

**Note 1:** This Configuration register is not available on PIC24HJ32GP302/304 devices.

TABLE 26-1: SYMBOLS USED IN OPCODE DESCRIPTIONS

| Field           | Description                                                                                                   |

|-----------------|---------------------------------------------------------------------------------------------------------------|

| #text           | Means literal defined by "text"                                                                               |

| (text)          | Means "content of text"                                                                                       |

| [text]          | Means "the location addressed by text"                                                                        |

| { }             | Optional field or operation                                                                                   |

| <n:m></n:m>     | Register bit field                                                                                            |

| .b              | Byte mode selection                                                                                           |

| .d              | Double Word mode selection                                                                                    |

| .S              | Shadow register select                                                                                        |

| .w              | Word mode selection (default)                                                                                 |

| bit4            | 4-bit bit selection field (used in word addressed instructions) ∈ {015}                                       |

| C, DC, N, OV, Z | MCU Status bits: Carry, Digit Carry, Negative, Overflow, Sticky Zero                                          |

| Expr            | Absolute address, label or expression (resolved by the linker)                                                |

| f               | File register address ∈ {0x00000x1FFF}                                                                        |

| lit1            | 1-bit unsigned literal ∈ {0,1}                                                                                |

| lit4            | 4-bit unsigned literal ∈ {015}                                                                                |

| lit5            | 5-bit unsigned literal ∈ {031}                                                                                |

| lit8            | 8-bit unsigned literal ∈ {0255}                                                                               |

| lit10           | 10-bit unsigned literal ∈ {0255} for Byte mode, {0:1023} for Word mode                                        |

| lit14           | 14-bit unsigned literal ∈ {016384}                                                                            |

| lit16           | 16-bit unsigned literal ∈ {065535}                                                                            |

| lit23           | 23-bit unsigned literal ∈ {08388608}; LSB must be '0'                                                         |

| None            | Field does not require an entry, may be blank                                                                 |

| PC              | Program Counter                                                                                               |

| Slit10          | 10-bit signed literal ∈ {-512511}                                                                             |

| Slit16          | 16-bit signed literal ∈ {-3276832767}                                                                         |

| Slit6           | 6-bit signed literal ∈ {-1616}                                                                                |

| Wb              | Base W register ∈ {W0W15}                                                                                     |

| Wd              | Destination W register ∈ { Wd, [Wd], [Wd++], [Wd], [++Wd], [Wd] }                                             |

| Wdo             | Destination W register ∈ { Wnd, [Wnd], [Wnd++], [Wnd], [++Wnd], [Wnd], [Wnd+Wb] }                             |

| Wm,Wn           | Dividend, Divisor working register pair (direct addressing)                                                   |

| Wm*Wm           | Multiplicand and Multiplier working register pair for Square instructions ∈ {W4 * W4,W5 * W5,W6 * W6,W7 * W7} |

| Wn              | One of 16 working registers ∈ {W0W15}                                                                         |

| Wnd             | One of 16 destination working registers ∈ {W0W15}                                                             |

| Wns             | One of 16 source working registers ∈ {W0W15}                                                                  |

| WREG            | W0 (working register used in file register instructions)                                                      |

| Ws              | Source W register ∈ { Ws, [Ws], [Ws++], [Ws], [++Ws], [Ws] }                                                  |

| Wso             | Source W register ∈ { Wns, [Wns++], [Wns], [++Wns], [Wns], [Wns+Wb] }                                         |

# 27.11 PICkit 2 Development Programmer/Debugger and PICkit 2 Debug Express

The PICkit™ 2 Development Programmer/Debugger is a low-cost development tool with an easy to use interface for programming and debugging Microchip's Flash families of microcontrollers. The full featured Windows<sup>®</sup> programming interface supports baseline (PIC10F, PIC12F5xx, PIC16F5xx), (PIC12F6xx, PIC16F), PIC18F, PIC24, dsPIC30, dsPIC33, and PIC32 families of 8-bit, 16-bit, and 32-bit microcontrollers, and many Microchip Serial EEPROM products. With Microchip's powerful MPLAB Integrated Development Environment (IDE) the PICkit™ 2 in-circuit debugging on most PIC® enables microcontrollers. In-Circuit-Debugging runs, halts and single steps the program while the PIC microcontroller is embedded in the application. When halted at a breakpoint, the file registers can be examined and modified.

The PICkit 2 Debug Express include the PICkit 2, demo board and microcontroller, hookup cables and CDROM with user's guide, lessons, tutorial, compiler and MPLAB IDE software.

### 27.12 MPLAB PM3 Device Programmer

The MPLAB PM3 Device Programmer is a universal, CE compliant device programmer with programmable voltage verification at VDDMIN and VDDMAX for maximum reliability. It features a large LCD display (128 x 64) for menus and error messages and a modular, detachable socket assembly to support various package types. The ICSP™ cable assembly is included as a standard item. In Stand-Alone mode, the MPLAB PM3 Device Programmer can read, verify and program PIC devices without a PC connection. It can also set code protection in this mode. The MPLAB PM3 connects to the host PC via an RS-232 or USB cable. The MPLAB PM3 has high-speed communications and optimized algorithms for quick programming of large memory devices and incorporates an MMC card for file storage and data applications.

# 27.13 Demonstration/Development Boards, Evaluation Kits, and Starter Kits

A wide variety of demonstration, development and evaluation boards for various PIC MCUs and dsPIC DSCs allows quick application development on fully functional systems. Most boards include prototyping areas for adding custom circuitry and provide application firmware and source code for examination and modification.

The boards support a variety of features, including LEDs, temperature sensors, switches, speakers, RS-232 interfaces, LCD displays, potentiometers and additional EEPROM memory.

The demonstration and development boards can be used in teaching environments, for prototyping custom circuits and for learning about various microcontroller applications.

In addition to the PICDEM™ and dsPICDEM™ demonstration/development board series of circuits, Microchip has a line of evaluation kits and demonstration software for analog filter design, Keeloq® security ICs, CAN, IrDA®, PowerSmart battery management, SEEVAL® evaluation system, Sigma-Delta ADC, flow rate sensing, plus many more.

Also available are starter kits that contain everything needed to experience the specified device. This usually includes a single application and debug capability, all on one board.

Check the Microchip web page (www.microchip.com) for the complete list of demonstration, development and evaluation kits.

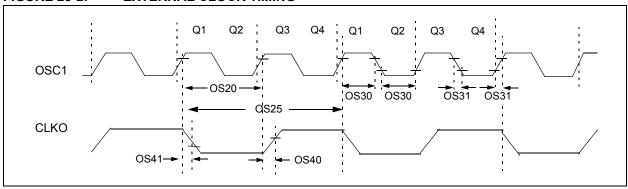

FIGURE 28-2: EXTERNAL CLOCK TIMING

**TABLE 28-16: EXTERNAL CLOCK TIMING REQUIREMENTS**

| AC CHA       | AC CHARACTERISTICS |                                                                                    |                                        | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated) Operating temperature -40°C ≤ TA ≤ +85°C for Industrial -40°C ≤ TA ≤ +125°C for Extended |                |                   |                          |  |

|--------------|--------------------|------------------------------------------------------------------------------------|----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|-------------------|--------------------------|--|

| Param<br>No. | Symb               | Characteristic                                                                     | Min Typ <sup>(1)</sup> Max Units Condi |                                                                                                                                                                |                |                   | Conditions               |  |

| OS10         | FIN                | External CLKI Frequency<br>(External clocks allowed only<br>in EC and ECPLL modes) | DC                                     | _                                                                                                                                                              | 40             | MHz               | EC                       |  |

|              |                    | Oscillator Crystal Frequency                                                       | 3.5<br>10                              |                                                                                                                                                                | 10<br>40<br>33 | MHz<br>MHz<br>kHz | XT<br>HS<br>Sosc         |  |

| OS20         | Tosc               | Tosc = 1/Fosc                                                                      | 12.5                                   | _                                                                                                                                                              | DC             | ns                |                          |  |

| OS25         | Tcy                | Instruction Cycle Time <sup>(2)</sup>                                              | 25                                     | _                                                                                                                                                              | DC             | ns                |                          |  |

| OS30         | TosL,<br>TosH      | External Clock in (OSC1)<br>High or Low Time                                       | 0.375 x Tosc                           | _                                                                                                                                                              | 0.625 x Tosc   | ns                | EC                       |  |

| OS31         | TosR,<br>TosF      | External Clock in (OSC1)<br>Rise or Fall Time                                      | _                                      | _                                                                                                                                                              | 20             | ns                | EC                       |  |

| OS40         | TckR               | CLKO Rise Time <sup>(3)</sup>                                                      | _                                      | 5.2                                                                                                                                                            | _              | ns                | _                        |  |

| OS41         | TckF               | CLKO Fall Time <sup>(3)</sup>                                                      | _                                      | 5.2                                                                                                                                                            | _              | ns                | _                        |  |

| OS42         | Gм                 | External Oscillator<br>Transconductance <sup>(4)</sup>                             | 14                                     | 16                                                                                                                                                             | 18             | mA/V              | VDD = 3.3V<br>TA = +25°C |  |

**Note 1:** Data in "Typ" column is at 3.3V, 25°C unless otherwise stated.

- 2: Instruction cycle period (TCY) equals two times the input oscillator time-base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min." values with an external clock applied to the OSC1/CLKI pin. When an external clock input is used, the "max." cycle time limit is "DC" (no clock) for all devices.

- 3: Measurements are taken in EC mode. The CLKO signal is measured on the OSC2 pin.

- 4: Data for this parameter is Preliminary. This parameter is characterized, but not tested in manufacturing.

# PIC24HJ32GP302/304, PIC24HJ64GPX02/X04 AND PIC24HJ128GPX02/X04

TABLE 28-32: SPIX SLAVE MODE (FULL-DUPLEX, CKE = 1, CKP = 0, SMP = 0) TIMING REQUIREMENTS

| AC CHA       | ARACTERIST            | rics                                                  | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated) Operating temperature -40°C ≤TA ≤+85°C for Industrial -40°C ≤TA ≤+125°C for Extended |                    |     |       |                                      |  |

|--------------|-----------------------|-------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----|-------|--------------------------------------|--|

| Param<br>No. | Symbol                | Characteristic <sup>(1)</sup>                         | Min                                                                                                                                                        | Typ <sup>(2)</sup> | Max | Units | Conditions                           |  |

| SP70         | TscP                  | Maximum SCK Input Frequency                           | _                                                                                                                                                          | _                  | 15  | MHz   | See Note 3                           |  |

| SP72         | TscF                  | SCKx Input Fall Time                                  | _                                                                                                                                                          |                    |     | ns    | See parameter DO32 and Note 4        |  |

| SP73         | TscR                  | SCKx Input Rise Time                                  |                                                                                                                                                            |                    | l   | ns    | See parameter DO31 and Note 4        |  |

| SP30         | TdoF                  | SDOx Data Output Fall Time                            |                                                                                                                                                            |                    |     | ns    | See parameter DO32 and <b>Note 4</b> |  |

| SP31         | TdoR                  | SDOx Data Output Rise Time                            | _                                                                                                                                                          | _                  | _   | ns    | See parameter DO31 and Note 4        |  |

| SP35         | TscH2doV,<br>TscL2doV | SDOx Data Output Valid after SCKx Edge                | _                                                                                                                                                          | 6                  | 20  | ns    | _                                    |  |

| SP36         | TdoV2scH,<br>TdoV2scL | SDOx Data Output Setup to First SCKx Edge             | 30                                                                                                                                                         | _                  | _   | ns    | _                                    |  |

| SP40         | TdiV2scH,<br>TdiV2scL | Setup Time of SDIx Data Input to SCKx Edge            | 30                                                                                                                                                         | _                  | _   | ns    | _                                    |  |

| SP41         | TscH2diL,<br>TscL2diL | Hold Time of SDIx Data Input to SCKx Edge             | 30                                                                                                                                                         |                    | _   | ns    | _                                    |  |

| SP50         | TssL2scH,<br>TssL2scL | SSx ↓to SCKx ↑ or SCKx Input                          | 120                                                                                                                                                        | -                  | _   | ns    | _                                    |  |

| SP51         | TssH2doZ              | SSx ↑ to SDOx Output<br>High-Impedance <sup>(4)</sup> | 10                                                                                                                                                         | _                  | 50  | ns    | _                                    |  |

| SP52         | TscH2ssH<br>TscL2ssH  | SSx after SCKx Edge                                   | 1.5 Tcy + 40                                                                                                                                               | _                  | _   | ns    | See Note 4                           |  |

| SP60         | TssL2doV              | SDOx Data Output Valid after SSx Edge                 | _                                                                                                                                                          | _                  | 50  | ns    | _                                    |  |

Note 1: These parameters are characterized, but are not tested in manufacturing.

<sup>2:</sup> Data in "Typ" column is at 3.3V, 25°C unless otherwise stated.

**<sup>3:</sup>** The minimum clock period for SCKx is 66.7 ns. Therefore, the SCK clock generated by the Master must not violate this specification.

<sup>4:</sup> Assumes 50 pF load on all SPIx pins.

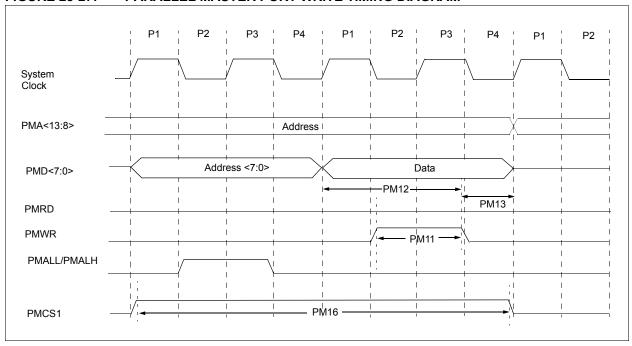

FIGURE 28-27: PARALLEL MASTER PORT WRITE TIMING DIAGRAM

TABLE 28-50: PARALLEL MASTER PORT WRITE TIMING REQUIREMENTS

| AC CH        | ARACTERISTICS                                                       | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$ for Extended |         |      |       |            |

|--------------|---------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------|-------|------------|

| Param<br>No. | Characteristic                                                      | Min.                                                                                                                                                                                                                                             | Тур     | Max. | Units | Conditions |

| PM11         | PMWR Pulse Width                                                    | _                                                                                                                                                                                                                                                | 0.5 TcY | _    | ns    | _          |

| PM12         | Data Out Valid before PMWR or PMENB goes Inactive (data setup time) | _                                                                                                                                                                                                                                                | _       | _    | ns    | _          |

| PM13         | PMWR or PMEMB Invalid to Data Out Invalid (data hold time)          | _                                                                                                                                                                                                                                                | _       | _    | ns    | _          |

| PM16         | PMCSx Pulse Width                                                   | Tcy - 5                                                                                                                                                                                                                                          | _       | _    | ns    | _          |

TABLE 28-51: DMA READ/WRITE TIMING REQUIREMENTS

| AC CH        | ARACTERISTICS             | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated)  Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$ for Extended |  |  |  |            |  |

|--------------|---------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|------------|--|

| Param<br>No. | Characteristic            | Min. Typ Max. Units Condition                                                                                                                                                                                                                     |  |  |  | Conditions |  |

| DM1          | DMA Read/Write Cycle Time | 1 Tcy ns _                                                                                                                                                                                                                                        |  |  |  | _          |  |

TABLE 29-10: SPIx MASTER MODE (CKE = 0) TIMING REQUIREMENTS

| _            | AC<br>TERISTICS       | Standard Operating Conditions Operating temperature -40°C |     | •   |     |       | tated)     |

|--------------|-----------------------|-----------------------------------------------------------|-----|-----|-----|-------|------------|

| Param<br>No. | Symbol                | Characteristic <sup>(1)</sup>                             | Min | Тур | Max | Units | Conditions |

| HSP35        | TscH2doV,<br>TscL2doV | SDOx Data Output Valid after<br>SCKx Edge                 | _   | 10  | 25  | ns    | _          |

| HSP40        | TdiV2scH,<br>TdiV2scL | Setup Time of SDIx Data Input to SCKx Edge                | 28  | _   | _   | ns    | _          |

| HSP41        | TscH2diL,<br>TscL2diL | Hold Time of SDIx Data Input to SCKx Edge                 | 35  | _   |     | ns    | _          |

Note 1: These parameters are characterized but not tested in manufacturing.

TABLE 29-11: SPIX MODULE MASTER MODE (CKE = 1) TIMING REQUIREMENTS

|              | AC<br>CTERISTICS      | Standard Operating Conditions Operating temperature -40°C ≤ | ated) |     |     |       |            |

|--------------|-----------------------|-------------------------------------------------------------|-------|-----|-----|-------|------------|

| Param<br>No. | Symbol                | Characteristic <sup>(1)</sup>                               | Min   | Тур | Max | Units | Conditions |

| HSP35        | TscH2doV,<br>TscL2doV | SDOx Data Output Valid after<br>SCKx Edge                   | _     | 10  | 25  | ns    | _          |

| HSP36        | TdoV2sc,<br>TdoV2scL  | SDOx Data Output Setup to First SCKx Edge                   | 35    | _   | _   | ns    | _          |

| HSP40        | TdiV2scH,<br>TdiV2scL | Setup Time of SDIx Data Input to SCKx Edge                  | 28    | _   | _   | ns    | _          |

| HSP41        | TscH2diL,<br>TscL2diL | Hold Time of SDIx Data Input to SCKx Edge                   | 35    |     | 1   | ns    | _          |

**Note 1:** These parameters are characterized but not tested in manufacturing.

# **Revision E (January 2011)**

This includes typographical and formatting changes throughout the data sheet text. In addition, the Preliminary marking in the footer was removed.

All occurrences of  $\ensuremath{\mathsf{VDDCORE}}$  have been removed throughout the document.

All other major changes are referenced by their respective section in the following table.

TABLE A-4: MAJOR SECTION UPDATES

| Section Name                                                              | Update Description                                                                                                                       |

|---------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|

| "High-Performance, 16-bit Microcontrollers"                               | The high temperature end range was updated to +150°C (see "Operating Range:").                                                           |

| Section 2.0 "Guidelines for Getting Started with 16-bit Microcontrollers" | The frequency limitation for device PLL start-up conditions was updated in Section 2.7 "Oscillator Value Conditions on Device Start-up". |

|                                                                           | The second paragraph in Section 2.9 "Unused I/Os" was updated.                                                                           |

| Section 4.0 "Memory Organization"                                         | The All Resets values for the following SFRs in the Timer Register Map were changed (see Table 4-5):                                     |

|                                                                           | • TMR1                                                                                                                                   |

|                                                                           | • TMR2                                                                                                                                   |

|                                                                           | • TMR3                                                                                                                                   |

|                                                                           | • TMR4                                                                                                                                   |

|                                                                           | • TMR5                                                                                                                                   |

| Section 9.0 "Oscillator Configuration"                                    | Added Note 3 to the OSCCON: Oscillator Control Register (see Register 9-1).                                                              |

|                                                                           | Added Note 2 to the CLKDIV: Clock Divisor Register (see Register 9-2).                                                                   |

|                                                                           | Added Note 1 to the PLLFBD: PLL Feedback Divisor Register (see Register 9-3).                                                            |

|                                                                           | Added Note 2 to the OSCTUN: FRC Oscillator Tuning Register (see Register 9-4).                                                           |

| Section 20.0 "10-bit/12-bit Analog-to-Digital Converter (ADC1)"           | Updated the VREFL references in the ADC1 module block diagrams (see Figure 20-1 and Figure 20-2).                                        |

| Section 25.0 "Special Features"                                           | Added a new paragraph and removed the third paragraph in Section 25.1 "Configuration Bits".                                              |

|                                                                           | Added the column "RTSP Effects" to the dsPIC33F Configuration Bits Descriptions (see Table 25-2).                                        |

# **Revision F (August 2011)**

This revision includes typographical and formatting changes throughout the data sheet text.

All other major changes are referenced by their respective section in the following table.

TABLE A-5: MAJOR SECTION UPDATES

| Section Name                              | Update Description                                                                                                                 |

|-------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|

| Section 25.0 "Special Features"           | Added Note 3 to the Connections for the On-chip Voltage Regulator diagram (see Figure 25-1).                                       |

| Section 28.0 "Electrical Characteristics" | Removed Voltage on VCAP with respect to Vss from the Absolute Maximum Ratings.                                                     |

|                                           | Removed Note 3 and parameter DC10 (VCORE) from the DC Temperature and Voltage Specifications (see Table 28-4).                     |

|                                           | Updated the Characteristics definition and Conditions for parameter BO10 in the Electrical Characteristics: BOR (see Table 28-11). |

|                                           | Added Note 1 to the Internal Voltage Regulator Specifications (see Table 28-13).                                                   |

# **Revision G (April 2012)**

This revision includes typographical and formatting changes throughout the data sheet text.

In addition, where applicable, new sections were added to each peripheral chapter that provide information and links to related resources, as well as helpful tips. For examples, see Section 9.2 "Oscillator Resources" and Section 20.4 "ADC Helpful Tips".

All other major changes are referenced by their respective section in the following table.

TABLE A-6: MAJOR SECTION UPDATES

| Section Name                                                              | Update Description                                                                                                                               |

|---------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| Section 2.0 "Guidelines for Getting Started with 16-bit Microcontrollers" | Added two new tables:  Crystal Recommendations (see Table 2-1)  Resonator Recommendations (see Table 2-2)                                        |

| Section 28.0 "Electrical Characteristics"                                 | Updated parameters DO10 and DO20 and removed parameters DO16 and DO26 in the DC Characteristics: I/O Pin Output Specifications (see Table 28-10) |

### THE MICROCHIP WEB SITE

Microchip provides online support via our WWW site at www.microchip.com. This web site is used as a means to make files and information easily available to customers. Accessible by using your favorite Internet browser, the web site contains the following information:

- Product Support Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQs), technical support requests, online discussion groups, Microchip consultant program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

# CUSTOMER CHANGE NOTIFICATION SERVICE

Microchip's customer notification service helps keep customers current on Microchip products. Subscribers will receive e-mail notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, access the Microchip web site at www.microchip.com. Under "Support", click on "Customer Change Notification" and follow the registration instructions.

### **CUSTOMER SUPPORT**

Users of Microchip products can receive assistance through several channels:

- · Distributor or Representative

- · Local Sales Office

- Field Application Engineer (FAE)

- Technical Support

- · Development Systems Information Line

Customers should contact their distributor, representative or field application engineer (FAE) for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in the back of this document.

Technical support is available through the web site at: http://microchip.com/support

| TES: |  |  |

|------|--|--|

|      |  |  |

|      |  |  |

|      |  |  |

|      |  |  |

|      |  |  |

|      |  |  |

|      |  |  |

|      |  |  |

|      |  |  |

|      |  |  |

|      |  |  |

|      |  |  |

|      |  |  |

|      |  |  |

|      |  |  |

|      |  |  |