Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Active                                                                        |

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 40 MIPs                                                                       |

| Connectivity               | I <sup>2</sup> C, PMP, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                    |

| Number of I/O              | 35                                                                            |

| Program Memory Size        | 32KB (11K x 24)                                                               |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 4K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                     |

| Data Converters            | A/D 13x10b/12b                                                                |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

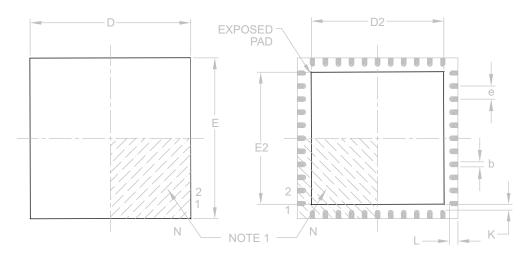

| Mounting Type              | Surface Mount                                                                 |

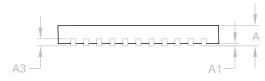

| Package / Case             | 44-VQFN Exposed Pad                                                           |

| Supplier Device Package    | 44-QFN (8x8)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24hj32gp304-i-ml |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| File Name  | Addr          | Bit 15 | Bit 14             | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8                      | Bit 7                      | Bit 6    | Bit 5    | Bit 4 | Bit 3  | Bit 2     | Bit 1  | Bit 0  | All<br>Resets |

|------------|---------------|--------|--------------------|--------|--------|--------|--------|--------|----------------------------|----------------------------|----------|----------|-------|--------|-----------|--------|--------|---------------|

|            | 0400-<br>041E |        |                    |        |        |        |        |        | See defini                 | tion when V                | VIN = x  |          |       |        |           |        |        |               |

| C1BUFPNT1  | 0420          |        | F3BF               | P<3:0> |        |        | F2BF   | P<3:0> |                            |                            | F1BP     | <3:0>    |       |        | F0BP<3:0> |        |        | 0000          |

| C1BUFPNT2  | 0422          |        | F7BF               | P<3:0> |        |        | F6BF   | P<3:0> |                            |                            | F5BP     | <3:0>    |       |        | F4BP      | <3:0>  |        | 0000          |

| C1BUFPNT3  | 0424          |        | F11B               | P<3:0> |        |        | F10B   | P<3:0> |                            |                            | F9BP     | <3:0>    |       |        | F8BP      | <3:0>  |        | 0000          |

| C1BUFPNT4  | 0426          |        | F15B               | P<3:0> |        |        | F14B   | P<3:0> |                            |                            | F13BF    | P<3:0>   |       |        | F12BF     | ><3:0> |        | 0000          |

| C1RXM0SID  | 0430          |        |                    |        | SID<   | 10:3>  |        |        |                            |                            | SID<2:0> |          | —     | MIDE   | _         | EID<   | 17:16> | XXXX          |

| C1RXM0EID  | 0432          |        |                    |        | EID<   | 15:8>  |        |        |                            |                            |          |          | EID<  | :7:0>  |           |        |        | XXXX          |

| C1RXM1SID  | 0434          |        |                    |        | SID<   | 10:3>  |        |        |                            | SID<2:0> — MIDE —          |          |          |       | EID<   | 17:16>    | XXXX   |        |               |

| C1RXM1EID  | 0436          |        | EID<15:8> EID<7:0> |        |        |        |        | 7:0>   |                            | _                          |          | XXXX     |       |        |           |        |        |               |

| C1RXM2SID  | 0438          |        |                    |        | SID<   | 10:3>  |        |        |                            |                            | SID<2:0> |          | —     | MIDE   | —         | EID<   | 17:16> | XXXX          |

| C1RXM2EID  | 043A          |        | EID<15:8>          |        |        |        |        |        |                            |                            |          | EID<     | 7:0>  |        |           |        | XXXX   |               |

| C1RXF0SID  | 0440          |        | SID<10:3>          |        |        |        |        |        | SID<2:0> — EXIDE — EID<17: |                            |          |          |       | 17:16> | XXXX      |        |        |               |

| C1RXF0EID  | 0442          |        | EID<15:8>          |        |        |        |        |        |                            |                            |          | EID<     | 7:0>  |        |           |        | XXXX   |               |

| C1RXF1SID  | 0444          |        | SID<10:3>          |        |        |        |        |        | SID<2:0>                   |                            | —        | EXIDE    | —     | EID<   | 17:16>    | XXXX   |        |               |

| C1RXF1EID  | 0446          |        | EID<15:8>          |        |        |        |        |        |                            | EID<                       | 7:0>     | 1        | 1     |        | XXXX      |        |        |               |

| C1RXF2SID  | 0448          |        | SID<10:3>          |        |        |        |        |        | SID<2:0>                   |                            | —        | EXIDE    | —     | EID<   | 17:16>    | XXXX   |        |               |

| C1RXF2EID  | 044A          |        |                    |        | EID<   | 15:8>  |        |        |                            | EID<7:0>                   |          |          |       |        |           |        | XXXX   |               |

| C1RXF3SID  | 044C          |        |                    |        |        | 10:3>  |        |        |                            |                            | SID<2:0> |          | —     | EXIDE  | —         | EID<   | 17:16> | XXXX          |

| C1RXF3EID  | 044E          |        |                    |        |        | 15:8>  |        |        |                            | EID<7:0>                   |          |          |       |        |           |        | XXXX   |               |

| C1RXF4SID  | 0450          |        |                    |        |        | 10:3>  |        |        |                            | SID<2:0> — EXIDE — EID<17  |          |          |       |        | 17:16>    | XXXX   |        |               |

| C1RXF4EID  | 0452          |        |                    |        |        | 15:8>  |        |        |                            |                            |          | EID<7:0> |       |        |           |        |        | XXXX          |

| C1RXF5SID  | 0454          |        |                    |        |        | 10:3>  |        |        |                            | SID<2:0> — EXIDE — EID<17: |          |          |       |        | 17:16>    | XXXX   |        |               |

| C1RXF5EID  | 0456          |        |                    |        |        | 15:8>  |        |        |                            |                            |          |          | EID<  |        |           | 1      |        | XXXX          |

| C1RXF6SID  | 0458          |        |                    |        |        | 10:3>  |        |        |                            |                            | SID<2:0> |          |       | EXIDE  | —         | EID<   | 17:16> | XXXX          |

| C1RXF6EID  | 045A          |        |                    |        |        | 15:8>  |        |        |                            |                            |          |          | EID<  |        |           |        |        | XXXX          |

| C1RXF7SID  | 045C          |        |                    |        |        | 10:3>  |        |        |                            |                            | SID<2:0> |          |       | EXIDE  | —         | EID<   | 17:16> | XXXX          |

| C1RXF7EID  | 045E          |        |                    |        |        | 15:8>  |        |        |                            |                            |          |          | EID<  |        |           |        |        | XXXX          |

| C1RXF8SID  | 0460          |        | SID<10:3>          |        |        |        |        |        |                            | SID<2:0>                   |          | -        | EXIDE | —      | EID<      | 17:16> | XXXX   |               |

| C1RXF8EID  | 0462          |        |                    |        |        | 15:8>  |        |        |                            |                            | 010 40-0 |          | EID<  | -      |           |        | 17.10  | XXXX          |

| C1RXF9SID  | 0464          |        |                    |        |        | 10:3>  |        |        |                            |                            | SID<2:0> |          |       | EXIDE  | —         | EID<   | 17:16> | XXXX          |

| C1RXF9EID  | 0466          |        |                    |        |        | 15:8>  |        |        |                            |                            | 010 40-0 |          | EID<  |        |           |        | 17.10  | XXXX          |

| C1RXF10SID | 0468          |        |                    |        |        | 10:3>  |        |        |                            |                            | SID<2:0> |          |       | EXIDE  | —         | EID<   | 17:16> | xxxx<br>xxxx  |

| C1RXF10EID | 046A          |        |                    |        |        | 15:8>  |        |        |                            |                            |          |          | EID<  | 7:0>   |           |        |        |               |

#### TABLE 4-18: ECAN1 REGISTER MAP WHEN C1CTRL1.WIN = 1 (FOR PIC24HJ128GP502/504 AND PIC24HJ64GP502/504)

DS70293G-page 40

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

PIC24HJ32GP302/304, PIC24HJ64GPX02/X04 AND PIC24HJ128GPX02/X04

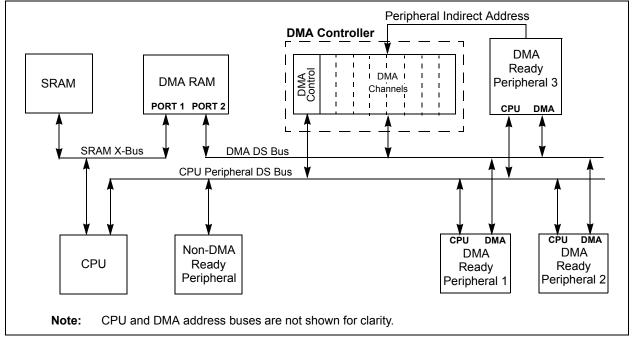

The DMA controller features eight identical data transfer channels.

Each channel has its own set of control and status registers. Each DMA channel can be configured to copy data either from buffers stored in dual port DMA RAM to peripheral SFRs, or from peripheral SFRs to buffers in DMA RAM.

The DMA controller supports the following features:

- Eight DMA channels

- Register Indirect with Post-increment Addressing mode

- Register Indirect without Post-increment Addressing mode

- Peripheral Indirect Addressing mode (peripheral generates destination address)

- CPU interrupt after half or full block transfer complete

- Byte or word transfers

- · Fixed priority channel arbitration

- Manual (software) or Automatic (peripheral DMA requests) transfer initiation

- One-Shot or Auto-Repeat block transfer modes

- Ping-Pong mode (automatic switch between two DPSRAM start addresses after each block transfer complete)

- DMA request for each channel can be selected from any supported interrupt source

- · Debug support features

For each DMA channel, a DMA interrupt request is generated when a block transfer is complete. Alternatively, an interrupt can be generated when half of the block has been filled.

#### FIGURE 8-1: TOP LEVEL SYSTEM ARCHITECTURE USING A DEDICATED TRANSACTION BUS

# 8.3 DMA Control Registers

| <b>D 2 1 1</b>     | <b>D</b> *** * | <b>D</b> # • * •                                                                                  | <b>D</b> # • * * | <b>D</b> #14.4   |                  |                   |          |  |  |  |  |

|--------------------|----------------|---------------------------------------------------------------------------------------------------|------------------|------------------|------------------|-------------------|----------|--|--|--|--|

| R/W-0              | R/W-0          | R/W-0                                                                                             | R/W-0            | R/W-0            | U-0              | U-0               | U-0      |  |  |  |  |

| CHEN               | SIZE           | DIR                                                                                               | HALF             | NULLW            |                  | —                 |          |  |  |  |  |

| bit 15             |                |                                                                                                   |                  |                  |                  |                   | bit 8    |  |  |  |  |

|                    |                |                                                                                                   |                  |                  |                  |                   |          |  |  |  |  |

| U-0                | U-0            | R/W-0                                                                                             | R/W-0            | U-0              | U-0              | R/W-0             | R/W-0    |  |  |  |  |

|                    | —              | AMOD                                                                                              | E<1:0>           |                  |                  | MODE              | <1:0>    |  |  |  |  |

| bit 7              |                |                                                                                                   |                  |                  |                  |                   | bit 0    |  |  |  |  |

|                    |                |                                                                                                   |                  |                  |                  |                   |          |  |  |  |  |

| Legend:            |                |                                                                                                   |                  |                  |                  |                   |          |  |  |  |  |

| R = Readable       | e bit          | W = Writable                                                                                      | bit              | U = Unimple      | mented bit, read | d as '0'          |          |  |  |  |  |

| -n = Value at      | POR            | '1' = Bit is set                                                                                  |                  | '0' = Bit is cle | eared            | x = Bit is unkno  | own      |  |  |  |  |

|                    |                |                                                                                                   |                  |                  |                  |                   |          |  |  |  |  |

| bit 15             | CHEN: Char     | nel Enable bit                                                                                    |                  |                  |                  |                   |          |  |  |  |  |

|                    | 1 = Channel    | enabled                                                                                           |                  |                  |                  |                   |          |  |  |  |  |

|                    | 0 = Channel    | disabled                                                                                          |                  |                  |                  |                   |          |  |  |  |  |

| bit 14             | SIZE: Data T   | ransfer Size bit                                                                                  |                  |                  |                  |                   |          |  |  |  |  |

|                    | 1 = Byte       |                                                                                                   |                  |                  |                  |                   |          |  |  |  |  |

|                    |                | <ul> <li>0 = Word</li> <li>DIR: Transfer Direction bit (source/destination bus select)</li> </ul> |                  |                  |                  |                   |          |  |  |  |  |

| bit 13             |                |                                                                                                   |                  |                  | -                |                   |          |  |  |  |  |

|                    |                | m DMA RAM ao<br>m peripheral ad                                                                   |                  |                  |                  |                   |          |  |  |  |  |

| bit 12             |                | Block Transfer                                                                                    |                  |                  |                  |                   |          |  |  |  |  |

| 51172              |                | lock transfer co                                                                                  | •                | •                |                  | een moved         |          |  |  |  |  |

|                    |                | lock transfer co                                                                                  |                  |                  |                  |                   |          |  |  |  |  |

| bit 11             |                | I Data Periphera                                                                                  |                  |                  |                  |                   |          |  |  |  |  |

|                    | 1 = Null data  | write to periphe                                                                                  | eral in addition | n to DMA RAM     | write (DIR bit r | nust also be clea | ar)      |  |  |  |  |

|                    | 0 = Normal c   | peration                                                                                          |                  |                  |                  |                   |          |  |  |  |  |

| bit 10-6           | Unimplemer     | nted: Read as '                                                                                   | 0'               |                  |                  |                   |          |  |  |  |  |

| bit 5-4            | AMODE<1:0      | >: DMA Chann                                                                                      | el Operating I   | Mode Select bi   | ts               |                   |          |  |  |  |  |

|                    |                | ed (acts as Peri                                                                                  |                  |                  | node)            |                   |          |  |  |  |  |

|                    |                | eral Indirect Add                                                                                 |                  |                  |                  |                   |          |  |  |  |  |

|                    |                | r Indirect withou<br>r Indirect with F                                                            |                  |                  |                  |                   |          |  |  |  |  |

| bit 3-2            | 0              | nted: Read as '                                                                                   |                  | it mode          |                  |                   |          |  |  |  |  |

| bit 0 2<br>bit 1-0 |                | : DMA Channel                                                                                     |                  | ode Select hits  |                  |                   |          |  |  |  |  |

| bit i o            |                |                                                                                                   |                  |                  |                  | each DMA RAM      | buffer)  |  |  |  |  |

|                    |                | ious, Ping-Pong                                                                                   |                  |                  |                  |                   | building |  |  |  |  |

|                    | 01 = One-Sh    | ot, Ping-Pong r                                                                                   | nodes disable    | ed               |                  |                   |          |  |  |  |  |

|                    | 00 = Continu   | ious, Ping-Pong                                                                                   | modes disat      | bled             |                  |                   |          |  |  |  |  |

|                    |                |                                                                                                   |                  |                  |                  |                   |          |  |  |  |  |

## REGISTER 8-1: DMAxCON: DMA CHANNEL x CONTROL REGISTER

## **10.0 POWER-SAVING FEATURES**

- **Note 1:** This data sheet summarizes the features the PIC24HJ32GP302/304. of PIC24HJ64GPX02/X04 and of PIC24HJ128GPX02/X04 families devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet. refer to Section 9. "Watchdog Timer and Power-Saving Modes" (DS70196) of the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The PIC24HJ32GP302/304, PIC24HJ64GPX02/X04 and PIC24HJ128GPX02/X04 devices provide the ability to manage power consumption by selectively managing clocking to the CPU and the peripherals. In general, a lower clock frequency and a reduction in the number of circuits being clocked constitutes lower consumed power. PIC24HJ32GP302/304, PIC24HJ64GPX02/X04 and PIC24HJ128GPX02/X04 devices can manage power consumption in four ways:

- Clock frequency

- Instruction-based Sleep and Idle modes

- Software-controlled Doze mode

- Selective peripheral control in software

Combinations of these methods can be used to selectively tailor an application's power consumption while still maintaining critical application features, such as timing-sensitive communications.

### 10.1 Clock Frequency and Clock Switching

PIC24HJ32GP302/304, PIC24HJ64GPX02/X04 and PIC24HJ128GPX02/X04 devices allow a wide range of clock frequencies to be selected under application control. If the system clock configuration is not locked, users can choose low-power or high-precision oscillators by simply changing the NOSC bits (OSCCON<10:8>). The process of changing a system clock during operation, as well as limitations to the process, are discussed in more detail in Section 9.0 "Oscillator Configuration".

#### 10.2 Instruction-Based Power-Saving Modes

PIC24HJ32GP302/304, PIC24HJ64GPX02/X04 and PIC24HJ128GPX02/X04 devices have two special power-saving modes that are entered through the execution of a special PWRSAV instruction. Sleep mode stops clock operation and halts all code execution. Idle mode halts the CPU and code execution, but allows peripheral modules to continue operation. The assembler syntax of the PWRSAV instruction is shown in Example 10-1.

Note: SLEEP\_MODE and IDLE\_MODE are constants defined in the assembler include file for the selected device.

Sleep and Idle modes can be exited as a result of an enabled interrupt, WDT time-out or a device Reset. When the device exits these modes, it is said to wake up.

#### 10.2.1 SLEEP MODE

The following occur in Sleep mode:

- The system clock source is shut down. If an on-chip oscillator is used, it is turned off.

- The device current consumption is reduced to a minimum, provided that no I/O pin is sourcing current.

- The Fail-Safe Clock Monitor does not operate, since the system clock source is disabled.

- The LPRC clock continues to run in Sleep mode if the WDT is enabled.

- The WDT, if enabled, is automatically cleared prior to entering Sleep mode.

- Some device features or peripherals can continue to operate. This includes items such as the input change notification on the I/O ports, or peripherals that use an external clock input.

- Any peripheral that requires the system clock source for its operation is disabled.

The device wakes up from Sleep mode on any of the these events:

- · Any interrupt source that is individually enabled

- Any form of device Reset

- A WDT time-out

On wake-up from Sleep mode, the processor restarts with the same clock source that was active when Sleep mode was entered.

#### EXAMPLE 10-1: PWRSAV INSTRUCTION SYNTAX

PWRSAV #SLEEP\_MODE ; Put the device into SLEEP mode

PWRSAV #IDLE\_MODE ; Put the device into IDLE mode

#### 11.2 Open-Drain Configuration

In addition to the PORT, LAT and TRIS registers for data control, some port pins can also be individually configured for either digital or open-drain output. This is controlled by the Open-Drain Control register, ODCx, associated with each port. Setting any of the bits configures the corresponding pin to act as an open-drain output.

The open-drain feature allows the generation of outputs higher than VDD (e.g., 5V) on any desired 5V tolerant pins by using external pull-up resistors. The maximum open-drain voltage allowed is the same as the maximum VIH specification.

See **"Pin Diagrams"** for the available pins and their functionality.

## 11.3 Configuring Analog Port Pins

The AD1PCFGL and TRIS registers control the operation of the analog-to-digital (A/D) port pins. The port pins that are to function as analog inputs must have their corresponding TRIS bit set (input). If the TRIS bit is cleared (output), the digital output level (VOH or VOL) is converted.

The AD1PCFGL register has a default value of 0x0000; therefore, all pins that share ANx functions are analog (not digital) by default.

When the PORT register is read, all pins configured as analog input channels are read as cleared (a low level).

Pins configured as digital inputs do not convert an analog input. Analog levels on any pin defined as a digital input (including the ANx pins) can cause the input buffer to consume current that exceeds the device specifications.

#### 11.4 I/O Port Write/Read Timing

One instruction cycle is required between a port direction change or port write operation and a read operation of the same port. Typically this instruction would be an NOP, as shown in Example 11-1.

## 11.5 Input Change Notification

The input change notification function of the I/O ports allows the PIC24HJ32GP302/304, PIC24HJ64GPX02/ X04 and PIC24HJ128GPX02/X04 devices to generate interrupt requests to the processor in response to a change-of-state on selected input pins. This feature can detect input change-of-states even in Sleep mode, when the clocks are disabled. Depending on the device pin count, up to 21 external signals (CNx pin) can be selected (enabled) for generating an interrupt request on a change-of-state.

Four control registers are associated with the CN module. The CNEN1 and CNEN2 registers contain the interrupt enable control bits for each of the CN input pins. Setting any of these bits enables a CN interrupt for the corresponding pins.

Each CN pin also has a weak pull-up connected to it. The pull-ups act as a current source connected to the pin, and eliminate the need for external resistors when push-button or keypad devices are connected. The pull-ups are enabled separately using the CNPU1 and CNPU2 registers, which contain the control bits for each of the CN pins. Setting any of the control bits enables the weak pull-ups for the corresponding pins.

Note: Pull-ups on change notification pins should always be disabled when the port pin is configured as a digital output.

| MOV  | 0xFF00, W0 | ; Configure PORTB<15:8> as inputs |

|------|------------|-----------------------------------|

| MOV  | WO, TRISBB | ; and PORTB<7:0> as outputs       |

| NOP  |            | ; Delay 1 cycle                   |

| btss | PORTB, #13 | ; Next Instruction                |

|      |            |                                   |

#### EXAMPLE 11-1: PORT WRITE/READ EXAMPLE

### REGISTER 11-7: RPINR11: PERIPHERAL PIN SELECT INPUT REGISTER 11

| U-0                                                                  | U-0                                                               | U-0 | U-0        | U-0   | U-0   | U-0   | U-0   |

|----------------------------------------------------------------------|-------------------------------------------------------------------|-----|------------|-------|-------|-------|-------|

| _                                                                    |                                                                   | -   | _          | —     | —     | —     | —     |

| bit 15                                                               |                                                                   |     |            |       |       |       | bit 8 |

|                                                                      |                                                                   |     |            |       |       |       |       |

| U-0                                                                  | U-0                                                               | U-0 | R/W-1      | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

| _                                                                    | _                                                                 | _   | OCFAR<4:0> |       |       |       |       |

| bit 7                                                                |                                                                   |     |            |       |       |       | bit 0 |

|                                                                      |                                                                   |     |            |       |       |       |       |

| Legend:                                                              |                                                                   |     |            |       |       |       |       |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |                                                                   |     |            |       |       |       |       |

| -n = Value at P                                                      | e at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknowr |     |            | nown  |       |       |       |

| •                                                                    |                                                                   |     |            |       |       |       |       |

bit 15-5 Unimplemented: Read as '0'

| bit 4-0             | <b>OCFAR&lt;4:0&gt;:</b> Assign Output Compare A (OCFA) to the corresponding RPn pin |

|---------------------|--------------------------------------------------------------------------------------|

| DIL <del>4</del> -0 | OCIAN 4.0/. Assign Output Compare A (OCIA) to the corresponding IV in pin            |

11111 = Input tied to Vss 11001 = Input tied to RP25

.

• 00001 = Input tied to RP1 00000 = Input tied to RP0

| REGISTER     |                       | R19: PERIPHE                       | _     |                      |                 | -         |                    |  |  |

|--------------|-----------------------|------------------------------------|-------|----------------------|-----------------|-----------|--------------------|--|--|

| U-0          | U-0                   | U-0                                | R/W-1 | R/W-1                | R/W-1           | R/W-1     | R/W-1              |  |  |

| —            | —                     | —                                  |       |                      | U2CTSR<4:       | )>        |                    |  |  |

| bit 15       |                       |                                    |       |                      |                 |           | bit 8              |  |  |

| U-0          | U-0                   | U-0                                | R/W-1 | R/W-1                | R/W-1           | R/W-1     | R/W-1              |  |  |

| _            | _                     | _                                  |       |                      | U2RXR<4:0       | >         |                    |  |  |

| bit 7        |                       |                                    |       |                      |                 |           | bit (              |  |  |

| Legend:      |                       |                                    |       |                      |                 |           |                    |  |  |

| R = Readab   | le bit                | W = Writable b                     | bit   | U = Unimple          | mented bit, rea | ad as '0' |                    |  |  |

| -n = Value a | t POR                 | '1' = Bit is set                   |       | '0' = Bit is cleared |                 |           | x = Bit is unknown |  |  |

|              | •<br>•<br>00001 = Inp | ut tied to RP25                    |       |                      |                 |           |                    |  |  |

| bit 7-5      | •                     | ut tied to RP0<br>nted: Read as '0 | ,     |                      |                 |           |                    |  |  |

| bit 4-0      | •                     | >: Assign UART2                    |       | 2RX) to the co       | rresponding R   | Pn nin    |                    |  |  |

| 511 4-0      | 11111 <b>= Inp</b>    | ut tied to Vss<br>ut tied to RP25  |       |                      |                 | i ii piii |                    |  |  |

|              | •                     |                                    |       |                      |                 |           |                    |  |  |

|              | •                     |                                    |       |                      |                 |           |                    |  |  |

|              | •                     |                                    |       |                      |                 |           |                    |  |  |

|              |                       | ut tied to RP1                     |       |                      |                 |           |                    |  |  |

00000 = Input tied to RP0

### REGISTER 11-19: RPOR4: PERIPHERAL PIN SELECT OUTPUT REGISTERS 4

| U-0                                | U-0 | R/W-0 | R/W-0                                        | R/W-0                                                                                                                                                    | R/W-0                                                                                                                                                                                                           | R/W-0                                                                                                                                                       |  |  |  |

|------------------------------------|-----|-------|----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| _                                  | —   |       |                                              | RP9R<4:0>                                                                                                                                                | •                                                                                                                                                                                                               |                                                                                                                                                             |  |  |  |

|                                    |     |       |                                              |                                                                                                                                                          |                                                                                                                                                                                                                 | bit 8                                                                                                                                                       |  |  |  |

|                                    |     |       |                                              |                                                                                                                                                          |                                                                                                                                                                                                                 |                                                                                                                                                             |  |  |  |

| U-0                                | U-0 | R/W-0 | R/W-0                                        | R/W-0                                                                                                                                                    | R/W-0                                                                                                                                                                                                           | R/W-0                                                                                                                                                       |  |  |  |

| —                                  | —   |       |                                              | RP8R<4:0>                                                                                                                                                | •                                                                                                                                                                                                               |                                                                                                                                                             |  |  |  |

|                                    |     |       |                                              |                                                                                                                                                          |                                                                                                                                                                                                                 | bit 0                                                                                                                                                       |  |  |  |

|                                    |     |       |                                              |                                                                                                                                                          |                                                                                                                                                                                                                 |                                                                                                                                                             |  |  |  |

|                                    |     |       |                                              |                                                                                                                                                          |                                                                                                                                                                                                                 |                                                                                                                                                             |  |  |  |

| R = Readable bit W = Writable bit  |     |       | U = Unimplemented bit, read as '0'           |                                                                                                                                                          |                                                                                                                                                                                                                 |                                                                                                                                                             |  |  |  |

| -n = Value at POR '1' = Bit is set |     |       | '0' = Bit is cleared x = Bit is unknown      |                                                                                                                                                          |                                                                                                                                                                                                                 |                                                                                                                                                             |  |  |  |

|                                    |     |       | <br>U-0 U-0 R/W-0<br><br>it W = Writable bit | —         —         —           U-0         U-0         R/W-0           —         —         —           it         W = Writable bit         U = Unimpler | —         —         RP9R<4:0>           U-0         U-0         R/W-0         R/W-0           —         —         —         RP8R<4:0>           it         W = Writable bit         U = Unimplemented bit, real | —         —         RP9R<4:0>           U-0         U-0         R/W-0         R/W-0         R/W-0           —         —         RP8R<4:0>         RP8R<4:0> |  |  |  |

bit 15-13 Unimplemented: Read as '0'

bit 12-8 **RP9R<4:0>:** Peripheral Output Function is Assigned to RP9 Output Pin bits (see Table 11-2 for peripheral function numbers)

bit 7-5 Unimplemented: Read as '0'

bit 4-0 **RP8R<4:0>:** Peripheral Output Function is Assigned to RP8 Output Pin bits (see Table 11-2 for peripheral function numbers)

#### REGISTER 11-20: RPOR5: PERIPHERAL PIN SELECT OUTPUT REGISTERS 5

| U-0    | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0      | R/W-0 | R/W-0 |

|--------|-----|-----|-------|-------|------------|-------|-------|

| —      | —   | —   |       |       | RP11R<4:0> |       |       |

| bit 15 |     |     |       |       |            |       | bit 8 |

| U-0   | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0      | R/W-0 | R/W-0 |

|-------|-----|-----|-------|-------|------------|-------|-------|

| —     | —   | —   |       |       | RP10R<4:0> |       |       |

| bit 7 |     |     |       |       |            |       | bit 0 |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 15-13 Unimplemented: Read as '0'

bit 12-8 **RP11R<4:0>:** Peripheral Output Function is Assigned to RP11 Output Pin bits (see Table 11-2 for peripheral function numbers)

bit 7-5 Unimplemented: Read as '0'

bit 4-0 **RP10R<4:0>:** Peripheral Output Function is Assigned to RP10 Output Pin bits (see Table 11-2 for peripheral function numbers)

# 12.2 Timer1 Control Register

## REGISTER 12-1: T1CON: TIMER1 CONTROL REGISTER

| R/W-0  | U-0 | R/W-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-------|-----|-----|-----|-----|-------|

| TON    | —   | TSIDL | —   | —   | —   | —   | —     |

| bit 15 |     |       |     |     |     |     | bit 8 |

|        |     |       |     |     |     |     |       |

| U-0   | R/W-0 | R/W-0 | R/W-0  | U-0 | R/W-0 | R/W-0 | U-0   |

|-------|-------|-------|--------|-----|-------|-------|-------|

| _     | TGATE | TCKPS | S<1:0> |     | TSYNC | TCS   | —     |

| bit 7 |       |       |        |     |       |       | bit 0 |

| Legend:           |                 |                                                         |                            |                    |

|-------------------|-----------------|---------------------------------------------------------|----------------------------|--------------------|

| R = Readal        | ble bit         | W = Writable bit                                        | U = Unimplemented bit,     | read as '0'        |

| -n = Value at POR |                 | '1' = Bit is set                                        | '0' = Bit is cleared       | x = Bit is unknown |

|                   |                 |                                                         |                            |                    |

| bit 15            | TON: Time       |                                                         |                            |                    |

|                   |                 | 16-bit Timer1                                           |                            |                    |

| bit 11            | •               | 16-bit Timer1                                           |                            |                    |

| bit 14            | -               | nented: Read as '0'                                     |                            |                    |

| bit 13            |                 | op in Idle Mode bit                                     | on dovice entere Idle mode |                    |

|                   |                 | ue module operation in Idle                             | en device enters Idle mode |                    |

| bit 12-7          |                 | nented: Read as '0'                                     |                            |                    |

| bit 6             | -               | imer1 Gated Time Accumul                                | ation Enable bit           |                    |

|                   | When TCS        | <b>S</b> = 1:                                           |                            |                    |

|                   | This bit is     |                                                         |                            |                    |

|                   | When TCS        |                                                         |                            |                    |

|                   |                 | time accumulation enabled<br>time accumulation disabled |                            |                    |

| bit 5-4           |                 |                                                         |                            |                    |

| DIL 3-4           | 11 = 1:25       | :0>: Timer1 Input Clock Pre                             |                            |                    |

|                   | 10 = 1:64       |                                                         |                            |                    |

|                   | 01 <b>= 1:8</b> |                                                         |                            |                    |

|                   | 00 = 1:1        |                                                         |                            |                    |

| bit 3             | -               | nented: Read as '0'                                     |                            |                    |

| bit 2             |                 | ïmer1 External Clock Input                              | Synchronization Select bit |                    |

|                   | <u>When TCS</u> | <u>S = 1:</u><br>ronize external clock input            |                            |                    |

|                   | •               | t synchronize external clock                            | cinput                     |                    |

|                   | When TCS        | •                                                       |                            |                    |

|                   | This bit is     |                                                         |                            |                    |

| bit 1             | TCS: Time       | er1 Clock Source Select bit                             |                            |                    |

|                   |                 | al clock from pin T1CK (on al clock (FcY)               | the rising edge)           |                    |

| bit 0             | Unimplem        | nented: Read as '0'                                     |                            |                    |

|                   | -               |                                                         |                            |                    |

NOTES:

# REGISTER 17-2: I2CxSTAT: I2Cx STATUS REGISTER (CONTINUED)

| bit 3 | S: Start bit                                                                                                                                                                                                                                 |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul> <li>1 = Indicates that a Start (or Repeated Start) bit has been detected last</li> <li>0 = Start bit was not detected last</li> <li>Hardware set or clear when Start, Repeated Start or Stop detected.</li> </ul>                       |

| bit 2 | <b>R_W:</b> Read/Write Information bit (when operating as I <sup>2</sup> C slave)                                                                                                                                                            |

|       | <ul> <li>1 = Read – indicates data transfer is output from slave</li> <li>0 = Write – indicates data transfer is input to slave</li> <li>Hardware set or clear after reception of I<sup>2</sup>C device address byte.</li> </ul>             |

| bit 1 | <b>RBF:</b> Receive Buffer Full Status bit<br>1 = Receive complete, I2CxRCV is full<br>0 = Receive not complete, I2CxRCV is empty<br>Hardware set when I2CxRCV is written with received byte. Hardware clear when software<br>reads I2CxRCV. |

| bit 0 | <b>TBF:</b> Transmit Buffer Full Status bit<br>1 = Transmit in progress, I2CxTRN is full<br>0 = Transmit complete, I2CxTRN is empty<br>Hardware set when software writes I2CxTRN. Hardware clear at completion of data transmission.         |

## 25.0 SPECIAL FEATURES

- Note 1: This data sheet summarizes the features of the PIC24HJ32GP302/304, PIC24HJ64GPX02/X04 and PIC24HJ128GPX02/X04 families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the *"dsPIC33F/PIC24H Family Reference Manual"*. Please see the Microchip web site (www.microchip.com) for the latest dsPIC33F/PIC24H Family Reference Manual sections.

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The PIC24HJ32GP302/304, PIC24HJ64GPX02/X04 and PIC24HJ128GPX02/X04 devices include the following features that are intended to maximize application flexibility and reliability, and minimize cost through elimination of external components:

- · Flexible configuration

- Watchdog Timer (WDT)

- Code Protection and CodeGuard<sup>™</sup> Security

- · JTAG Boundary Scan Interface

- In-Circuit Serial Programming™ (ICSP™)

- In-Circuit Emulation

## 25.1 Configuration Bits

The PIC24HJ32GP302/304, PIC24HJ64GPX02/X04 and PIC24HJ128GPX02/X04 devices provide nonvolatile memory implementation for device configuration bits. Refer to **Section 25. "Device Configuration"** (DS70194), in the *"dsPIC33F/PIC24H Family Reference Manual"* for more information on this implementation.

The Configuration bits can be programmed (read as '0'), or left unprogrammed (read as '1'), to select various device configurations. These bits are mapped starting at program memory location 0xF80000.

The individual Configuration bit descriptions for the Configuration registers are shown in Table 25-1.

Note that address 0xF80000 is beyond the user program memory space. It belongs to the configuration memory space (0x800000-0xFFFFFF), which can only be accessed using table reads and table writes.

The Device Configuration register map is shown in Table 25-1.

| Address  | Name               | Bit 7                                     | Bit 6               | Bit 5   | Bit 4        | Bit 3    | Bit 2               | Bit 1 | Bit 0   |

|----------|--------------------|-------------------------------------------|---------------------|---------|--------------|----------|---------------------|-------|---------|

| 0xF80000 | FBS                | RBS<                                      | :1:0>               |         | _            |          | BSS<2:0> BW         |       | BWRP    |

| 0xF80002 | FSS <sup>(1)</sup> | RSS<                                      | :1:0>               | _       | _            |          | SSS<2:0>            |       | SWRP    |

| 0xF80004 | FGS                | _                                         | _                   | _       |              | _        | — GSS<1:0> G\       |       | GWRP    |

| 0xF80006 | FOSCSEL            | IESO                                      | _                   | _       | _            | _        | FNOSC<2:0>          |       |         |

| 0xF80008 | FOSC               | FCKSN                                     | 1<1:0>              | IOL1WAY | _            | _        | OSCIOFNC POSCMD<1:0 |       | 1D<1:0> |

| 0xF8000A | FWDT               | FWDTEN                                    | WINDIS              | _       | WDTPRE       |          | WDTPOST<3:0>        |       |         |

| 0xF8000C | FPOR               | Reserved <sup>(2)</sup> ALTI2C — FPWRT<2: |                     |         | /RT<2:0>     |          |                     |       |         |

| 0xF8000E | FICD               | Reserv                                    | /ed <sup>(3)</sup>  | JTAGEN  | —            | _        | —                   | ICS<  | <1:0>   |

| 0xF80010 | FUID0              |                                           |                     |         | User Unit ID | ) Byte 0 |                     |       |         |

| 0xF80012 | FUID1              |                                           | User Unit ID Byte 1 |         |              |          |                     |       |         |

| 0xF80014 | FUID2              |                                           | User Unit ID Byte 2 |         |              |          |                     |       |         |

| 0xF80016 | FUID3              |                                           | User Unit ID Byte 3 |         |              |          |                     |       |         |

#### TABLE 25-1: DEVICE CONFIGURATION REGISTER MAP

**Legend:** — = unimplemented bit, read as '0'.

Note 1: This Configuration register is not available and reads as 0xFF on PIC24HJ32GP302/304 devices.

2: These bits are reserved and always read as '1'.

3: These bits are reserved for use by development tools and must be programmed as '1'.

| TABLE 25-2:             | PIC24H CONFIGURATION BITS DESCRIPTION |             |                                                                                                                                                                                                                 |  |  |  |

|-------------------------|---------------------------------------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Bit Field               | Register                              | RTSP Effect | Description                                                                                                                                                                                                     |  |  |  |

| BWRP                    | FBS                                   | Immediate   | Boot Segment Program Flash Write Protection<br>1 = Boot segment can be written<br>0 = Boot segment is write-protected                                                                                           |  |  |  |

| BSS<2:0>                | FBS                                   | Immediate   | Boot Segment Program Flash Code Protection Size<br>X11 = No Boot program Flash segment                                                                                                                          |  |  |  |

|                         |                                       |             | Boot space is 1K Instruction Words (except interrupt vectors)<br>110 = Standard security; boot program Flash segment ends<br>at 0x0007FE<br>010 = High security; boot program Flash segment ends at<br>0x0007FE |  |  |  |

|                         |                                       |             | Boot space is 4K Instruction Words (except interrupt vectors)<br>101 = Standard security; boot program Flash segment, ends<br>at 0x001FFE                                                                       |  |  |  |

|                         |                                       |             | 001 = High security; boot program Flash segment ends at<br>0x001FFE                                                                                                                                             |  |  |  |

|                         |                                       |             | Boot space is 8K Instruction Words (except interrupt vectors)<br>100 = Standard security; boot program Flash segment ends<br>at 0x003FFE                                                                        |  |  |  |

|                         |                                       |             | 000 = High security; boot program Flash segment ends at<br>0x003FFE                                                                                                                                             |  |  |  |

| RBS<1:0> <sup>(1)</sup> | FBS                                   | Immediate   | Boot Segment RAM Code Protection Size<br>11 = No Boot RAM defined<br>10 = Boot RAM is 128 bytes<br>01 = Boot RAM is 256 bytes<br>00 = Boot RAM is 1024 bytes                                                    |  |  |  |

| SWRP <sup>(1)</sup>     | FSS <sup>(1)</sup>                    | Immediate   | Secure Segment Program Flash Write-Protect bit<br>1 = Secure Segment can bet written<br>0 = Secure Segment is write-protected                                                                                   |  |  |  |

| SSS<2:0> <sup>(1)</sup> | FSS <sup>(1)</sup>                    | Immediate   | Secure Segment Program Flash Code Protection Size<br>(Secure segment is not implemented on 32K devices)<br>X11 = No Secure program flash segment                                                                |  |  |  |

|                         |                                       |             | Secure space is 4K IW less BS<br>110 = Standard security; secure program flash segment starts<br>at End of BS, ends at 0x001FFE                                                                                 |  |  |  |

|                         |                                       |             | 010 = High security; secure program flash segment starts at<br>End of BS, ends at 0x001FFE                                                                                                                      |  |  |  |

|                         |                                       |             | Secure space is 8K IW less BS<br>101 = Standard security; secure program flash segment starts<br>at End of BS, ends at 0x003FFE<br>001 = High security; secure program flash segment starts at                  |  |  |  |

|                         |                                       |             | End of BS, ends at 0x003FFE<br>Secure space is 16K IW less BS<br>100 = Standard security; secure program flash segment starts                                                                                   |  |  |  |

|                         |                                       |             | at End of BS, ends at 007FFEh<br>000 = High security; secure program flash segment starts at<br>End of BS, ends at 0x007FFE                                                                                     |  |  |  |

## TABLE 25-2: PIC24H CONFIGURATION BITS DESCRIPTION

**Note 1:** This Configuration register is not available on PIC24HJ32GP302/304 devices.

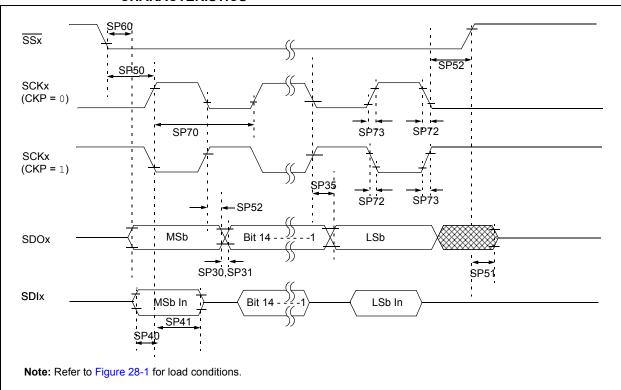

FIGURE 28-14: SPIx SLAVE MODE (FULL-DUPLEX, CKE = 1, CKP = 1, SMP = 0) TIMING CHARACTERISTICS

| TABLE 28-35: | SPIX SLAVE MODE (FULL-DUPLEX, CKE = 0, CKP = 0, SMP = 0) TIMING |

|--------------|-----------------------------------------------------------------|

|              | REQUIREMENTS                                                    |

| АС СНА       | AC CHARACTERISTICS    |                                                            |              | erating<br>rwise st<br>nperatur | <b>ated)</b><br>e -40° | C ≤TA ≤+ | V to 3.6V<br>85°C for Industrial<br>125°C for Extended |

|--------------|-----------------------|------------------------------------------------------------|--------------|---------------------------------|------------------------|----------|--------------------------------------------------------|

| Param<br>No. | Symbol                | Characteristic <sup>(1)</sup>                              | Min          | Тур <sup>(2)</sup>              | Мах                    | Units    | Conditions                                             |

| SP70         | TscP                  | Maximum SCK Input Frequency                                |              | _                               | 11                     | MHz      | See Note 3                                             |

| SP72         | TscF                  | SCKx Input Fall Time                                       | —            | _                               | _                      | ns       | See parameter DO32 and Note 4                          |

| SP73         | TscR                  | SCKx Input Rise Time                                       | —            |                                 |                        | ns       | See parameter DO31 and Note 4                          |

| SP30         | TdoF                  | SDOx Data Output Fall Time                                 | —            | _                               |                        | ns       | See parameter DO32 and Note 4                          |

| SP31         | TdoR                  | SDOx Data Output Rise Time                                 | —            |                                 |                        | ns       | See parameter DO31 and Note 4                          |

| SP35         | TscH2doV,<br>TscL2doV | SDOx Data Output Valid after<br>SCKx Edge                  | —            | 6                               | 20                     | ns       | —                                                      |

| SP36         | TdoV2scH,<br>TdoV2scL | SDOx Data Output Setup to<br>First SCKx Edge               | 30           |                                 |                        | ns       | —                                                      |

| SP40         | TdiV2scH,<br>TdiV2scL | Setup Time of SDIx Data Input to SCKx Edge                 | 30           |                                 |                        | ns       | —                                                      |

| SP41         | TscH2diL,<br>TscL2diL | Hold Time of SDIx Data Input to SCKx Edge                  | 30           | _                               | _                      | ns       | —                                                      |

| SP50         | TssL2scH,<br>TssL2scL | $\overline{SSx} \downarrow to SCKx \uparrow or SCKx Input$ | 120          | _                               | _                      | ns       | —                                                      |

| SP51         | TssH2doZ              | SSx                                                        | 10           | _                               | 50                     | ns       | -                                                      |

| SP52         | TscH2ssH<br>TscL2ssH  | SSx after SCKx Edge                                        | 1.5 Tcy + 40 | —                               | _                      | ns       | See Note 4                                             |

**Note 1:** These parameters are characterized, but are not tested in manufacturing.

2: Data in "Typ" column is at 3.3V, 25°C unless otherwise stated.

**3:** The minimum clock period for SCKx is 91 ns. Therefore, the SCK clock generated by the Master must not violate this specification.

4: Assumes 50 pF load on all SPIx pins.

| AC CHA       | ARACTER | ISTICS           |                           | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |      |       |                        |  |

|--------------|---------|------------------|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|------------------------|--|

| Param<br>No. | Symbol  | Charac           | teristic                  | Min <sup>(1)</sup>                                                                                                                                                                                                                                                                      | Мах  | Units | Conditions             |  |

| IM10         | TLO:SCL | Clock Low Time   | 100 kHz mode              | Tcy/2 (BRG + 1)                                                                                                                                                                                                                                                                         | _    | μs    | _                      |  |

|              |         |                  | 400 kHz mode              | Tcy/2 (BRG + 1)                                                                                                                                                                                                                                                                         | —    | μs    | _                      |  |

|              |         |                  | 1 MHz mode <sup>(2)</sup> | Tcy/2 (BRG + 1)                                                                                                                                                                                                                                                                         | —    | μs    | _                      |  |

| IM11         | THI:SCL | Clock High Time  | 100 kHz mode              | Tcy/2 (BRG + 1)                                                                                                                                                                                                                                                                         | —    | μs    | —                      |  |

|              |         |                  | 400 kHz mode              | Tcy/2 (BRG + 1)                                                                                                                                                                                                                                                                         | —    | μs    | _                      |  |

|              |         |                  | 1 MHz mode <sup>(2)</sup> | Tcy/2 (BRG + 1)                                                                                                                                                                                                                                                                         | —    | μs    | _                      |  |

| IM20         | TF:SCL  | SDAx and SCLx    | 100 kHz mode              |                                                                                                                                                                                                                                                                                         | 300  | ns    | CB is specified to be  |  |

|              |         | Fall Time        | 400 kHz mode              | 20 + 0.1 Св                                                                                                                                                                                                                                                                             | 300  | ns    | from 10 to 400 pF      |  |

|              |         |                  | 1 MHz mode <sup>(2)</sup> | _                                                                                                                                                                                                                                                                                       | 100  | ns    |                        |  |

| IM21         | TR:SCL  | SDAx and SCLx    | 100 kHz mode              | —                                                                                                                                                                                                                                                                                       | 1000 | ns    | CB is specified to be  |  |

|              |         | Rise Time        | 400 kHz mode              | 20 + 0.1 Св                                                                                                                                                                                                                                                                             | 300  | ns    | from 10 to 400 pF      |  |

|              |         |                  | 1 MHz mode <sup>(2)</sup> |                                                                                                                                                                                                                                                                                         | 300  | ns    |                        |  |

| IM25         | TSU:DAT | Data Input       | 100 kHz mode              | 250                                                                                                                                                                                                                                                                                     | _    | ns    | _                      |  |

|              |         | Setup Time       | 400 kHz mode              | 100                                                                                                                                                                                                                                                                                     | _    | ns    |                        |  |

|              |         |                  | 1 MHz mode <sup>(2)</sup> | 40                                                                                                                                                                                                                                                                                      | —    | ns    |                        |  |

| IM26         | THD:DAT | Data Input       | 100 kHz mode              | 0                                                                                                                                                                                                                                                                                       | _    | μs    | _                      |  |

|              |         | Hold Time        | 400 kHz mode              | 0                                                                                                                                                                                                                                                                                       | 0.9  | μs    |                        |  |

|              |         |                  | 1 MHz mode <sup>(2)</sup> | 0.2                                                                                                                                                                                                                                                                                     | _    | μs    |                        |  |

| IM30         | TSU:STA | Start Condition  | 100 kHz mode              | Tcy/2 (BRG + 1)                                                                                                                                                                                                                                                                         | —    | μs    | Only relevant for      |  |

|              |         | Setup Time       | 400 kHz mode              | Tcy/2 (BRG + 1)                                                                                                                                                                                                                                                                         | _    | μs    | Repeated Start         |  |