Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XFI

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Active                                                                        |

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 40 MIPs                                                                       |

| Connectivity               | I <sup>2</sup> C, PMP, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                    |

| Number of I/O              | 21                                                                            |

| Program Memory Size        | 64KB (22K x 24)                                                               |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 8K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                     |

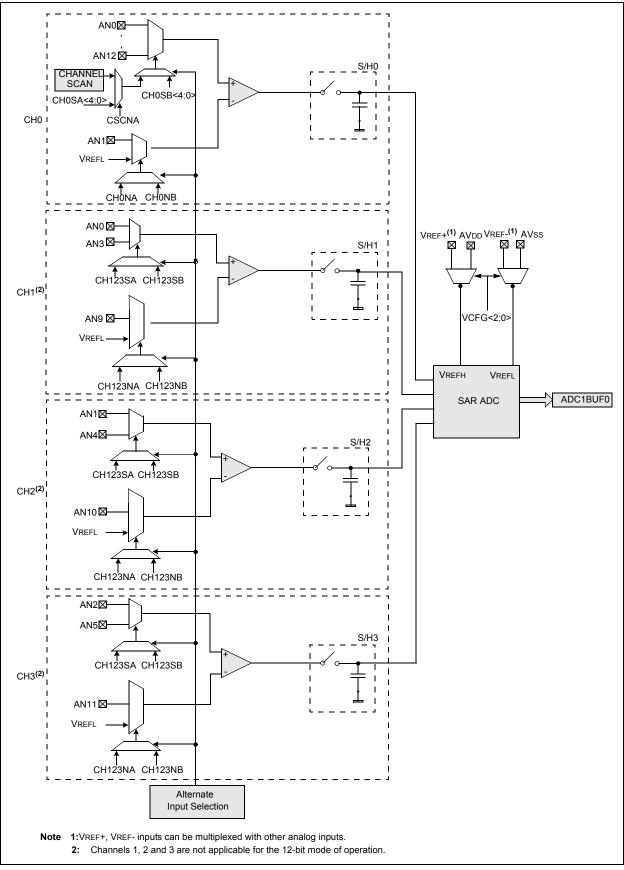

| Data Converters            | A/D 10x10b/12b                                                                |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 28-VQFN Exposed Pad                                                           |

| Supplier Device Package    | 28-QFN-S (6x6)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24hj64gp202-e-mm |

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

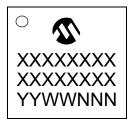

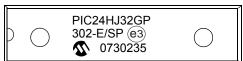

NOTES:

### TABLE 4-7: OUTPUT COMPARE REGISTER MAP

|          |             |        |                           |        |          |            |            |             |             |             |              |       |       |        |       |          |       | -             |

|----------|-------------|--------|---------------------------|--------|----------|------------|------------|-------------|-------------|-------------|--------------|-------|-------|--------|-------|----------|-------|---------------|

| SFR Name | SFR<br>Addr | Bit 15 | Bit 14                    | Bit 13 | Bit 12   | Bit 11     | Bit 10     | Bit 9       | Bit 8       | Bit 7       | Bit 6        | Bit 5 | Bit 4 | Bit 3  | Bit 2 | Bit 1    | Bit 0 | All<br>Resets |

| OC1RS    | 0180        |        |                           |        |          |            |            | Ou          | tput Compar | e 1 Seconda | ary Register |       |       |        |       |          |       | xxxx          |

| OC1R     | 0182        |        | Output Compare 1 Register |        |          |            |            |             | XXXX        |             |              |       |       |        |       |          |       |               |

| OC1CON   | 0184        | _      | _                         | OCSIDL | _        | _          |            | _           | —           | _           | _            | _     | OCFLT | OCTSEL |       | OCM<2:0> |       | 0000          |

| OC2RS    | 0186        |        |                           |        |          |            |            | Ou          | tput Compar | e 2 Seconda | ary Register |       |       |        |       |          |       | XXXX          |

| OC2R     | 0188        |        | Output Compare 2 Register |        |          |            |            | XXXX        |             |             |              |       |       |        |       |          |       |               |

| OC2CON   | 018A        | _      | _                         | OCSIDL | _        | _          |            | _           | —           | _           | _            | _     | OCFLT | OCTSEL |       | OCM<2:0> |       | 0000          |

| OC3RS    | 018C        |        |                           |        |          |            |            | Ou          | tput Compar | e 3 Seconda | ary Register |       |       |        |       |          |       | XXXX          |

| OC3R     | 018E        |        |                           |        |          |            |            |             | Output Co   | ompare 3 Re | gister       |       |       |        |       |          |       | XXXX          |

| OC3CON   | 0190        | _      | _                         | OCSIDL | _        | _          |            | _           | —           | _           | _            | _     | OCFLT | OCTSEL |       | OCM<2:0> |       | 0000          |

| OC4RS    | 0192        |        |                           |        |          |            |            | Ou          | tput Compar | e 4 Seconda | ary Register |       |       |        |       |          |       | XXXX          |

| OC4R     | 0194        |        | Output Compare 4 Register |        |          |            |            |             | XXXX        |             |              |       |       |        |       |          |       |               |

| OC4CON   | 0196        | _      | _                         | OCSIDL | _        | _          | _          | _           | _           | _           | _            | _     | OCFLT | OCTSEL |       | OCM<2:0> |       | 0000          |

| l edend. | v = unk     |        | o on Posot                | = unim | lomontod | road as '0 | ' Posot va | luce are ch | own in hove | docimal     |              |       |       | •      | •     |          |       |               |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-8: I2C1 REGISTER MAP

| SFR Name | SFR<br>Addr | Bit 15  | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9                    | Bit 8 | Bit 7                        | Bit 6 | Bit 5 | Bit 4    | Bit 3    | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|----------|-------------|---------|--------|---------|--------|--------|--------|--------------------------|-------|------------------------------|-------|-------|----------|----------|-------|-------|-------|---------------|

| I2C1RCV  | 0200        | _       | _      | -       | _      | _      | -      | -                        | _     | Receive Register             |       |       |          |          | 0000  |       |       |               |

| I2C1TRN  | 0202        | _       | _      | _       | _      | _      | _      | _                        | _     |                              |       |       | Transmit | Register |       |       |       | OOFF          |

| I2C1BRG  | 0204        | _       | _      | _       | _      | _      | _      | _                        |       | Baud Rate Generator Register |       |       |          | 0000     |       |       |       |               |

| I2C1CON  | 0206        | I2CEN   | _      | I2CSIDL | SCLREL | IPMIEN | A10M   | DISSLW                   | SMEN  | GCEN                         | STREN | ACKDT | ACKEN    | RCEN     | PEN   | RSEN  | SEN   | 1000          |

| I2C1STAT | 0208        | ACKSTAT | TRSTAT | _       | _      | _      | BCL    | GCSTAT                   | ADD10 | IWCOL                        | I2COV | D_A   | Р        | S        | R_W   | RBF   | TBF   | 0000          |

| I2C1ADD  | 020A        | _       | _      | _       | _      | _      | _      | Address Register         |       |                              |       |       | 0000     |          |       |       |       |               |

| I2C1MSK  | 020C        | _       | _      | _       | _      | _      | -      | Address Mask Register 00 |       |                              |       |       |          | 0000     |       |       |       |               |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-9: UART1 REGISTER MAP

| SFR Name | SFR<br>Addr | Bit 15   | Bit 14 | Bit 13   | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8      | Bit 7        | Bit 6   | Bit 5 | Bit 4       | Bit 3        | Bit 2 | Bit 1  | Bit 0 | All<br>Resets |

|----------|-------------|----------|--------|----------|--------|--------|--------|-------|------------|--------------|---------|-------|-------------|--------------|-------|--------|-------|---------------|

| U1MODE   | 0220        | UARTEN   | _      | USIDL    | IREN   | RTSMD  | _      | UEN1  | UEN0       | WAKE         | LPBACK  | ABAUD | URXINV      | BRGH         | PDSEI | _<1:0> | STSEL | 0000          |

| U1STA    | 0222        | UTXISEL1 | UTXINV | UTXISEL0 | -      | UTXBRK | UTXEN  | UTXBF | TRMT       | URXISE       | EL<1:0> | ADDEN | RIDLE       | PERR         | FERR  | OERR   | URXDA | 0110          |

| U1TXREG  | 0224        | _        | _      | _        | _      | _      | —      | _     | UTX8       |              |         | U     | ART Transm  | nit Register |       |        |       | XXXX          |

| U1RXREG  | 0226        | _        | _      | _        | _      | _      | _      | _     | URX8       |              |         | U     | ART Receive | ed Register  |       |        |       | 0000          |

| U1BRG    | 0228        |          |        |          |        |        |        | Bau   | d Rate Ger | erator Presc | aler    |       |             |              |       |        |       | 0000          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| U-0                               | R/W-1               | R/W-0                                  | R/W-0           | U-0              | R/W-1          | R/W-0           | R/W-0 |

|-----------------------------------|---------------------|----------------------------------------|-----------------|------------------|----------------|-----------------|-------|

| _                                 |                     | U1RXIP<2:0>                            |                 |                  |                | SPI1IP<2:0>     |       |

| bit 15                            |                     |                                        |                 |                  |                |                 | bit 8 |

|                                   |                     |                                        |                 |                  |                |                 |       |

| U-0                               | R/W-1               | R/W-0                                  | R/W-0           | U-0              | R/W-1          | R/W-0           | R/W-0 |

| —                                 |                     | SPI1EIP<2:0>                           |                 |                  |                | T3IP<2:0>       |       |

| bit 7                             |                     |                                        |                 |                  |                |                 | bit C |

| Legend:                           |                     |                                        |                 |                  |                |                 |       |

| R = Readab                        | ole bit             | W = Writable                           | bit             | U = Unimplei     | mented bit, re | ad as '0'       |       |

| n = Value at POR '1' = Bit is set |                     |                                        |                 | '0' = Bit is cle |                | x = Bit is unkn | own   |

|                                   |                     |                                        |                 |                  |                |                 |       |

| bit 15                            | Unimpleme           | nted: Read as '                        | 0'              |                  |                |                 |       |

| bit 14-12                         | U1RXIP<2:0          | <b>)&gt;:</b> UART1 Rece               | eiver Interrupt | Priority bits    |                |                 |       |

|                                   | 111 = Interr        | upt is priority 7 (                    | highest priori  | ty interrupt)    |                |                 |       |

|                                   | •                   |                                        |                 |                  |                |                 |       |

|                                   | •                   |                                        |                 |                  |                |                 |       |

|                                   | 001 = Interr        | upt is priority 1                      |                 |                  |                |                 |       |

|                                   | 000 <b>= Interr</b> | upt source is dis                      | abled           |                  |                |                 |       |

| bit 11                            | Unimpleme           | nted: Read as '                        | 0'              |                  |                |                 |       |

| bit 10-8                          |                     | SPI1 Event In                          |                 | •                |                |                 |       |

|                                   | 111 = Interr        | upt is priority 7 (                    | highest priori  | ty interrupt)    |                |                 |       |

|                                   | •                   |                                        |                 |                  |                |                 |       |

|                                   | •                   |                                        |                 |                  |                |                 |       |

|                                   |                     | upt is priority 1                      |                 |                  |                |                 |       |

|                                   |                     | upt source is dis                      |                 |                  |                |                 |       |

| bit 7                             | •                   | nted: Read as '                        |                 |                  |                |                 |       |

| bit 6-4                           |                     | 0>: SPI1 Error Ir                      | -               | -                |                |                 |       |

|                                   | 111 = Interr<br>•   | upt is priority 7 (                    | nignest priori  | ty interrupt)    |                |                 |       |

|                                   | •                   |                                        |                 |                  |                |                 |       |

|                                   | •                   |                                        |                 |                  |                |                 |       |

|                                   |                     | upt is priority 1<br>upt source is dis | abled           |                  |                |                 |       |

| bit 3                             |                     | nted: Read as '                        |                 |                  |                |                 |       |

| bit 2-0                           | -                   | Timer3 Interrupt                       |                 |                  |                |                 |       |

|                                   |                     | upt is priority 7 (                    | -               | ty interrupt)    |                |                 |       |

|                                   | •                   |                                        |                 | • •              |                |                 |       |

|                                   | •                   |                                        |                 |                  |                |                 |       |

|                                   | •<br>001 = Interr   | upt is priority 1                      |                 |                  |                |                 |       |

|                                   |                     | upt is priority 1                      |                 |                  |                |                 |       |

000 = Interrupt source is disabled

| U-0        | R/W-1        | R/W-0                                     | R/W-0          | U-0                    | R/W-1                       | R/W-0           | R/W-0 |

|------------|--------------|-------------------------------------------|----------------|------------------------|-----------------------------|-----------------|-------|

| _          |              | C1IP<2:0> <sup>(1)</sup>                  |                | _                      |                             | C1RXIP<2:0>(1)  |       |

| bit 15     | •            |                                           |                |                        |                             |                 | bit 8 |

|            |              |                                           |                |                        |                             |                 |       |

| U-0        | R/W-1        | R/W-0                                     | R/W-0          | U-0                    | R/W-1                       | R/W-0           | R/W-0 |

| —          |              | SPI2IP<2:0>                               |                | _                      |                             | SPI2EIP<2:0>    |       |

| bit 7      |              |                                           |                |                        |                             |                 | bit C |

| Legend:    |              |                                           |                |                        |                             |                 |       |

| R = Readab | le bit       | W = Writable b                            | oit            | U = Unimple            | mented bit, re              | ead as '0'      |       |

|            |              | '1' = Bit is set                          |                | '0' = Bit is cle       |                             | x = Bit is unkn | own   |

|            |              |                                           |                |                        |                             |                 |       |

| bit 15     | Unimpleme    | ented: Read as '0                         | ,              |                        |                             |                 |       |

| bit 14-12  | C1IP<2:0>:   | ECAN1 Event In                            | terrupt Priori | ty bits <sup>(1)</sup> |                             |                 |       |

|            | 111 = Interr | rupt is priority 7 (h                     | nighest priori | ty interrupt)          |                             |                 |       |

|            | •            |                                           |                |                        |                             |                 |       |

|            | •            |                                           |                |                        |                             |                 |       |

|            |              | rupt is priority 1                        |                |                        |                             |                 |       |

|            |              | rupt source is disa                       |                |                        |                             |                 |       |

| bit 11     |              | ented: Read as '0                         |                |                        |                             |                 |       |

| bit 10-8   |              | 0>: ECAN1 Rece                            |                |                        | riority bits <sup>(1)</sup> |                 |       |

|            | 111 = Interr | rupt is priority 7 (h                     | highest priori | ty interrupt)          |                             |                 |       |

|            | •            |                                           |                |                        |                             |                 |       |

|            | •            |                                           |                |                        |                             |                 |       |

|            |              | rupt is priority 1                        |                |                        |                             |                 |       |

| h:+ 7      |              | rupt source is disa                       |                |                        |                             |                 |       |

| bit 7      | -            | ented: Read as '0                         |                | . hite                 |                             |                 |       |

| bit 6-4    |              | SPI2 Event Int<br>rupt is priority 7 (h   | -              | -                      |                             |                 |       |

|            | •            |                                           | lighest phon   | ly interrupt)          |                             |                 |       |

|            | •            |                                           |                |                        |                             |                 |       |

|            | •            | unt in priority 1                         |                |                        |                             |                 |       |

|            |              | rupt is priority 1<br>rupt source is disa | abled          |                        |                             |                 |       |

| bit 3      |              | ented: Read as '0                         |                |                        |                             |                 |       |

| bit 2-0    | -            | :0>: SPI2 Error In                        |                | tv bits                |                             |                 |       |

|            |              | rupt is priority 7 (h                     |                | •                      |                             |                 |       |

|            | •            |                                           | -              |                        |                             |                 |       |

|            | •            |                                           |                |                        |                             |                 |       |

|            | 001 = Interr | rupt is priority 1                        |                |                        |                             |                 |       |

|            |              | rupt io priority i<br>rupt course is die  |                |                        |                             |                 |       |

### 000 = Interrupt source is disabled

Note 1: Interrupts disabled on devices without ECAN<sup>™</sup> modules.

| U-0                               | U-0                                                                                                                                                                                | U-0                                                                                                                                                                                                                       | U-0                                                                                                                   | U-0                                              | R/W-1                        | R/W-0           | R/W-0 |

|-----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|------------------------------|-----------------|-------|

|                                   | _                                                                                                                                                                                  | _                                                                                                                                                                                                                         | _                                                                                                                     | _                                                |                              | C1TXIP<2:0>(1)  |       |

| bit 15                            |                                                                                                                                                                                    |                                                                                                                                                                                                                           |                                                                                                                       |                                                  |                              |                 | bit   |

|                                   |                                                                                                                                                                                    |                                                                                                                                                                                                                           |                                                                                                                       |                                                  |                              |                 |       |

| U-0                               | R/W-1                                                                                                                                                                              | R/W-0                                                                                                                                                                                                                     | R/W-0                                                                                                                 | U-0                                              | R/W-1                        | R/W-0           | R/W-0 |

|                                   |                                                                                                                                                                                    | DMA7IP<2:0>                                                                                                                                                                                                               |                                                                                                                       | <u> </u>                                         |                              | DMA6IP<2:0>     |       |

| bit 7                             |                                                                                                                                                                                    |                                                                                                                                                                                                                           |                                                                                                                       |                                                  |                              |                 | bit   |

| Legend:                           |                                                                                                                                                                                    |                                                                                                                                                                                                                           |                                                                                                                       |                                                  |                              |                 |       |

| R = Readab                        | ole bit                                                                                                                                                                            | W = Writable                                                                                                                                                                                                              | bit                                                                                                                   | U = Unimpler                                     | nented bit, rea              | id as '0'       |       |

| n = Value at POR '1' = Bit is set |                                                                                                                                                                                    |                                                                                                                                                                                                                           |                                                                                                                       | '0' = Bit is cle                                 | ared                         | x = Bit is unkn | iown  |

|                                   |                                                                                                                                                                                    |                                                                                                                                                                                                                           |                                                                                                                       |                                                  |                              |                 |       |

| bit 15-11                         | -                                                                                                                                                                                  | nted: Read as '                                                                                                                                                                                                           |                                                                                                                       |                                                  |                              |                 |       |

| bit 10-8                          | C1TXIP<2.0                                                                                                                                                                         | >: FCAN1 Trans                                                                                                                                                                                                            | smit Data Red                                                                                                         | quest Interrupt                                  | Priority bits <sup>(1)</sup> |                 |       |

|                                   | 011741 32.0                                                                                                                                                                        |                                                                                                                                                                                                                           |                                                                                                                       |                                                  |                              |                 |       |

|                                   |                                                                                                                                                                                    | upt is priority 7 (I                                                                                                                                                                                                      |                                                                                                                       | • •                                              |                              |                 |       |

|                                   |                                                                                                                                                                                    |                                                                                                                                                                                                                           |                                                                                                                       | • •                                              | ineniy ene                   |                 |       |

|                                   |                                                                                                                                                                                    |                                                                                                                                                                                                                           |                                                                                                                       | • •                                              |                              |                 |       |

|                                   | 111 = Intern<br>•<br>•                                                                                                                                                             | upt is priority 7 (I                                                                                                                                                                                                      |                                                                                                                       | • •                                              |                              |                 |       |

|                                   | 111 = Intern<br>•<br>•<br>•<br>•<br>•                                                                                                                                              | upt is priority 7 (I<br>upt is priority 1                                                                                                                                                                                 | nighest priorif                                                                                                       | • •                                              |                              |                 |       |

| bit 7                             | 111 = Intern<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•                                                                        | upt is priority 7 (I<br>upt is priority 1<br>upt source is dis                                                                                                                                                            | nighest priorif<br>abled                                                                                              | • •                                              |                              |                 |       |

| bit 7<br>bit 6-4                  | 111 = Intern<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•                                                                        | upt is priority 7 (I<br>upt is priority 1<br>upt source is disa<br><b>nted:</b> Read as '(                                                                                                                                | nighest priorit<br>abled<br>)'                                                                                        | ty interrupt)                                    |                              | ritv bits       |       |

|                                   | 111 = Intern<br>•<br>•<br>001 = Intern<br>000 = Intern<br>Unimpleme<br>DMA7IP<2:0                                                                                                  | upt is priority 7 (I<br>upt is priority 1<br>upt source is disa<br><b>nted:</b> Read as '(<br><b>0&gt;:</b> DMA Channe                                                                                                    | abled<br>o'<br>el 7 Data Tra                                                                                          | ty interrupt)<br>nsfer Complete                  |                              | rity bits       |       |

|                                   | 111 = Intern<br>•<br>•<br>001 = Intern<br>000 = Intern<br>Unimpleme<br>DMA7IP<2:0                                                                                                  | upt is priority 7 (I<br>upt is priority 1<br>upt source is disa<br><b>nted:</b> Read as '(                                                                                                                                | abled<br>o'<br>el 7 Data Tra                                                                                          | ty interrupt)<br>nsfer Complete                  |                              | rity bits       |       |

|                                   | 111 = Intern<br>•<br>•<br>001 = Intern<br>000 = Intern<br>Unimpleme<br>DMA7IP<2:0                                                                                                  | upt is priority 7 (I<br>upt is priority 1<br>upt source is disa<br><b>nted:</b> Read as '(<br><b>0&gt;:</b> DMA Channe                                                                                                    | abled<br>o'<br>el 7 Data Tra                                                                                          | ty interrupt)<br>nsfer Complete                  |                              | rity bits       |       |

|                                   | 111 = Intern<br>001 = Intern<br>000 = Intern<br>Unimpleme<br>DMA7IP<2:0<br>111 = Intern                                                                                            | upt is priority 7 (I<br>upt is priority 1<br>upt source is dis<br><b>nted:</b> Read as '(<br><b>0&gt;:</b> DMA Channe<br>upt is priority 7 (I                                                                             | abled<br>o'<br>el 7 Data Tra                                                                                          | ty interrupt)<br>nsfer Complete                  |                              | rity bits       |       |

|                                   | 111 = Intern<br>001 = Intern<br>000 = Intern<br>Unimpleme<br>DMA7IP<2:(<br>111 = Intern<br>001 = Intern                                                                            | upt is priority 7 (I<br>upt is priority 1<br>upt source is dis<br><b>nted:</b> Read as '(<br><b>0&gt;:</b> DMA Channe<br>upt is priority 7 (I<br>upt is priority 1                                                        | abled<br><sub>)</sub> '<br>el 7 Data Tra<br>nighest priorit                                                           | ty interrupt)<br>nsfer Complete                  |                              | rity bits       |       |

| bit 6-4                           | 111 = Intern<br>001 = Intern<br>000 = Intern<br>Unimpleme<br>DMA7IP<2:(<br>111 = Intern<br>001 = Intern<br>000 = Intern                                                            | upt is priority 7 (I<br>upt is priority 1<br>upt source is disa<br><b>nted:</b> Read as '(<br><b>0&gt;:</b> DMA Channe<br>upt is priority 7 (I<br>upt is priority 1<br>upt source is disa                                 | abled<br>o'<br>el 7 Data Tra<br>highest priorit                                                                       | ty interrupt)<br>nsfer Complete                  |                              | rity bits       |       |

| bit 6-4<br>bit 3                  | 111 = Intern<br>001 = Intern<br>000 = Intern<br>Unimpleme<br>DMA7IP<2:(<br>111 = Intern<br>001 = Intern<br>000 = Intern<br>Unimpleme                                               | upt is priority 7 (I<br>upt is priority 1<br>upt source is disa<br><b>nted:</b> Read as '(<br><b>0&gt;:</b> DMA Channe<br>upt is priority 7 (I<br>upt is priority 1<br>upt source is disa<br><b>nted:</b> Read as '(      | abled<br>o'<br>el 7 Data Tra<br>nighest priorit<br>abled                                                              | ty interrupt)<br>nsfer Complete<br>ty interrupt) | Interrupt Prior              |                 |       |

|                                   | 111 = Intern<br>001 = Intern<br>000 = Intern<br>Unimpleme<br>DMA7IP<2:(<br>111 = Intern<br>001 = Intern<br>Unimpleme<br>DMA6IP<2:(                                                 | upt is priority 7 (I<br>upt is priority 1<br>upt source is dis<br><b>nted:</b> Read as '(<br><b>0&gt;:</b> DMA Channe<br>upt is priority 7 (I<br>upt source is dis<br><b>nted:</b> Read as '(<br><b>0&gt;:</b> DMA Channe | abled<br>o'<br>el 7 Data Tra<br>nighest priorit<br>abled<br>o'<br>el 6 Data Tra                                       | ty interrupt)<br>nsfer Complete<br>ty interrupt) | Interrupt Prior              |                 |       |

| bit 6-4<br>bit 3                  | 111 = Intern<br>001 = Intern<br>000 = Intern<br>Unimpleme<br>DMA7IP<2:(<br>111 = Intern<br>001 = Intern<br>Unimpleme<br>DMA6IP<2:(                                                 | upt is priority 7 (I<br>upt is priority 1<br>upt source is disa<br><b>nted:</b> Read as '(<br><b>0&gt;:</b> DMA Channe<br>upt is priority 7 (I<br>upt is priority 1<br>upt source is disa<br><b>nted:</b> Read as '(      | abled<br>o'<br>el 7 Data Tra<br>nighest priorit<br>abled<br>o'<br>el 6 Data Tra                                       | ty interrupt)<br>nsfer Complete<br>ty interrupt) | Interrupt Prior              |                 |       |

| bit 6-4<br>bit 3                  | 111 = Intern<br>001 = Intern<br>000 = Intern<br>Unimpleme<br>DMA7IP<2:(<br>111 = Intern<br>001 = Intern<br>Unimpleme<br>DMA6IP<2:(                                                 | upt is priority 7 (I<br>upt is priority 1<br>upt source is dis<br><b>nted:</b> Read as '(<br><b>0&gt;:</b> DMA Channe<br>upt is priority 7 (I<br>upt source is dis<br><b>nted:</b> Read as '(<br><b>0&gt;:</b> DMA Channe | abled<br>o'<br>el 7 Data Tra<br>nighest priorit<br>abled<br>o'<br>el 6 Data Tra                                       | ty interrupt)<br>nsfer Complete<br>ty interrupt) | Interrupt Prior              |                 |       |

| bit 6-4<br>bit 3                  | 111 = Intern<br>001 = Intern<br>000 = Intern<br>Unimpleme<br>DMA7IP<2:(<br>111 = Intern<br>001 = Intern<br>Unimpleme<br>DMA6IP<2:(                                                 | upt is priority 7 (I<br>upt is priority 1<br>upt source is dis<br><b>nted:</b> Read as '(<br><b>0&gt;:</b> DMA Channe<br>upt is priority 7 (I<br>upt source is dis<br><b>nted:</b> Read as '(<br><b>0&gt;:</b> DMA Channe | abled<br>o'<br>el 7 Data Tra<br>nighest priorit<br>abled<br>o'<br>el 6 Data Tra                                       | ty interrupt)<br>nsfer Complete<br>ty interrupt) | Interrupt Prior              |                 |       |

| bit 6-4<br>bit 3                  | 111 = Intern<br>001 = Intern<br>000 = Intern<br>Unimpleme<br>DMA7IP<2:(<br>111 = Intern<br>001 = Intern<br>000 = Intern<br>Unimpleme<br>DMA6IP<2:(<br>111 = Intern<br>001 = Intern | upt is priority 7 (I<br>upt is priority 1<br>upt source is dis<br><b>nted:</b> Read as '(<br><b>0&gt;:</b> DMA Channe<br>upt is priority 7 (I<br>upt source is dis<br><b>nted:</b> Read as '(<br><b>0&gt;:</b> DMA Channe | nighest priorit<br>abled<br>o'<br>el 7 Data Tra<br>nighest priorit<br>abled<br>o'<br>el 6 Data Tra<br>nighest priorit | ty interrupt)<br>nsfer Complete<br>ty interrupt) | Interrupt Prior              |                 |       |

Note 1: Interrupts disabled on devices without ECAN™ modules.

| REGISTER      | 11-5: RPIN                        | R7: PERIPHEI                                           | RAL PIN SI |                  | <b>FREGISTER</b> | 7              |       |

|---------------|-----------------------------------|--------------------------------------------------------|------------|------------------|------------------|----------------|-------|

| U-0           | U-0                               | U-0                                                    | R/W-1      | R/W-1            | R/W-1            | R/W-1          | R/W-1 |

| —             | _                                 | _                                                      |            |                  | IC2R<4:0>        |                |       |

| bit 15        | ·                                 | ·                                                      |            |                  |                  |                | bit 8 |

| U-0           | U-0                               | U-0                                                    | R/W-1      | R/W-1            | R/W-1            | R/W-1          | R/W-1 |

| _             | _                                 | —                                                      |            |                  | IC1R<4:0>        |                |       |

| bit 7         |                                   | ·                                                      |            |                  |                  |                | bit ( |

| Legend:       |                                   |                                                        |            |                  |                  |                |       |

| R = Readabl   | le bit                            | W = Writable                                           | bit        | U = Unimple      | mented bit, rea  | ad as '0'      |       |

| -n = Value at | n = Value at POR '1' = Bit is set |                                                        |            | '0' = Bit is cle | eared            | x = Bit is unk | nown  |

|               | •<br>•<br>00001 = Ing             | but tied to RP25                                       |            |                  |                  |                |       |

| bit 7-5       | •                                 | out tied to RP0<br>ented: Read as '0                   | ·,         |                  |                  |                |       |

|               | •                                 |                                                        |            | to the corresp   | onding DDn ni    | 2              |       |

| bit 4-0       | 11111 <b>= In</b> p               | Assign Input Ca<br>out tied to Vss<br>put tied to RP25 | ,          | no me correspo   | onung KPn pl     | 1              |       |

|               | •                                 |                                                        |            |                  |                  |                |       |

|               | •                                 |                                                        |            |                  |                  |                |       |

|               | •                                 | out tied to RP1                                        |            |                  |                  |                |       |

00000 = Input tied to RP0

## 14.2 Input Capture Registers

# **REGISTER 14-1:** ICxCON: INPUT CAPTURE x CONTROL REGISTER (x = 1, 2, 7 OR 8)

| U-0    | U-0 | R/W-0  | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|--------|-----|-----|-----|-----|-------|

| —      | —   | ICSIDL | —   | —   | —   | —   | —     |

| bit 15 |     |        |     |     |     |     | bit 8 |

| R/W-0 | R/W-0 | R/W-0 | R-0, HC | R-0, HC | R/W-0 | R/W-0    | R/W-0 |

|-------|-------|-------|---------|---------|-------|----------|-------|

| ICTMR | ICI<  | 1:0>  | ICOV    | ICBNE   |       | ICM<2:0> |       |

| bit 7 |       |       |         |         |       |          | bit 0 |

| Legend:           | HC = Cleared in Hardware |                             |                    |

|-------------------|--------------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit         | U = Unimplemented bit, read | l as '0'           |

| -n = Value at POR | '1' = Bit is set         | '0' = Bit is cleared        | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                                                                                                                                                                    |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13    | ICSIDL: Input Capture Module Stop in Idle Control bit                                                                                                                                                                         |

|           | 1 = Input capture module halts in CPU Idle mode                                                                                                                                                                               |

|           | 0 = Input capture module continues to operate in CPU Idle mode                                                                                                                                                                |

| bit 12-8  | Unimplemented: Read as '0'                                                                                                                                                                                                    |

| bit 7     | ICTMR: Input Capture Timer Select bits                                                                                                                                                                                        |

|           | <ul> <li>1 = TMR2 contents are captured on capture event</li> <li>0 = TMR3 contents are captured on capture event</li> </ul>                                                                                                  |

| bit 6-5   | ICI<1:0>: Select Number of Captures per Interrupt bits                                                                                                                                                                        |

|           | 11 = Interrupt on every fourth capture event                                                                                                                                                                                  |

|           | <ul> <li>10 = Interrupt on every third capture event</li> <li>01 = Interrupt on every second capture event</li> </ul>                                                                                                         |

|           | 00 = Interrupt on every capture event                                                                                                                                                                                         |

| bit 4     | ICOV: Input Capture Overflow Status Flag bit (read-only)                                                                                                                                                                      |

|           | 1 = Input capture overflow occurred                                                                                                                                                                                           |

|           | 0 = No input capture overflow occurred                                                                                                                                                                                        |

| bit 3     | ICBNE: Input Capture Buffer Empty Status bit (read-only)                                                                                                                                                                      |

|           | <ul> <li>1 = Input capture buffer is not empty, at least one more capture value can be read</li> <li>0 = Input capture buffer is empty</li> </ul>                                                                             |

| bit 2-0   | ICM<2:0>: Input Capture Mode Select bits                                                                                                                                                                                      |

|           | <ul> <li>111 = Input capture functions as interrupt pin only when device is in Sleep or Idle mode<br/>(Rising edge detect only, all other control bits are not applicable)</li> <li>110 = Unused (module disabled)</li> </ul> |

|           | 101 = Capture mode, every 16th rising edge                                                                                                                                                                                    |

|           | 100 = Capture mode, every 4th rising edge                                                                                                                                                                                     |

|           | 011 = Capture mode, every rising edge<br>010 = Capture mode, every falling edge                                                                                                                                               |

|           | 001 = Capture mode, every edge (rising and falling)                                                                                                                                                                           |

|           | (ICI<1:0> bits do not control interrupt generation for this mode)                                                                                                                                                             |

|           | 000 = Input capture module turned off                                                                                                                                                                                         |

|               |                                                                            | •••••            |                  |                    |                  |                  |       |  |  |

|---------------|----------------------------------------------------------------------------|------------------|------------------|--------------------|------------------|------------------|-------|--|--|

| R/W-0         | R/W-0                                                                      | R/W-0            | U-0              | U-0                | U-0              | U-0              | U-0   |  |  |

| FRMEN         | SPIFSD                                                                     | FRMPOL           | —                | _                  | —                | —                | —     |  |  |

| bit 15        |                                                                            |                  |                  |                    |                  |                  | bit 8 |  |  |

|               |                                                                            |                  |                  |                    |                  |                  |       |  |  |

| U-0           | U-0                                                                        | U-0              | U-0              | U-0                | U-0              | R/W-0            | U-0   |  |  |

| —             | —                                                                          | —                | —                | —                  | —                | FRMDLY           |       |  |  |

| bit 7         |                                                                            |                  |                  |                    |                  |                  | bit 0 |  |  |

|               |                                                                            |                  |                  |                    |                  |                  |       |  |  |

| Legend:       |                                                                            |                  |                  |                    |                  |                  |       |  |  |

| R = Readable  | e bit                                                                      | W = Writable     | bit              | U = Unimpler       | nented bit, read | l as '0'         |       |  |  |

| -n = Value at | POR                                                                        | '1' = Bit is set |                  | '0' = Bit is cle   | ared             | x = Bit is unkno | own   |  |  |

|               |                                                                            |                  |                  |                    |                  |                  |       |  |  |

| bit 15        | FRMEN: Fran                                                                | med SPIx Supp    | ort bit          |                    |                  |                  |       |  |  |

|               |                                                                            |                  |                  | in used as fram    | ie sync pulse in | put/output)      |       |  |  |

|               |                                                                            | SPIx support dis |                  |                    |                  |                  |       |  |  |

| bit 14        |                                                                            | me Sync Pulse    |                  | ntrol bit          |                  |                  |       |  |  |

|               | 1 = Frame sync pulse input (slave)<br>0 = Frame sync pulse output (master) |                  |                  |                    |                  |                  |       |  |  |

| bit 13        | ,                                                                          | ame Sync Puls    | ( )              |                    |                  |                  |       |  |  |

| bit 15        |                                                                            | nc pulse is acti |                  |                    |                  |                  |       |  |  |

|               |                                                                            | nc pulse is acti |                  |                    |                  |                  |       |  |  |

| bit 12-2      |                                                                            | ited: Read as '  |                  |                    |                  |                  |       |  |  |

| bit 1         | FRMDLY: Fra                                                                | ame Sync Pulse   | e Edge Selec     | t bit              |                  |                  |       |  |  |

|               |                                                                            | nc pulse coinci  | •                |                    |                  |                  |       |  |  |

|               | 0 = Frame sy                                                               | nc pulse prece   | des first bit cl | ock                |                  |                  |       |  |  |

| bit 0         | Unimplemen                                                                 | ted: This bit m  | ust not be se    | t to '1' by the us | ser application  |                  |       |  |  |

|               |                                                                            |                  |                  |                    |                  |                  |       |  |  |

| REGISTER      | 19-6: CilNTF                                       | : ECAN™ IN                                                                                                                      | ITERRUPT       | FLAG REGIS                  | STER              |                 |       |  |  |  |

|---------------|----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|----------------|-----------------------------|-------------------|-----------------|-------|--|--|--|

| U-0           | U-0                                                | R-0                                                                                                                             | R-0            | R-0                         | R-0               | R-0             | R-0   |  |  |  |

|               | —                                                  | TXBO                                                                                                                            | TXBP           | RXBP                        | TXWAR             | RXWAR           | EWARN |  |  |  |

| bit 15        |                                                    |                                                                                                                                 |                |                             |                   |                 | bit 8 |  |  |  |

| R/C-0         | R/C-0                                              | R/C-0                                                                                                                           | U-0            | R/C-0                       | R/C-0             | R/C-0           | R/C-0 |  |  |  |

| IVRIF         | WAKIF                                              | ERRIF                                                                                                                           | _              | FIFOIF                      | RBOVIF            | RBIF            | TBIF  |  |  |  |

| bit 7         |                                                    |                                                                                                                                 |                |                             |                   |                 | bit C |  |  |  |

| Legend:       |                                                    | C = Writeable                                                                                                                   | bit, but only  | '0' can be writt            | en to clear the b | oit             |       |  |  |  |

| R = Readabl   | le bit                                             | W = Writable                                                                                                                    | bit            | U = Unimple                 | mented bit, read  | d as '0'        |       |  |  |  |

| -n = Value at | t POR                                              | '1' = Bit is set                                                                                                                |                | '0' = Bit is cle            | eared             | x = Bit is unkr | nown  |  |  |  |

| bit 15-14     | Unimplemen                                         | ted: Read as '                                                                                                                  | 0'             |                             |                   |                 |       |  |  |  |

| bit 13        | -                                                  | mitter in Error                                                                                                                 |                | bit                         |                   |                 |       |  |  |  |

|               | 1 = Transmitte                                     | er is in Bus Off                                                                                                                | state          |                             |                   |                 |       |  |  |  |

|               | 0 = Transmitte                                     | er is not in Bus                                                                                                                | Off state      |                             |                   |                 |       |  |  |  |

| bit 12        |                                                    | mitter in Error S                                                                                                               |                | sive bit                    |                   |                 |       |  |  |  |

|               |                                                    | er is in Bus Pa<br>er is not in Bus                                                                                             |                | -                           |                   |                 |       |  |  |  |

| bit 11        |                                                    | ver in Error Sta                                                                                                                |                |                             |                   |                 |       |  |  |  |

|               |                                                    | is in Bus Passi                                                                                                                 |                | ve bit                      |                   |                 |       |  |  |  |

|               |                                                    | is not in Bus P                                                                                                                 |                |                             |                   |                 |       |  |  |  |

| bit 10        | TXWAR: Trar                                        | nsmitter in Erro                                                                                                                | r State Warni  | ng bit                      |                   |                 |       |  |  |  |

|               |                                                    | 1 = Transmitter is in Error Warning state                                                                                       |                |                             |                   |                 |       |  |  |  |

|               |                                                    | er is not in Erro                                                                                                               | -              |                             |                   |                 |       |  |  |  |

| bit 9         |                                                    | eiver in Error S                                                                                                                | •              | bit                         |                   |                 |       |  |  |  |

|               |                                                    | <ol> <li>Receiver is in Error Warning state</li> <li>Receiver is not in Error Warning state</li> </ol>                          |                |                             |                   |                 |       |  |  |  |

| bit 8         |                                                    |                                                                                                                                 | •              |                             | , hit             |                 |       |  |  |  |

| bit o         |                                                    | <b>EWARN:</b> Transmitter or Receiver in Error State Warning bit<br>1 = Transmitter or Receiver is in Error State Warning state |                |                             |                   |                 |       |  |  |  |

|               |                                                    | er or Receiver                                                                                                                  |                | •                           |                   |                 |       |  |  |  |

| bit 7         | IVRIF: Invalid Message Received Interrupt Flag bit |                                                                                                                                 |                |                             |                   |                 |       |  |  |  |

|               |                                                    | Request has o                                                                                                                   |                |                             |                   |                 |       |  |  |  |

| 1.11.0        | •                                                  | Request has no                                                                                                                  |                |                             |                   |                 |       |  |  |  |

| bit 6         |                                                    | Wake-up Activi<br>Request has o                                                                                                 |                | ag bit                      |                   |                 |       |  |  |  |

|               |                                                    | Request has no                                                                                                                  |                |                             |                   |                 |       |  |  |  |

| bit 5         | •                                                  | •                                                                                                                               |                | ources in CilN <sup>-</sup> | TF<13:8> regist   | er)             |       |  |  |  |

|               |                                                    | Request has or                                                                                                                  | · ·            |                             |                   |                 |       |  |  |  |

|               |                                                    | Request has no                                                                                                                  |                |                             |                   |                 |       |  |  |  |

| bit 4         | Unimplemen                                         | ted: Read as '                                                                                                                  | 0'             |                             |                   |                 |       |  |  |  |

| bit 3         | FIFOIF: FIFO                                       | Almost Full In                                                                                                                  | terrupt Flag b | it                          |                   |                 |       |  |  |  |

|               | 1 = Interrupt Request has occurred                 |                                                                                                                                 |                |                             |                   |                 |       |  |  |  |

|               | •                                                  | Request has no                                                                                                                  |                |                             |                   |                 |       |  |  |  |

| bit 2         |                                                    | Buffer Overflov                                                                                                                 |                | ag bit                      |                   |                 |       |  |  |  |

|               |                                                    | Request has or<br>Request has no                                                                                                |                |                             |                   |                 |       |  |  |  |

| bit 1         |                                                    | ffer Interrupt FI                                                                                                               |                |                             |                   |                 |       |  |  |  |

|               |                                                    | Request has or                                                                                                                  |                |                             |                   |                 |       |  |  |  |

|               |                                                    | Request has no                                                                                                                  |                |                             |                   |                 |       |  |  |  |

| bit 0         |                                                    | fer Interrupt Fla                                                                                                               |                |                             |                   |                 |       |  |  |  |

|               |                                                    | Request has or                                                                                                                  |                |                             |                   |                 |       |  |  |  |

|               | 0 = Interrupt I                                    | Request has no                                                                                                                  | ot occurred    |                             |                   |                 |       |  |  |  |