# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Detalls                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Active                                                                        |

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 40 MIPs                                                                       |

| Connectivity               | I <sup>2</sup> C, PMP, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                    |

| Number of I/O              | 21                                                                            |

| Program Memory Size        | 64KB (22K x 24)                                                               |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 8K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                     |

| Data Converters            | A/D 10x10b/12b                                                                |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                                |

| Supplier Device Package    | 28-SOIC                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24hj64gp202-i-so |

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

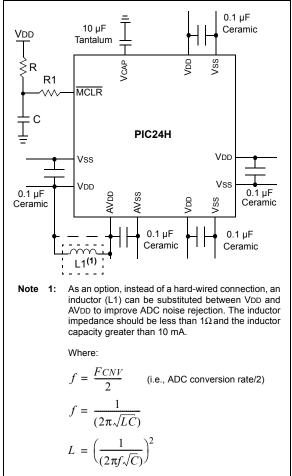

# FIGURE 2-1: RECOMMENDED MINIMUM CONNECTION

# 2.2.1 TANK CAPACITORS

On boards with power traces running longer than six inches in length, it is suggested to use a tank capacitor for integrated circuits including MCUs to supply a local power source. The value of the tank capacitor should be determined based on the trace resistance that connects the power supply source to the device, and the maximum current drawn by the device in the application. In other words, select the tank capacitor so that it meets the acceptable voltage sag at the device. Typical values range from 4.7  $\mu$ F to 47  $\mu$ F.

# 2.3 CPU Logic Filter Capacitor Connection (VCAP)

A low-ESR (< 5 Ohms) capacitor is required on the VCAP pin, which is used to stabilize the voltage regulator output voltage. The VCAP pin must not be connected to VDD, and must have a capacitor between 4.7  $\mu$ F and 10  $\mu$ F, preferably surface mount connected within one-eights inch of the VCAP pin connected to ground. The type can be ceramic or tantalum. Refer to **Section 28.0** "Electrical Characteristics" for additional information.

The placement of this capacitor should be close to the VCAP. It is recommended that the trace length not exceed one-quarter inch (6 mm). Refer to **Section 25.2 "On-Chip Voltage Regulator"** for details.

# 2.4 Master Clear (MCLR) Pin

The MCLR pin provides for two specific device functions:

- Device Reset

- Device programming and debugging

During device programming and debugging, the resistance and capacitance that can be added to the pin must be considered. Device programmers and debuggers drive the  $\overline{\text{MCLR}}$  pin. Consequently, specific voltage levels (VIH and VIL) and fast signal transitions must not be adversely affected. Therefore, specific values of R and C will need to be adjusted based on the application and PCB requirements.

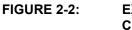

For example, as shown in Figure 2-2, it is recommended that the capacitor C, be isolated from the MCLR pin during programming and debugging operations.

Place the components shown in Figure 2-2 within one-quarter inch (6 mm) from the MCLR pin.

#### EXAMPLE OF MCLR PIN CONNECTIONS

- - 2:  $\underline{R1} \leq 470\Omega$  will limit any current flowing into  $\overline{MCLR}$  from the external capacitor C, in the event of  $\overline{MCLR}$  pin breakdown, due to Electrostatic Discharge (ESD) or <u>Electrical</u> Overstress (EOS). Ensure that the MCLR pin VIH and VIL specifications are met.

| U-0          | R/W-1             | R/W-0                                    | R/W-0          | U-0               | R/W-1            | R/W-0           | R/W-0 |

|--------------|-------------------|------------------------------------------|----------------|-------------------|------------------|-----------------|-------|

| _            |                   | U2TXIP<2:0>                              |                | —                 |                  | U2RXIP<2:0>     |       |

| bit 15       |                   |                                          |                |                   |                  |                 | bit 8 |

|              |                   |                                          |                |                   |                  |                 |       |

| U-0          | R/W-1             | R/W-0                                    | R/W-0          | U-0               | R/W-1            | R/W-0           | R/W-0 |

| —            |                   | INT2IP<2:0>                              |                |                   |                  | T5IP<2:0>       |       |

| bit 7        |                   |                                          |                |                   |                  |                 | bit ( |

| Legend:      |                   |                                          |                |                   |                  |                 |       |

| R = Readab   | le bit            | W = Writable                             | bit            | U = Unimple       | emented bit, rea | ad as '0'       |       |

| -n = Value a | t POR             | '1' = Bit is set                         |                | '0' = Bit is cl   | eared            | x = Bit is unkr | nown  |

| bit 15       | Unimpleme         | ented: Read as '                         | 0'             |                   |                  |                 |       |

| bit 14-12    | -                 | 0>: UART2 Trans                          |                | upt Prioritv bits |                  |                 |       |

|              |                   | rupt is priority 7 (                     |                |                   |                  |                 |       |

|              | •                 |                                          |                |                   |                  |                 |       |

|              | •                 |                                          |                |                   |                  |                 |       |

|              | 001 = Interr      | rupt is priority 1                       |                |                   |                  |                 |       |

|              | 000 = Interr      | upt source is dis                        | abled          |                   |                  |                 |       |

| bit 11       | Unimpleme         | ented: Read as '                         | 0'             |                   |                  |                 |       |

| bit 10-8     | U2RXIP<2:         | 0>: UART2 Rece                           | eiver Interrup | t Priority bits   |                  |                 |       |

|              | 111 = Interr      | rupt is priority 7 (                     | highest priori | ity interrupt)    |                  |                 |       |

|              | •                 |                                          |                |                   |                  |                 |       |

|              | •                 |                                          |                |                   |                  |                 |       |

|              | 001 = Interr      | rupt is priority 1                       |                |                   |                  |                 |       |

|              | 000 = Interr      | rupt source is dis                       | abled          |                   |                  |                 |       |

| bit 7        | Unimpleme         | ented: Read as '                         | 0'             |                   |                  |                 |       |

| bit 6-4      |                   | >: External Inter                        |                |                   |                  |                 |       |

|              | 111 = Interr      | rupt is priority 7 (                     | highest priori | ity interrupt)    |                  |                 |       |

|              | •                 |                                          |                |                   |                  |                 |       |

|              | •                 |                                          |                |                   |                  |                 |       |

|              |                   | rupt is priority 1<br>rupt source is dis | abled          |                   |                  |                 |       |

| bit 3        | Unimpleme         | ented: Read as '                         | 0'             |                   |                  |                 |       |

| bit 2-0      | T5IP<2:0>:        | Timer5 Interrupt                         | Priority bits  |                   |                  |                 |       |

|              | 111 = Interr<br>• | rupt is priority 7 (                     | highest prior  | ity interrupt)    |                  |                 |       |

|              | •                 |                                          |                |                   |                  |                 |       |

|              | •                 | and the method of the state              |                |                   |                  |                 |       |

|              |                   | rupt is priority 1                       |                |                   |                  |                 |       |

000 = Interrupt source is disabled

| U-0          | R/W-1                                                                        | R/W-0                                     | R/W-0          | U-0                    | R/W-1          | R/W-0           | R/W-0 |  |  |  |

|--------------|------------------------------------------------------------------------------|-------------------------------------------|----------------|------------------------|----------------|-----------------|-------|--|--|--|

| _            |                                                                              | C1IP<2:0> <sup>(1)</sup>                  |                | _                      |                | C1RXIP<2:0>(1)  |       |  |  |  |

| bit 15       | •                                                                            |                                           |                |                        |                |                 | bit 8 |  |  |  |

|              |                                                                              |                                           |                |                        |                |                 |       |  |  |  |

| U-0          | R/W-1                                                                        | R/W-0                                     | R/W-0          | U-0                    | R/W-1          | R/W-0           | R/W-0 |  |  |  |

| —            |                                                                              | SPI2IP<2:0>                               |                | _                      |                | SPI2EIP<2:0>    |       |  |  |  |

| bit 7        |                                                                              |                                           |                |                        |                |                 | bit C |  |  |  |

| Legend:      |                                                                              |                                           |                |                        |                |                 |       |  |  |  |

| R = Readab   | le bit                                                                       | W = Writable b                            | oit            | U = Unimple            | mented bit, re | ead as '0'      |       |  |  |  |

| -n = Value a | t POR                                                                        | '1' = Bit is set                          |                | '0' = Bit is cle       |                | x = Bit is unkn | own   |  |  |  |

|              |                                                                              |                                           |                |                        |                |                 |       |  |  |  |

| bit 15       | Unimpleme                                                                    | ented: Read as '0                         | ,              |                        |                |                 |       |  |  |  |

| bit 14-12    | C1IP<2:0>:                                                                   | ECAN1 Event In                            | terrupt Priori | ty bits <sup>(1)</sup> |                |                 |       |  |  |  |

|              | 111 = Interr                                                                 | rupt is priority 7 (h                     | nighest priori | ty interrupt)          |                |                 |       |  |  |  |

|              | •                                                                            |                                           |                |                        |                |                 |       |  |  |  |

|              | •                                                                            |                                           |                |                        |                |                 |       |  |  |  |

|              | 001 = Interrupt is priority 1                                                |                                           |                |                        |                |                 |       |  |  |  |

|              |                                                                              | rupt source is disa                       |                |                        |                |                 |       |  |  |  |

| bit 11       |                                                                              | ented: Read as '0                         |                |                        |                |                 |       |  |  |  |

| bit 10-8     | C1RXIP<2:0>: ECAN1 Receive Data Ready Interrupt Priority bits <sup>(1)</sup> |                                           |                |                        |                |                 |       |  |  |  |

|              | 111 = Interr                                                                 | rupt is priority 7 (h                     | highest priori | ty interrupt)          |                |                 |       |  |  |  |

|              | •                                                                            |                                           |                |                        |                |                 |       |  |  |  |

|              | •                                                                            |                                           |                |                        |                |                 |       |  |  |  |

|              |                                                                              | rupt is priority 1                        |                |                        |                |                 |       |  |  |  |

| h:+ 7        |                                                                              | rupt source is disa                       |                |                        |                |                 |       |  |  |  |

| bit 7        | -                                                                            | ented: Read as '0                         |                |                        |                |                 |       |  |  |  |

| bit 6-4      |                                                                              | SPI2 Event Int<br>rupt is priority 7 (h   | -              | -                      |                |                 |       |  |  |  |

|              | •                                                                            |                                           | lighest phon   | ly interrupt)          |                |                 |       |  |  |  |

|              | •                                                                            |                                           |                |                        |                |                 |       |  |  |  |

|              | •                                                                            | unt in priority 1                         |                |                        |                |                 |       |  |  |  |

|              |                                                                              | rupt is priority 1<br>rupt source is disa | abled          |                        |                |                 |       |  |  |  |

| bit 3        |                                                                              | ented: Read as '0                         |                |                        |                |                 |       |  |  |  |

| bit 2-0      | -                                                                            | :0>: SPI2 Error In                        |                | tv bits                |                |                 |       |  |  |  |

|              |                                                                              | rupt is priority 7 (h                     |                | •                      |                |                 |       |  |  |  |

|              | •                                                                            |                                           | -              |                        |                |                 |       |  |  |  |

|              | •                                                                            |                                           |                |                        |                |                 |       |  |  |  |

|              | 001 = Interr                                                                 | rupt is priority 1                        |                |                        |                |                 |       |  |  |  |

|              |                                                                              | rupt io priority i<br>rupt course is die  |                |                        |                |                 |       |  |  |  |

# 000 = Interrupt source is disabled

Note 1: Interrupts disabled on devices without ECAN<sup>™</sup> modules.

# REGISTER 7-29: INTTREG: INTERRUPT CONTROL AND STATUS REGISTER

| U-0           | U-0                                              | U-0               | U-0             | R-0                                                 | R-0           | R-0       | R-0   |  |  |

|---------------|--------------------------------------------------|-------------------|-----------------|-----------------------------------------------------|---------------|-----------|-------|--|--|

| —             |                                                  | —                 | —               |                                                     | ILI           | R<3:0>    |       |  |  |

| pit 15        |                                                  |                   | •               |                                                     |               |           | bit 8 |  |  |

| U-0           | R-0                                              | R-0               | R-0             | R-0                                                 | R-0           | R-0       | R-0   |  |  |

|               |                                                  | 10                | 100             | VECNUM<6:0>                                         |               | 100       | 10    |  |  |

| bit 7         |                                                  |                   |                 |                                                     |               |           | bit C |  |  |

| Legend:       |                                                  |                   |                 |                                                     |               |           |       |  |  |

| R = Readabl   | e bit                                            | W = Writable      | bit             | U = Unimpleme                                       | ented bit, re | ad as '0' |       |  |  |

| -n = Value at | POR                                              | '1' = Bit is set  |                 | $(0)^{\circ}$ = Bit is cleared $x = Bit is unknown$ |               |           |       |  |  |

|               |                                                  |                   |                 |                                                     |               |           |       |  |  |

| bit 15-12     | Unimplement                                      | ed: Read as '     | כי              |                                                     |               |           |       |  |  |

| bit 11-8      | ILR: New CPU                                     | J Interrupt Pric  | rity Level bits | 6                                                   |               |           |       |  |  |

|               | 1111 <b>= CPU I</b>                              | nterrupt Priorit  | y Level is 15   |                                                     |               |           |       |  |  |

|               | •                                                |                   |                 |                                                     |               |           |       |  |  |

|               | •                                                |                   |                 |                                                     |               |           |       |  |  |

|               | 0001 <b>= CPU  </b><br>0000 <b>= CPU  </b>       |                   |                 |                                                     |               |           |       |  |  |

| bit 7         | Unimplement                                      | ed: Read as '     | כי              |                                                     |               |           |       |  |  |

| bit 6-0       | VECNUM: Vec                                      | ctor Number o     | f Pending Inte  | errupt bits                                         |               |           |       |  |  |

|               | 0111111 = Interrupt Vector pending is number 135 |                   |                 |                                                     |               |           |       |  |  |

|               | •                                                |                   |                 |                                                     |               |           |       |  |  |

|               | •                                                |                   |                 |                                                     |               |           |       |  |  |

|               | 0000001 <b>= In</b> i                            | errupt Vector     | pending is nu   | mber 9                                              |               |           |       |  |  |

|               | 0000000 <b>= In</b> t                            | a mu unt \/a atam |                 |                                                     |               |           |       |  |  |

© 2007-2012 Microchip Technology Inc.

# REGISTER 8-7: DMACS0: DMA CONTROLLER STATUS REGISTER 0 (CONTINUED)

| bit 3 | XWCOL3: Channel 3 DMA RAM Write Collision Flag bit |

|-------|----------------------------------------------------|

|       | 1 = Write collision detected                       |

|       | 0 = No write collision detected                    |

| bit 2 | XWCOL2: Channel 2 DMA RAM Write Collision Flag bit |

|       | 1 = Write collision detected                       |

|       | 0 = No write collision detected                    |

| bit 1 | XWCOL1: Channel 1 DMA RAM Write Collision Flag bit |

|       | 1 = Write collision detected                       |

|       | 0 = No write collision detected                    |

| bit 0 | XWCOL0: Channel 0 DMA RAM Write Collision Flag bit |

|       | 1 = Write collision detected                       |

|       | 0 = No write collision detected                    |

# PIC24HJ32GP302/304, PIC24HJ64GPX02/X04 AND PIC24HJ128GPX02/X04

| REGISTER       | 10-3: PMD3     | : PERIPHER                         | AL MODULE     | E DISABLE C      | ONTROL RE       | GISTER 3        |       |

|----------------|----------------|------------------------------------|---------------|------------------|-----------------|-----------------|-------|

| U-0            | U-0            | U-0                                | U-0           | U-0              | R/W-0           | R/W-0           | R/W-0 |

| _              | —              | —                                  |               | —                | CMPMD           | RTCCMD          | PMPMD |

| bit 15         |                |                                    |               |                  |                 |                 | bit 8 |

| <b>D</b> 444 0 | <b>D</b> /// 0 |                                    |               |                  |                 |                 |       |

| R/W-0          | R/W-0          | U-0                                | U-0           | U-0              | U-0             | U-0             | U-0   |

| CRCMD          | DAC1MD         | —                                  | —             | —                | _               | _               | —     |

| bit 7          |                |                                    |               |                  |                 |                 | bit C |

| Legend:        |                |                                    |               |                  |                 |                 |       |

| R = Readabl    | e bit          | W = Writable I                     | bit           | U = Unimplen     | nented bit, rea | d as '0'        |       |

| -n = Value at  | POR            | '1' = Bit is set                   |               | '0' = Bit is cle | ared            | x = Bit is unkn | own   |

|                |                |                                    |               |                  |                 |                 |       |

| bit 15-11      | Unimplement    | ted: Read as 'd                    | )'            |                  |                 |                 |       |

| bit 10         | CMPMD: Con     | nparator Modul                     | e Disable bit |                  |                 |                 |       |

|                |                | or module is di                    |               |                  |                 |                 |       |

|                | 0 = Comparat   | or module is er                    | nabled        |                  |                 |                 |       |

| bit 9          |                | CC Module Dis                      |               |                  |                 |                 |       |

|                |                | dule is disable<br>dule is enabled |               |                  |                 |                 |       |

| bit 8          |                | P Module Disat                     | -             |                  |                 |                 |       |

| DILO           |                | ule is disabled                    |               |                  |                 |                 |       |

|                |                | ule is enabled                     |               |                  |                 |                 |       |

| bit 7          | CRCMD: CRO     | C Module Disab                     | ole bit       |                  |                 |                 |       |

|                | 1 = CRC mod    | ule is disabled                    |               |                  |                 |                 |       |

|                | 0 = CRC mod    | ule is enabled                     |               |                  |                 |                 |       |

| bit 6          | DAC1MD: DA     | C1 Module Dis                      | able bit      |                  |                 |                 |       |

|                |                | dule is disabled                   |               |                  |                 |                 |       |

|                |                | dule is enabled                    |               |                  |                 |                 |       |

| bit 5-0        | Unimplement    | ted: Read as '(                    | )′            |                  |                 |                 |       |

# 11.6 Peripheral Pin Select

Peripheral pin select configuration enables peripheral set selection and placement on a wide range of I/O pins. By increasing the pinout options available on a particular device, programmers can better tailor the microcontroller to their entire application, rather than trimming the application to fit the device.

The peripheral pin select configuration feature operates over a fixed subset of digital I/O pins. Programmers can independently map the input and/or output of most digital peripherals to any one of these I/O pins. Peripheral pin select is performed in software, and generally does not require the device to be reprogrammed. Hardware safeguards are included that prevent accidental or spurious changes to the peripheral mapping, once it has been established.

## 11.6.1 AVAILABLE PINS

The peripheral pin select feature is used with a range of up to 26 pins. The number of available pins depends on the particular device and its pin count. Pins that support the peripheral pin select feature include the designation "RPn" in their full pin designation, where "RP" designates a remappable peripheral and "n" is the remappable pin number.

#### 11.6.2 CONTROLLING PERIPHERAL PIN SELECT

Peripheral pin select features are controlled through two sets of special function registers: one to map peripheral inputs, and another one to map outputs. Because they are separately controlled, a particular peripheral's input and output (if the peripheral has both) can be placed on any selectable function pin without constraint.

The association of a peripheral to a peripheral selectable pin is handled in two different ways, depending on whether an input or output is being mapped.

## 11.6.2.1 Input Mapping

The inputs of the peripheral pin select options are mapped on the basis of the peripheral. A control register associated with a peripheral dictates the pin it is mapped to. The RPINRx registers are used to configure peripheral input mapping (see Register 11-1 through Register 11-14). Each register contains sets of 5-bit fields, with each set associated with one of the remappable peripherals. Programming a given peripheral's bit field with an appropriate 5-bit value maps the RPn pin with that value to that peripheral. For any given device, the valid range of values for any bit field corresponds to the maximum number of peripheral pin selections supported by the device.

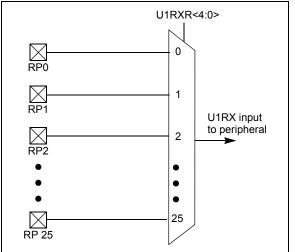

Figure 11-2 illustrates remappable pin selection for U1RX input.

# FIGURE 11-2: REMAPPABLE MUX INPUT FOR U1RX

| Input Name              | Function Name | Register | Configuration<br>Bits |

|-------------------------|---------------|----------|-----------------------|

| External Interrupt 1    | INT1          | RPINR0   | INT1R<4:0>            |

| External Interrupt 2    | INT2          | RPINR1   | INT2R<4:0>            |

| Timer2 External Clock   | T2CK          | RPINR3   | T2CKR<4:0>            |

| Timer3 External Clock   | T3CK          | RPINR3   | T3CKR<4:0>            |

| Timer4 External Clock   | T4CK          | RPINR4   | T4CKR<4:0>            |

| Timer5 External Clock   | T5CK          | RPINR4   | T5CKR<4:0>            |

| Input Capture 1         | IC1           | RPINR7   | IC1R<4:0>             |

| Input Capture 2         | IC2           | RPINR7   | IC2R<4:0>             |

| Input Capture 7         | IC7           | RPINR10  | IC7R<4:0>             |

| Input Capture 8         | IC8           | RPINR10  | IC8R<4:0>             |

| Output Compare Fault A  | OCFA          | RPINR11  | OCFAR<4:0>            |

| UART1 Receive           | U1RX          | RPINR18  | U1RXR<4:0>            |

| UART1 Clear To Send     | U1CTS         | RPINR18  | U1CTSR<4:0>           |

| UART2 Receive           | U2RX          | RPINR19  | U2RXR<4:0>            |

| UART2 Clear To Send     | U2CTS         | RPINR19  | U2CTSR<4:0>           |

| SPI1 Data Input         | SDI1          | RPINR20  | SDI1R<4:0>            |

| SPI1 Clock Input        | SCK1          | RPINR20  | SCK1R<4:0>            |

| SPI1 Slave Select Input | SS1           | RPINR21  | SS1R<4:0>             |

| SPI2 Data Input         | SDI2          | RPINR22  | SDI2R<4:0>            |

| SPI2 Clock Input        | SCK2          | RPINR22  | SCK2R<4:0>            |

| SPI2 Slave Select Input | SS2           | RPINR23  | SS2R<4:0>             |

| ECAN1 Receive           | CIRX          | RPINR26  | CIRXR<4:0>            |

# TABLE 11-1: SELECTABLE INPUT SOURCES (MAPS INPUT TO FUNCTION)<sup>(1)</sup>

**Note 1:** Unless otherwise noted, all inputs use Schmitt input buffers.

# REGISTER 11-15: RPOR0: PERIPHERAL PIN SELECT OUTPUT REGISTERS 0

| U-0                                | U-0 | U-0 | R/W-0                                   | R/W-0                              | R/W-0     | R/W-0 | R/W-0 |

|------------------------------------|-----|-----|-----------------------------------------|------------------------------------|-----------|-------|-------|

| —                                  |     | _   |                                         |                                    | RP1R<4:0> | •     |       |

| bit 15                             |     |     |                                         |                                    |           |       | bit 8 |

|                                    |     |     |                                         |                                    |           |       |       |

| U-0                                | U-0 | U-0 | R/W-0                                   | R/W-0                              | R/W-0     | R/W-0 | R/W-0 |

| —                                  | _   | —   | RP0R<4:0>                               |                                    |           |       |       |

| bit 7                              |     | ·   |                                         |                                    |           |       | bit ( |

|                                    |     |     |                                         |                                    |           |       |       |

| Legend:                            |     |     |                                         |                                    |           |       |       |

| R = Readable bit W = Writable bit  |     |     | oit                                     | U = Unimplemented bit, read as '0' |           |       |       |

| -n = Value at POR '1' = Bit is set |     |     | '0' = Bit is cleared x = Bit is unknown |                                    |           |       |       |

bit 15-13 Unimplemented: Read as '0'

bit 12-8 **RP1R<4:0>:** Peripheral Output Function is Assigned to RP1 Output Pin bits (see Table 11-2 for peripheral function numbers)

bit 7-5 Unimplemented: Read as '0'

bit 4-0 **RP0R<4:0>:** Peripheral Output Function is Assigned to RP0 Output Pin bits (see Table 11-2 for peripheral function numbers)

## REGISTER 11-16: RPOR1: PERIPHERAL PIN SELECT OUTPUT REGISTERS 1

| U-0    | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0     | R/W-0 | R/W-0 |

|--------|-----|-----|-------|-------|-----------|-------|-------|

| —      | —   | —   |       |       | RP3R<4:0> |       |       |

| bit 15 |     |     |       |       |           |       | bit 8 |

| U-0   | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0     | R/W-0 | R/W-0 |

|-------|-----|-----|-------|-------|-----------|-------|-------|

| —     | —   | —   |       |       | RP2R<4:0> |       |       |

| bit 7 |     |     |       |       |           |       | bit 0 |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 15-13 Unimplemented: Read as '0'

bit 12-8 **RP3R<4:0>:** Peripheral Output Function is Assigned to RP3 Output Pin bits (see Table 11-2 for peripheral function numbers)

bit 7-5 Unimplemented: Read as '0'

bit 4-0 **RP2R<4:0>:** Peripheral Output Function is Assigned to RP2 Output Pin bits (see Table 11-2 for peripheral function numbers)

# 14.2 Input Capture Registers

# **REGISTER 14-1:** ICxCON: INPUT CAPTURE x CONTROL REGISTER (x = 1, 2, 7 OR 8)

| U-0    | U-0 | R/W-0  | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|--------|-----|-----|-----|-----|-------|

| —      | —   | ICSIDL | —   | —   | —   | —   | —     |

| bit 15 |     |        |     |     |     |     | bit 8 |

| R/W-0 | R/W-0    | R/W-0 | R-0, HC | R-0, HC | R/W-0 | R/W-0    | R/W-0 |

|-------|----------|-------|---------|---------|-------|----------|-------|

| ICTMR | ICI<1:0> |       | ICOV    | ICBNE   |       | ICM<2:0> |       |

| bit 7 | bit 7    |       |         |         |       |          | bit 0 |

| Legend:           | HC = Cleared in Hardware |                             |                    |  |  |

|-------------------|--------------------------|-----------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit         | U = Unimplemented bit, read | l as '0'           |  |  |

| -n = Value at POR | '1' = Bit is set         | '0' = Bit is cleared        | x = Bit is unknown |  |  |

| bit 15-14 | Unimplemented: Read as '0'                                                                                                                                                                                                    |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13    | ICSIDL: Input Capture Module Stop in Idle Control bit                                                                                                                                                                         |

|           | 1 = Input capture module halts in CPU Idle mode                                                                                                                                                                               |

|           | 0 = Input capture module continues to operate in CPU Idle mode                                                                                                                                                                |

| bit 12-8  | Unimplemented: Read as '0'                                                                                                                                                                                                    |

| bit 7     | ICTMR: Input Capture Timer Select bits                                                                                                                                                                                        |

|           | <ul> <li>1 = TMR2 contents are captured on capture event</li> <li>0 = TMR3 contents are captured on capture event</li> </ul>                                                                                                  |

| bit 6-5   | ICI<1:0>: Select Number of Captures per Interrupt bits                                                                                                                                                                        |

|           | 11 = Interrupt on every fourth capture event                                                                                                                                                                                  |

|           | <ul> <li>10 = Interrupt on every third capture event</li> <li>01 = Interrupt on every second capture event</li> </ul>                                                                                                         |

|           | 00 = Interrupt on every capture event                                                                                                                                                                                         |

| bit 4     | ICOV: Input Capture Overflow Status Flag bit (read-only)                                                                                                                                                                      |

|           | 1 = Input capture overflow occurred                                                                                                                                                                                           |

|           | 0 = No input capture overflow occurred                                                                                                                                                                                        |

| bit 3     | ICBNE: Input Capture Buffer Empty Status bit (read-only)                                                                                                                                                                      |

|           | <ul> <li>1 = Input capture buffer is not empty, at least one more capture value can be read</li> <li>0 = Input capture buffer is empty</li> </ul>                                                                             |

| bit 2-0   | ICM<2:0>: Input Capture Mode Select bits                                                                                                                                                                                      |

|           | <ul> <li>111 = Input capture functions as interrupt pin only when device is in Sleep or Idle mode<br/>(Rising edge detect only, all other control bits are not applicable)</li> <li>110 = Unused (module disabled)</li> </ul> |

|           | 101 = Capture mode, every 16th rising edge                                                                                                                                                                                    |

|           | 100 = Capture mode, every 4th rising edge                                                                                                                                                                                     |

|           | 011 = Capture mode, every rising edge<br>010 = Capture mode, every falling edge                                                                                                                                               |

|           | 001 = Capture mode, every edge (rising and falling)                                                                                                                                                                           |

|           | (ICI<1:0> bits do not control interrupt generation for this mode)                                                                                                                                                             |

|           | 000 = Input capture module turned off                                                                                                                                                                                         |

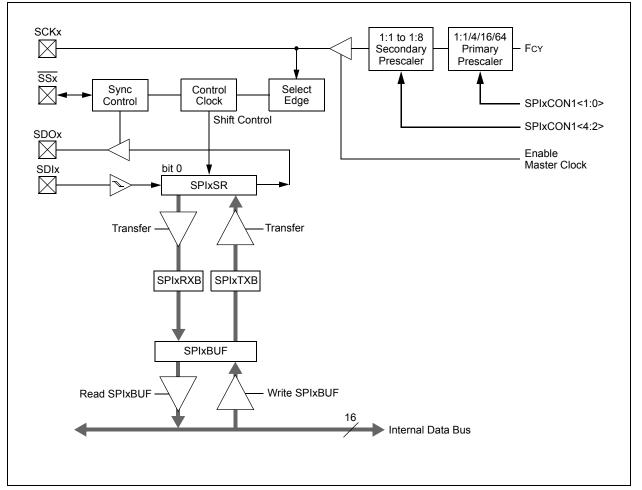

# 16.0 SERIAL PERIPHERAL INTERFACE (SPI)

- Note 1: This data sheet summarizes the features PIC24HJ32GP302/304, of the PIC24HJ64GPX02/X04 and PIC24HJ128GPX02/X04 families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 18. "Serial Peripheral Interface (SPI)" (DS70206) of the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Serial Peripheral Interface (SPI) module is a synchronous serial interface useful for communicating with other peripheral or microcontroller devices. These peripheral devices can be serial EEPROMs, shift registers, display drivers, analog-to-digital converters, etc. The SPI module is compatible with Motorola<sup>®</sup> SPI and SIOP.

Each SPI module consists of a 16-bit shift register, SPIxSR (where x = 1 or 2), used for shifting data in and out, and a buffer register, SPIxBUF. A control register, SPIxCON, configures the module. Additionally, a status register, SPIxSTAT, indicates status conditions.

The serial interface consists of 4 pins:

- · SDIx (serial data input)

- SDOx (serial data output)

- <u>SCKx</u> (shift clock input or output)

- SSx (active-low slave select)

In Master mode operation, SCK is a clock output. In Slave mode, it is a clock input.

#### FIGURE 16-1: SPI MODULE BLOCK DIAGRAM

# REGISTER 18-2: UxSTA: UARTx STATUS AND CONTROL REGISTER (CONTINUED)

| bit 5 | <b>ADDEN:</b> Address Character Detect bit (bit 8 of received data = 1)                                                                                                                                                     |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul> <li>1 = Address Detect mode enabled. If 9-bit mode is not selected, this does not take effect</li> <li>0 = Address Detect mode disabled</li> </ul>                                                                     |

| bit 4 | RIDLE: Receiver Idle bit (read-only)                                                                                                                                                                                        |

|       | <ul><li>1 = Receiver is Idle</li><li>0 = Receiver is active</li></ul>                                                                                                                                                       |

| bit 3 | PERR: Parity Error Status bit (read-only)                                                                                                                                                                                   |

|       | <ul> <li>1 = Parity error has been detected for the current character (character at the top of the receive FIFO)</li> <li>0 = Parity error has not been detected</li> </ul>                                                 |

| bit 2 | FERR: Framing Error Status bit (read-only)                                                                                                                                                                                  |

|       | 1 = Framing error has been detected for the current character (character at the top of the receive FIFO)                                                                                                                    |

|       | 0 = Framing error has not been detected                                                                                                                                                                                     |

| bit 1 | OERR: Receive Buffer Overrun Error Status bit (read/clear only)                                                                                                                                                             |

|       | <ul> <li>1 = Receive buffer has overflowed</li> <li>0 = Receive buffer has not overflowed. Clearing a previously set OERR bit (1 → 0 transition) resets<br/>the receiver buffer and the UxRSR to the empty state</li> </ul> |

| bit 0 | URXDA: Receive Buffer Data Available bit (read-only)                                                                                                                                                                        |

|       | <ul> <li>1 = Receive buffer has data, at least one more character can be read</li> <li>0 = Receive buffer is empty</li> </ul>                                                                                               |

|       |                                                                                                                                                                                                                             |

**Note 1:** Refer to **Section 17. "UART"** (DS70232) in the *"dsPIC33F/PIC24H Family Reference Manual"* for information on enabling the UART module for transmit operation.

# PIC24HJ32GP302/304, PIC24HJ64GPX02/X04 AND PIC24HJ128GPX02/X04

|                               |                                                                                                       | R/W-0                                                                                                                                        | U-0                                | U-0               | U-0               | U-0             | U-0   |

|-------------------------------|-------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|-------------------|-------------------|-----------------|-------|

|                               | DMABS<2:0>                                                                                            |                                                                                                                                              | —                                  | —                 | _                 | —               | —     |

| bit 15                        |                                                                                                       |                                                                                                                                              |                                    |                   |                   |                 | bit 8 |

| U-0                           | U-0                                                                                                   | U-0                                                                                                                                          | R/W-0                              | R/W-0             | R/W-0             | R/W-0           | R/W-0 |

| _                             | _                                                                                                     | _                                                                                                                                            |                                    |                   | FSA<4:0>          |                 |       |

| bit 7                         |                                                                                                       |                                                                                                                                              |                                    |                   |                   |                 | bit ( |

| Levende                       |                                                                                                       | C = M/rite able                                                                                                                              |                                    | 'O' oon ho writte | ve to close the l | .:4             |       |

| <b>Legend:</b><br>R = Readabl | a hit                                                                                                 | W = Writable                                                                                                                                 | •                                  | '0' can be writte |                   |                 |       |

| -n = Value at                 |                                                                                                       | '1' = Bit is set                                                                                                                             |                                    | 0 = Onimplen      | nented bit, read  | x = Bit is unkr |       |

|                               | FUR                                                                                                   |                                                                                                                                              |                                    |                   | aleu              |                 | IOWIT |

| bit 12-5                      | 101 = 24 buffe<br>100 = 16 buffe<br>011 = 12 buffe<br>010 = 8 buffe<br>001 = 6 buffe<br>000 = 4 buffe | ers in DMA RA<br>ers in DMA RA<br>ers in DMA RA<br>ers in DMA RA<br>rs in DMA RAN<br>rs in DMA RAN<br>rs in DMA RAN<br><b>ted:</b> Read as ' | AM<br>AM<br>AM<br>A<br>A<br>A<br>A |                   |                   |                 |       |

| bit 4-0                       | •                                                                                                     | FO Area Starts                                                                                                                               |                                    | oite              |                   |                 |       |

|                               | 11111 = Read<br>11110 = Read<br>•                                                                     | d buffer RB31                                                                                                                                |                                    | 5113              |                   |                 |       |

| R/W-0        | R/W-0       | R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-                       |                 |                             | R/W-0            | R/W-0           |         |  |  |  |

|--------------|-------------|----------------------------------------------------------|-----------------|-----------------------------|------------------|-----------------|---------|--|--|--|

| F15N         | /ISK<1:0>   | F14MS                                                    | F14MSK<1:0>     |                             | F13MSK<1:0>      |                 | SK<1:0> |  |  |  |

| bit 15       |             |                                                          |                 |                             |                  |                 | bit 8   |  |  |  |

|              |             |                                                          |                 |                             |                  |                 |         |  |  |  |

| R/W-0        | R/W-0       | R/W-0                                                    | R/W-0           | R/W-0                       | R/W-0            | R/W-0           | R/W-0   |  |  |  |

| F11M         | ISK<1:0>    | F10MS                                                    | K<1:0>          | F9MS                        | K<1:0>           | F8MS            | K<1:0>  |  |  |  |

| bit 7        |             |                                                          |                 |                             |                  |                 | bit 0   |  |  |  |

|              |             | 0                                                        | . 1. 1. 1       | 01                          |                  | . '1            |         |  |  |  |

| Legend:      |             |                                                          | •               | 0' can be writte            |                  |                 |         |  |  |  |

| R = Readab   |             | W = Writable bit                                         |                 | U = Unimplemented bit, read |                  |                 |         |  |  |  |

| -n = Value a | t POR       | '1' = Bit is set                                         |                 | '0' = Bit is cle            | ared             | x = Bit is unkr | nown    |  |  |  |

| bit 15-14    | F15MSK<1.   | <b>n&gt;:</b> Mask Sourc                                 | e for Filter 15 | bit                         |                  |                 |         |  |  |  |

|              |             | 15MSK<1:0>: Mask Source for Filter 15 bit<br>1 = No mask |                 |                             |                  |                 |         |  |  |  |

|              | 10 = Accept | 10 = Acceptance Mask 2 registers contain mask            |                 |                             |                  |                 |         |  |  |  |

|              | 01 = Accept | 01 = Acceptance Mask 1 registers contain mask            |                 |                             |                  |                 |         |  |  |  |

|              | 00 = Accept | ance Mask 0 re                                           | gisters contair | n mask                      |                  |                 |         |  |  |  |

| bit 13-12    | F14MSK<1:   | 0>: Mask Source                                          | e for Filter 14 | bit (same value             | es as bit 15-14  | )               |         |  |  |  |

| bit 11-10    | F13MSK<1:   | 0>: Mask Sourc                                           | e for Filter 13 | bit (same value             | es as bit 15-14  | )               |         |  |  |  |

| bit 9-8      | F12MSK<1:   | 0>: Mask Sourc                                           | e for Filter 12 | bit (same value             | es as bit 15-14  | )               |         |  |  |  |

| bit 7-6      | F11MSK<1:   | 0>: Mask Sourc                                           | e for Filter 11 | bit (same value             | es as bit 15-14) | )               |         |  |  |  |

| bit 5-4      | F10MSK<1:   | 0>: Mask Sourc                                           | e for Filter 10 | bit (same value             | es as bit 15-14  | )               |         |  |  |  |

| bit 3-2      | F9MSK<1:0   | >: Mask Source                                           | for Filter 9 bi | t (same values              | as bit 15-14)    |                 |         |  |  |  |

|              |             |                                                          |                 |                             |                  |                 |         |  |  |  |

# REGISTER 19-19: CiFMSKSEL2: ECAN™ FILTER 15-8 MASK SELECTION REGISTER

bit 1-0 **F8MSK<1:0>:** Mask Source for Filter 8 bit (same values as bit 15-14)

# 22.3 RTCC Registers

| (*)                  | U-0                                                                                                                                | R/W-0                                                                                | R-0            | R-0                                   | R/W-0           | R/W-0            | R/W-0         |  |  |

|----------------------|------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|----------------|---------------------------------------|-----------------|------------------|---------------|--|--|

| RTCEN <sup>(2)</sup> |                                                                                                                                    | RTCWREN                                                                              | RTCSYNC        | HALFSEC <sup>(3)</sup>                | RTCOE           | RTCPT            | R<1:0>        |  |  |

| bit 15               |                                                                                                                                    |                                                                                      |                |                                       |                 |                  | bit           |  |  |

| R/W-0                | R/W-0                                                                                                                              | R/W-0                                                                                | R/W-0          | R/W-0                                 | R/W-0           | R/W-0            | R/W-0         |  |  |

|                      |                                                                                                                                    |                                                                                      | CAL            | <7:0>                                 |                 |                  |               |  |  |

| bit 7                |                                                                                                                                    |                                                                                      |                |                                       |                 |                  | bit           |  |  |

| Legend:              |                                                                                                                                    |                                                                                      |                |                                       |                 |                  |               |  |  |

| R = Readable         | e bit                                                                                                                              | W = Writable                                                                         | bit            | U = Unimplem                          | ented bit, read | as '0'           |               |  |  |

| -n = Value at        | POR                                                                                                                                | '1' = Bit is set                                                                     |                | '0' = Bit is clea                     | red             | x = Bit is unkn  | own           |  |  |

| bit 15               |                                                                                                                                    | CC Enable bit <sup>(2)</sup>                                                         |                |                                       |                 |                  |               |  |  |

| DIL 15               |                                                                                                                                    | nodule is enable                                                                     |                |                                       |                 |                  |               |  |  |

|                      |                                                                                                                                    | nodule is disable                                                                    |                |                                       |                 |                  |               |  |  |

| bit 14               | Unimpleme                                                                                                                          | nted: Read as '                                                                      | 0'             |                                       |                 |                  |               |  |  |

| bit 13               | -                                                                                                                                  | RTCC Value Re                                                                        |                | Enable bit                            |                 |                  |               |  |  |

|                      |                                                                                                                                    |                                                                                      | •              | in be written to b                    | by the user     |                  |               |  |  |

|                      | 0 = RTCVAL                                                                                                                         | _H and RTCVAL                                                                        | L registers ar | e locked out from                     | m being writter | n to by the user |               |  |  |

| bit 12               | RTCSYNC:                                                                                                                           | RTCSYNC: RTCC Value Registers Read Synchronization bit                               |                |                                       |                 |                  |               |  |  |

|                      | 1 = RTCVALH, RTCVALL and ALCFGRPT registers can change while reading due to a rollover ripple                                      |                                                                                      |                |                                       |                 |                  |               |  |  |

|                      | resulting in an invalid data read. If the register is read twice and results in the same data, the data can be assumed to be valid |                                                                                      |                |                                       |                 |                  |               |  |  |

|                      |                                                                                                                                    |                                                                                      |                | registers can be                      | e read without  | concern over a   | rollover rinn |  |  |

| bit 11               |                                                                                                                                    |                                                                                      |                |                                       |                 |                  |               |  |  |

|                      |                                                                                                                                    | HALFSEC: Half-Second Status bit <sup>(3)</sup><br>1 = Second half period of a second |                |                                       |                 |                  |               |  |  |

|                      |                                                                                                                                    | f period of a sec                                                                    |                |                                       |                 |                  |               |  |  |

| bit 10               | RTCOE: RT                                                                                                                          | CC Output Enat                                                                       | ole bit        |                                       |                 |                  |               |  |  |

|                      | 1 = RTCC output enabled                                                                                                            |                                                                                      |                |                                       |                 |                  |               |  |  |

|                      | 0 = RTCC o                                                                                                                         | utput disabled                                                                       |                |                                       |                 |                  |               |  |  |

| bit 9-8              |                                                                                                                                    |                                                                                      | •              | ndow Pointer bit                      |                 |                  |               |  |  |

|                      |                                                                                                                                    | • •                                                                                  |                | registers when r<br>every read or wri | •               |                  | •             |  |  |

|                      | RTCVAL<15                                                                                                                          |                                                                                      |                |                                       |                 |                  |               |  |  |

|                      | 11 = Reserved                                                                                                                      |                                                                                      |                |                                       |                 |                  |               |  |  |

|                      | 10 = MONTH<br>01 = WEEKDAY                                                                                                         |                                                                                      |                |                                       |                 |                  |               |  |  |

|                      |                                                                                                                                    |                                                                                      |                |                                       |                 |                  |               |  |  |

|                      | 00 <b>= MINUT</b>                                                                                                                  |                                                                                      |                |                                       |                 |                  |               |  |  |

|                      | 00 <b>= MINUT</b><br><u>RTCVAL&lt;7:0</u>                                                                                          | ES                                                                                   |                |                                       |                 |                  |               |  |  |

|                      | <u>RTCVAL&lt;7:(</u><br>11 <b>= YEAR</b>                                                                                           | ES                                                                                   |                |                                       |                 |                  |               |  |  |

|                      | RTCVAL<7:0                                                                                                                         | ES<br>)>:                                                                            |                |                                       |                 |                  |               |  |  |

# REGISTER 22-1: RCFGCAL: RTCC CALIBRATION AND CONFIGURATION REGISTER<sup>(1)</sup>

- 2: A write to the RTCEN bit is only allowed when RTCWREN = 1.

- **3:** This bit is read-only. It is cleared to '0' on a write to the lower half of the MINSEC register.

# **REGISTER 22-4: RTCVAL (WHEN RTCPTR<1:0> = 11): YEAR VALUE REGISTER<sup>(1)</sup>**

| U-0                                | U-0   | U-0            | U-0   | U-0                                     | U-0   | U-0   | U-0   |  |

|------------------------------------|-------|----------------|-------|-----------------------------------------|-------|-------|-------|--|

| —                                  | —     | —              | _     | —                                       | —     | —     |       |  |

| bit 15                             |       |                |       |                                         |       |       | bit 8 |  |

|                                    |       |                |       |                                         |       |       |       |  |

| R/W-x                              | R/W-x | R/W-x          | R/W-x | R/W-x                                   | R/W-x | R/W-x | R/W-x |  |

|                                    | YRTEN | <b>\</b> <3:0> |       | YRONE<3:0>                              |       |       |       |  |

| bit 7                              |       |                |       | •                                       |       |       | bit 0 |  |

|                                    |       |                |       |                                         |       |       |       |  |

| Legend:                            |       |                |       |                                         |       |       |       |  |

| R = Readable bit W = Writable bit  |       |                |       | U = Unimplemented bit, read as '0'      |       |       |       |  |

| -n = Value at POR '1' = Bit is set |       |                |       | '0' = Bit is cleared x = Bit is unknown |       |       |       |  |

|                                    |       |                |       |                                         |       |       |       |  |

bit 15-8 Unimplemented: Read as '0'