Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 40 MIPs                                                                        |

| Connectivity               | I <sup>2</sup> C, PMP, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                     |

| Number of I/O              | 21                                                                             |

| Program Memory Size        | 64KB (22K x 24)                                                                |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 8K x 8                                                                         |

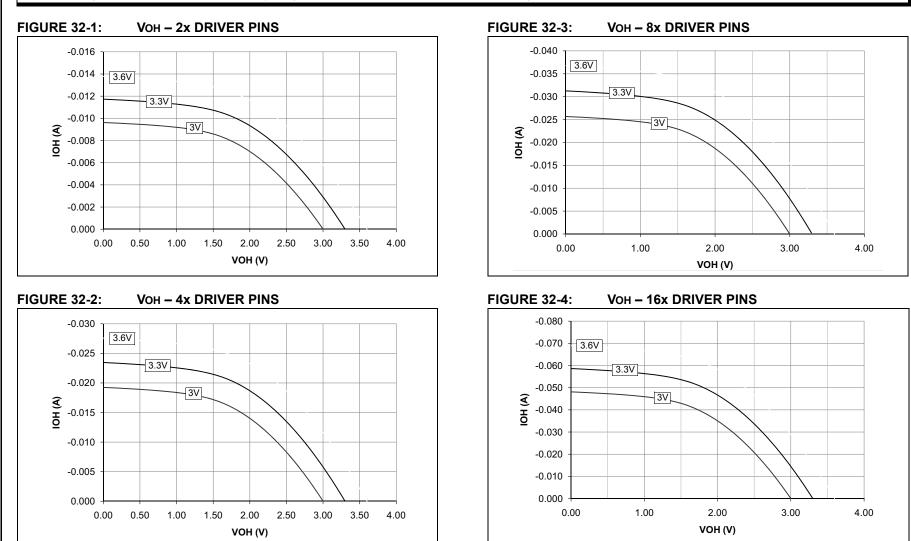

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                      |

| Data Converters            | A/D 10x10b/12b                                                                 |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 28-VQFN Exposed Pad                                                            |

| Supplier Device Package    | 28-QFN-S (6x6)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24hj64gp202t-i-mm |

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 4.0 MEMORY ORGANIZATION

| Note: | This data sheet summarizes the features      |

|-------|----------------------------------------------|

|       | of the PIC24HJ32GP302/304,                   |

|       | PIC24HJ64GPX02/X04 and                       |

|       | PIC24HJ128GPX02/X04 families of              |

|       | devices. It is not intended to be a compre-  |

|       | hensive reference source. To complement      |

|       | the information in this data sheet, refer to |

|       | Section 4. "Program Memory"                  |

|       | (DS70203) of the "dsPIC33F/PIC24H            |

|       | Family Reference Manual", which is avail-    |

|       | able from the Microchip web site             |

|       | (www.microchip.com).                         |

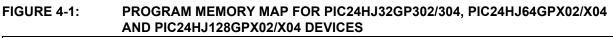

The PIC24HJ32GP302/304, PIC24HJ64GPX02/X04 and PIC24HJ128GPX02/X04 architecture features separate program and data memory spaces and buses. This architecture also allows the direct access of program memory from the data space during code execution.

#### 4.1 Program Address Space

The program address memory space of the PIC24HJ32GP302/304, PIC24HJ64GPX02/X04 and PIC24HJ128GPX02/X04 devices is 4M instructions. The space is addressable by a 24-bit value derived either from the 23-bit Program Counter (PC) during program execution, or from table operation or data space remapping as described in Section 4.6 "Interfacing Program and Data Memory Spaces".

User application access to the program memory space is restricted to the lower half of the address range (0x000000 to 0x7FFFFF). The exception is the use of TBLRD/TBLWT operations, which use TBLPAG<7> to permit access to the Configuration bits and Device ID sections of the configuration memory space.

The memory map for the PIC24HJ32GP302/304, PIC24HJ64GPX02/X04 and PIC24HJ128GPX02/X04 devices is shown in Figure 4-1.

|      | PIC24HJ32GP302/304                                   | PIC24HJ64GPX02/X04                | PIC24HJ128GPX02/X04                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|------|------------------------------------------------------|-----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4    | GOTO Instruction                                     | GOTO Instruction                  | GOTO Instruction 0x000000<br>Reset Address 0x000002                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|      | Reset Address                                        | Reset Address                     | 0x000004                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|      | Interrupt Vector Table                               | Interrupt Vector Table            | Interrupt Vector Table 0x0000FE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|      | Reserved                                             | Reserved                          | <u>Reserved</u> 0x000100<br>0x000104                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|      | Alternate Vector Table                               | Alternate Vector Table            | Alternate vector rable 0x0001FE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 2000 | User Program<br>Flash Memory<br>(11264 instructions) | User Program<br>Flash Memory      | 0x000200<br>0x0057FE<br>0x0057FE<br>0x005800                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|      | Unimplemented                                        |                                   | User Program<br>Flash Memory<br>(44032 instructions)<br>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|      | (Read '0's)                                          | Unimplemented                     | 0x0157FE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|      |                                                      | (Read '0's)                       | 0x015800                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|      |                                                      |                                   | Unimplemented<br>(Read '0's)<br>0x7FFFE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|      | Reserved                                             | Reserved                          | 0x800000<br>Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|      | Device Configuration<br>Registers                    | Device Configuration<br>Registers | Device Configuration 0xF7FFE<br>Device Configuration 0xF80000<br>Registers 0xF80017                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|      | Reserved                                             | Reserved                          | Care Control C |

| 0    |                                                      |                                   | DEVID (2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|      | Reserved                                             | Reserved                          | 0xFF0002           Reserved           0xFFFFE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| TABLE       | 4-4:        | INTER  |        | ONTRO       | LLER R | EGISTER | R MAP  |            |                     |       |                       |             |         |                     |                       |            |         |               |

|-------------|-------------|--------|--------|-------------|--------|---------|--------|------------|---------------------|-------|-----------------------|-------------|---------|---------------------|-----------------------|------------|---------|---------------|

| SFR<br>Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13      | Bit 12 | Bit 11  | Bit 10 | Bit 9      | Bit 8               | Bit 7 | Bit 6                 | Bit 5       | Bit 4   | Bit 3               | Bit 2                 | Bit 1      | Bit 0   | All<br>Resets |

| INTCON1     | 0080        | NSTDIS | —      | —           | _      |         | _      | —          | _                   | _     | DIV0ERR               | DMACERR     | MATHERR | ADDRERR             | STKERR                | OSCFAIL    | -       | 0000          |

| INTCON2     | 0082        | ALTIVT | DISI   |             |        | _       |        | _          | _                   | _     | _                     |             |         | _                   | INT2EP                | INT1EP     | INT0EP  | 0000          |

| IFS0        | 0084        | _      | DMA1IF | AD1IF       | U1TXIF | U1RXIF  | SPI1IF | SPI1EIF    | T3IF                | T2IF  | OC2IF                 | IC2IF       | DMA0IF  | T1IF                | OC1IF                 | IC1IF      | INT0IF  | 0000          |

| IFS1        | 0086        | U2TXIF | U2RXIF | INT2IF      | T5IF   | T4IF    | OC4IF  | OC3IF      | DMA2IF              | IC8IF | IC7IF                 | _           | INT1IF  | CNIF                | CMIF                  | MI2C1IF    | SI2C1IF | 0000          |

| IFS2        | 0088        | _      | DMA4IF | PMPIF       | _      | _       | _      | _          | _                   | _     | _                     | _           | DMA3IF  | C1IF <sup>(1)</sup> | C1RXIF <sup>(1)</sup> | SPI2IF     | SPI2EIF | 0000          |

| IFS3        | 008A        | _      | RTCIF  | DMA5IF      | _      | _       | _      | —          | _                   | _     | —                     | _           | _       | —                   | _                     | _          | _       | 0000          |

| IFS4        | 008C        | _      | _      | _           | _      | —       | _      | —          | —                   | _     | C1TXIF <sup>(1)</sup> | DMA7IF      | DMA6IF  | CRCIF               | U2EIF                 | U1EIF      | _       | 0000          |

| IEC0        | 0094        | _      | DMA1IE | AD1IE       | U1TXIE | U1RXIE  | SPI1IE | SPI1EIE    | T3IE                | T2IE  | OC2IE                 | IC2IE       | DMA0IE  | T1IE                | OC1IE                 | IC1IE      | INT0IE  | 0000          |

| IEC1        | 0096        | U2TXIE | U2RXIE | INT2IE      | T5IE   | T4IE    | OC4IE  | OC3IE      | DMA2IE              | IC8IE | IC7IE                 | _           | INT1IE  | CNIE                | CMIE                  | MI2C1IE    | SI2C1IE | 0000          |

| IEC2        | 0098        | _      | DMA4IE | PMPIE       | _      | _       | _      | _          | _                   | _     | _                     | _           | DMA3IE  | C1IE <sup>(1)</sup> | C1RXIE <sup>(1)</sup> | SPI2IE     | SPI2EIE | 0000          |

| IEC3        | 009A        | _      | RTCIE  | DMA5IE      | _      | _       | _      | _          | _                   | _     | _                     | _           | _       | _                   | _                     | _          | _       | 0000          |

| IEC4        | 009C        | _      | _      | _           | _      | _       | _      | _          | _                   | _     | C1TXIE <sup>(1)</sup> | DMA7IE      | DMA6IE  | CRCIE               | U2EIE                 | U1EIE      | _       | 0000          |

| IPC0        | 00A4        | _      |        | T1IP<2:0>   |        | _       | (      | OC1IP<2:0  | >                   | _     |                       | IC1IP<2:0>  |         | _                   | IN                    | IT0IP<2:0> |         | 4444          |

| IPC1        | 00A6        | —      |        | T2IP<2:0>   |        |         | (      | OC2IP<2:0  | >                   | —     |                       | IC2IP<2:0>  |         | —                   | DN                    | /A0IP<2:0  | >       | 4444          |

| IPC2        | 00A8        | _      | U      | 1RXIP<2:0   | >      | _       | Ş      | SPI1IP<2:0 | >                   | _     | :                     | SPI1EIP<2:0 | >       | _                   | ٦                     | [31P<2:0>  |         | 4444          |

| IPC3        | 00AA        | _      | _      | _           | _      | _       | D      | MA1IP<2:   | )>                  | _     |                       | AD1IP<2:0>  |         | _                   | U                     | 1TXIP<2:0> | >       | 0444          |

| IPC4        | 00AC        | _      | (      | CNIP<2:0>   |        | _       |        | CMIP<2:0   | <b>`</b>            | _     | I                     | MI2C1IP<2:0 | >       | _                   | SI                    | 2C1IP<2:0  | >       | 4444          |

| IPC5        | 00AE        | _      | I      | C8IP<2:0>   |        | _       |        | IC7IP<2:0  | <b>`</b>            | _     | _                     | _           | _       | _                   | IN                    | IT1IP<2:0> |         | 4404          |

| IPC6        | 00B0        | —      |        | T4IP<2:0>   |        |         | (      | OC4IP<2:0  | >                   | —     |                       | OC3IP<2:0>  |         | —                   | DN                    | /A2IP<2:0  | >       | 4444          |

| IPC7        | 00B2        | —      | U      | 2TXIP<2:0>  | >      |         | L      | J2RXIP<2:( | )>                  | —     |                       | INT2IP<2:0> | •       | —                   | ٦                     | [5IP<2:0>  |         | 4444          |

| IPC8        | 00B4        | —      | С      | 1IP<2:0>(1) | )      |         | C,     | 1RXIP<2:0  | <sub>&gt;</sub> (1) | —     |                       | SPI2IP<2:0> | •       | —                   | SF                    | PI2EIP<2:0 | >       | 4444          |

| IPC9        | 00B6        | —      | —      |             |        |         | —      | —          |                     | —     | —                     |             |         | —                   | DN                    | /A3IP<2:0  | >       | 0004          |

| IPC11       | 00BA        | —      | —      |             |        |         | D      | MA4IP<2:   | )>                  | —     |                       | PMPIP<2:0>  | •       | —                   | —                     | —          | _       | 0440          |

| IPC15       | 00C2        | —      | _      | —           |        |         |        | RTCIP<2:0  | >                   | —     |                       | DMA5IP<2:0  | >       | -                   | _                     | _          | —       | 0440          |

| IPC16       | 00C4        | —      | С      | RCIP<2:0>   |        |         |        | U2EIP<2:0  | >                   | —     |                       | U1EIP<2:0>  |         | -                   | _                     | —          | —       | 4440          |

| IPC17       | 00C6        | —      | _      | —           |        |         | C      | 1TXIP<2:0  | <b>(</b> 1)         | —     |                       | DMA7IP<2:0  | >       | -                   | DN                    | /A6IP<2:0  | >       | 0444          |

| INTTREG     | 00E0        | —      | _      | —           |        |         | ILR<   | 3:0>       |                     | —     |                       |             | VEC     | CNUM<6:0>           |                       |            |         | 4444          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: Interrupts disabled on devices without ECAN™ modules.

#### TABLE 4-7: OUTPUT COMPARE REGISTER MAP

|          |             |        |            |        |          |            |            |             |             |             |              |       |       |        |       |          |       | -             |

|----------|-------------|--------|------------|--------|----------|------------|------------|-------------|-------------|-------------|--------------|-------|-------|--------|-------|----------|-------|---------------|

| SFR Name | SFR<br>Addr | Bit 15 | Bit 14     | Bit 13 | Bit 12   | Bit 11     | Bit 10     | Bit 9       | Bit 8       | Bit 7       | Bit 6        | Bit 5 | Bit 4 | Bit 3  | Bit 2 | Bit 1    | Bit 0 | All<br>Resets |

| OC1RS    | 0180        |        |            |        |          |            |            | Ou          | tput Compar | e 1 Seconda | ary Register |       |       |        |       |          |       | xxxx          |

| OC1R     | 0182        |        |            |        |          |            |            |             | Output Co   | ompare 1 Re | gister       |       |       |        |       |          |       | XXXX          |

| OC1CON   | 0184        | _      | _          | OCSIDL | _        | _          |            | _           | —           | _           | _            | _     | OCFLT | OCTSEL |       | OCM<2:0> |       | 0000          |

| OC2RS    | 0186        |        |            |        |          |            |            | Ou          | tput Compar | e 2 Seconda | ary Register |       |       |        |       |          |       | XXXX          |

| OC2R     | 0188        |        |            |        |          |            |            |             | Output Co   | ompare 2 Re | gister       |       |       |        |       |          |       | XXXX          |

| OC2CON   | 018A        | _      | _          | OCSIDL | _        | _          |            | _           | —           | _           | _            | _     | OCFLT | OCTSEL |       | OCM<2:0> |       | 0000          |

| OC3RS    | 018C        |        |            |        |          |            |            | Ou          | tput Compar | e 3 Seconda | ary Register |       |       |        |       |          |       | XXXX          |

| OC3R     | 018E        |        |            |        |          |            |            |             | Output Co   | ompare 3 Re | gister       |       |       |        |       |          |       | XXXX          |

| OC3CON   | 0190        | _      | _          | OCSIDL | _        | _          |            | _           | —           | _           | _            | _     | OCFLT | OCTSEL |       | OCM<2:0> |       | 0000          |

| OC4RS    | 0192        |        |            |        |          |            |            | Ou          | tput Compar | e 4 Seconda | ary Register |       |       |        |       |          |       | XXXX          |

| OC4R     | 0194        |        |            |        |          |            |            |             | Output Co   | ompare 4 Re | gister       |       |       |        |       |          |       | XXXX          |

| OC4CON   | 0196        | _      | _          | OCSIDL | _        | _          | _          | _           | _           | _           | _            | _     | OCFLT | OCTSEL |       | OCM<2:0> |       | 0000          |

| l edend. | v = unk     |        | o on Posot | = unim | lomontod | road as '0 | ' Posot va | luce are ch | own in hove | docimal     |              |       |       | •      | •     |          |       |               |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-8: I2C1 REGISTER MAP

| SFR Name | SFR<br>Addr | Bit 15  | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8 | Bit 7 | Bit 6 | Bit 5      | Bit 4        | Bit 3      | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|----------|-------------|---------|--------|---------|--------|--------|--------|--------|-------|-------|-------|------------|--------------|------------|-------|-------|-------|---------------|

| I2C1RCV  | 0200        | _       | _      | -       | _      | _      | -      | -      | _     |       |       |            | Receive      | Register   |       |       |       | 0000          |

| I2C1TRN  | 0202        | _       | _      | _       | _      | _      | _      | _      | _     |       |       |            | Transmit     | Register   |       |       |       | OOFF          |

| I2C1BRG  | 0204        | _       | _      | _       | _      | _      | _      | _      |       |       |       | Baud Rat   | e Generato   | r Register |       |       |       | 0000          |

| I2C1CON  | 0206        | I2CEN   | _      | I2CSIDL | SCLREL | IPMIEN | A10M   | DISSLW | SMEN  | GCEN  | STREN | ACKDT      | ACKEN        | RCEN       | PEN   | RSEN  | SEN   | 1000          |

| I2C1STAT | 0208        | ACKSTAT | TRSTAT | _       | _      | _      | BCL    | GCSTAT | ADD10 | IWCOL | I2COV | D_A        | Р            | S          | R_W   | RBF   | TBF   | 0000          |

| I2C1ADD  | 020A        | _       | _      | _       | _      | _      | _      |        |       |       |       | Address    | Register     |            |       |       |       | 0000          |

| I2C1MSK  | 020C        | _       | _      | _       | _      | _      | -      |        |       |       |       | Address Ma | isk Register |            |       |       |       | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-9: UART1 REGISTER MAP

| SFR Name | SFR<br>Addr | Bit 15   | Bit 14 | Bit 13   | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8      | Bit 7        | Bit 6   | Bit 5 | Bit 4       | Bit 3        | Bit 2 | Bit 1  | Bit 0 | All<br>Resets |

|----------|-------------|----------|--------|----------|--------|--------|--------|-------|------------|--------------|---------|-------|-------------|--------------|-------|--------|-------|---------------|

| U1MODE   | 0220        | UARTEN   | _      | USIDL    | IREN   | RTSMD  | _      | UEN1  | UEN0       | WAKE         | LPBACK  | ABAUD | URXINV      | BRGH         | PDSEI | _<1:0> | STSEL | 0000          |

| U1STA    | 0222        | UTXISEL1 | UTXINV | UTXISEL0 | -      | UTXBRK | UTXEN  | UTXBF | TRMT       | URXISE       | EL<1:0> | ADDEN | RIDLE       | PERR         | FERR  | OERR   | URXDA | 0110          |

| U1TXREG  | 0224        | _        | _      | _        | _      | _      | —      | _     | UTX8       |              |         | U     | ART Transm  | nit Register |       |        |       | XXXX          |

| U1RXREG  | 0226        | _        | _      | _        | _      | _      | _      | _     | URX8       |              |         | U     | ART Receive | ed Register  |       |        |       | 0000          |

| U1BRG    | 0228        |          |        |          |        |        |        | Bau   | d Rate Ger | erator Presc | aler    |       |             |              |       |        |       | 0000          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-13: ADC1 REGISTER MAP FOR PIC24HJ64GP202/502, PIC24HJ128GP202/502 AND PIC24HJ32GP302

| File Name | Addr | Bit 15 | Bit 14   | Bit 13 | Bit 12  | Bit 11 | Bit 10   | Bit 9   | Bit 8   | Bit 7       | Bit 6     | Bit 5 | Bit 4 | Bit 3  | Bit 2    | Bit 1    | Bit 0   | All<br>Resets |

|-----------|------|--------|----------|--------|---------|--------|----------|---------|---------|-------------|-----------|-------|-------|--------|----------|----------|---------|---------------|

| ADC1BUF0  | 0300 |        |          |        |         |        |          |         | ADC Da  | ta Buffer 0 |           |       |       |        |          |          |         | XXXX          |

| AD1CON1   | 0320 | ADON   | _        | ADSIDL | ADDMABM | —      | AD12B    | FOR     | M<1:0>  | ;           | SSRC<2:0> |       | —     | SIMSAM | ASAM     | SAMP     | DONE    | 0000          |

| AD1CON2   | 0322 | V      | 'CFG<2:0 | >      | _       | _      | CSCNA    | CHP     | S<1:0>  | BUFS        | _         |       | SMPI  | <3:0>  |          | BUFM     | ALTS    | 0000          |

| AD1CON3   | 0324 | ADRC   | _        | _      |         | S      | AMC<4:0> |         |         |             |           |       | ADCS  | <7:0>  |          |          |         | 0000          |

| AD1CHS123 | 0326 | _      | _        | _      | _       | _      | CH123N   | NB<1:0> | CH123SB | _           | _         | _     | _     | _      | CH123N   | VA<1:0>  | CH123SA | 0000          |

| AD1CHS0   | 0328 | CH0NB  | _        | _      |         | C      | H0SB<4:0 | >       |         | CH0NA       | _         | _     |       | С      | H0SA<4:0 | >        |         | 0000          |

| AD1PCFGL  | 032C | _      | _        | _      | PCFG12  | PCFG11 | PCFG10   | PCFG9   | _       | _           | _         | PCFG5 | PCFG4 | PCFG3  | PCFG2    | PCFG1    | PCFG0   | 0000          |

| AD1CSSL   | 0330 | —      | _        | —      | CSS12   | CSS11  | CSS10    | CSS9    | —       | —           | _         | CSS5  | CSS4  | CSS3   | CSS2     | CSS1     | CSS0    | 0000          |

| AD1CON4   | 0332 | _      |          |        | _       | —      | -        |         | _       |             | _         | _     |       | _      | [        | DMABL<2: | 0>      | 0000          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-14: ADC1 REGISTER MAP FOR PIC24HJ64GP204/504, PIC24HJ128GP204/504 AND PIC24HJ32GP304

| File Name | Addr | Bit 15 | Bit 14   | Bit 13 | Bit 12  | Bit 11 | Bit 10    | Bit 9   | Bit 8   | Bit 7        | Bit 6     | Bit 5 | Bit 4 | Bit 3  | Bit 2    | Bit 1    | Bit 0   | All<br>Resets |

|-----------|------|--------|----------|--------|---------|--------|-----------|---------|---------|--------------|-----------|-------|-------|--------|----------|----------|---------|---------------|

| ADC1BUF0  | 0300 |        |          |        |         |        |           |         | ADC Da  | ata Buffer 0 |           |       |       |        |          |          |         | xxxx          |

| AD1CON1   | 0320 | ADON   | —        | ADSIDL | ADDMABM | —      | AD12B     | FOR     | M<1:0>  | :            | SSRC<2:0> |       | —     | SIMSAM | ASAM     | SAMP     | DONE    | 0000          |

| AD1CON2   | 0322 | V      | 'CFG<2:0 | >      | _       | _      | CSCNA     | CHP     | S<1:0>  | BUFS         | _         |       | SMP   | <3:0>  |          | BUFM     | ALTS    | 0000          |

| AD1CON3   | 0324 | ADRC   | _        | _      |         | S      | AMC<4:0>  |         |         |              |           |       | ADCS  | <7:0>  |          |          |         | 0000          |

| AD1CHS123 | 0326 | _      | _        | _      | _       | _      | CH123N    | IB<1:0> | CH123SB | _            | _         | _     | _     | _      | CH123    | NA<1:0>  | CH123SA | 0000          |

| AD1CHS0   | 0328 | CH0NB  | _        | _      |         | C      | +0SB<4:0> | •       |         | CH0NA        | _         | _     |       | С      | H0SA<4:0 | >        |         | 0000          |

| AD1PCFGL  | 032C | _      | _        | _      | PCFG12  | PCFG11 | PCFG10    | PCFG9   | PCFG8   | PCFG7        | PCFG6     | PCFG5 | PCFG4 | PCFG3  | PCFG2    | PCFG1    | PCFG0   | 0000          |

| AD1CSSL   | 0330 | _      | _        | _      | CSS12   | CSS11  | CSS10     | CSS9    | CSS8    | CSS7         | CSS6      | CSS5  | CSS4  | CSS3   | CSS2     | CSS1     | CSS0    | 0000          |

| AD1CON4   | 0332 | _      |          | _      | _       |        | _         | _       | _       | _            | _         | _     |       | _      | I        | DMABL<2: | 0>      | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### 5.6.1 PROGRAMMING ALGORITHM FOR FLASH PROGRAM MEMORY

Programmers can program one row of program Flash memory at a time. To do this, it is necessary to erase the 8-row erase page that contains the desired row. The general process is:

- 1. Read eight rows of program memory (512 instructions) and store in data RAM.

- 2. Update the program data in RAM with the desired new data.

- 3. Erase the block (see Example 5-1):

- a) Set the NVMOP bits (NVMCON<3:0>) to <sup>(0010)</sup> to configure for block erase. Set the ERASE (NVMCON<6>) and WREN (NVMCON<14>) bits.

- b) Write the starting address of the page to be erased into the TBLPAG and W registers.

- c) Write 0x55 to NVMKEY.

- d) Write 0xAA to NVMKEY.

- e) Set the WR bit (NVMCON<15>). The erase cycle begins and the CPU stalls for the duration of the erase cycle. When the erase is done, the WR bit is cleared automatically.

- 4. Write the first 64 instructions from data RAM into the program memory buffers (see Example 5-2).

- 5. Write the program block to Flash memory:

- a) Set the NVMOP bits to '0001' to configure for row programming. Clear the ERASE bit and set the WREN bit.

- b) Write 0x55 to NVMKEY.

- c) Write 0xAA to NVMKEY.

- d) Set the WR bit. The programming cycle begins and the CPU stalls for the duration of the write cycle. When the write to Flash memory is done, the WR bit is cleared automatically.

- Repeat steps 4 and 5, using the next available 64 instructions from the block in data RAM by incrementing the value in TBLPAG, until all 512 instructions are written back to Flash memory.

For protection against accidental operations, the write initiate sequence for NVMKEY must be used to allow any erase or program operation to proceed. After the programming command has been executed, the user application must wait for the programming time until programming is complete. The two instructions following the start of the programming sequence should be NOPS, as shown in Example 5-3.

#### EXAMPLE 5-1: ERASING A PROGRAM MEMORY PAGE

| ; Set up NVMCON for block erase  | operation                                       |

|----------------------------------|-------------------------------------------------|

| MOV #0x4042, W0                  | ;                                               |

| MOV W0, NVMCON                   | ; Initialize NVMCON                             |

| ; Init pointer to row to be ERAS | SED                                             |

| MOV #tblpage(PROG_ADI            | DR), WO ;                                       |

| MOV W0, TBLPAG                   | ; Initialize PM Page Boundary SFR               |

| MOV #tbloffset(PROG_A            | ADDR), W0 ; Initialize in-page EA[15:0] pointer |

| TBLWTL W0, [W0]                  | ; Set base address of erase block               |

| DISI #5                          | ; Block all interrupts with priority <7         |

|                                  | ; for next 5 instructions                       |

| MOV #0x55, W0                    |                                                 |

| MOV W0, NVMKEY                   | ; Write the 55 key                              |

| MOV #0xAA, W1                    | ;                                               |

| MOV W1, NVMKEY                   | ; Write the AA key                              |

| BSET NVMCON, #WR                 | ; Start the erase sequence                      |

| NOP                              | ; Insert two NOPs after the erase               |

| NOP                              | ; command is asserted                           |

| NOP                              | ; COMMANA IS ASSETTED                           |

| U-0                              | R/W-0                                                                                                                                                                                                                                                                                   | R/W-0                                                                                                                                                                                             | U-0                                                                                                                                                                           | U-0                                   | U-0                   | U-0    | U-0                                            |  |  |  |  |  |  |  |

|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|-----------------------|--------|------------------------------------------------|--|--|--|--|--|--|--|

|                                  | DMA4IF                                                                                                                                                                                                                                                                                  | PMPIF                                                                                                                                                                                             |                                                                                                                                                                               |                                       |                       |        |                                                |  |  |  |  |  |  |  |

| <br>bit 15                       | DWAHI                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                   |                                                                                                                                                                               |                                       |                       |        | bit                                            |  |  |  |  |  |  |  |

| bit 10                           |                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                   |                                                                                                                                                                               |                                       |                       |        | Dit                                            |  |  |  |  |  |  |  |

| U-0                              | U-0                                                                                                                                                                                                                                                                                     | U-0                                                                                                                                                                                               | R/W-0                                                                                                                                                                         | R/W-0                                 | R/W-0                 | R/W-0  | R/W-0                                          |  |  |  |  |  |  |  |

| _                                | _                                                                                                                                                                                                                                                                                       | _                                                                                                                                                                                                 | DMA3IF                                                                                                                                                                        | C1IF <sup>(1)</sup>                   | C1RXIF <sup>(1)</sup> | SPI2IF | SPI2EIF                                        |  |  |  |  |  |  |  |

| bit 7                            |                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                   |                                                                                                                                                                               |                                       |                       |        | bit                                            |  |  |  |  |  |  |  |

|                                  |                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                   |                                                                                                                                                                               |                                       |                       |        |                                                |  |  |  |  |  |  |  |

| Legend:                          |                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                   |                                                                                                                                                                               |                                       |                       |        |                                                |  |  |  |  |  |  |  |

| R = Readab                       | ole bit                                                                                                                                                                                                                                                                                 | W = Writable                                                                                                                                                                                      | bit                                                                                                                                                                           | •                                     | mented bit, read      | as '0' |                                                |  |  |  |  |  |  |  |

| -n = Value a                     | It POR                                                                                                                                                                                                                                                                                  | '1' = Bit is set '0' = Bit is cleared x = Bit is unknown                                                                                                                                          |                                                                                                                                                                               |                                       |                       |        |                                                |  |  |  |  |  |  |  |

|                                  |                                                                                                                                                                                                                                                                                         | anted: Bood on 'o'                                                                                                                                                                                |                                                                                                                                                                               |                                       |                       |        |                                                |  |  |  |  |  |  |  |

| bit 15                           | •                                                                                                                                                                                                                                                                                       | ented: Read as '0'                                                                                                                                                                                |                                                                                                                                                                               |                                       |                       |        |                                                |  |  |  |  |  |  |  |

| bit 14                           |                                                                                                                                                                                                                                                                                         | MA Channel 4 Data Transfer Complete Interrupt Flag Status bit                                                                                                                                     |                                                                                                                                                                               |                                       |                       |        |                                                |  |  |  |  |  |  |  |

|                                  |                                                                                                                                                                                                                                                                                         | rupt request has occurred                                                                                                                                                                         |                                                                                                                                                                               |                                       |                       |        |                                                |  |  |  |  |  |  |  |

|                                  | 0 = Interrupt                                                                                                                                                                                                                                                                           | request has no                                                                                                                                                                                    | ot occurred                                                                                                                                                                   |                                       |                       |        |                                                |  |  |  |  |  |  |  |

| bit 13                           | PMPIF: Para                                                                                                                                                                                                                                                                             | llel Master Por                                                                                                                                                                                   | t Interrupt Flag                                                                                                                                                              | Status bit                            |                       |        |                                                |  |  |  |  |  |  |  |