Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| 2 0 0 0 0 0 0              |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Active                                                                        |

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 40 MIPs                                                                       |

| Connectivity               | I <sup>2</sup> C, PMP, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                    |

| Number of I/O              | 35                                                                            |

| Program Memory Size        | 64KB (22K x 24)                                                               |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                |                                                                               |

| RAM Size                   | 8K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                     |

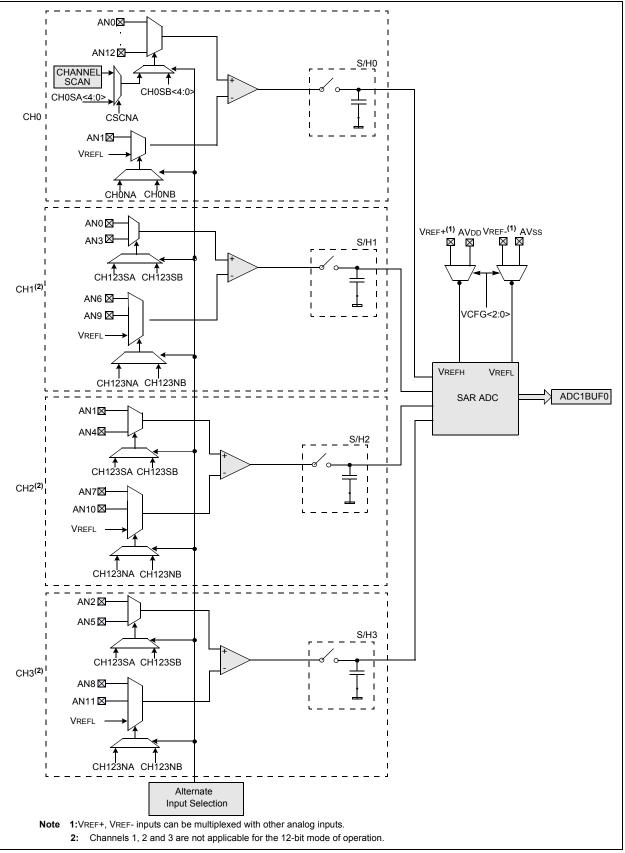

| Data Converters            | A/D 13x10b/12b                                                                |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 44-TQFP                                                                       |

| Supplier Device Package    | 44-TQFP (10x10)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24hj64gp204-e-pt |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 2.0 GUIDELINES FOR GETTING STARTED WITH 16-BIT MICROCONTROLLERS

- **Note 1:** This data sheet summarizes the features PIC24HJ32GP302/304, of the PIC24HJ64GPX02/X04 and PIC24HJ128GPX02/X04 of family devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the "dsPIC33F/PIC24H Family Reference Manual". Please see the Microchip web site (www.microchip.com) for the latest dsPIC33F/PIC24H Family Reference Manual sections.

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

### 2.1 Basic Connection Requirements

Getting started with the PIC24HJ32GP302/304, PIC24HJ64GPX02/X04 and PIC24HJ128GPX02/X04 family of 16-bit Microcontrollers (MCUs) requires attention to a minimal set of device pin connections before proceeding with development. The following is a list of pin names, which must always be connected:

- All VDD and VSS pins (see Section 2.2 "Decoupling Capacitors")

- All AVDD and AVSS pins (regardless if ADC module is not used)

(see Section 2.2 "Decoupling Capacitors")

• VCAP

(see Section 2.3 "CPU Logic Filter Capacitor Connection (VCAP)")

- MCLR pin (see Section 2.4 "Master Clear (MCLR) Pin")

- PGECx/PGEDx pins used for In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) and debugging purposes (see Section 2.5 "ICSP Pins")

- OSC1 and OSC2 pins when external oscillator source is used

(see Section 2.6 "External Oscillator Pins")

Additionally, the following pins may be required:

• VREF+/VREF- pins used when external voltage reference for ADC module is implemented

Note: The AVDD and AVSS pins must be connected independent of the ADC voltage reference source.

### 2.2 Decoupling Capacitors

The use of decoupling capacitors on every pair of power supply pins, such as VDD, VSS, AVDD and AVss is required.

Consider the following criteria when using decoupling capacitors:

- Value and type of capacitor: Recommendation of 0.1  $\mu$ F (100 nF), 10-20V. This capacitor should be a low-ESR and have resonance frequency in the range of 20 MHz and higher. It is recommended that ceramic capacitors be used.

- Placement on the printed circuit board: The decoupling capacitors should be placed as close to the pins as possible. It is recommended to place the capacitors on the same side of the board as the device. If space is constricted, the capacitor can be placed on another layer on the PCB using a via; however, ensure that the trace length from the pin to the capacitor is within one-quarter inch (6 mm) in length.

- Handling high frequency noise: If the board is experiencing high frequency noise, upward of tens of MHz, add a second ceramic-type capacitor in parallel to the above described decoupling capacitor. The value of the second capacitor can be in the range of 0.01  $\mu$ F to 0.001  $\mu$ F. Place this second capacitor next to the primary decoupling capacitor. In high-speed circuit designs, consider implementing a decade pair of capacitances as close to the power and ground pins as possible. For example, 0.1  $\mu$ F in parallel with 0.001  $\mu$ F.

- Maximizing performance: On the board layout from the power supply circuit, run the power and return traces to the decoupling capacitors first, and then to the device pins. This ensures that the decoupling capacitors are first in the power chain. Equally important is to keep the trace length between the capacitor and the power pins to a minimum thereby reducing PCB track inductance.

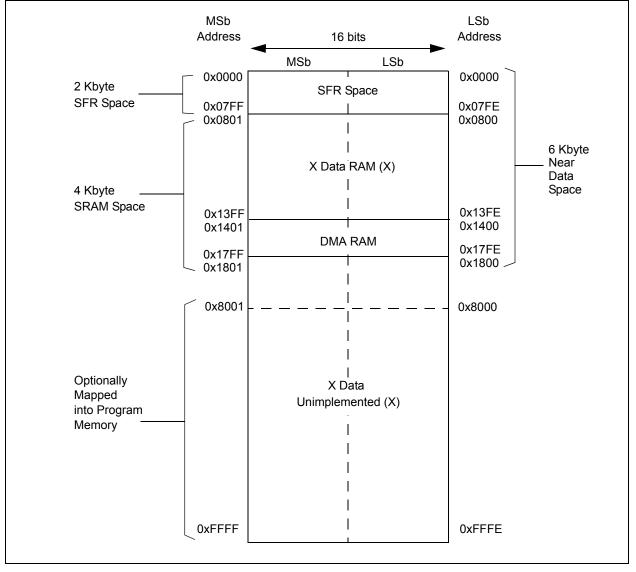

#### 4.2.5 DMA RAM

The PIC24HJ32GP302/304 devices contain 1 Kbytes of dual ported DMA RAM located at the end of X data PIC24HJ64GPX02/X04 space. The and PIC24HJ128GPX02/X04 devices contain 2 Kbytes of dual ported DMA RAM located at the end of X data space, and is a part of X data space. Memory locations in the DMA RAM space are accessible simultaneously by the CPU and the DMA controller module. DMA RAM is utilized by the DMA controller to store data to be transferred to various peripherals using DMA, as well as data transferred from various peripherals using DMA. The DMA RAM can be accessed by the DMA controller without having to steal cycles from the CPU.

When the CPU and the DMA controller attempt to concurrently write to the same DMA RAM location, the hardware ensures that the CPU is given precedence in accessing the DMA RAM location. Therefore, the DMA RAM provides a reliable means of transferring DMA data without ever having to stall the CPU.

| Note: | DMA RAM can be used for general          |

|-------|------------------------------------------|

|       | purpose data storage if the DMA function |

|       | is not required in an application.       |

#### FIGURE 4-3: DATA MEMORY MAP FOR PIC24HJ32GP302/304 DEVICES WITH 4 KB RAM

| File Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|-----------|------|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|-------|--------|--------|--------|---------------|

| BSRAM     | 0750 | _      | —      | _      |        |        | —      | -     | _     | —     | _     |       | _     | -     | IW_BSR | IR_BSR | RL_BSR | 0000          |

| SSRAM     | 0752 | _      | _      | _      | —      | —      | —      | -     | -     | —     | —     | —     | —     | —     | IW_SSR | IR_SSR | RL_SSR | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This register is not present in devices with 32K Flash (PIC24HJ32GP302/304).

#### TABLE 4-33: NVM REGISTER MAP

| File Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3   | Bit 2 | Bit 1  | Bit 0 | All<br>Resets |

|-----------|------|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|---------|-------|--------|-------|---------------|

| NVMCON    | 0760 | WR     | WREN   | WRERR  | —      | —      | —      | —     | —     | _     | ERASE | _     | -     |         | NVMO  | P<3:0> |       | 0000          |

| NVMKEY    | 0766 |        | —      | _      | —      | —      | —      |       |       |       |       |       | NVMKE | EY<7:0> |       |        |       | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-34: PMD REGISTER MAP

| File Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8 | Bit 7  | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-----------|------|--------|--------|--------|--------|--------|--------|--------|-------|--------|-------|-------|--------|--------|-------|-------|-------|---------------|

| PMD1      | 0770 | T5MD   | T4MD   | T3MD   | T2MD   | T1MD   | _      | _      | —     | I2C1MD | U2MD  | U1MD  | SPI2MD | SPI1MD | —     | C1MD  | AD1MD | 0000          |

| PMD2      | 0772 | IC8MD  | IC7MD  | _      | _      | _      | _      | IC2MD  | IC1MD | _      | _     | _     | _      | OC4MD  | OC3MD | OC2MD | OC1MD | 0000          |

| PMD3      | 0774 | _      | _      | _      | _      | _      | CMPMD  | RTCCMD | PMPMD | CRCMD  | _     | _     | _      | _      | _     | _     | _     | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| REGISTER              | 27-4: INTC                                                                          | CON2: INTERR                                                                                                                     | UPT CONT                          | ROL REGIST       | ER 2             |                 |        |

|-----------------------|-------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|------------------|------------------|-----------------|--------|

| R/W-0                 | R-0                                                                                 | U-0                                                                                                                              | U-0                               | U-0              | U-0              | U-0             | U-0    |

| ALTIVT                | DISI                                                                                | _                                                                                                                                | _                                 | —                | —                | —               | _      |

| bit 15                |                                                                                     |                                                                                                                                  |                                   |                  |                  |                 | bit 8  |

| U-0                   | U-0                                                                                 | U-0                                                                                                                              | U-0                               | U-0              | R/W-0            | R/W-0           | R/W-0  |

| _                     | _                                                                                   | _                                                                                                                                | _                                 | —                | INT2EP           | INT1EP          | INT0EP |

| bit 7                 |                                                                                     | ·                                                                                                                                |                                   |                  |                  |                 | bit C  |

|                       |                                                                                     |                                                                                                                                  |                                   |                  |                  |                 |        |

| Legend:<br>R = Readab | ole bit                                                                             | W = Writable                                                                                                                     | bit                               | U = Unimpler     | mented bit, read | as '0'          |        |

| -n = Value a          | at POR                                                                              | '1' = Bit is set                                                                                                                 | t                                 | '0' = Bit is cle |                  | x = Bit is unkr | nown   |

| bit 14                | 1 <b>= Use alt</b><br>0 <b>= Use sta</b><br><b>DISI:</b> DISI<br>1 <b>=</b> DISI ir | nable Alternate Ir<br>ernate vector tab<br>andard (default) v<br>Instruction Statu<br>nstruction is activ<br>nstruction is not a | le<br>vector table<br>is bit<br>e |                  |                  |                 |        |

| bit 13-3              | Unimplem                                                                            | ented: Read as '                                                                                                                 | 0'                                |                  |                  |                 |        |

| bit 2                 | 1 = Interrup                                                                        | xternal Interrupt 2<br>ot on negative ed<br>ot on positive edg                                                                   | ge                                | t Polarity Selec | t bit            |                 |        |

| bit 1                 | 1 = Interrup                                                                        | xternal Interrupt of<br>ot on negative ed<br>ot on positive edg                                                                  | ge                                | t Polarity Selec | t bit            |                 |        |

| bit 0                 |                                                                                     | xternal Interrupt (<br>ot on negative ed                                                                                         |                                   | t Polarity Selec | t bit            |                 |        |

# REGISTER 7-4: INTCON2: INTERRUPT CONTROL REGISTER 2

1 = Interrupt on negative edge 0 = Interrupt on positive edge

| REGISTER 7-13: | IEC3: INTERRUPT ENABLE CONTROL REGISTER 3 |

|----------------|-------------------------------------------|

|----------------|-------------------------------------------|

| U-0             | R/W-0           | R/W-0            | U-0            | U-0              | U-0              | U-0             | U-0   |

|-----------------|-----------------|------------------|----------------|------------------|------------------|-----------------|-------|

| _               | RTCIE           | DMA5IE           | —              | _                | —                | —               | —     |

| bit 15          |                 | -                |                |                  |                  |                 | bit 8 |

|                 |                 |                  |                |                  |                  |                 |       |

| U-0             | U-0             | U-0              | U-0            | U-0              | U-0              | U-0             | U-0   |

| —               | —               | —                | _              | —                | —                | —               | —     |

| bit 7           |                 |                  |                |                  |                  |                 | bit 0 |

|                 |                 |                  |                |                  |                  |                 |       |

| Legend:         |                 |                  |                |                  |                  |                 |       |

| R = Readable    | bit             | W = Writable     | bit            | U = Unimpler     | nented bit, read | as '0'          |       |

| -n = Value at F | POR             | '1' = Bit is set |                | '0' = Bit is cle | ared             | x = Bit is unkr | nown  |

|                 |                 |                  |                |                  |                  |                 |       |

| bit 15          | Unimplemen      | ted: Read as '   | )'             |                  |                  |                 |       |

| bit 14          | RTCIE: Real-    | Time Clock and   | d Calendar Int | errupt Enable    | bit              |                 |       |

|                 | 1 = Interrupt i | request enabled  | b              |                  |                  |                 |       |

0 = Interrupt request not enabled

bit 13 DMA5IE: DMA Channel 5 Data Transfer Complete Interrupt Enable bit

1 = Interrupt request enabled

0 = Interrupt request not enabled

bit 12-0 Unimplemented: Read as '0'

| U-0          | R/W-1        | R/W-0                                   | R/W-0           | U-0               | R/W-1          | R/W-0           | R/W-0 |

|--------------|--------------|-----------------------------------------|-----------------|-------------------|----------------|-----------------|-------|

| _            |              | T1IP<2:0>                               |                 | —                 |                | OC1IP<2:0>      |       |

| bit 15       |              |                                         |                 |                   |                |                 | bit 8 |

|              |              |                                         |                 |                   |                |                 |       |

| U-0          | R/W-1        | R/W-0                                   | R/W-0           | U-0               | R/W-1          | R/W-0           | R/W-0 |

| _            |              | IC1IP<2:0>                              |                 |                   |                | INT0IP<2:0>     |       |

| bit 7        |              |                                         |                 |                   |                |                 | bit C |

| Legend:      |              |                                         |                 |                   |                |                 |       |

| R = Readab   | le bit       | W = Writable I                          | oit             | U = Unimple       | mented bit, re | ad as '0'       |       |

| -n = Value a | It POR       | '1' = Bit is set                        |                 | '0' = Bit is cle  |                | x = Bit is unkn | own   |

|              |              |                                         |                 |                   |                |                 |       |

| bit 15       | Unimpleme    | ented: Read as '                        | )'              |                   |                |                 |       |

| bit 14-12    | T1IP<2:0>:   | Timer1 Interrupt                        | Priority bits   |                   |                |                 |       |

|              | 111 = Interr | upt is priority 7 (ł                    | nighest priorit | y interrupt)      |                |                 |       |

|              | •            |                                         |                 |                   |                |                 |       |

|              | •            |                                         |                 |                   |                |                 |       |

|              |              | upt is priority 1                       |                 |                   |                |                 |       |

|              |              | upt source is dis                       |                 |                   |                |                 |       |

| bit 11       | -            | ented: Read as '                        |                 |                   |                |                 |       |

| bit 10-8     |              | >: Output Compa                         |                 |                   | rity bits      |                 |       |

|              | 111 = Interr | upt is priority 7 (I                    | highest priorit | y interrupt)      |                |                 |       |

|              | •            |                                         |                 |                   |                |                 |       |

|              | •            |                                         |                 |                   |                |                 |       |

|              |              | upt is priority 1<br>upt source is disa | ahled           |                   |                |                 |       |

| bit 7        |              | ented: Read as '                        |                 |                   |                |                 |       |

| bit 6-4      | •            | : Input Capture C                       |                 | errupt Priority b | oits           |                 |       |

|              |              | upt is priority 7 (I                    |                 |                   |                |                 |       |

|              | •            |                                         |                 |                   |                |                 |       |

|              | •            |                                         |                 |                   |                |                 |       |

|              |              | upt is priority 1                       |                 |                   |                |                 |       |

|              |              | upt source is dis                       | abled           |                   |                |                 |       |

| bit 3        | Unimpleme    | ented: Read as '                        | )'              |                   |                |                 |       |

| bit 2-0      | INT0IP<2:0   | >: External Interr                      | upt 0 Priority  | bits              |                |                 |       |

|              | 111 = Interr | upt is priority 7 (I                    | nighest priorit | y interrupt)      |                |                 |       |

|              | •            |                                         |                 |                   |                |                 |       |

|              | •            |                                         |                 |                   |                |                 |       |

|              |              |                                         |                 |                   |                |                 |       |

001 = Interrupt is priority 1 000 = Interrupt source is disabled

| REGISTER 7-20: IPC5: INTERRUPT PRIORITY CONTROL REGISTER 5 | 0: IPC5: INTERRUPT PRIORITY | CONTROL REGISTER 5 |

|------------------------------------------------------------|-----------------------------|--------------------|

|------------------------------------------------------------|-----------------------------|--------------------|

| U-0          | R/W-1               | R/W-0                                | R/W-0          | U-0                | R/W-1           | R/W-0           | R/W-0          |

|--------------|---------------------|--------------------------------------|----------------|--------------------|-----------------|-----------------|----------------|

| _            |                     | IC8IP<2:0>                           |                | —                  |                 | IC7IP<2:0>      |                |

| bit 15       |                     |                                      |                |                    |                 |                 | bit            |

|              |                     |                                      |                |                    | <b>D</b> 444 4  | <b>D</b> 444 0  | <b>D</b> 444 0 |

| U-0          | U-1                 | U-0                                  | U-0            | U-0                | R/W-1           | R/W-0           | R/W-0          |

| <br>bit 7    |                     | _                                    |                | —                  |                 | INT1IP<2:0>     | bit            |

|              |                     |                                      |                |                    |                 |                 | bit            |

| Legend:      |                     |                                      |                |                    |                 |                 |                |

| R = Readab   | le bit              | W = Writable                         | oit            | U = Unimplen       | nented bit, rea | ad as '0'       |                |

| -n = Value a | It POR              | '1' = Bit is set                     |                | '0' = Bit is cle   | ared            | x = Bit is unkn | own            |

|              |                     |                                      |                |                    |                 |                 |                |

| bit 15       | -                   | ted: Read as '                       |                |                    |                 |                 |                |

| bit 14-12    |                     | · ·                                  |                | errupt Priority bi | ts              |                 |                |

|              | 111 = Interrup      | pt is priority 7 (I                  | nighest priori | ty interrupt)      |                 |                 |                |

|              | •                   |                                      |                |                    |                 |                 |                |

|              | •                   |                                      |                |                    |                 |                 |                |

|              | 001 = Interrup      | pt is priority 1                     |                |                    |                 |                 |                |

|              | 000 = Interrup      | pt source is dis                     | abled          |                    |                 |                 |                |

| bit 11       | Unimplemen          | ted: Read as '                       | )'             |                    |                 |                 |                |

| bit 10-8     | IC7IP<2:0>:         | nput Capture C                       | hannel 7 Inte  | errupt Priority bi | ts              |                 |                |

|              | 111 = Interrup      | pt is priority 7 (I                  | nighest priori | ty interrupt)      |                 |                 |                |

|              | •                   |                                      |                |                    |                 |                 |                |

|              | •                   |                                      |                |                    |                 |                 |                |

|              | •<br>001 = Interrup | ot is priority 1                     |                |                    |                 |                 |                |

|              |                     | pt is priority i<br>pt source is dis | abled          |                    |                 |                 |                |

| bit 7-3      | -                   | ted: Read as '                       |                |                    |                 |                 |                |

| bit 2-0      | -                   | External Interr                      |                | , bits             |                 |                 |                |

| 5112 0       |                     | pt is priority 7 (I                  |                |                    |                 |                 |                |

|              | •                   | , (i                                 | g. eet p. er   | (j                 |                 |                 |                |

|              | •                   |                                      |                |                    |                 |                 |                |

|              | •                   |                                      |                |                    |                 |                 |                |

|              | 001 = Interrup      |                                      | ablad          |                    |                 |                 |                |

|              | 000 = interrup      | pt source is dis                     | anieu          |                    |                 |                 |                |

| U-0          | U-0                    | U-0                                    | U-0            | U-0               | R/W-1            | R/W-0           | R/W-0 |

|--------------|------------------------|----------------------------------------|----------------|-------------------|------------------|-----------------|-------|

| —            | —                      | —                                      | _              | —                 |                  | RTCIP<2:0>      |       |

| bit 15       |                        |                                        |                |                   |                  |                 | bit   |

| U-0          | R/W-1                  | R/W-0                                  | R/W-0          | U-0               | U-0              | U-0             | U-0   |

|              |                        | DMA5IP<2:0>                            | 1011 0         |                   |                  | _               | _     |

| bit 7        |                        |                                        |                |                   |                  |                 | bit   |

|              |                        |                                        |                |                   |                  |                 |       |

| Legend:      |                        |                                        |                |                   |                  |                 |       |

| R = Readab   | ole bit                | W = Writable                           | bit            | U = Unimplen      | nented bit, read | 1 as '0'        |       |

| -n = Value a | It POR                 | '1' = Bit is set                       |                | '0' = Bit is clea | ared             | x = Bit is unkr | nown  |

|              |                        |                                        |                |                   |                  |                 |       |

| bit 15-11    | Unimpleme              | ented: Read as '                       | )'             |                   |                  |                 |       |

| bit 10-8     |                        | Real-Time Clo                          |                | •                 | ag Status bits   |                 |       |

|              | 111 = Interr           | upt is priority 7 (I                   | highest priori | ty interrupt)     |                  |                 |       |

|              | •                      |                                        |                |                   |                  |                 |       |

|              | •                      |                                        |                |                   |                  |                 |       |

|              |                        | upt is priority 1<br>upt source is dis | abled          |                   |                  |                 |       |

| bit 7        | Unimpleme              | ented: Read as '                       | כי             |                   |                  |                 |       |

| bit 6-4      | DMA5IP<2:              | 0>: DMA Channe                         | el 5 Data Tra  | nsfer Complete    | Interrupt Priori | ty bits         |       |

|              | 111 = Interr           | upt is priority 7 (I                   | highest priori | ty interrupt)     |                  |                 |       |

|              |                        |                                        |                |                   |                  |                 |       |

|              | •                      |                                        |                |                   |                  |                 |       |

|              | •<br>•                 |                                        |                |                   |                  |                 |       |

|              | •<br>•<br>001 = Interr | upt is priority 1                      |                |                   |                  |                 |       |

# REGISTER 7-26: IPC15: INTERRUPT PRIORITY CONTROL REGISTER 15

bit 3-0

Unimplemented: Read as '0'

#### 9.1 CPU Clocking System

The PIC24HJ32GP302/304, PIC24HJ64GPX02/X04 and PIC24HJ128GPX02/X04 devices provide seven system clock options:

- Fast RC (FRC) Oscillator

- FRC Oscillator with Phase-Locked Loop (PLL)

- Primary (XT, HS or EC) Oscillator

- Primary Oscillator with PLL

- Secondary (LP) Oscillator

- · Low-Power RC (LPRC) Oscillator

- · FRC Oscillator with postscaler

#### 9.1.1 SYSTEM CLOCK SOURCES

The Fast RC (FRC) internal oscillator runs at a nominal frequency of 7.37 MHz. User software can tune the FRC frequency. User software can optionally specify a factor (ranging from 1:2 to 1:256) by which the FRC clock frequency is divided. This factor is selected using the FRCDIV<2:0> (CLKDIV<10:8>) bits.

The primary oscillator can use one of the following as its clock source:

- Crystal (XT): Crystals and ceramic resonators in the range of 3 MHz to 10 MHz. The crystal is connected to the OSC1 and OSC2 pins.

- High-Speed Crystal (HS): Crystals in the range of 10 MHz to 40 MHz. The crystal is connected to the OSC1 and OSC2 pins.

- External Clock (EC): External clock signal is directly applied to the OSC1 pin.

The secondary (LP) oscillator is designed for low power and uses a 32.768 kHz crystal or ceramic resonator. The LP oscillator uses the SOSCI and SOSCO pins.

The Low-Power RC (LPRC) internal oscillator runs at a nominal frequency of 32.768 kHz. It is also used as a reference clock by the Watchdog Timer (WDT) and Fail-Safe Clock Monitor (FSCM).

The clock signals generated by the FRC and primary oscillators can be optionally applied to an on-chip PLL to provide a wide range of output frequencies for device operation. PLL configuration is described in **Section 9.1.3 "PLL Configuration**".

The FRC frequency depends on the FRC accuracy (see Table 28-19) and the value of the FRC Oscillator Tuning register (see Register 9-4).

#### 9.1.2 SYSTEM CLOCK SELECTION

The oscillator source used at a device Power-on Reset event is selected using Configuration bit settings. The oscillator Configuration bit settings are located in the Configuration registers in the program memory. (Refer to Section 25.1 "Configuration Bits" for further details.) The Initial Oscillator FNOSC<2:0> Selection Configuration bits, (FOSCSEL<2:0>), and the Primary Oscillator Mode Select Configuration bits, POSCMD<1:0> (FOSC<1:0>), select the oscillator source that is used at a Power-on Reset. The FRC primary oscillator is the default (unprogrammed) selection.

The Configuration bits allow users to choose among 12 different clock modes, shown in Table 9-1.

The output of the oscillator (or the output of the PLL if a PLL mode has been selected) Fosc is divided by 2 to generate the device instruction clock (FcY) and the peripheral clock time base (FP). FcY defines the operating speed of the device, and speeds up to 40 MHz are supported by the PIC24HJ32GP302/304, PIC24HJ64GPX02/X04 and PIC24HJ128GPX02/X04 architecture.

Instruction execution speed or device operating frequency, FCY, is given by:

#### EQUATION 9-1: DEVICE OPERATING FREQUENCY

$$FCY = \frac{FOSC}{2}$$

### REGISTER 11-4: RPINR4: PERIPHERAL PIN SELECT INPUT REGISTER 4

| U-0          | U-0                                                        | U-0                                                                                   | R/W-1          | R/W-1            | R/W-1           | R/W-1          | R/W-1 |  |

|--------------|------------------------------------------------------------|---------------------------------------------------------------------------------------|----------------|------------------|-----------------|----------------|-------|--|

|              | —                                                          | —                                                                                     | T5CKR<4:0>     |                  |                 |                |       |  |

| bit 15       |                                                            |                                                                                       |                |                  |                 |                | bit 8 |  |

| U-0          | U-0                                                        | U-0                                                                                   | R/W-1          | R/W-1            | R/W-1           | R/W-1          | R/W-1 |  |

| _            |                                                            |                                                                                       |                |                  | T4CKR<4:0       | >              |       |  |

| bit 7        | ·                                                          |                                                                                       |                |                  |                 |                | bit 0 |  |

|              |                                                            |                                                                                       |                |                  |                 |                |       |  |

| Legend:      |                                                            |                                                                                       |                |                  |                 |                |       |  |

| R = Readab   | le bit                                                     | W = Writable                                                                          | bit            | U = Unimpler     | mented bit, rea | ad as '0'      |       |  |

| -n = Value a | t POR                                                      | '1' = Bit is set                                                                      |                | '0' = Bit is cle | ared            | x = Bit is unk | nown  |  |

|              | •<br>•<br>00001 = Inpu                                     | ut tied to RP25<br>ut tied to RP1<br>ut tied to RP0                                   |                |                  |                 |                |       |  |

| bit 7-5      | Unimplemer                                                 | nted: Read as '                                                                       | 0'             |                  |                 |                |       |  |

| bit 4-0      | 11111 = Inpu<br>11001 = Inpu<br>•<br>•<br>•<br>•<br>•<br>• | Assign Timer<br>ut tied to Vss<br>ut tied to RP25<br>ut tied to RP1<br>ut tied to RP0 | 4 External Clo | ock (T4CK) to t  | he correspond   | ing RPn pin    |       |  |

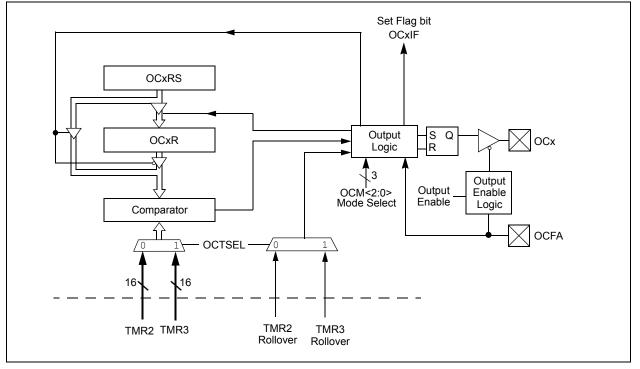

# 15.0 OUTPUT COMPARE

- Note 1: This data sheet summarizes the features of the PIC24HJ32GP302/304, PIC24HJ64GPX02/X04 and PIC24HJ128GPX02/X04 families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 13. "Output Compare" (DS70209) of the "dsPIC33F/ PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Output Compare module can select either Timer2 or Timer3 for its time base. The module compares the value of the timer with the value of one or two compare registers depending on the operating mode selected. The state of the output pin changes when the timer value matches the compare register value. The Output Compare module generates either a single output pulse or a sequence of output pulses, by changing the state of the output pin on the compare match events. The Output Compare module can also generate interrupts on compare match events.

The Output Compare module has multiple operating modes:

- Active-Low One-Shot mode

- Active-High One-Shot mode

- Toggle mode

- · Delayed One-Shot mode

- · Continuous Pulse mode

- PWM mode without fault protection

- · PWM mode with fault protection

#### FIGURE 15-1: OUTPUT COMPARE MODULE BLOCK DIAGRAM

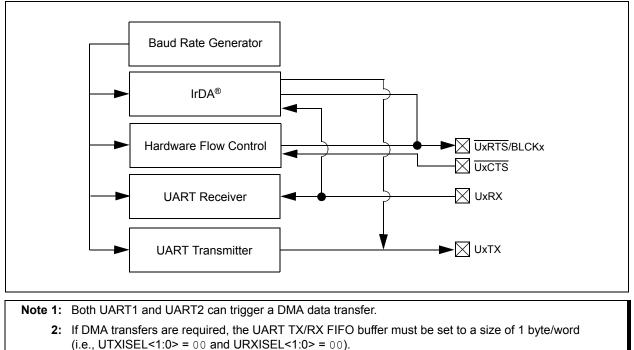

# 18.0 UNIVERSAL ASYNCHRONOUS RECEIVER TRANSMITTER (UART)

- **Note 1:** This data sheet summarizes the features the PIC24HJ32GP302/304, of PIC24HJ64GPX02/X04 and PIC24HJ128GPX02/X04 families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 17. "UART" (DS70188) of the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Universal Asynchronous Receiver Transmitter (UART) module is one of the serial I/O modules available in the PIC24HJ32GP302/304, PIC24HJ64GPX02/ X04 and PIC24HJ128GPX02/X04 device family. The UART is a full-duplex asynchronous system that can communicate with peripheral devices, such as personal computers, LIN 2.0, RS-232 and RS-485 interfaces. The module also supports a hardware flow control option with the UxCTS and UxRTS pins and also includes an IrDA<sup>®</sup> encoder and decoder. The primary features of the UART module are:

- Full-Duplex, 8- or 9-bit Data Transmission through the UxTX and UxRX pins

- Even, Odd or No Parity Options (for 8-bit data)

- One or two stop bits

- Hardware flow control option with UxCTS and UxRTS pins

- Fully integrated Baud Rate Generator with 16-bit prescaler

- Baud rates ranging from 10 Mbps to 38 bps at 40 MIPS

- 4-deep First-In First-Out (FIFO) Transmit Data buffer

- · 4-deep FIFO Receive Data buffer

- Parity, framing and buffer overrun error detection

- Support for 9-bit mode with Address Detect (9th bit = 1)

- · Transmit and Receive interrupts

- · A separate interrupt for all UART error conditions

- · Loopback mode for diagnostic support

- Support for sync and break characters

- · Support for automatic baud rate detection

- IrDA<sup>®</sup> encoder and decoder logic

- 16x baud clock output for IrDA<sup>®</sup> support

A simplified block diagram of the UART module is shown in Figure 18-1. The UART module consists of these key hardware elements:

- Baud Rate Generator

- Asynchronous Transmitter

- · Asynchronous Receiver

# REGISTER 22-8: ALRMVAL (WHEN ALRMPTR<1:0> = 10): ALARM MONTH AND DAY VALUE REGISTER<sup>(1)</sup>

| U-0    | U-0 | U-0 | R/W-x   | R/W-x | R/W-x | R/W-x   | R/W-x |

|--------|-----|-----|---------|-------|-------|---------|-------|

| —      | —   | —   | MTHTEN0 |       | MTHOM | NE<3:0> |       |

| bit 15 |     |     |         |       |       |         | bit 8 |

|        |     |     |         |       |       |         |       |

| U-0   | U-0 | R/W-x | R/W-x  | R/W-x | R/W-x | R/W-x  | R/W-x |

|-------|-----|-------|--------|-------|-------|--------|-------|

| —     | —   | DAYTE | N<1:0> |       | DAYON | E<3:0> |       |

| bit 7 |     |       |        |       |       |        | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-13 | Unimplemented: Read as '0'                                                                  |

|-----------|---------------------------------------------------------------------------------------------|

| bit 12    | MTHTEN0: Binary Coded Decimal Value of Month's Tens Digit; contains a value of 0 or 1       |

| bit 11-8  | MTHONE<3:0>: Binary Coded Decimal Value of Month's Ones Digit; contains a value from 0 to 9 |

| bit 7-6   | Unimplemented: Read as '0'                                                                  |

| bit 5-4   | DAYTEN<1:0>: Binary Coded Decimal Value of Day's Tens Digit; contains a value from 0 to 3   |

| bit 3-0   | DAYONE<3:0>: Binary Coded Decimal Value of Day's Ones Digit; contains a value from 0 to 9   |

**Note 1:** A write to this register is only allowed when RTCWREN = 1.

# **REGISTER 22-9:** ALRMVAL (WHEN ALRMPTR<1:0> = 01): ALARM WEEKDAY AND HOURS VALUE REGISTER<sup>(1)</sup>

| U-0    | U-0 | U-0 | U-0 | U-0 | R/W-x | R/W-x | R/W-x |

|--------|-----|-----|-----|-----|-------|-------|-------|

| —      | —   |     |     | —   | WDAY2 | WDAY1 | WDAY0 |

| bit 15 |     |     |     |     |       |       | bit 8 |

| U-0   | U-0 | R/W-x | R/W-x  | R/W-x | R/W-x | R/W-x  | R/W-x |

|-------|-----|-------|--------|-------|-------|--------|-------|

| —     | —   | HRTEN | N<1:0> |       | HRON  | E<3:0> |       |

| bit 7 |     |       |        |       |       |        | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | as '0'             |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 15-11 | Unimplemented: Read as '0'                                                                |

|-----------|-------------------------------------------------------------------------------------------|

| bit 10-8  | WDAY<2:0>: Binary Coded Decimal Value of Weekday Digit; contains a value from 0 to 6      |

| bit 7-6   | Unimplemented: Read as '0'                                                                |

| bit 5-4   | HRTEN<1:0>: Binary Coded Decimal Value of Hour's Tens Digit; contains a value from 0 to 2 |

| bit 3-0   | HRONE<3:0>: Binary Coded Decimal Value of Hour's Ones Digit; contains a value from 0 to 9 |

|           |                                                                                           |

| Mada di   | A write to this register is only allowed when $DTCM/DEN = 1$                              |

**Note 1:** A write to this register is only allowed when RTCWREN = 1.

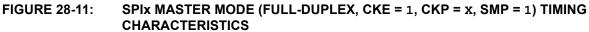

# TABLE 28-30:SPIX MASTER MODE (FULL-DUPLEX, CKE = 1, CKP = x, SMP = 1) TIMING<br/>REQUIREMENTS

| АС СНА       | RACTERIST             | Standard<br>(unless o<br>Operating            | therwise | <b>stated)</b><br>ture -40 | °C ≤Ta ≤+8 | <b>to 3.6V</b><br>35°C for Industrial<br>125°C for Extended |                               |

|--------------|-----------------------|-----------------------------------------------|----------|----------------------------|------------|-------------------------------------------------------------|-------------------------------|

| Param<br>No. | Symbol                | Characteristic <sup>(1)</sup>                 | Min      | Тур <sup>(2)</sup>         | Max        | Units                                                       | Conditions                    |

| SP10         | TscP                  | Maximum SCK Frequency                         | _        | _                          | 9          | MHz                                                         | See Note 3                    |

| SP20         | TscF                  | SCKx Output Fall Time                         | —        | —                          | —          | ns                                                          | See parameter DO32 and Note 4 |

| SP21         | TscR                  | SCKx Output Rise Time                         | —        | —                          | —          | ns                                                          | See parameter DO31 and Note 4 |

| SP30         | TdoF                  | SDOx Data Output Fall Time                    | —        | —                          | —          | ns                                                          | See parameter DO32 and Note 4 |

| SP31         | TdoR                  | SDOx Data Output Rise Time                    | —        | —                          | —          | ns                                                          | See parameter DO31 and Note 4 |

| SP35         | TscH2doV,<br>TscL2doV | SDOx Data Output Valid after SCKx Edge        | —        | 6                          | 20         | ns                                                          | —                             |

| SP36         | TdoV2sc,<br>TdoV2scL  | SDOx Data Output Setup to<br>First SCKx Edge  | 30       |                            | —          | ns                                                          | —                             |

| SP40         | TdiV2scH,<br>TdiV2scL | Setup Time of SDIx Data<br>Input to SCKx Edge | 30       | —                          | —          | ns                                                          | —                             |

| SP41         | TscH2diL,<br>TscL2diL | Hold Time of SDIx Data Input to SCKx Edge     | 30       | _                          |            | ns                                                          | —                             |

**Note 1:** These parameters are characterized, but are not tested in manufacturing.

**2:** Data in "Typ" column is at 3.3V, 25°C unless otherwise stated.

**3:** The minimum clock period for SCKx is 111 ns. The clock generated in Master mode must not violate this specification.

4: Assumes 50 pF load on all SPIx pins.

# TABLE 28-33:SPIX SLAVE MODE (FULL-DUPLEX, CKE = 1, CKP = 1, SMP = 0) TIMING<br/>REQUIREMENTS

| АС СНА       |                       | TICS                                                       | Standard Op<br>(unless othe<br>Operating ter | rwise st           | <b>ated)</b><br>e -40° | 'C ≤Ta ≤+ | V to 3.6V<br>85°C for Industrial<br>125°C for Extended |

|--------------|-----------------------|------------------------------------------------------------|----------------------------------------------|--------------------|------------------------|-----------|--------------------------------------------------------|

| Param<br>No. | Symbol                | Characteristic <sup>(1)</sup>                              | Min                                          | Тур <sup>(2)</sup> | Max                    | Units     | Conditions                                             |

| SP70         | TscP                  | Maximum SCK Input Frequency                                | _                                            | _                  | 11                     | MHz       | See Note 3                                             |

| SP72         | TscF                  | SCKx Input Fall Time                                       | _                                            | —                  |                        | ns        | See parameter DO32 and Note 4                          |

| SP73         | TscR                  | SCKx Input Rise Time                                       | —                                            | _                  |                        | ns        | See parameter DO31 and Note 4                          |

| SP30         | TdoF                  | SDOx Data Output Fall Time                                 | —                                            | —                  |                        | ns        | See parameter DO32 and Note 4                          |

| SP31         | TdoR                  | SDOx Data Output Rise Time                                 | —                                            | —                  |                        | ns        | See parameter DO31 and Note 4                          |

| SP35         | TscH2doV,<br>TscL2doV | SDOx Data Output Valid after<br>SCKx Edge                  | —                                            | 6                  | 20                     | ns        | —                                                      |

| SP36         | TdoV2scH,<br>TdoV2scL | SDOx Data Output Setup to<br>First SCKx Edge               | 30                                           | —                  |                        | ns        | —                                                      |

| SP40         | TdiV2scH,<br>TdiV2scL | Setup Time of SDIx Data Input to SCKx Edge                 | 30                                           | —                  | _                      | ns        | —                                                      |

| SP41         | TscH2diL,<br>TscL2diL | Hold Time of SDIx Data Input to SCKx Edge                  | 30                                           | _                  |                        | ns        | —                                                      |

| SP50         | TssL2scH,<br>TssL2scL | $\overline{SSx} \downarrow to SCKx \uparrow or SCKx Input$ | 120                                          | _                  | _                      | ns        | —                                                      |

| SP51         | TssH2doZ              | SSx ↑ to SDOx Output<br>High-Impedance <sup>(4)</sup>      | 10                                           | _                  | 50                     | ns        | —                                                      |

| SP52         | TscH2ssH<br>TscL2ssH  | SSx after SCKx Edge                                        | 1.5 TCY + 40                                 | _                  |                        | ns        | See Note 4                                             |

| SP60         | TssL2doV              | SDOx Data Output Valid after<br>SSx Edge                   | _                                            | _                  | 50                     | ns        | _                                                      |

**Note 1:** These parameters are characterized, but are not tested in manufacturing.

**2:** Data in "Typ" column is at 3.3V, 25°C unless otherwise stated.

**3:** The minimum clock period for SCKx is 91 ns. Therefore, the SCK clock generated by the Master must not violate this specification.

**4:** Assumes 50 pF load on all SPIx pins.

# PIC24HJ32GP302/304, PIC24HJ64GPX02/X04 AND PIC24HJ128GPX02/X04

#### TABLE 29-7: DC CHARACTERISTICS: PROGRAM MEMORY

| DC CHARACTERISTICS |        |                               | (unless               | Standard Operating Conditions: 3.0V to 3.6V(unless otherwise stated)Operating temperature-40°C ≤TA ≤+150°C for High Temperature |   |            |                                                                  |  |

|--------------------|--------|-------------------------------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------|---|------------|------------------------------------------------------------------|--|

| Param<br>No.       | Symbol | Characteristic <sup>(1)</sup> | Min Typ Max Units Con |                                                                                                                                 |   | Conditions |                                                                  |  |

|                    |        | Program Flash Memory          |                       |                                                                                                                                 |   |            |                                                                  |  |

| HD130              | Eр     | Cell Endurance                | 10,000                | _                                                                                                                               | _ | E/W        | -40° C to +150° C <sup>(2)</sup>                                 |  |

| HD134              | TRETD  | Characteristic Retention      | 20                    | _                                                                                                                               | _ | Year       | 1000 E/W cycles or less and no other specifications are violated |  |

**Note 1:** These parameters are assured by design, but are not characterized or tested in manufacturing.

**2:** Programming of the Flash memory is allowed up to 150°C.

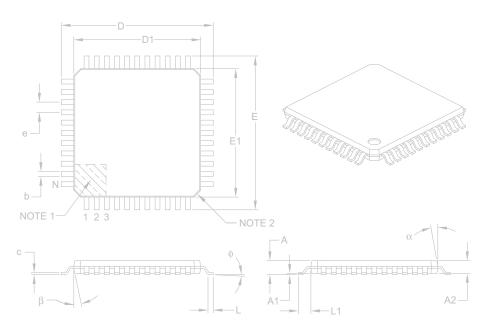

#### 44-Lead Plastic Thin Quad Flatpack (PT) – 10x10x1 mm Body, 2.00 mm Footprint [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units         | MILLIMETERS |      |      |

|--------------------------|---------------|-------------|------|------|

| Dim                      | ension Limits | MIN         | NOM  | MAX  |

| Number of Leads          | N             | 44          |      |      |

| Lead Pitch               | е             | 0.80 BSC    |      |      |

| Overall Height           | А             | -           | -    | 1.20 |

| Molded Package Thickness | A2            | 0.95        | 1.00 | 1.05 |

| Standoff                 | A1            | 0.05        | -    | 0.15 |

| Foot Length              | L             | 0.45        | 0.60 | 0.75 |

| Footprint                | L1            | 1.00 REF    |      |      |

| Foot Angle               | φ             | 0°          | 3.5° | 7°   |

| Overall Width            | E             | 12.00 BSC   |      |      |

| Overall Length           | D             | 12.00 BSC   |      |      |

| Molded Package Width     | E1            | 10.00 BSC   |      |      |

| Molded Package Length    | D1            | 10.00 BSC   |      |      |

| Lead Thickness           | С             | 0.09        | -    | 0.20 |

| Lead Width               | b             | 0.30        | 0.37 | 0.45 |

| Mold Draft Angle Top     | α             | 11°         | 12°  | 13°  |

| Mold Draft Angle Bottom  | β             | 11°         | 12°  | 13°  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Chamfers at corners are optional; size may vary.

3. Dimensions D1 and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.25 mm per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-076B

| Peripheral Module Disable (PMD)      | 130    |

|--------------------------------------|--------|

| Pinout I/O Descriptions              | 11     |

| PMD Module                           |        |

| Register Map                         |        |

| PORTA                                |        |

| Register Map                         | 44, 45 |

| PORTB                                |        |

| Register Map                         | 45     |

| Power-on Reset (POR)                 | 65     |

| Power-Saving Features                | 129    |

| Clock Frequency and Switching        | 129    |

| Program Address Space                |        |

| Construction                         |        |

| Data Access from Program Memory      |        |

| Using Program Space Visibility       | 52     |

| Data Access from Program Memory      |        |

| Using Table Instructions             | 51     |

| Data Access from, Address Generation | 50     |

| Memory Map                           |        |

| Table Read Instructions              |        |

| TBLRDH                               |        |

| TBLRDL                               | 51     |

| Visibility Operation                 | 52     |

| Program Memory                       |        |

| Interrupt Vector                     |        |

| Organization                         |        |

| Reset Vector                         |        |

|                                      |        |

# R

| Reader Response                               | . 388            |

|-----------------------------------------------|------------------|

| Register Map                                  |                  |

| CRC                                           | 44               |

| Dual Comparator                               |                  |

| Parallel Master/Slave Port                    | 43               |

| Real-Time Clock and Calendar                  |                  |

| Registers                                     |                  |

| AD1CHS0 (ADC1 Input Channel 0 Select          | . 238            |

| AD1CHS123 (ADC1 Input Channel 1, 2, 3 Select) | . 237            |

| AD1CON1 (ADC1 Control 1)                      |                  |

| AD1CON2 (ADC1 Control 2)                      |                  |

| AD1CON3 (ADC1 Control 3)                      |                  |

| AD1CON4 (ADC1 Control 4)                      | . 236            |

| AD1CSSL (ADC1 Input Scan Select Low)          | . 239            |

| AD1PCFGL (ADC1 Port Configuration Low)        | . 239            |

| CiBUFPNT1 (ECAN Filter 0-3 Buffer Pointer)    | . 213            |

| CiBUFPNT2 (ECAN Filter 4-7 Buffer Pointer)    | . 214            |

| CiBUFPNT3 (ECAN Filter 8-11 Buffer Pointer)   | . 214            |

| CiBUFPNT4 (ECAN Filter 12-15 Buffer Pointer)  | . 215            |

| CiCFG1 (ECAN Baud Rate Configuration 1)       | . 211            |

| CiCFG2 (ECAN Baud Rate Configuration 2)       | . 212            |

| CiCTRL1 (ECAN Control 1)                      | . 204            |

| CiCTRL2 (ECAN Control 2)                      | . 205            |

| CIEC (ECAN Transmit/Receive Error Count)      |                  |

| CIFCTRL (ECAN FIFO Control)                   | . 207            |

| CiFEN1 (ECAN Acceptance Filter Enable)        | . 213            |

| CiFIFO (ECAN FIFO Status)                     |                  |

| CiFMSKSEL1 (ECAN Filter 7-0 Mask Selection)   |                  |

|                                               | 040              |

| CilNTE (ECAN Interrupt Enable)                |                  |

| CiINTF (ECAN Interrupt Flag)                  | . 209            |

| CiRXFnEID (ECAN Acceptance Filter n           | o 1 <del>-</del> |

| Extended Identifier)                          | .217             |

| CiRXFnSID (ECAN Acceptance Filter n           |                  |

| Standard Identifier)                          |                  |

| CiRXFUL1 (ECAN Receive Buffer Full 1)         |                  |

| CiRXFUL2 (ECAN Receive Buffer Full 2)         | . 220            |

| CiRXMnEID (ECAN Acceptance Filter Mask n      |                  |

| Extended Identifier)                                                       | 219    |

|----------------------------------------------------------------------------|--------|

| CiRXMnSID (ECAN Acceptance Filter Mask n                                   |        |

| Standard Identifier)                                                       | 219    |

| CiRXOVF1 (ECAN Receive Buffer Overflow 1)                                  | 221    |

| CiRXOVF2 (ECAN Receive Buffer Overflow 2)                                  | 221    |

| CiTRBnSID (ECAN Buffer n Standard Identifier)                              | 223,   |

| 224, 226                                                                   |        |

| CiTRmnCON (ECAN TX/RX Buffer m Control)                                    | 222    |

| CiVEC (ECAN Interrupt Code)                                                |        |

| CLKDIV (Clock Divisor)                                                     |        |

| CORCON (Core Control)                                                      |        |

| DMACS0 (DMA Controller Status 0)                                           |        |

| DMACS1 (DMA Controller Status 1)                                           |        |

| DMACST (DMA Controller Status 1)<br>DMAXCNT (DMA Channel x Transfer Count) |        |

| DMAXCON (DMA Channel x Control)                                            |        |

|                                                                            |        |

| DMAxPAD (DMA Channel x Peripheral Address)                                 |        |

| DMAxREQ (DMA Channel x IRQ Select)                                         |        |

| DMAxSTA (DMA Channel x RAM Start Address A                                 |        |

| DMAxSTB (DMA Channel x RAM Start Address E                                 |        |

| DSADR (Most Recent DMA RAM Address)                                        |        |

| I2CxCON (I2Cx Control)                                                     |        |

| I2CxMSK (I2Cx Slave Mode Address Mask)                                     | 192    |

| I2CxSTAT (I2Cx Status)                                                     | 190    |

| IFS0 (Interrupt Flag Status 0)                                             | 77, 84 |

| IFS1 (Interrupt Flag Status 1)                                             | 79, 86 |

| IFS2 (Interrupt Flag Status 2)                                             | 81, 88 |

| IFS3 (Interrupt Flag Status 3)                                             | 82, 89 |

| IFS4 (Interrupt Flag Status 4)                                             | 83, 90 |

| INTCON1 (Interrupt Control 1)                                              | 75     |

| INTCON2 (Interrupt Control 2)                                              |        |

| INTTREG Interrupt Control and Status Register                              |        |

| IPC0 (Interrupt Priority Control 0)                                        |        |

| IPC1 (Interrupt Priority Control 1)                                        |        |

| IPC11 (Interrupt Priority Control 11)                                      |        |

| IPC15 (Interrupt Priority Control 15)                                      |        |

| IPC16 (Interrupt Priority Control 16)                                      |        |

| IPC17 (Interrupt Priority Control 17)                                      |        |

| IPC2 (Interrupt Priority Control 2)                                        |        |

| IPC3 (Interrupt Priority Control 3)                                        |        |

| IPC4 (Interrupt Priority Control 4)                                        |        |

| IPC5 (Interrupt Priority Control 5)                                        |        |

| IPC6 (Interrupt Priority Control 6)                                        |        |

| IPC7 (Interrupt Priority Control 7)                                        |        |

| IPC8 (Interrupt Priority Control 8)                                        |        |

|                                                                            |        |

| IPC9 (Interrupt Priority Control 9)                                        | 100    |

| NVMCON (Flash Memory Control)                                              |        |

| NVMKEY (Nonvolatile Memory Key)                                            |        |

| OCxCON (Output Compare x Control)                                          |        |

| OSCCON (Oscillator Control)                                                |        |

| OSCTUN (FRC Oscillator Tuning)                                             |        |

| PLLFBD (PLL Feedback Divisor)                                              | 126    |

| PMD1 (Peripheral Module Disable                                            |        |

| Control Register 1)                                                        | 132    |

| PMD2 (Peripheral Module Disable                                            |        |

| Control Register 2)                                                        | 133    |

| PMD3 (Peripheral Module Disable                                            |        |

| Control Register 3)                                                        |        |

| RCON (Reset Control)                                                       |        |

| SPIxCON1 (SPIx Control 1)                                                  |        |

| SPIxCON2 (SPIx Control 2)                                                  | 184    |

| SPIxSTAT (SPIx Status and Control)                                         | 181    |

| SR (CPU Status)                                                            | 21, 74 |

| T1CON (Timer1 Control)                                                     |        |

| TCxCON (Input Capture x Control)                                           |        |

| TxCON (Type B Time Base Control)                                           |        |

| TyCON (Type C Time Base Control)                                           |        |

| UxMODE (UARTx Mode)                                                        |        |

|                                                                            |        |