Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XFl

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 40 MIPs                                                                        |

| Connectivity               | I <sup>2</sup> C, PMP, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                     |

| Number of I/O              | 35                                                                             |

| Program Memory Size        | 64KB (22K x 24)                                                                |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 8K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                      |

| Data Converters            | A/D 13x10b/12b                                                                 |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 44-VQFN Exposed Pad                                                            |

| Supplier Device Package    | 44-QFN (8x8)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24hj64gp204t-i-ml |

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 3.4 CPU Resources

Many useful resources related to the CPU are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the |

|-------|---------------------------------------------|

|       | product page using the link above, enter    |

|       | this URL in your browser:                   |

|       | http://www.microchip.com/wwwproducts/       |

|       | Devices.aspx?dDocName=en534555              |

### 3.4.1 KEY RESOURCES

- Section 2. "CPU" (DS70204)

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All related dsPIC33F/PIC24H Family Reference Manuals Sections

- Development Tools

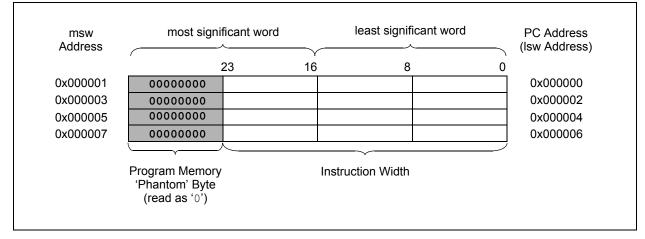

### 4.1.1 PROGRAM MEMORY ORGANIZATION

The program memory space is organized in word-addressable blocks. Although it is treated as 24 bits wide, it is more appropriate to think of each address of the program memory as a lower and upper word, with the upper byte of the upper word being unimplemented. The lower word always has an even address, while the upper word has an odd address, as shown in Figure 4-2.

Program memory addresses are always word-aligned on the lower word, and addresses are incremented or decremented by two during code execution. This arrangement provides compatibility with data memory space addressing and makes data in the program memory space accessible.

### 4.1.2 INTERRUPT AND TRAP VECTORS

All PIC24HJ32GP302/304, PIC24HJ64GPX02/X04 and PIC24HJ128GPX02/X04 devices reserve the addresses between 0x00000 and 0x000200 for hard-coded program execution vectors. A hardware Reset vector is provided to redirect code execution from the default value of the PC on device Reset to the actual start of code. A GOTO instruction is programmed by the user application at 0x000000, with the actual address for the start of code at 0x000002.

PIC24HJ32GP302/304, PIC24HJ64GPX02/X04 and PIC24HJ128GPX02/X04 devices also have two interrupt vector tables, located from 0x000004 to 0x0000FF and 0x000100 to 0x0001FF. These vector tables allow each of the device interrupt sources to be handled by separate Interrupt Service Routines (ISRs). A more detailed discussion of the interrupt vector tables is provided in Section 7.1 "Interrupt Vector Table".

### FIGURE 4-2: PROGRAM MEMORY ORGANIZATION

| IADLE 4-10 | J. L |         | LOIST    |         |         |          |            |          |         | K FIC24HJ 120GF 502/504 AND FIC24HJ04GF 502/504 |                  |        |            |        |        |          |        |               |

|------------|------|---------|----------|---------|---------|----------|------------|----------|---------|-------------------------------------------------|------------------|--------|------------|--------|--------|----------|--------|---------------|

| File Name  | Addr | Bit 15  | Bit 14   | Bit 13  | Bit 12  | Bit 11   | Bit 10     | Bit 9    | Bit 8   | Bit 7                                           | Bit 6            | Bit 5  | Bit 4      | Bit 3  | Bit 2  | Bit 1    | Bit 0  | All<br>Resets |

| C1CTRL1    | 0400 | _       | _        | CSIDL   | ABAT    | _        | R          | EQOP<2:0 | >       | OPN                                             | /ODE<2:0         | >      | —          | CANCAP | —      | —        | WIN    | 0480          |

| C1CTRL2    | 0402 | —       | _        | _       | —       | _        | _          | —        | _       | —                                               | — — — DNCNT<4:0> |        |            |        | 0000   |          |        |               |

| C1VEC      | 0404 | —       | _        | _       |         | F        | ILHIT<4:0> |          |         | —                                               |                  |        | ICODE<6:0> |        |        |          | 0000   |               |

| C1FCTRL    | 0406 | D       | MABS<2:0 | >       | —       | —        | —          | —        | _       | —                                               | —                | —      | FSA<4:0>   |        |        | 0000     |        |               |

| C1FIFO     | 0408 | —       | _        |         |         | FBP<5:0> |            |          | _       | _                                               | FNRB<5:0>        |        |            | 0000   |        |          |        |               |

| C1INTF     | 040A | _       | _        | TXBO    | TXBP    | RXBP     | TXWAR      | RXWAR    | EWARN   | IVRIF                                           | WAKIF            | ERRIF  |            | FIFOIF | RBOVIF | RBIF     | TBIF   | 0000          |

| C1INTE     | 040C | —       | _        | _       | —       | _        | _          | —        | _       | IVRIE                                           | WAKIE            | ERRIE  | _          | FIFOIE | RBOVIE | RBIE     | TBIE   | 0000          |

| C1EC       | 040E |         |          |         | TERRCN  | IT<7:0>  |            |          |         |                                                 |                  |        | RERRCN     | T<7:0> |        |          |        | 0000          |

| C1CFG1     | 0410 | —       | _        | _       | —       | _        | _          | —        | _       | SJW<1                                           | :0>              |        |            | BRP<   | :5:0>  |          |        | 0000          |

| C1CFG2     | 0412 | —       | WAKFIL   | _       | —       | _        | SE         | G2PH<2:0 | )>      | SEG2PHTS                                        | SAM              | S      | EG1PH<2    | :0>    | P      | RSEG<2:0 | )>     | 0000          |

| C1FEN1     | 0414 | FLTEN15 | FLTEN14  | FLTEN13 | FLTEN12 | FLTEN11  | FLTEN10    | FLTEN9   | FLTEN8  | FLTEN7                                          | FLTEN6           | FLTEN5 | FLTEN4     | FLTEN3 | FLTEN2 | FLTEN1   | FLTEN0 | FFFF          |

| C1FMSKSEL1 | 0418 | F7MSk   | <1:0>    | F6MS    | <<1:0>  | F5MSI    | K<1:0>     | F4MS     | K<1:0>  | F3MSK<                                          | :1:0>            | F2MSH  | <<1:0>     | F1MSK  | <1:0>  | F0MSI    | K<1:0> | 0000          |

| C1FMSKSEL2 | 041A | F15MS   | K<1:0>   | F14MS   | K<1:0>  | F13MS    | K<1:0>     | F12MS    | SK<1:0> | F11MSK                                          | <1:0>            | F10MS  | K<1:0>     | F9MSK  | <1:0>  | F8MSI    | K<1:0> | 0000          |

### TABLE 4-16: ECAN1 REGISTER MAP WHEN C1CTRL1.WIN = 0 OR 1 (FOR PIC24HJ128GP502/504 AND PIC24HJ64GP502/504)

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-17: ECAN1 REGISTER MAP WHEN C1CTRL1.WIN = 0 (FOR PIC24HJ128GP502/504 AND PIC24HJ64GP502/504)

| File Name | Addr          | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11  | Bit 10  | Bit 9   | Bit 8        | Bit 7     | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   | All<br>Resets |

|-----------|---------------|---------|---------|---------|---------|---------|---------|---------|--------------|-----------|---------|---------|---------|---------|---------|---------|---------|---------------|

|           | 0400-<br>041E |         |         |         |         |         |         | See     | e definition | when WIN  | = x     |         |         |         |         |         |         |               |

| C1RXFUL1  | 0420          | RXFUL15 | RXFUL14 | RXFUL13 | RXFUL12 | RXFUL11 | RXFUL10 | RXFUL9  | RXFUL8       | RXFUL7    | RXFUL6  | RXFUL5  | RXFUL4  | RXFUL3  | RXFUL2  | RXFUL1  | RXFUL0  | 0000          |

| C1RXFUL2  | 0422          | RXFUL31 | RXFUL30 | RXFUL29 | RXFUL28 | RXFUL27 | RXFUL26 | RXFUL25 | RXFUL24      | RXFUL23   | RXFUL22 | RXFUL21 | RXFUL20 | RXFUL19 | RXFUL18 | RXFUL17 | RXFUL16 | 0000          |

| C1RXOVF1  | 0428          | RXOVF15 | RXOVF14 | RXOVF13 | RXOVF12 | RXOVF11 | RXOVF10 | RXOVF9  | RXOVF8       | RXOVF7    | RXOVF6  | RXOVF5  | RXOVF4  | RXOVF3  | RXOVF2  | RXOVF1  | RXOVF0  | 0000          |

| C1RXOVF2  | 042A          | RXOVF31 | RXOVF30 | RXOVF29 | RXOVF28 | RXOVF27 | RXOVF26 | RXOVF25 | RXOVF24      | RXOVF23   | RXOVF22 | RXOVF21 | RXOVF20 | RXOVF19 | RXOVF18 | RXOVF17 | RXOVF16 | 0000          |

| C1TR01CON | 0430          | TXEN1   | TXABT1  | TXLARB1 | TXERR1  | TXREQ1  | RTREN1  | TX1PF   | RI<1:0>      | TXEN0     | TXABT0  | TXLARB0 | TXERR0  | TXREQ0  | RTREN0  | TX0PF   | RI<1:0> | 0000          |

| C1TR23CON | 0432          | TXEN3   | TXABT3  | TXLARB3 | TXERR3  | TXREQ3  | RTREN3  | TX3PF   | RI<1:0>      | TXEN2     | TXABT2  | TXLARB2 | TXERR2  | TXREQ2  | RTREN2  | TX2PF   | RI<1:0> | 0000          |

| C1TR45CON | 0434          | TXEN5   | TXABT5  | TXLARB5 | TXERR5  | TXREQ5  | RTREN5  | TX5PF   | RI<1:0>      | TXEN4     | TXABT4  | TXLARB4 | TXERR4  | TXREQ4  | RTREN4  | TX4PF   | RI<1:0> | 0000          |

| C1TR67CON | 0436          | TXEN7   | TXABT7  | TXLARB7 | TXERR7  | TXREQ7  | RTREN7  | TX7PF   | RI<1:0>      | TXEN6     | TXABT6  | TXLARB6 | TXERR6  | TXREQ6  | RTREN6  | TX6PF   | RI<1:0> | 0000          |

| C1RXD     | 0440          |         |         |         |         |         |         |         | Received     | Data Word |         |         |         |         |         |         |         | xxxx          |

| C1TXD     | 0442          |         |         |         |         |         |         |         | Transmit I   | Data Word |         |         |         |         |         |         |         | xxxx          |

Legend:

x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### EXAMPLE 5-2: LOADING THE WRITE BUFFERS

| ; Set up NVMCON for row programming oper | ations                                           |

|------------------------------------------|--------------------------------------------------|

| MOV #0x4001, W0                          | ;                                                |

| MOV W0, NVMCON                           | ; Initialize NVMCON                              |

| ; Set up a pointer to the first program  | memory location to be written                    |

| ; program memory selected, and writes en | abled                                            |

| MOV #0x0000, W0                          | ;                                                |

| MOV W0, TBLPAG                           | ; Initialize PM Page Boundary SFR                |

| MOV #0x6000, W0                          | ; An example program memory address              |

| ; Perform the TBLWT instructions to writ | e the latches                                    |

| ; 0th_program_word                       |                                                  |

| MOV #LOW_WORD_0, W2                      | ;                                                |

| MOV #HIGH_BYTE_0, W3                     | ;                                                |

| TBLWTL W2, [W0]                          | ; Write PM low word into program latch           |

| TBLWTH W3, [W0++]                        | ; Write PM high byte into program latch          |

| ; 1st_program_word                       |                                                  |

| MOV #LOW_WORD_1, W2                      | ;                                                |

| MOV #HIGH_BYTE_1, W3                     | ;                                                |

| TBLWTL W2, [W0]                          | ; Write PM low word into program latch           |

| TBLWTH W3, [W0++]                        | ; Write PM high byte into program latch          |

| ; 2nd_program_word                       |                                                  |

| MOV #LOW_WORD_2, W2                      | ;                                                |

| MOV #HIGH_BYTE_2, W3                     | ;                                                |

| TBLWTL W2, [W0]                          | ; Write PM low word into program latch           |

| TBLWTH W3, [W0++]                        | ; Write PM high byte into program latch          |

| •                                        |                                                  |

| •                                        |                                                  |

| •                                        |                                                  |

| ; 63rd_program_word                      |                                                  |

| MOV #LOW_WORD_31, W2                     | ;                                                |

| MOV #HIGH_BYTE_31, W3                    | i . Muite DM less second into management less in |

| TBLWTL W2, [W0]                          | ; Write PM low word into program latch           |

| TBLWTH W3, [W0++]                        | ; Write PM high byte into program latch          |

|                                          |                                                  |

### EXAMPLE 5-3: INITIATING A PROGRAMMING SEQUENCE

| DISI | #5          | <pre>; Block all interrupts with priority &lt;7 ; for next 5 instructions</pre> |

|------|-------------|---------------------------------------------------------------------------------|

| MOV  | #0x55, W0   |                                                                                 |

| MOV  | W0, NVMKEY  | ; Write the 55 key                                                              |

| MOV  | #0×AA, W1   | ;                                                                               |

| MOV  | W1, NVMKEY  | ; Write the AA key                                                              |

| BSET | NVMCON, #WR | ; Start the erase sequence                                                      |

| NOP  |             | ; Insert two NOPs after the                                                     |

| NOP  |             | ; erase command is asserted                                                     |

|      |             |                                                                                 |

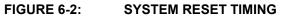

- **Note 1: POR:** A POR circuit holds the device in Reset when the power supply is turned on. The POR circuit is active until VDD crosses the VPOR threshold and the delay TPOR has elapsed.

- 2: BOR: The on-chip voltage regulator has a BOR circuit that keeps the device in Reset until VDD crosses the VBOR threshold and the delay TBOR has elapsed. The delay TBOR ensures the voltage regulator output becomes stable.

- **3: PWRT Timer:** The programmable power-up timer continues to hold the processor in Reset for a specific period of time (TPWRT) after a BOR. The delay TPWRT ensures that the system power supplies have stabilized at the appropriate level for full-speed operation. After the delay TPWRT has elapsed, the SYSRST becomes inactive, which in turn enables the selected oscillator to start generating clock cycles.

- 4: Oscillator Delay: The total delay for the clock to be ready for various clock source selections are given in Table 6-1. Refer to Section 9.0 "Oscillator Configuration" for more information.

- **5:** When the oscillator clock is ready, the processor begins execution from location 0x000000. The user application programs a GOTO instruction at the reset address, which redirects program execution to the appropriate start-up routine.

- 6: The Fail-Safe Clock Monitor (FSCM), if enabled, begins to monitor the system clock when the system clock is ready and the delay TFSCM elapsed.

| REGISTER 7            | 7-25: IPC11: | INTERRUPT                                               | PRIORITY       |                  | REGISTER 11       |                    |       |  |

|-----------------------|--------------|---------------------------------------------------------|----------------|------------------|-------------------|--------------------|-------|--|

| U-0                   | U-0          | U-0                                                     | U-0            | U-0              | R/W-1             | R/W-0              | R/W-0 |  |

|                       | _            | _                                                       |                | _                |                   | DMA4IP<2:0>        |       |  |

| bit 15                |              |                                                         |                |                  |                   |                    | bit 8 |  |

| r                     |              |                                                         |                |                  |                   |                    |       |  |

| U-0                   | R/W-1        | R/W-0                                                   | R/W-0          | U-0              | U-0               | U-0                | U-0   |  |

|                       |              | PMPIP<2:0>                                              |                | —                | —                 | —                  |       |  |

| bit 7                 |              |                                                         |                |                  |                   |                    | bit 0 |  |

|                       |              |                                                         |                |                  |                   |                    |       |  |

| Legend:               |              |                                                         |                |                  |                   |                    |       |  |

| R = Readable          | bit          | W = Writable                                            | bit            | U = Unimpler     | mented bit, rea   | d as '0'           |       |  |

| -n = Value at I       | POR          | '1' = Bit is set                                        |                | '0' = Bit is cle | ared              | x = Bit is unknown |       |  |

| bit 15-11<br>bit 10-8 | DMA4IP<2:0   | ted: Read as '(<br>>: DMA Channe<br>pt is priority 7 (l | el 4 Data Trar | •                | e Interrupt Prior | ity bits           |       |  |

|                       |              | pt is priority i<br>pt source is dis                    | abled          |                  |                   |                    |       |  |

| bit 7                 | Unimplemen   | ted: Read as '                                          | 0'             |                  |                   |                    |       |  |

**PMPIP<2:0>:** Parallel Master Port Interrupt Priority bits 111 = Interrupt is priority 7 (highest priority interrupt)

001 = Interrupt is priority 1 000 = Interrupt source is disabled

Unimplemented: Read as '0'

bit 6-4

bit 3-0

| REGISTER 8-2: DMAxREQ: DMA CHANNEL x IRQ SELECT REGIST |

|--------------------------------------------------------|

|--------------------------------------------------------|

| -                    |                            |                                 |       |                                    |      |                 |       |  |  |  |  |  |

|----------------------|----------------------------|---------------------------------|-------|------------------------------------|------|-----------------|-------|--|--|--|--|--|

| R/W-0                | U-0                        | U-0                             | U-0   | U-0                                | U-0  | U-0             | U-0   |  |  |  |  |  |

| FORCE <sup>(1)</sup> | —                          | —                               |       | —                                  |      |                 | —     |  |  |  |  |  |

| bit 15               |                            |                                 |       |                                    |      |                 | bit 8 |  |  |  |  |  |

|                      |                            |                                 |       |                                    |      |                 |       |  |  |  |  |  |

| U-0                  | R/W-0                      | R/W-0                           | R/W-0 | U-0                                | U-0  | R/W-0           | R/W-0 |  |  |  |  |  |

|                      | IRQSEL<6:0> <sup>(2)</sup> |                                 |       |                                    |      |                 |       |  |  |  |  |  |

| bit 7                | •                          |                                 |       |                                    |      |                 | bit 0 |  |  |  |  |  |

|                      |                            |                                 |       |                                    |      |                 |       |  |  |  |  |  |

| Legend:              |                            |                                 |       |                                    |      |                 |       |  |  |  |  |  |

| R = Readable         | bit                        | W = Writable I                  | bit   | U = Unimplemented bit, read as '0' |      |                 |       |  |  |  |  |  |

| -n = Value at P      | OR                         | '1' = Bit is set                |       | '0' = Bit is cle                   | ared | x = Bit is unkr | nown  |  |  |  |  |  |

|                      |                            |                                 |       |                                    |      |                 |       |  |  |  |  |  |

| bit 15               |                            | e DMA Transfe                   |       |                                    |      |                 |       |  |  |  |  |  |

|                      |                            | ingle DMA trans<br>DMA transfer |       |                                    |      |                 |       |  |  |  |  |  |

bit 14-7 Unimplemented: Read as '0'

## bit 6-0 IRQSEL<6:0>: DMA Peripheral IRQ Number Select bits<sup>(2)</sup>

0000000-1111111 = DMAIRQ0-DMAIRQ127 selected to be Channel DMAREQ

**Note 1:** The FORCE bit cannot be cleared by the user. The FORCE bit is cleared by hardware when the forced DMA transfer is complete.

2: Refer to Table 7-1 for a complete listing of IRQ numbers for all interrupt sources.

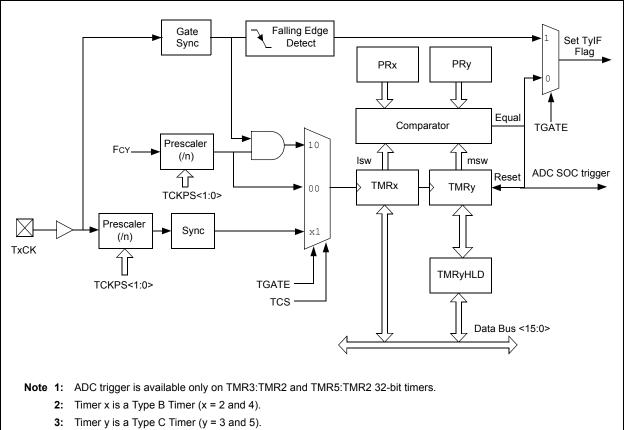

### 13.3 Timer Resources

Many useful resources related to Timers are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

Note: In the event you are not able to access the product page using the link above, enter this URL in your browser: http://www.microchip.com/wwwproducts/ Devices.aspx?dDocName=en532315

### 13.3.1 KEY RESOURCES

- Section 11. "Timers" (DS70205)

- Code Samples

- Application Notes

- Software Libraries

- · Webinars

- All related dsPIC33F/PIC24H Family Reference Manuals Sections

- Development Tools

## REGISTER 17-2: I2CxSTAT: I2Cx STATUS REGISTER (CONTINUED)

| bit 3 | S: Start bit                                                                                                                                                                                                                                 |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul> <li>1 = Indicates that a Start (or Repeated Start) bit has been detected last</li> <li>0 = Start bit was not detected last</li> <li>Hardware set or clear when Start, Repeated Start or Stop detected.</li> </ul>                       |

| bit 2 | <b>R_W:</b> Read/Write Information bit (when operating as I <sup>2</sup> C slave)                                                                                                                                                            |

|       | <ul> <li>1 = Read – indicates data transfer is output from slave</li> <li>0 = Write – indicates data transfer is input to slave</li> <li>Hardware set or clear after reception of I<sup>2</sup>C device address byte.</li> </ul>             |

| bit 1 | <b>RBF:</b> Receive Buffer Full Status bit<br>1 = Receive complete, I2CxRCV is full<br>0 = Receive not complete, I2CxRCV is empty<br>Hardware set when I2CxRCV is written with received byte. Hardware clear when software<br>reads I2CxRCV. |

| bit 0 | <b>TBF:</b> Transmit Buffer Full Status bit<br>1 = Transmit in progress, I2CxTRN is full<br>0 = Transmit complete, I2CxTRN is empty<br>Hardware set when software writes I2CxTRN. Hardware clear at completion of data transmission.         |

# PIC24HJ32GP302/304, PIC24HJ64GPX02/X04 AND PIC24HJ128GPX02/X04

|                                                                   |                                                                                                       | R/W-0                                                                                                                                        | U-0                                | U-0               | U-0               | U-0             | U-0   |  |  |

|-------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|-------------------|-------------------|-----------------|-------|--|--|

|                                                                   | DMABS<2:0>                                                                                            |                                                                                                                                              | —                                  | —                 | _                 | —               | —     |  |  |

| bit 15                                                            |                                                                                                       |                                                                                                                                              |                                    |                   |                   |                 | bit 8 |  |  |

| U-0                                                               | U-0                                                                                                   | U-0                                                                                                                                          | R/W-0                              | R/W-0             | R/W-0             | R/W-0           | R/W-0 |  |  |

| _                                                                 | — — FSA<4:0>                                                                                          |                                                                                                                                              |                                    |                   |                   |                 |       |  |  |

| bit 7                                                             |                                                                                                       |                                                                                                                                              |                                    |                   |                   |                 | bit ( |  |  |

| Levende                                                           |                                                                                                       | C = M/rite eble                                                                                                                              |                                    | 'O' oon ho writte | ve to close the l | .:4             |       |  |  |

| Legend:<br>B = Boodabl                                            | a hit                                                                                                 |                                                                                                                                              | •                                  | '0' can be writte |                   |                 |       |  |  |

| R = Readable bitW = Writable bit-n = Value at POR'1' = Bit is set |                                                                                                       |                                                                                                                                              |                                    | 0 = Onimplen      | nented bit, read  | x = Bit is unkr |       |  |  |

|                                                                   | FUR                                                                                                   |                                                                                                                                              |                                    |                   | aleu              |                 | IOWIT |  |  |

| bit 12-5                                                          | 101 = 24 buffe<br>100 = 16 buffe<br>011 = 12 buffe<br>010 = 8 buffe<br>001 = 6 buffe<br>000 = 4 buffe | ers in DMA RA<br>ers in DMA RA<br>ers in DMA RA<br>ers in DMA RA<br>rs in DMA RAN<br>rs in DMA RAN<br>rs in DMA RAN<br><b>ted:</b> Read as ' | AM<br>AM<br>AM<br>A<br>A<br>A<br>A |                   |                   |                 |       |  |  |

| bit 4-0                                                           | •                                                                                                     | FO Area Starts                                                                                                                               |                                    | oite              |                   |                 |       |  |  |

|                                                                   | 11111 = Read<br>11110 = Read<br>•                                                                     | d buffer RB31                                                                                                                                |                                    | 5113              |                   |                 |       |  |  |

# PIC24HJ32GP302/304, PIC24HJ64GPX02/X04 AND PIC24HJ128GPX02/X04

### **REGISTER 19-8:** CIEC: ECAN™ TRANSMIT/RECEIVE ERROR COUNT REGISTER

| R-0                                | R-0 | R-0             | R-0           | R-0                                    | R-0            | R-0   | R-0   |  |  |  |

|------------------------------------|-----|-----------------|---------------|----------------------------------------|----------------|-------|-------|--|--|--|

|                                    |     |                 | TERRC         | NT<7:0>                                |                |       |       |  |  |  |

| bit 15                             |     |                 |               |                                        |                |       | bit 8 |  |  |  |

| R-0                                | R-0 | R-0             | R-0           | R-0                                    | R-0            | R-0   | R-0   |  |  |  |

|                                    |     |                 | RERRC         | CNT<7:0>                               |                |       |       |  |  |  |

| bit 7                              |     |                 |               |                                        |                |       | bit 0 |  |  |  |

| Legend:                            |     | C = Writeable b | oit, but only | 0' can be writter                      | n to clear the | e bit |       |  |  |  |

| R = Readable bit W = Writable bit  |     |                 | it            | U = Unimplemented bit, read as '0'     |                |       |       |  |  |  |

| -n = Value at POR '1' = Bit is set |     |                 |               | '0' = Bit is cleared x = Bit is unknow |                |       |       |  |  |  |

| bit 15-8 | TERRCNT<7:0>: Transmit Error Count bits |

|----------|-----------------------------------------|

| bit 7-0  | RERRCNT<7:0>: Receive Error Count bits  |

### REGISTER 19-9: CiCFG1: ECAN™ BAUD RATE CONFIGURATION REGISTER 1

| <u> </u>     | U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------------|--------|-----|-----|-----|-----|-----|-----|-------|

| bit 15 bit 8 | —      | —   | —   | —   | —   | —   | —   | _     |

|              | bit 15 |     |     |     |     |     |     | bit 8 |

| R/W-0 | R/W-0 | R/W-0    | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-------|----------|-------|-------|-------|-------|-------|

| SJW   | <1:0> | BRP<5:0> |       |       |       |       |       |

| bit 7 |       |          |       |       |       |       | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-8 | Unimplemented: Read as '0'                |

|----------|-------------------------------------------|

| bit 7-6  | SJW<1:0>: Synchronization Jump Width bits |

|          | 11 = Length is 4 x TQ                     |

|          | 10 = Length is 3 x TQ                     |

|          | 01 = Length is 2 x TQ                     |

|          | 00 = Length is 1 x TQ                     |

| bit 5-0  | BRP<5:0>: Baud Rate Prescaler bits        |

|          | 11 1111 = TQ = 2 x 64 x 1/FCAN            |

|          | •                                         |

|          | •                                         |

|          | •                                         |

|          | 00 0010 = Tq = 2 x 3 x 1/Fcan             |

|          | 00 0001 = Tq = 2 x 2 x 1/Fcan             |

|          | 00 0000 = Tq = 2 x 1 x 1/FCAN             |

| U-0             | R/W-x                                                                                                 | U-0             | U-0               | U-0              | R/W-x          | R/W-x                | R/W-x |  |  |

|-----------------|-------------------------------------------------------------------------------------------------------|-----------------|-------------------|------------------|----------------|----------------------|-------|--|--|

| _               | WAKFIL                                                                                                | _               | _                 | _                |                | SEG2PH<2:0>          |       |  |  |

| bit 15          |                                                                                                       |                 |                   |                  |                |                      | bit   |  |  |

| -               |                                                                                                       |                 | <b>-</b>          |                  |                |                      |       |  |  |

| R/W-x           | R/W-x                                                                                                 | R/W-x           | R/W-x             | R/W-x            | R/W-x          | R/W-x                | R/W-x |  |  |

| SEG2PHTS        | SAM                                                                                                   |                 | SEG1PH<2:0>       | >                |                | PRSEG<2:0>           |       |  |  |

| bit 7           |                                                                                                       |                 |                   |                  |                |                      | bit   |  |  |

| Legend:         |                                                                                                       |                 |                   |                  |                |                      |       |  |  |

| R = Readable    | bit                                                                                                   | W = Writable    | e bit             | U = Unimple      | mented bit, re | ad as '0'            |       |  |  |

| -n = Value at F | POR                                                                                                   | '1' = Bit is se | et                | '0' = Bit is cle | eared          | x = Bit is unkno     | own   |  |  |

|                 |                                                                                                       |                 |                   |                  |                |                      |       |  |  |

| bit 15          | •                                                                                                     | ted: Read as    |                   |                  |                |                      |       |  |  |

| bit 14          |                                                                                                       |                 | Line Filter for W | /ake-up bit      |                |                      |       |  |  |

|                 |                                                                                                       | bus line filter |                   |                  |                |                      |       |  |  |

| L:1 40 44       |                                                                                                       |                 | ot used for wake  | e-up             |                |                      |       |  |  |

| bit 13-11       |                                                                                                       | ted: Read as    |                   |                  |                |                      |       |  |  |

| bit 10-8        |                                                                                                       | )>: Phase Seg   | gment 2 bits      |                  |                |                      |       |  |  |

|                 | 111 = Length                                                                                          | IIS 8 X IQ      |                   |                  |                |                      |       |  |  |

|                 | •                                                                                                     |                 |                   |                  |                |                      |       |  |  |

|                 | •                                                                                                     |                 |                   |                  |                |                      |       |  |  |

|                 | •                                                                                                     |                 |                   |                  |                |                      |       |  |  |

| bit 7           | 000 = Length                                                                                          |                 | ent 2 Time Sele   | ot hit           |                |                      |       |  |  |

|                 | 1 = Freely pro                                                                                        |                 |                   |                  |                |                      |       |  |  |

|                 |                                                                                                       |                 | hits or Informati | ion Processin    | a Time (IPT)   | whichever is greate  | ≥r    |  |  |

| bit 6           |                                                                                                       |                 |                   |                  | ge (ii ),      | inicite for to grout |       |  |  |

| bit o           | <b>SAM:</b> Sample of the CAN bus Line bit<br>1 = Bus line is sampled three times at the sample point |                 |                   |                  |                |                      |       |  |  |

|                 |                                                                                                       |                 | ce at the sampl   |                  |                |                      |       |  |  |

| bit 5-3         |                                                                                                       | )>: Phase Seg   | -                 |                  |                |                      |       |  |  |

|                 | 111 = Length                                                                                          |                 |                   |                  |                |                      |       |  |  |

|                 | •                                                                                                     |                 |                   |                  |                |                      |       |  |  |

|                 | •                                                                                                     |                 |                   |                  |                |                      |       |  |  |

|                 | •                                                                                                     |                 |                   |                  |                |                      |       |  |  |

|                 | 000 = Length                                                                                          | is 1 x Tq       |                   |                  |                |                      |       |  |  |

| bit 2-0         | •                                                                                                     |                 | Time Segmen       | t bits           |                |                      |       |  |  |

|                 | 111 = Length                                                                                          |                 | 0                 |                  |                |                      |       |  |  |

|                 | •                                                                                                     |                 |                   |                  |                |                      |       |  |  |

|                 | •                                                                                                     |                 |                   |                  |                |                      |       |  |  |

|                 | •                                                                                                     |                 |                   |                  |                |                      |       |  |  |

|                 | 000 = Length                                                                                          | is 1 x Tq       |                   |                  |                |                      |       |  |  |

|                 | 5                                                                                                     |                 |                   |                  |                |                      |       |  |  |

| REGISTER      | 19-20: CiRXM<br>REGIS                                          | InSID: ECAN<br>TER n (n = 0                                  |                 | ANCE FILTE       | R MASK STA                                                 | NDARD IDEI | NTIFIER          |

|---------------|----------------------------------------------------------------|--------------------------------------------------------------|-----------------|------------------|------------------------------------------------------------|------------|------------------|

| R/W-x         | R/W-x                                                          | R/W-x                                                        | R/W-x           | R/W-x            | R/W-x                                                      | R/W-x      | R/W-x            |

| SID10         | SID9                                                           | SID8                                                         | SID7            | SID6             | SID5                                                       | SID4       | SID3             |

| bit 15        |                                                                |                                                              |                 |                  |                                                            |            | bit 8            |

| R/W-x         | R/W-x                                                          | R/W-x                                                        | U-0             | R/W-x            | U-0                                                        | R/W-x      | R/W-x            |

| SID2          | SID1                                                           | SID0                                                         | —               | MIDE             |                                                            | EID17      | EID16            |

| bit 7         |                                                                |                                                              |                 |                  |                                                            |            | bit 0            |

|               |                                                                |                                                              |                 |                  |                                                            |            |                  |

| Legend:       |                                                                | C = Writeable                                                | bit, but only ' | 0' can be writte | en to clear the b                                          | bit        |                  |

| R = Readabl   | le bit                                                         | W = Writable                                                 | bit             | U = Unimpler     | mented bit, read                                           | d as '0'   |                  |

| -n = Value at | t POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown |                                                              |                 |                  |                                                            |            | nown             |

| bit 15-5      | 1 = Include bi                                                 | standard Identifi<br>t SIDx in filter c<br>s don't care in f | comparison      | on               |                                                            |            |                  |

| bit 4         | Unimplemen                                                     | ted: Read as 'o                                              | )'              |                  |                                                            |            |                  |

| bit 3         | MIDE: Identif                                                  | ier Receive Mo                                               | de bit          |                  |                                                            |            |                  |

|               | 0 = Match eit                                                  | ner standard or                                              | extended ad     | dress message    | ldress) that corr<br>e if filters match<br>EID) = (Message |            | DE bit in filter |

- bit 2 Unimplemented: Read as '0'

- bit 1-0 EID<17:16>: Extended Identifier bits

- 1 = Include bit EIDx in filter comparison

- 0 = Bit EIDx is don't care in filter comparison

# REGISTER 19-21: CIRXMnEID: ECAN<sup>™</sup> ACCEPTANCE FILTER MASK EXTENDED IDENTIFIER REGISTER n (n = 0-2)

|        |       | •     | •     |       |       |       |       |

|--------|-------|-------|-------|-------|-------|-------|-------|

| R/W-x  | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x |

| EID15  | EID14 | EID13 | EID12 | EID11 | EID10 | EID9  | EID8  |

| bit 15 |       |       |       |       |       |       | bit 8 |

|        |       |       |       |       |       |       |       |

| R/W-x  | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x |

| R/W-x |

|-------|-------|-------|-------|-------|-------|-------|-------|

| EID7  | EID6  | EID5  | EID4  | EID3  | EID2  | EID1  | EID0  |

| bit 7 |       |       |       |       |       |       | bit 0 |

| Legend:           | C = Writeable bit, but only | C = Writeable bit, but only '0' can be written to clear the bit |                    |  |  |  |

|-------------------|-----------------------------|-----------------------------------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit            | U = Unimplemented bit, rea                                      | d as '0'           |  |  |  |

| -n = Value at POR | '1' = Bit is set            | '0' = Bit is cleared                                            | x = Bit is unknown |  |  |  |

bit 15-0 EID<15:0>: Extended Identifier bits

1 = Include bit EIDx in filter comparison

0 = Bit EIDx is don't care in filter comparison

| R/W-0                             | R/W-0 | R/W-0            | R/W-0        | R/W-0                | R/W-0    | R/W-0              | R/W-0 |

|-----------------------------------|-------|------------------|--------------|----------------------|----------|--------------------|-------|

| ADDR15                            | CS1   |                  | 10110        | -                    | R<13:8>  | 1011 0             |       |

| bit 15                            |       |                  |              |                      |          |                    | bit 8 |

| R/W-0                             | R/W-0 | R/W-0            | R/W-0        | R/W-0                | R/W-0    | R/W-0              | R/W-0 |

|                                   |       |                  | ADD          | R<7:0>               |          |                    |       |

| bit 7                             |       |                  |              |                      |          |                    | bit ( |

| Legend:                           |       |                  |              |                      |          |                    |       |

| R = Readable bit W = Writable bit |       | bit              | U = Unimplen | nented bit, rea      | d as '0' |                    |       |

| -n = Value at POR                 |       | '1' = Bit is set |              | '0' = Bit is cleared |          | x = Bit is unknown |       |

| bit 15   | ADDR15: Parallel Port Destination Address bits       |

|----------|------------------------------------------------------|

| bit 14   | CS1: Chip Select 1 bit                               |

|          | 1 = Chip select 1 is active                          |

|          | 0 = Chip select 1 is inactive                        |

| bit 13-0 | ADDR13:ADDR0: Parallel Port Destination Address bits |

## REGISTER 24-4: PMAEN: PARALLEL PORT ENABLE REGISTER

| U-0    | R/W-0  | U-0 | U-0 | U-0 | R/W-0 | R/W-0                     | R/W-0 |

|--------|--------|-----|-----|-----|-------|---------------------------|-------|

| —      | PTEN14 | —   | —   | —   | F     | PTEN<10:8> <sup>(1)</sup> |       |

| bit 15 |        |     |     |     |       |                           | bit 8 |

| R/W-0 | R/W-0                    | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  |

|-------|--------------------------|-------|-------|-------|-------|-------|--------|

|       | PTEN<7:2> <sup>(1)</sup> |       |       |       |       | PTEN  | l<1:0> |

| bit 7 |                          |       |       |       |       |       | bit 0  |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

|                   |                  |                        |                    |

| bit 15    | Unimplemented: Read as '0'                                                                                                                       |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 14    | PTEN14: PMCS1 Strobe Enable bit                                                                                                                  |

|           | <ul> <li>1 = PMA14 functions as either PMA&lt;14&gt; bit or PMCS1</li> <li>0 = PMA14 pin functions as port I/O</li> </ul>                        |

| bit 13-11 | Unimplemented: Read as '0'                                                                                                                       |

| bit 10-2  | PTEN<10:2>: PMP Address Port Enable bits <sup>(1)</sup>                                                                                          |

|           | <ul><li>1 = PMA&lt;10:2&gt; function as PMP address lines</li><li>0 = PMA&lt;10:2&gt; function as port I/O</li></ul>                             |

| bit 1-0   | PTEN<1:0>: PMALH/PMALL Strobe Enable bits                                                                                                        |

|           | <ul> <li>1 = PMA1 and PMA0 function as either PMA&lt;1:0&gt; or PMALH and PMALL</li> <li>0 = PMA1 and PMA0 pads functions as port I/O</li> </ul> |

Note 1: Devices with 28 pins do not have PMA<10:2>.

| IADL               | E 26-2:              | INSTRUCTION SET OVERVIEW (CONTINUED) |                 |                                                            |               |                |                          |  |  |  |  |  |

|--------------------|----------------------|--------------------------------------|-----------------|------------------------------------------------------------|---------------|----------------|--------------------------|--|--|--|--|--|

| Base<br>Instr<br># | Assembly<br>Mnemonic |                                      | Assembly Syntax | Description                                                | # of<br>Words | # of<br>Cycles | Status Flags<br>Affected |  |  |  |  |  |

| 12                 | BTST                 | BTST                                 | f,#bit4         | Bit Test f                                                 | 1             | 1              | Z                        |  |  |  |  |  |

|                    |                      | BTST.C                               | Ws,#bit4        | Bit Test Ws to C                                           | 1             | 1              | С                        |  |  |  |  |  |

|                    |                      | BTST.Z                               | Ws,#bit4        | Bit Test Ws to Z                                           | 1             | 1              | Z                        |  |  |  |  |  |

|                    |                      | BTST.C                               | Ws,Wb           | Bit Test Ws <wb> to C</wb>                                 | 1             | 1              | С                        |  |  |  |  |  |

|                    |                      | BTST.Z                               | Ws,Wb           | Bit Test Ws <wb> to Z</wb>                                 | 1             | 1              | Z                        |  |  |  |  |  |

| 13                 | BTSTS                | BTSTS                                | f,#bit4         | Bit Test then Set f                                        | 1             | 1              | Z                        |  |  |  |  |  |

|                    |                      | BTSTS.C                              | Ws,#bit4        | Bit Test Ws to C, then Set                                 | 1             | 1              | С                        |  |  |  |  |  |

|                    |                      | BTSTS.Z                              | Ws,#bit4        | Bit Test Ws to Z, then Set                                 | 1             | 1              | Z                        |  |  |  |  |  |

| 14                 | CALL                 | CALL                                 | lit23           | Call subroutine                                            | 2             | 2              | None                     |  |  |  |  |  |

|                    |                      | CALL                                 | Wn              | Call indirect subroutine                                   | 1             | 2              | None                     |  |  |  |  |  |

| 15                 | CLR                  | CLR                                  | f               | f = 0x0000                                                 | 1             | 1              | None                     |  |  |  |  |  |

|                    |                      | CLR                                  | WREG            | WREG = 0x0000                                              | 1             | 1              | None                     |  |  |  |  |  |

|                    |                      | CLR                                  | Ws              | Ws = 0x0000                                                | 1             | 1              | None                     |  |  |  |  |  |

| 16                 | CLRWDT               | CLRWDT                               |                 | Clear Watchdog Timer                                       | 1             | 1              | WDTO,Sleep               |  |  |  |  |  |

| 17                 | COM                  | COM                                  | f               | f = f                                                      | 1             | 1              | N,Z                      |  |  |  |  |  |

|                    |                      | СОМ                                  | f,WREG          | WREG = f                                                   | 1             | 1              | N.Z                      |  |  |  |  |  |

|                    |                      | СОМ                                  | Ws,Wd           | $Wd = \overline{Ws}$                                       | 1             | 1              | N,Z                      |  |  |  |  |  |

| 18                 | CP                   | CP                                   | f               | Compare f with WREG                                        | 1             | 1              | C,DC,N,OV,Z              |  |  |  |  |  |

|                    | 01                   | CP                                   | Wb,#lit5        | Compare Wb with lit5                                       | 1             | 1              | C,DC,N,OV,Z              |  |  |  |  |  |

|                    |                      | CP                                   | Wb,Ws           | Compare Wb with Ws (Wb – Ws)                               | 1             | 1              | C,DC,N,OV,Z              |  |  |  |  |  |

| 19                 | CPO                  | CPO                                  | f               | Compare f with 0x0000                                      | 1             | 1              | C,DC,N,OV,Z              |  |  |  |  |  |

| 10                 | 010                  | CPO                                  | Ws              | Compare Ws with 0x0000                                     | 1             | 1              | C,DC,N,OV,Z              |  |  |  |  |  |

| 20                 | CPB                  | CPB                                  | f               | Compare f with WREG, with Borrow                           | 1             | 1              | C,DC,N,OV,Z              |  |  |  |  |  |

| 20                 | 0110                 | CPB                                  | Wb,#lit5        | Compare Wb with lit5, with Borrow                          | 1             | 1              | C,DC,N,OV,Z              |  |  |  |  |  |

|                    |                      | CPB                                  | Wb,Ws           | Compare Wb with Ws, with Borrow $(Wb - Ws - \overline{C})$ | 1             | 1              | C,DC,N,OV,Z              |  |  |  |  |  |

| 21                 | CPSEQ                | CPSEQ                                | Wb, Wn          | Compare Wb with Wn, skip if =                              | 1             | 1<br>(2 or 3)  | None                     |  |  |  |  |  |

| 22                 | CPSGT                | CPSGT                                | Wb, Wn          | Compare Wb with Wn, skip if >                              | 1             | 1<br>(2 or 3)  | None                     |  |  |  |  |  |

| 23                 | CPSLT                | CPSLT                                | Wb, Wn          | Compare Wb with Wn, skip if <                              | 1             | 1<br>(2 or 3)  | None                     |  |  |  |  |  |

| 24                 | CPSNE                | CPSNE                                | Wb, Wn          | Compare Wb with Wn, skip if ≠                              | 1             | 1<br>(2 or 3)  | None                     |  |  |  |  |  |

| 25                 | DAW                  | DAW                                  | Wn              | Wn = decimal adjust Wn                                     | 1             | 1              | С                        |  |  |  |  |  |

| 26                 | DEC                  | DEC                                  | f               | f = f - 1                                                  | 1             | 1              | C,DC,N,OV,Z              |  |  |  |  |  |

|                    |                      | DEC                                  | f,WREG          | WREG = f – 1                                               | 1             | 1              | C,DC,N,OV,Z              |  |  |  |  |  |

|                    |                      | DEC                                  | Ws,Wd           | Wd = Ws - 1                                                | 1             | 1              | C,DC,N,OV,Z              |  |  |  |  |  |

| 27                 | DEC2                 | DEC2                                 | f               | f = f - 2                                                  | 1             | 1              | C,DC,N,OV,Z              |  |  |  |  |  |

|                    |                      | DEC2                                 | f,WREG          | WREG = f – 2                                               | 1             | 1              | C,DC,N,OV,Z              |  |  |  |  |  |

|                    |                      | DEC2                                 | Ws,Wd           | Wd = Ws - 2                                                | 1             | 1              | C,DC,N,OV,Z              |  |  |  |  |  |

| 28                 | DISI                 | DISI                                 | #lit14          | Disable Interrupts for k instruction cycles                | 1             | 1              | None                     |  |  |  |  |  |

| 29                 | DIV                  | DIV.S                                | Wm,Wn           | Signed 16/16-bit Integer Divide                            | 1             | 18             | N,Z,C,OV                 |  |  |  |  |  |

|                    |                      | DIV.SD                               | Wm,Wn           | Signed 32/16-bit Integer Divide                            | 1             | 18             | N,Z,C,OV                 |  |  |  |  |  |

|                    |                      | DIV.U                                | Wm,Wn           | Unsigned 16/16-bit Integer Divide                          | 1             | 18             | N,Z,C,OV                 |  |  |  |  |  |

|                    |                      | DIV.UD                               | Wm,Wn           | Unsigned 32/16-bit Integer Divide                          | 1             | 18             | N,Z,C,OV                 |  |  |  |  |  |

| 30                 | EXCH                 | EXCH                                 | Wns,Wnd         | Swap Wns with Wnd                                          | 1             | 1              | None                     |  |  |  |  |  |

| 31                 | FBCL                 | FBCL                                 | Ws,Wnd          | Find Bit Change from Left (MSb) Side                       | 1             | 1              | С                        |  |  |  |  |  |

| 32                 | FF1L                 | FF1L                                 | Ws,Wnd          | Find First One from Left (MSb) Side                        | 1             | 1              | С                        |  |  |  |  |  |

| 33                 | FF1R                 | FF1R                                 | Ws,Wnd          | Find First One from Right (LSb) Side                       | 1             | 1              | С                        |  |  |  |  |  |

| 34                 | GOTO                 | GOTO                                 | Expr            | Go to address                                              | 2             | 2              | None                     |  |  |  |  |  |

|                    |                      | GOTO                                 | Wn              | Go to indirect                                             | 1             | 2              | None                     |  |  |  |  |  |

### TABLE 26-2: INSTRUCTION SET OVERVIEW (CONTINUED)

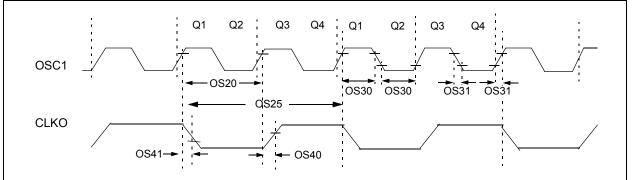

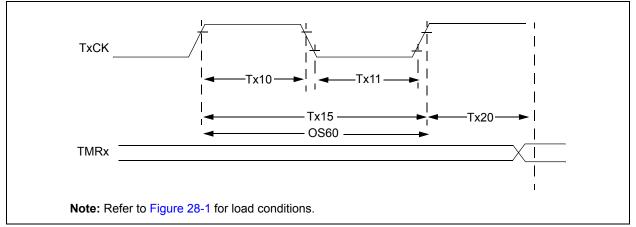

### FIGURE 28-2: EXTERNAL CLOCK TIMING

### TABLE 28-16: EXTERNAL CLOCK TIMING REQUIREMENTS

| AC CHARACTERISTICS |               |                                                                                    | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |                    |                |                   |                          |  |  |

|--------------------|---------------|------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|----------------|-------------------|--------------------------|--|--|

| Param<br>No.       | Symb          | Characteristic                                                                     | Min                                                                                                                                                                                                                                                                                     | Typ <sup>(1)</sup> | Мах            | Units             | Conditions               |  |  |

| OS10               | Fin           | External CLKI Frequency<br>(External clocks allowed only<br>in EC and ECPLL modes) | DC                                                                                                                                                                                                                                                                                      | _                  | 40             | MHz               | EC                       |  |  |

|                    |               | Oscillator Crystal Frequency                                                       | 3.5<br>10                                                                                                                                                                                                                                                                               |                    | 10<br>40<br>33 | MHz<br>MHz<br>kHz | XT<br>HS<br>Sosc         |  |  |

| OS20               | Tosc          | Tosc = 1/Fosc                                                                      | 12.5                                                                                                                                                                                                                                                                                    |                    | DC             | ns                |                          |  |  |

| OS25               | TCY           | Instruction Cycle Time <sup>(2)</sup>                                              | 25                                                                                                                                                                                                                                                                                      |                    | DC             | ns                |                          |  |  |

| OS30               | TosL,<br>TosH | External Clock in (OSC1)<br>High or Low Time                                       | 0.375 x Tosc                                                                                                                                                                                                                                                                            | —                  | 0.625 x Tosc   | ns                | EC                       |  |  |

| OS31               | TosR,<br>TosF | External Clock in (OSC1)<br>Rise or Fall Time                                      | -                                                                                                                                                                                                                                                                                       | —                  | 20             | ns                | EC                       |  |  |

| OS40               | TckR          | CLKO Rise Time <sup>(3)</sup>                                                      |                                                                                                                                                                                                                                                                                         | 5.2                |                | ns                | —                        |  |  |

| OS41               | TckF          | CLKO Fall Time <sup>(3)</sup>                                                      | —                                                                                                                                                                                                                                                                                       | 5.2                | —              | ns                | —                        |  |  |

| OS42               | Gм            | External Oscillator<br>Transconductance <sup>(4)</sup>                             | 14                                                                                                                                                                                                                                                                                      | 16                 | 18             | mA/V              | VDD = 3.3V<br>TA = +25°C |  |  |

Note 1: Data in "Typ" column is at 3.3V, 25°C unless otherwise stated.

2: Instruction cycle period (TcY) equals two times the input oscillator time-base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min." values with an external clock applied to the OSC1/CLKI pin. When an external clock input is used, the "max." cycle time limit is "DC" (no clock) for all devices.

- 3: Measurements are taken in EC mode. The CLKO signal is measured on the OSC2 pin.

- 4: Data for this parameter is Preliminary. This parameter is characterized, but not tested in manufacturing.

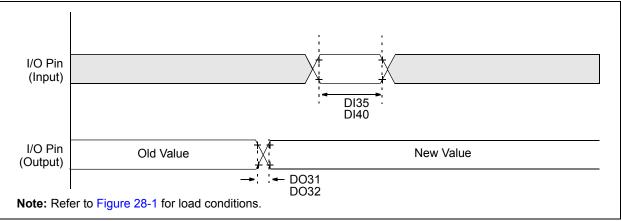

### FIGURE 28-3: CLKO AND I/O TIMING CHARACTERISTICS

### TABLE 28-20: I/O TIMING REQUIREMENTS

| AC CHARACTERISTICS |        |                                   | Standard Oper<br>(unless otherw<br>Operating temp | vise state | <b>ed)</b><br>-40°C ≤ | Ta ≤+85 | <b>3.6V</b><br>°C for Inc<br>5°C for E |            |

|--------------------|--------|-----------------------------------|---------------------------------------------------|------------|-----------------------|---------|----------------------------------------|------------|