# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Active                                                                        |

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 40 MIPs                                                                       |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                  |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                    |

| Number of I/O              | 21                                                                            |

| Program Memory Size        | 64KB (22K x 24)                                                               |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 8K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                     |

| Data Converters            | A/D 10x10b/12b                                                                |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

| Mounting Type              | Through Hole                                                                  |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                       |

| Supplier Device Package    | 28-SPDIP                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24hj64gp502-i-sp |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Table of Contents**

| PIC2  | 4HJ32GP302/304, PIC24HJ64GPX02/X04 and PIC24HJ128GPX02/X04 Product Families |     |

|-------|-----------------------------------------------------------------------------|-----|

| 1.0   | Device Overview                                                             |     |

| 2.0   | Guidelines for Getting Started with 16-bit Microcontrollers                 |     |

| 3.0   | СРИ                                                                         |     |

| 4.0   | Memory Organization                                                         |     |

| 5.0   | Flash Program Memory                                                        |     |

| 6.0   | Resets                                                                      |     |

| 7.0   | Interrupt Controller                                                        |     |

| 8.0   | Direct Memory Access (DMA)                                                  | 107 |

| 9.0   | Oscillator Configuration                                                    | 119 |

| 10.0  | Power-Saving Features                                                       | 129 |

| 11.0  | I/O Ports                                                                   | 135 |

| 12.0  | Timer1                                                                      | 161 |

| 13.0  |                                                                             |     |

| 14.0  | Input Capture                                                               |     |

| 15.0  | Output Compare                                                              | 175 |

| 16.0  | Serial Peripheral Interface (SPI)                                           | 179 |

| 17.0  | Inter-Integrated Circuit™ (I <sup>2</sup> C™)                               | 185 |

| 18.0  | Universal Asynchronous Receiver Transmitter (UART)                          | 193 |

| 19.0  | Enhanced CAN (ECAN™) Module                                                 | 199 |

| 20.0  | 10-bit/12-bit Analog-to-Digital Converter (ADC1)                            |     |

| 21.0  | Comparator Module                                                           |     |

| 22.0  | Real-Time Clock and Calendar (RTCC)                                         |     |

| 23.0  | Programmable Cyclic Redundancy Check (CRC) Generator                        |     |

| 24.0  | Parallel Master Port (PMP)                                                  |     |

|       | Special Features                                                            |     |

| 26.0  | Instruction Set Summary                                                     |     |

| 27.0  | Development Support                                                         |     |

|       | Electrical Characteristics                                                  |     |

| 29.0  | High Temperature Electrical Characteristics                                 |     |

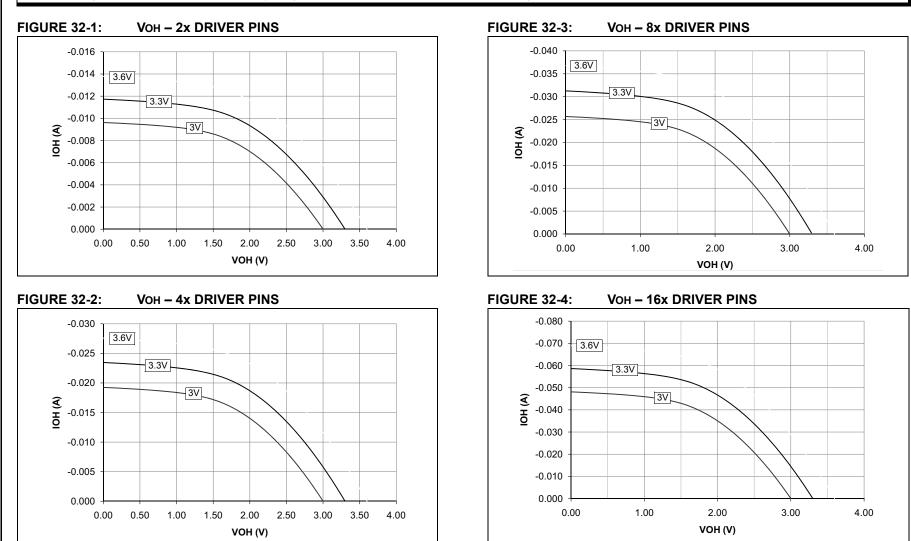

| 32.0  | DC and AC Device Characteristics Graphs                                     |     |

| 33.0  | Packaging Information                                                       |     |

| Appe  | endix A: Revision History                                                   |     |

| The I | Microchip Web Site                                                          |     |

| Custo | omer Change Notification Service                                            |     |

| Custo | omer Support                                                                |     |

| Read  | ler Response                                                                |     |

| Prod  | uct Identification System                                                   |     |

## FIGURE 7-1: PIC24HJ32GP302/304, PIC24HJ64GPX02/X04 and PIC24HJ128GPX02/X04 INTERRUPT VECTOR TABLE

|                                   |                                       | _                 |                                                        |

|-----------------------------------|---------------------------------------|-------------------|--------------------------------------------------------|

|                                   | Reset – GOTO Instruction              | 0x000000          |                                                        |

|                                   | Reset – GOTO Address                  | 0x000002          |                                                        |

|                                   | Reserved                              | 0x000004          |                                                        |

|                                   | Oscillator Fail Trap Vector           |                   |                                                        |

|                                   | Address Error Trap Vector             |                   |                                                        |

|                                   | Stack Error Trap Vector               |                   |                                                        |

|                                   | Math Error Trap Vector                |                   |                                                        |

|                                   | DMA Error Trap Vector                 |                   |                                                        |

|                                   | Reserved                              |                   |                                                        |

|                                   | Reserved                              |                   |                                                        |

|                                   | Interrupt Vector 0                    | 0x000014          |                                                        |

|                                   | Interrupt Vector 1                    |                   |                                                        |

|                                   | ~                                     |                   |                                                        |

|                                   | ~                                     | 1                 |                                                        |

|                                   | ~                                     |                   |                                                        |

|                                   | Interrupt Vector 52                   | 0x00007C          | $l_{1}$                                                |

|                                   | Interrupt Vector 53                   | 0x00007E          | Interrupt Vector Table (IVT) <sup>(1)</sup>            |

| ity                               | Interrupt Vector 54                   | 0x000080          |                                                        |

| ior                               | ~                                     |                   |                                                        |

| ā                                 | ~                                     |                   |                                                        |

| dei                               | ~                                     |                   |                                                        |

| Decreasing Natural Order Priority | Interrupt Vector 116                  | 0x0000FC          |                                                        |

| ral                               | Interrupt Vector 117                  | 0x0000FE          | •                                                      |

| atu                               | Reserved                              | 0x000100          |                                                        |

| ž                                 | Reserved                              | 0x000102          |                                                        |

| ing                               | Reserved                              |                   |                                                        |

| as                                | Oscillator Fail Trap Vector           |                   |                                                        |

| cre                               | Address Error Trap Vector             |                   |                                                        |

| De                                | Stack Error Trap Vector               | -                 |                                                        |

|                                   | Math Error Trap Vector                | _                 |                                                        |

|                                   | DMA Error Trap Vector                 | _                 |                                                        |

|                                   | Reserved                              |                   | ]                                                      |

|                                   | Reserved                              |                   |                                                        |

|                                   | Interrupt Vector 0                    | 0x000114          |                                                        |

|                                   | Interrupt Vector 1                    |                   |                                                        |

|                                   | ~                                     | -                 |                                                        |

|                                   | ~                                     |                   |                                                        |

|                                   | ~                                     |                   | Alternate Interrupt Vector Table (AIVT) <sup>(1)</sup> |

|                                   | Interrupt Vector 52                   | 0x00017C          |                                                        |

|                                   | Interrupt Vector 53                   | 0x00017E          |                                                        |

|                                   | Interrupt Vector 54                   | 0x000180          |                                                        |

|                                   | ~                                     |                   |                                                        |

|                                   | ~                                     |                   |                                                        |

|                                   | ~                                     |                   |                                                        |

|                                   | Interrupt Vector 116                  | 1 –               | -                                                      |

|                                   | Interrupt Vector 117                  | 0x0001FE          |                                                        |

| V                                 | Start of Code                         | 0x000200          |                                                        |

|                                   |                                       | -                 |                                                        |

|                                   |                                       |                   |                                                        |

|                                   |                                       |                   |                                                        |

| Note 1: S                         | See Table 7-1 for the list of impleme | ented interrupt v | vectors.                                               |

|                                   |                                       |                   |                                                        |

|                                   |                                       |                   |                                                        |

| TABLE 7-1:       | INTERRUPT VECT    | UKS               |                                    |

|------------------|-------------------|-------------------|------------------------------------|

| Vector<br>Number | IVT Address       | AIVT Address      | Interrupt Source                   |

| 0                | 0x000004          | 0x000104          | Reserved                           |

| 1                | 0x000006          | 0x000106          | Oscillator Failure                 |

| 2                | 0x00008           | 0x000108          | Address Error                      |

| 3                | 0x00000A          | 0x00010A          | Stack Error                        |

| 4                | 0x00000C          | 0x00010C          | Math Error                         |

| 5                | 0x00000E          | 0x00010E          | DMA Error                          |

| 6-7              | 0x000010-0x000012 | 0x000110-0x000112 | Reserved                           |

| 8                | 0x000014          | 0x000114          | INT0 – External Interrupt 0        |

| 9                | 0x000016          | 0x000116          | IC1 – Input Capture 1              |

| 10               | 0x000018          | 0x000118          | OC1 – Output Compare 1             |

| 11               | 0x00001A          | 0x00011A          | T1 – Timer1                        |

| 12               | 0x00001C          | 0x00011C          | DMA0 – DMA Channel 0               |

| 13               | 0x00001E          | 0x00011E          | IC2 – Input Capture 2              |

| 14               | 0x000020          | 0x000120          | OC2 – Output Compare 2             |

| 15               | 0x000022          | 0x000122          | T2 – Timer2                        |

| 16               | 0x000024          | 0x000124          | T3 – Timer3                        |

| 17               | 0x000026          | 0x000126          | SPI1E – SPI1 Error                 |

| 18               | 0x000028          | 0x000128          | SPI1 – SPI1 Transfer Done          |

| 19               | 0x00002A          | 0x00012A          | U1RX – UART1 Receiver              |

| 20               | 0x00002C          | 0x00012C          | U1TX – UART1 Transmitter           |

| 21               | 0x00002E          | 0x00012E          | ADC1 – ADC 1                       |

| 22               | 0x000030          | 0x000130          | DMA1 – DMA Channel 1               |

| 23               | 0x000032          | 0x000132          | Reserved                           |

| 24               | 0x000034          | 0x000134          | SI2C1 – I2C1 Slave Events          |

| 25               | 0x000036          | 0x000136          | MI2C1 – I2C1 Master Events         |

| 26               | 0x000038          | 0x000138          | CM – Comparator Interrupt          |

| 27               | 0x00003A          | 0x00013A          | CN – Change Notification Interrupt |

| 28               | 0x00003C          | 0x00013C          | INT1 – External Interrupt 1        |

| 29               | 0x00003E          | 0x00013E          | Reserved                           |

| 30               | 0x000040          | 0x000140          | IC7 – Input Capture 7              |

| 31               | 0x000042          | 0x000142          | IC8 – Input Capture 8              |

| 32               | 0x000044          | 0x000144          | DMA2 – DMA Channel 2               |

| 33               | 0x000046          | 0x000146          | OC3 – Output Compare 3             |

| 34               | 0x000048          | 0x000148          | OC4 – Output Compare 4             |

| 35               | 0x00004A          | 0x00014A          | T4 – Timer4                        |

| 36               | 0x00004C          | 0x00014C          | T5 – Timer5                        |

| 37               | 0x00004E          | 0x00014E          | INT2 – External Interrupt 2        |

| 38               | 0x000050          | 0x000150          | U2RX – UART2 Receiver              |

| 39               | 0x000052          | 0x000152          | U2TX – UART2 Transmitter           |

| 40               | 0x000054          | 0x000154          | SPI2E – SPI2 Error                 |

| 41               | 0x000056          | 0x000156          | SPI2 – SPI2 Transfer Done          |

| 42               | 0x000058          | 0x000158          | C1RX – ECAN1 RX Data Ready         |

| 43               | 0x00005A          | 0x00015A          | C1 – ECAN1 Event                   |

| 44               | 0x00005C          | 0x00015C          | DMA3 – DMA Channel 3               |

| 45-52            | 0x00005E-0x00006C | 0x00015E-0x00016C | Reserved                           |

| 53               | 0x00006E          | 0x00016E          | PMP – Parallel Master Port         |

| 54               | 0x000070          | 0x000170          | DMA – DMA Channel 4                |

TABLE 7-1: INTERRUPT VECTORS

| Vector<br>Number | IVT Address       | AIVT Address      | Interrupt Source              |  |  |  |  |

|------------------|-------------------|-------------------|-------------------------------|--|--|--|--|

| 55-68            | 0x000072-0x00008C | 0x000172-0x00018C | Reserved                      |  |  |  |  |

| 69               | 0x00008E          | 0x00018E          | DMA5 – DMA Channel 5          |  |  |  |  |

| 70               | 0x000090          | 0x000190          | RTCC – Real Time Clock        |  |  |  |  |

| 71-72            | 0x000092-0x000094 | 0x000192-0x000194 | Reserved                      |  |  |  |  |

| 73               | 0x000096          | 0x000196          | U1E – UART1 Error             |  |  |  |  |

| 74               | 0x000098          | 0x000198          | U2E – UART2 Error             |  |  |  |  |

| 75               | 0x00009A          | 0x00019A          | CRC – CRC Generator Interrupt |  |  |  |  |

| 76               | 0x00009C          | 0x00019C          | DMA6 – DMA Channel 6          |  |  |  |  |

| 77               | 0x00009E          | 0x00019E          | DMA7 – DMA Channel 7          |  |  |  |  |

| 78               | 0x0000A0          | 0x0001A0          | C1TX – ECAN1 TX Data Request  |  |  |  |  |

| 79-126           | 0x0000A2-0x0000FE | 0x0001A2-0x0001FE | Reserved                      |  |  |  |  |

#### TABLE 7-1: INTERRUPT VECTORS (CONTINUED)

## REGISTER 7-6: IFS1: INTERRUPT FLAG STATUS REGISTER 1 (CONTINUED)

| bit 2 | CMIF: Comparator Interrupt Flag Status bit                                                             |

|-------|--------------------------------------------------------------------------------------------------------|

|       | <ul><li>1 = Interrupt request has occurred</li><li>0 = Interrupt request has not occurred</li></ul>    |

| bit 1 | MI2C1IF: I2C1 Master Events Interrupt Flag Status bit                                                  |

|       | <ol> <li>1 = Interrupt request has occurred</li> <li>0 = Interrupt request has not occurred</li> </ol> |

| bit 0 | SI2C1IF: I2C1 Slave Events Interrupt Flag Status bit                                                   |

|       | <ul><li>1 = Interrupt request has occurred</li><li>0 = Interrupt request has not occurred</li></ul>    |

| REGISTER              | (/-9: IFS4:I                       | NIERRUPI                                                                                                                  | FLAGSIAI       | US REGISTE       | =R 4                      |                 |       |  |  |  |  |

|-----------------------|------------------------------------|---------------------------------------------------------------------------------------------------------------------------|----------------|------------------|---------------------------|-----------------|-------|--|--|--|--|

| U-0                   | U-0                                | U-0                                                                                                                       | U-0            | U-0              | U-0                       | U-0             | U-0   |  |  |  |  |

| _                     | —                                  | —                                                                                                                         | —              | —                | —                         | —               | _     |  |  |  |  |

| bit 15                |                                    |                                                                                                                           |                |                  |                           |                 | bit 8 |  |  |  |  |

| U-0                   | R/W-0                              | R/W-0                                                                                                                     | R/W-0          | R/W-0            | R/W-0                     | R/W-0           | U-0   |  |  |  |  |

| —                     | C1TXIF <sup>(1)</sup>              | DMA7IF                                                                                                                    | DMA6IF         | CRCIF            | U2EIF                     | U1EIF           | —     |  |  |  |  |

| bit 7                 |                                    |                                                                                                                           |                |                  |                           |                 | bit C |  |  |  |  |

| Logondi               |                                    |                                                                                                                           |                |                  |                           |                 |       |  |  |  |  |

| Legend:<br>R = Readab | le hit                             | W = Writable                                                                                                              | hit            | II – I Inimpler  | nented bit, read          | ae 'O'          |       |  |  |  |  |

|                       |                                    |                                                                                                                           |                | '0' = Bit is cle |                           |                 |       |  |  |  |  |

| -n = Value a          | at POR                             | '1' = Bit is set                                                                                                          |                | 0 = Bit is cie   | ared                      | x = Bit is unkn | own   |  |  |  |  |

| bit 15-7              | Unimplemen                         | ted: Read as '                                                                                                            | 0'             |                  |                           |                 |       |  |  |  |  |

| bit 6                 | C1TXIF: ECA                        | N1 Transmit D                                                                                                             | ata Request I  | nterrupt Flag S  | status bit <sup>(1)</sup> |                 |       |  |  |  |  |

|                       |                                    | <b>C1TXIF:</b> ECAN1 Transmit Data Request Interrupt Flag Status bit <sup>(1)</sup><br>1 = Interrupt request has occurred |                |                  |                           |                 |       |  |  |  |  |

|                       |                                    | equest has no                                                                                                             |                |                  |                           |                 |       |  |  |  |  |

| bit 5                 | DMA7IF: DM                         | A Channel 7 D                                                                                                             | ata Transfer C | Complete Interr  | upt Flag Status           | bit             |       |  |  |  |  |

|                       | 1 = Interrupt r                    | 1 = Interrupt request has occurred                                                                                        |                |                  |                           |                 |       |  |  |  |  |

|                       | 0 = Interrupt r                    | equest has no                                                                                                             | t occurred     |                  |                           |                 |       |  |  |  |  |

| bit 4                 | DMA6IF: DM                         | A Channel 6 D                                                                                                             | ata Transfer C | Complete Interr  | upt Flag Status           | bit             |       |  |  |  |  |

|                       | 1 = Interrupt request has occurred |                                                                                                                           |                |                  |                           |                 |       |  |  |  |  |

|                       |                                    | equest has no                                                                                                             |                |                  |                           |                 |       |  |  |  |  |

| bit 3                 |                                    | Generator Inte                                                                                                            | , ,            | itus bit         |                           |                 |       |  |  |  |  |

|                       |                                    | 1 = Interrupt request has occurred                                                                                        |                |                  |                           |                 |       |  |  |  |  |

|                       | •                                  | equest has no                                                                                                             |                |                  |                           |                 |       |  |  |  |  |

| bit 2                 |                                    | U2EIF: UART2 Error Interrupt Flag Status bit                                                                              |                |                  |                           |                 |       |  |  |  |  |

|                       |                                    | equest has oc<br>equest has no                                                                                            |                |                  |                           |                 |       |  |  |  |  |

| hit 1                 | -                                  | -                                                                                                                         |                | hit              |                           |                 |       |  |  |  |  |

| bit 1                 |                                    | 1 Error Interru                                                                                                           |                | DIL              |                           |                 |       |  |  |  |  |

|                       |                                    | equest has oc<br>equest has no                                                                                            |                |                  |                           |                 |       |  |  |  |  |

|                       |                                    |                                                                                                                           |                |                  |                           |                 |       |  |  |  |  |

| REGISTER 7-9: | FS4: INTERRUPT FLAG STATUS REGISTER 4 |

|---------------|---------------------------------------|

|---------------|---------------------------------------|

Note 1: Interrupts disabled on devices without ECAN<sup>™</sup> modules.

Unimplemented: Read as '0'

bit 0

| U-0          | R/W-1                                                                                                                      | R/W-0                                    | R/W-0          | U-0                    | R/W-1          | R/W-0           | R/W-0 |  |  |  |

|--------------|----------------------------------------------------------------------------------------------------------------------------|------------------------------------------|----------------|------------------------|----------------|-----------------|-------|--|--|--|

| _            |                                                                                                                            | C1IP<2:0> <sup>(1)</sup>                 |                | _                      |                | C1RXIP<2:0>(1)  |       |  |  |  |

| bit 15       | •                                                                                                                          |                                          |                |                        |                |                 | bit 8 |  |  |  |

|              |                                                                                                                            |                                          |                |                        |                |                 |       |  |  |  |

| U-0          | R/W-1                                                                                                                      | R/W-0                                    | R/W-0          | U-0                    | R/W-1          | R/W-0           | R/W-0 |  |  |  |

| —            |                                                                                                                            | SPI2IP<2:0>                              |                | _                      |                | SPI2EIP<2:0>    |       |  |  |  |

| bit 7        |                                                                                                                            |                                          |                |                        |                |                 | bit C |  |  |  |

| Legend:      |                                                                                                                            |                                          |                |                        |                |                 |       |  |  |  |

| R = Readab   | le bit                                                                                                                     | W = Writable b                           | oit            | U = Unimple            | mented bit, re | ead as '0'      |       |  |  |  |

| -n = Value a | t POR                                                                                                                      | '1' = Bit is set                         |                | '0' = Bit is cle       |                | x = Bit is unkn | own   |  |  |  |

|              |                                                                                                                            |                                          |                |                        |                |                 |       |  |  |  |

| bit 15       | Unimpleme                                                                                                                  | ented: Read as '0                        | ,              |                        |                |                 |       |  |  |  |

| bit 14-12    | C1IP<2:0>:                                                                                                                 | ECAN1 Event In                           | terrupt Priori | ty bits <sup>(1)</sup> |                |                 |       |  |  |  |

|              | 111 = Interr                                                                                                               | rupt is priority 7 (h                    | nighest priori | ty interrupt)          |                |                 |       |  |  |  |

|              | •                                                                                                                          |                                          |                |                        |                |                 |       |  |  |  |

|              | •                                                                                                                          |                                          |                |                        |                |                 |       |  |  |  |

|              | 001 = Interrupt is priority 1                                                                                              |                                          |                |                        |                |                 |       |  |  |  |

|              |                                                                                                                            | rupt source is disa                      |                |                        |                |                 |       |  |  |  |

| bit 11       |                                                                                                                            | ented: Read as '0                        |                |                        |                |                 |       |  |  |  |

| bit 10-8     | C1RXIP<2:0>: ECAN1 Receive Data Ready Interrupt Priority bits <sup>(1)</sup>                                               |                                          |                |                        |                |                 |       |  |  |  |

|              | 111 = Interrupt is priority 7 (highest priority interrupt)                                                                 |                                          |                |                        |                |                 |       |  |  |  |

|              | •                                                                                                                          |                                          |                |                        |                |                 |       |  |  |  |

|              | •                                                                                                                          |                                          |                |                        |                |                 |       |  |  |  |

|              | 001 = Interrupt is priority 1<br>000 = Interrupt source is disabled                                                        |                                          |                |                        |                |                 |       |  |  |  |

| h:+ 7        |                                                                                                                            | •                                        |                |                        |                |                 |       |  |  |  |

| bit 7        | -                                                                                                                          | ented: Read as '0                        |                | . hite                 |                |                 |       |  |  |  |

| bit 6-4      | <b>SPI2IP&lt;2:0&gt;:</b> SPI2 Event Interrupt Priority bits<br>111 = Interrupt is priority 7 (highest priority interrupt) |                                          |                |                        |                |                 |       |  |  |  |

|              | •                                                                                                                          |                                          | lighest phon   | ly interrupt)          |                |                 |       |  |  |  |

|              | •                                                                                                                          |                                          |                |                        |                |                 |       |  |  |  |

|              | •<br>001 = Interrupt is priority 1                                                                                         |                                          |                |                        |                |                 |       |  |  |  |

|              |                                                                                                                            | rupt source is disa                      | abled          |                        |                |                 |       |  |  |  |

| bit 3        |                                                                                                                            | ented: Read as '0                        |                |                        |                |                 |       |  |  |  |

| bit 2-0      | -                                                                                                                          | :0>: SPI2 Error In                       |                | tv bits                |                |                 |       |  |  |  |

|              |                                                                                                                            | rupt is priority 7 (h                    |                | •                      |                |                 |       |  |  |  |

|              | •                                                                                                                          |                                          | -              |                        |                |                 |       |  |  |  |

|              | •                                                                                                                          |                                          |                |                        |                |                 |       |  |  |  |

|              | 001 = Interr                                                                                                               | rupt is priority 1                       |                |                        |                |                 |       |  |  |  |

|              |                                                                                                                            | rupt io priority i<br>rupt course is die |                |                        |                |                 |       |  |  |  |

## 000 = Interrupt source is disabled

Note 1: Interrupts disabled on devices without ECAN<sup>™</sup> modules.

| REGISTER 8-5: | DMAxPAD: DMA CHANNEL x PERIPHERAL ADDRESS REGISTER <sup>(1)</sup> |

|---------------|-------------------------------------------------------------------|

|               |                                                                   |

| R/W-0                                                           | R/W-0 | R/W-0 | R/W-0           | R/W-0                              | R/W-0 | R/W-0 | R/W-0 |

|-----------------------------------------------------------------|-------|-------|-----------------|------------------------------------|-------|-------|-------|

|                                                                 |       |       | PAD             | <15:8>                             |       |       |       |

| bit 15                                                          |       |       |                 |                                    |       |       | bit 8 |

|                                                                 |       |       |                 |                                    |       |       |       |

| R/W-0                                                           | R/W-0 | R/W-0 | R/W-0           | R/W-0                              | R/W-0 | R/W-0 | R/W-0 |

|                                                                 |       |       | PAE             | )<7:0>                             |       |       |       |

| bit 7                                                           |       |       |                 |                                    |       |       | bit 0 |

|                                                                 |       |       |                 |                                    |       |       |       |

| Legend:                                                         |       |       |                 |                                    |       |       |       |

| R = Readable bit W = Writable bit                               |       |       | bit             | U = Unimplemented bit, read as '0' |       |       |       |

| -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit |       |       | x = Bit is unkr | nown                               |       |       |       |

|                                                                 |       |       |                 |                                    |       |       |       |

bit 15-0 PAD<15:0>: Peripheral Address Register bits

**Note 1:** If the channel is enabled (i.e., active), writes to this register may result in unpredictable behavior of the DMA channel and should be avoided.

### REGISTER 8-6: DMAxCNT: DMA CHANNEL x TRANSFER COUNT REGISTER<sup>(1)</sup>

| U-0                                                                  | U-0   | U-0             | U-0                                | U-0                  | U-0   | R/W-0 | R/W-0               |

|----------------------------------------------------------------------|-------|-----------------|------------------------------------|----------------------|-------|-------|---------------------|

| —                                                                    |       | —               | _                                  | —                    | —     | CNT<  | 9:8> <sup>(2)</sup> |

| bit 15                                                               |       |                 |                                    |                      |       | ·     | bit 8               |

|                                                                      |       |                 |                                    |                      |       |       |                     |

| R/W-0                                                                | R/W-0 | R/W-0           | R/W-0                              | R/W-0                | R/W-0 | R/W-0 | R/W-0               |

|                                                                      |       |                 | CNT                                | <7:0> <sup>(2)</sup> |       |       |                     |

| bit 7                                                                |       |                 |                                    |                      |       |       | bit 0               |

|                                                                      |       |                 |                                    |                      |       |       |                     |

| Legend:                                                              |       |                 |                                    |                      |       |       |                     |

| R = Readable bit W = Writable bit                                    |       | bit             | U = Unimplemented bit, read as '0' |                      |       |       |                     |

| -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is u |       | x = Bit is unkr | nown                               |                      |       |       |                     |

bit 15-10 Unimplemented: Read as '0'

bit 9-0 CNT<9:0>: DMA Transfer Count Register bits<sup>(2)</sup>

**Note 1:** If the channel is enabled (i.e., active), writes to this register may result in unpredictable behavior of the DMA channel and should be avoided.

2: Number of DMA transfers = CNT<9:0> + 1.

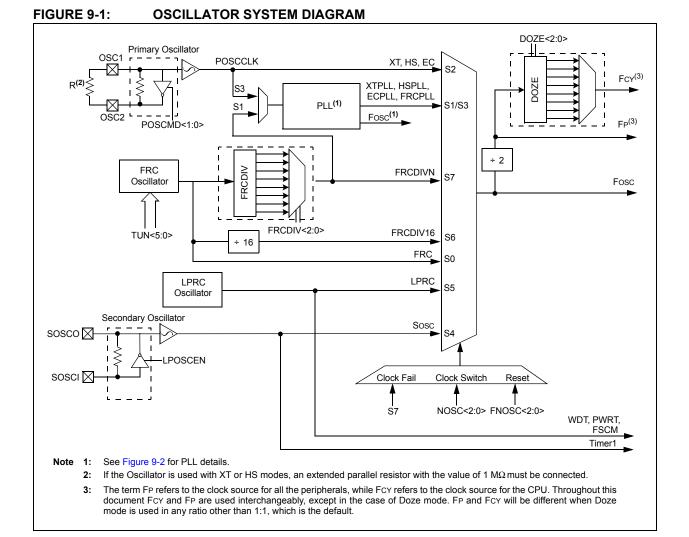

## 9.0 OSCILLATOR CONFIGURATION

- Note 1: This data sheet summarizes the features PIC24HJ32GP302/304 of the PIC24HJ64GPX02/X04 and PIC24HJ128GPX02/X04 families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 39. "Oscillator (Part III)" (DS70216) of the "dsPIC33F/ PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The PIC24HJ32GP302/304, PIC24HJ64GPX02/X04 and PIC24HJ128GPX02/X04 oscillator system provides:

- External and internal oscillator options as clock sources

- An on-chip Phase-Locked Loop (PLL) to scale the internal operating frequency to the required system clock frequency

- An internal FRC oscillator that can also be used with the PLL, thereby allowing full-speed operation without any external clock generation hardware

- Clock switching between various clock sources

- Programmable clock postscaler for system power savings

- A Fail-Safe Clock Monitor (FSCM) that detects clock failure and takes fail-safe measures

- An Oscillator Control register (OSCCON)

- Nonvolatile Configuration bits for main oscillator selection.

- A simplified diagram of the oscillator system is shown in Figure 9-1.

#### 11.6.3 CONTROLLING CONFIGURATION CHANGES

Because peripheral remapping can be changed during run time, some restrictions on peripheral remapping are needed to prevent accidental configuration changes. PIC24H devices include three features to prevent alterations to the peripheral map:

- Control register lock sequence

- · Continuous state monitoring

- Configuration bit pin select lock

#### 11.6.3.1 Control Register Lock

Under normal operation, writes to the RPINRx and RPORx registers are not allowed. Attempted writes appear to execute normally, but the contents of the registers remain unchanged. To change these registers, they must be unlocked in hardware. The register lock is controlled by the IOLOCK bit (OSCCON<6>). Setting IOLOCK prevents writes to the control registers; clearing IOLOCK allows writes.

To set or clear IOLOCK, a specific command sequence must be executed:

- 1. Write 0x46 to OSCCON<7:0>.

- 2. Write 0x57 to OSCCON<7:0>.

- 3. Clear (or set) the IOLOCK bit as a single operation.

| Note: | MPLAB <sup>®</sup> C30 provides built-in C language functions for unlocking the OSCCON register: |  |  |  |  |  |  |

|-------|--------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

|       | builtin_write_OSCCONL(value)<br>builtin_write_OSCCONH(value)                                     |  |  |  |  |  |  |

|       | See MPLAB Help for more information.                                                             |  |  |  |  |  |  |

Unlike the similar sequence with the oscillator's LOCK bit, IOLOCK remains in one state until changed. This allows all of the peripheral pin selects to be configured with a single unlock sequence followed by an update to all control registers, then locked with a second lock sequence.

#### 11.6.3.2 Continuous State Monitoring

In addition to being protected from direct writes, the contents of the RPINRx and RPORx registers are constantly monitored in hardware by shadow registers. If an unexpected change in any of the registers occurs (such as cell disturbances caused by ESD or other external events), a configuration mismatch Reset is triggered.

#### 11.6.3.3 Configuration Bit Pin Select Lock

As an additional level of safety, the device can be configured to prevent more than one write session to the RPINRx and RPORx registers. The IOL1WAY Configuration bit (FOSC<5>) blocks the IOLOCK bit from being cleared after it has been set once. If IOLOCK remains set, the register unlock procedure does not execute, and the peripheral pin select control registers cannot be written to. The only way to clear the bit and re-enable peripheral remapping is to perform a device Reset.

In the default (unprogrammed) state, IOL1WAY is set, restricting users to one write session. Programming IOL1WAY allows user applications unlimited access (with the proper use of the unlock sequence) to the peripheral pin select registers.

## 15.3 Output Compare Control Registers

## **REGISTER 15-1:** OCxCON: OUTPUT COMPAREX CONTROL REGISTER (x = 1, 2, 3 OR 4)

| U-0                                  | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | U-0        | U-0              | U-0             | U-0             | U-0   |  |

|--------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|------------------|-----------------|-----------------|-------|--|

|                                      | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | OCSIDL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | _          | —                |                 | —               | —     |  |

| bit 15                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |            |                  |                 |                 | bit 8 |  |

|                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |            |                  |                 |                 |       |  |

| U-0                                  | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | R-0 HC     | R/W-0            | R/W-0           | R/W-0           | R/W-0 |  |

|                                      | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | OCFLT      | OCTSEL           |                 | OCM<2:0>        | 1:10  |  |

| bit 7                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |            |                  |                 |                 | bit 0 |  |

| Legend:                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | HC = Cleared in                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | n Hardware | HS = Set in H    | Hardware        |                 |       |  |

| R = Readab                           | ole bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | W = Writable bi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | t          | U = Unimple      | mented bit, rea | d as '0'        |       |  |

| -n = Value a                         | it POR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | '1' = Bit is set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |            | '0' = Bit is cle | eared           | x = Bit is unki | nown  |  |

| bit 13<br>bit 12-5<br>bit 4<br>bit 3 | 1 = Output Co<br>0 = Output Co<br>Unimplement<br>OCFLT: PWN<br>1 = PWM Fac<br>0 = No PWM<br>(This bit is on<br>OCTSEL: Ou<br>1 = Timer3 is                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | <ul> <li>OCSIDL: Stop Output Compare in Idle Mode Control bit</li> <li>1 = Output Compare x halts in CPU Idle mode</li> <li>0 = Output Compare x continues to operate in CPU Idle mode</li> <li>Unimplemented: Read as '0'</li> <li>OCFLT: PWM Fault Condition Status bit</li> <li>1 = PWM Fault condition has occurred (cleared in hardware only)</li> <li>0 = No PWM Fault condition has occurred</li> <li>(This bit is only used when OCM&lt;2:0&gt; = 111)</li> <li>OCTSEL: Output Compare Timer Select bit</li> <li>1 = Timer3 is the clock source for Compare x</li> </ul> |            |                  |                 |                 |       |  |

| bit 2-0                              | <ul> <li>0 = Timer2 is the clock source for Compare x</li> <li>OCM&lt;2:0&gt;: Output Compare Mode Select bits</li> <li>111 = PWM mode on OCx, Fault pin enabled</li> <li>110 = PWM mode on OCx, Fault pin disabled</li> <li>101 = Initialize OCx pin low, generate continuous output pulses on OCx pin</li> <li>100 = Initialize OCx pin low, generate single output pulse on OCx pin</li> <li>011 = Compare event toggles OCx pin</li> <li>010 = Initialize OCx pin high, compare event forces OCx pin low</li> <li>001 = Initialize OCx pin low, compare event forces OCx pin high</li> <li>000 = Output compare channel is disabled</li> </ul> |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |            |                  |                 |                 |       |  |

## 18.3 UART Control Registers

## REGISTER 18-1: UXMODE: UARTX MODE REGISTER

| R/W-0                 | U-0 | R/W-0 | R/W-0               | R/W-0 | U-0 | R/W-0 | R/W-0 |

|-----------------------|-----|-------|---------------------|-------|-----|-------|-------|

| UARTEN <sup>(1)</sup> | —   | USIDL | IREN <sup>(2)</sup> | RTSMD | —   | UEN   | <1:0> |

| bit 15                |     |       |                     |       |     |       | bit 8 |

| R/W-0 HC | R/W-0  | R/W-0 HC | R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|----------|--------|----------|--------|-------|-------|-------|-------|

| WAKE     | LPBACK | ABAUD    | URXINV | BRGH  | PDSEL | <1:0> | STSEL |

| bit 7    |        |          |        |       |       |       | bit 0 |

| Legend:           | HC = Hardware cleared |                             |                    |

|-------------------|-----------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit      | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set      | '0' = Bit is cleared        | x = Bit is unknown |

| bit 15  | UARTEN: UARTx Enable bit <sup>(1)</sup>                                                                                                                 |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | 1 = UARTx is enabled; all UARTx pins are controlled by UARTx as defined by UEN<1:0>                                                                     |

|         | 0 = UARTx is disabled; all UARTx pins are controlled by port latches; UARTx power consumption                                                           |

| h:+ 4 4 | minimal<br>Unimplemented: Deed es (s)                                                                                                                   |

| bit 14  | Unimplemented: Read as '0'                                                                                                                              |

| bit 13  | USIDL: Stop in Idle Mode bit                                                                                                                            |

|         | <ul> <li>1 = Discontinue module operation when device enters Idle mode</li> <li>0 = Continue module operation in Idle mode</li> </ul>                   |

| bit 12  | IREN: IrDA <sup>®</sup> Encoder and Decoder Enable bit <sup>(2)</sup>                                                                                   |

|         | 1 = IrDA encoder and decoder enabled                                                                                                                    |

|         | 0 = IrDA encoder and decoder disabled                                                                                                                   |

| bit 11  | RTSMD: Mode Selection for UxRTS Pin bit                                                                                                                 |

|         | 1 = UxRTS pin in Simplex mode                                                                                                                           |

|         | 0 = UxRTS pin in Flow Control mode                                                                                                                      |

| bit 10  | Unimplemented: Read as '0'                                                                                                                              |

| bit 9-8 | UEN<1:0>: UARTx Enable bits                                                                                                                             |

|         | 11 = UxTX, UxRX and BCLK pins are enabled and used; UxCTS pin controlled by port latches                                                                |

|         | 10 = UxTX, UxRX, UxCTS and UxRTS pins are enabled and used<br>01 = UxTX, UxRX and UxRTS pins are enabled and used; UxCTS pin controlled by port latches |

|         | 00 = UxTX and UxRX pins are enabled and used; UxCTS and UxRTS/BCLK pins controlled by                                                                   |

|         | port latches                                                                                                                                            |

| bit 7   | WAKE: Wake-up on Start bit Detect During Sleep Mode Enable bit                                                                                          |

|         | 1 = UARTx continues to sample the UxRX pin; interrupt generated on falling edge; bit cleared                                                            |

|         | in hardware on following rising edge                                                                                                                    |

| 1.11.0  | 0 = No wake-up enabled                                                                                                                                  |

| bit 6   | LPBACK: UARTx Loopback Mode Select bit                                                                                                                  |

|         | <ul> <li>1 = Enable Loopback mode</li> <li>0 = Loopback mode is disabled</li> </ul>                                                                     |

| bit 5   | ABAUD: Auto-Baud Enable bit                                                                                                                             |

|         | 1 = Enable baud rate measurement on the next character – requires reception of a Sync field (55h)                                                       |

|         | before other data; cleared in hardware upon completion                                                                                                  |

|         | 0 = Baud rate measurement disabled or completed                                                                                                         |

| Note 1: | Refer to Section 17. "UART" (DS70232) in the "dsPIC33F/PIC24H Family Reference Manual" for                                                              |

|         | information on enabling the UART module for receive or transmit operation.                                                                              |

2: This feature is only available for the 16x BRG mode (BRGH = 0).

#### **19.5 ECAN Control Registers**