Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Active                                                                        |

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 40 MIPs                                                                       |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                  |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                    |

| Number of I/O              | 35                                                                            |

| Program Memory Size        | 64KB (22K x 24)                                                               |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 8K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                     |

| Data Converters            | A/D 13x10b/12b                                                                |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 44-VQFN Exposed Pad                                                           |

| Supplier Device Package    | 44-QFN (8x8)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24hj64gp504-e-ml |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 2.0 GUIDELINES FOR GETTING STARTED WITH 16-BIT MICROCONTROLLERS

- **Note 1:** This data sheet summarizes the features PIC24HJ32GP302/304, of the PIC24HJ64GPX02/X04 and PIC24HJ128GPX02/X04 of family devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the "dsPIC33F/PIC24H Family Reference Manual". Please see the Microchip web site (www.microchip.com) for the latest dsPIC33F/PIC24H Family Reference Manual sections.

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

# 2.1 Basic Connection Requirements

Getting started with the PIC24HJ32GP302/304, PIC24HJ64GPX02/X04 and PIC24HJ128GPX02/X04 family of 16-bit Microcontrollers (MCUs) requires attention to a minimal set of device pin connections before proceeding with development. The following is a list of pin names, which must always be connected:

- All VDD and VSS pins (see Section 2.2 "Decoupling Capacitors")

- All AVDD and AVSS pins (regardless if ADC module is not used)

(see Section 2.2 "Decoupling Capacitors")

• VCAP

(see Section 2.3 "CPU Logic Filter Capacitor Connection (VCAP)")

- MCLR pin (see Section 2.4 "Master Clear (MCLR) Pin")

- PGECx/PGEDx pins used for In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) and debugging purposes (see Section 2.5 "ICSP Pins")

- OSC1 and OSC2 pins when external oscillator source is used

(see Section 2.6 "External Oscillator Pins")

Additionally, the following pins may be required:

• VREF+/VREF- pins used when external voltage reference for ADC module is implemented

Note: The AVDD and AVSS pins must be connected independent of the ADC voltage reference source.

# 2.2 Decoupling Capacitors

The use of decoupling capacitors on every pair of power supply pins, such as VDD, VSS, AVDD and AVss is required.

Consider the following criteria when using decoupling capacitors:

- Value and type of capacitor: Recommendation of 0.1  $\mu$ F (100 nF), 10-20V. This capacitor should be a low-ESR and have resonance frequency in the range of 20 MHz and higher. It is recommended that ceramic capacitors be used.

- Placement on the printed circuit board: The decoupling capacitors should be placed as close to the pins as possible. It is recommended to place the capacitors on the same side of the board as the device. If space is constricted, the capacitor can be placed on another layer on the PCB using a via; however, ensure that the trace length from the pin to the capacitor is within one-quarter inch (6 mm) in length.

- Handling high frequency noise: If the board is experiencing high frequency noise, upward of tens of MHz, add a second ceramic-type capacitor in parallel to the above described decoupling capacitor. The value of the second capacitor can be in the range of 0.01  $\mu$ F to 0.001  $\mu$ F. Place this second capacitor next to the primary decoupling capacitor. In high-speed circuit designs, consider implementing a decade pair of capacitances as close to the power and ground pins as possible. For example, 0.1  $\mu$ F in parallel with 0.001  $\mu$ F.

- Maximizing performance: On the board layout from the power supply circuit, run the power and return traces to the decoupling capacitors first, and then to the device pins. This ensures that the decoupling capacitors are first in the power chain. Equally important is to keep the trace length between the capacitor and the power pins to a minimum thereby reducing PCB track inductance.

# TABLE 4-7: OUTPUT COMPARE REGISTER MAP

|          |             |        |            |        |          |            |            |             |             |             |              |       |       |        |       |          |       | -             |

|----------|-------------|--------|------------|--------|----------|------------|------------|-------------|-------------|-------------|--------------|-------|-------|--------|-------|----------|-------|---------------|

| SFR Name | SFR<br>Addr | Bit 15 | Bit 14     | Bit 13 | Bit 12   | Bit 11     | Bit 10     | Bit 9       | Bit 8       | Bit 7       | Bit 6        | Bit 5 | Bit 4 | Bit 3  | Bit 2 | Bit 1    | Bit 0 | All<br>Resets |

| OC1RS    | 0180        |        |            |        |          |            |            | Ou          | tput Compar | e 1 Seconda | ary Register |       |       |        |       |          |       | xxxx          |

| OC1R     | 0182        |        |            |        |          |            |            |             | Output Co   | ompare 1 Re | gister       |       |       |        |       |          |       | XXXX          |

| OC1CON   | 0184        | _      | _          | OCSIDL | _        | _          |            | _           | —           | _           | _            | _     | OCFLT | OCTSEL |       | OCM<2:0> |       | 0000          |

| OC2RS    | 0186        |        |            |        |          |            |            | Ou          | tput Compar | e 2 Seconda | ary Register |       |       |        |       |          |       | XXXX          |

| OC2R     | 0188        |        |            |        |          |            |            |             | Output Co   | ompare 2 Re | gister       |       |       |        |       |          |       | XXXX          |

| OC2CON   | 018A        | _      | _          | OCSIDL | _        | _          |            | _           | —           | _           | _            | _     | OCFLT | OCTSEL |       | OCM<2:0> |       | 0000          |

| OC3RS    | 018C        |        |            |        |          |            |            | Ou          | tput Compar | e 3 Seconda | ary Register |       |       |        |       |          |       | XXXX          |

| OC3R     | 018E        |        |            |        |          |            |            |             | Output Co   | ompare 3 Re | gister       |       |       |        |       |          |       | XXXX          |

| OC3CON   | 0190        | _      | _          | OCSIDL | _        | _          |            | _           | —           | _           | _            | _     | OCFLT | OCTSEL |       | OCM<2:0> |       | 0000          |

| OC4RS    | 0192        |        |            |        |          |            |            | Ou          | tput Compar | e 4 Seconda | ary Register |       |       |        |       |          |       | XXXX          |

| OC4R     | 0194        |        |            |        |          |            |            |             | Output Co   | ompare 4 Re | gister       |       |       |        |       |          |       | XXXX          |

| OC4CON   | 0196        | _      | _          | OCSIDL | _        | _          | _          | _           | _           | _           | _            | _     | OCFLT | OCTSEL |       | OCM<2:0> |       | 0000          |

| l edend. | v = unk     |        | o on Posot | = unim | lomontod | road as '0 | ' Posot va | luce are ch | own in hove | docimal     |              |       |       | •      | •     |          |       |               |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# TABLE 4-8: I2C1 REGISTER MAP

| SFR Name | SFR<br>Addr | Bit 15  | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8 | Bit 7 | Bit 6 | Bit 5      | Bit 4        | Bit 3      | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|----------|-------------|---------|--------|---------|--------|--------|--------|--------|-------|-------|-------|------------|--------------|------------|-------|-------|-------|---------------|

| I2C1RCV  | 0200        | _       | _      | -       | _      | _      | -      | -      | _     |       |       |            | Receive      | Register   |       |       |       | 0000          |

| I2C1TRN  | 0202        | _       | _      | _       | _      | _      | _      | _      | _     |       |       |            | Transmit     | Register   |       |       |       | OOFF          |

| I2C1BRG  | 0204        | _       | _      | _       | _      | _      | _      | _      |       |       |       | Baud Rat   | e Generato   | r Register |       |       |       | 0000          |

| I2C1CON  | 0206        | I2CEN   | _      | I2CSIDL | SCLREL | IPMIEN | A10M   | DISSLW | SMEN  | GCEN  | STREN | ACKDT      | ACKEN        | RCEN       | PEN   | RSEN  | SEN   | 1000          |

| I2C1STAT | 0208        | ACKSTAT | TRSTAT | _       | _      | _      | BCL    | GCSTAT | ADD10 | IWCOL | I2COV | D_A        | Р            | S          | R_W   | RBF   | TBF   | 0000          |

| I2C1ADD  | 020A        | _       | _      | _       | _      | _      | _      |        |       |       |       | Address    | Register     |            |       |       |       | 0000          |

| I2C1MSK  | 020C        | _       | _      | _       | _      | _      | -      |        |       |       |       | Address Ma | isk Register |            |       |       |       | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# TABLE 4-9: UART1 REGISTER MAP

| SFR Name | SFR<br>Addr | Bit 15   | Bit 14 | Bit 13   | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8      | Bit 7        | Bit 6   | Bit 5 | Bit 4       | Bit 3        | Bit 2 | Bit 1  | Bit 0 | All<br>Resets |

|----------|-------------|----------|--------|----------|--------|--------|--------|-------|------------|--------------|---------|-------|-------------|--------------|-------|--------|-------|---------------|

| U1MODE   | 0220        | UARTEN   | _      | USIDL    | IREN   | RTSMD  | _      | UEN1  | UEN0       | WAKE         | LPBACK  | ABAUD | URXINV      | BRGH         | PDSEI | _<1:0> | STSEL | 0000          |

| U1STA    | 0222        | UTXISEL1 | UTXINV | UTXISEL0 | -      | UTXBRK | UTXEN  | UTXBF | TRMT       | URXISE       | EL<1:0> | ADDEN | RIDLE       | PERR         | FERR  | OERR   | URXDA | 0110          |

| U1TXREG  | 0224        | _        | _      | _        | _      | _      | —      | _     | UTX8       |              |         | U     | ART Transm  | nit Register |       |        |       | XXXX          |

| U1RXREG  | 0226        | _        | _      | _        | _      | _      | _      | _     | URX8       |              |         | U     | ART Receive | ed Register  |       |        |       | 0000          |

| U1BRG    | 0228        |          |        |          |        |        |        | Bau   | d Rate Ger | erator Presc | aler    |       |             |              |       |        |       | 0000          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| File Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|-----------|------|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|-------|--------|--------|--------|---------------|

| BSRAM     | 0750 | _      | _      | _      |        |        | —      | -     | _     | —     | _     |       | _     | -     | IW_BSR | IR_BSR | RL_BSR | 0000          |

| SSRAM     | 0752 | _      | _      | _      | —      | —      | —      | -     | -     | —     | —     | —     | —     | —     | IW_SSR | IR_SSR | RL_SSR | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This register is not present in devices with 32K Flash (PIC24HJ32GP302/304).

#### TABLE 4-33: NVM REGISTER MAP

| File Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3   | Bit 2 | Bit 1  | Bit 0 | All<br>Resets |

|-----------|------|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|---------|-------|--------|-------|---------------|

| NVMCON    | 0760 | WR     | WREN   | WRERR  | —      | —      | —      | —     | —     | _     | ERASE | _     | -     |         | NVMO  | P<3:0> |       | 0000          |

| NVMKEY    | 0766 |        | —      | _      | —      | —      | —      |       |       |       |       |       | NVMKE | EY<7:0> |       |        |       | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-34: PMD REGISTER MAP

| File Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8 | Bit 7  | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-----------|------|--------|--------|--------|--------|--------|--------|--------|-------|--------|-------|-------|--------|--------|-------|-------|-------|---------------|

| PMD1      | 0770 | T5MD   | T4MD   | T3MD   | T2MD   | T1MD   | _      | _      | —     | I2C1MD | U2MD  | U1MD  | SPI2MD | SPI1MD | —     | C1MD  | AD1MD | 0000          |

| PMD2      | 0772 | IC8MD  | IC7MD  | _      | _      | _      | _      | IC2MD  | IC1MD | _      | _     | _     | _      | OC4MD  | OC3MD | OC2MD | OC1MD | 0000          |

| PMD3      | 0774 | _      | _      | _      | _      | _      | CMPMD  | RTCCMD | PMPMD | CRCMD  | _     | _     | _      | _      | _     | _     | _     | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

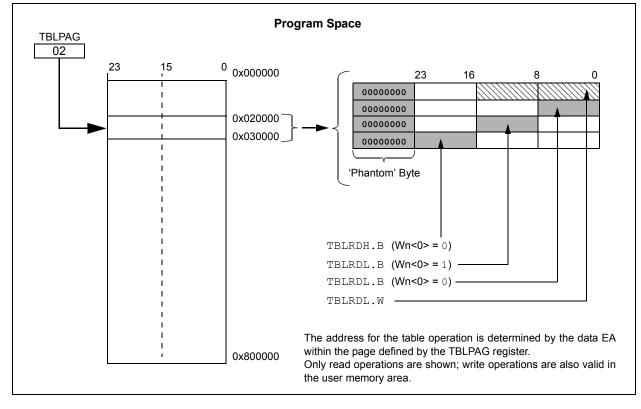

#### 4.6.2 DATA ACCESS FROM PROGRAM MEMORY USING TABLE INSTRUCTIONS

The TBLRDL and TBLWTL instructions offer a direct method of reading or writing the lower word of any address within the program space without going through data space. The TBLRDH and TBLWTH instructions are the only method to read or write the upper 8 bits of a program space word as data.

The PC is incremented by two for each successive 24-bit program word. This allows program memory addresses to directly map to data space addresses. Program memory can thus be regarded as two 16-bit wide word address spaces, residing side by side, each with the same address range. TBLRDL and TBLWTL access the space that contains the least significant data word. TBLRDH and TBLWTH access the space that contains the upper data byte.

Two table instructions are provided to move byte or word-sized (16-bit) data to and from program space. Both function as either byte or word operations.

- TBLRDL (Table Read Low):

- In Word mode, this instruction maps the lower word of the program space location (P<15:0>) to a data address (D<15:0>).

- In Byte mode, either the upper or lower byte of the lower program word is mapped to the lower byte of a data address. The upper byte is selected when Byte Select is '1'; the lower byte is selected when it is '0'.

- TBLRDH (Table Read High):

- In Word mode, this instruction maps the entire upper word of a program address (P<23:16>) to a data address. The 'phantom' byte (D<15:8>), is always '0'.

- In Byte mode, this instruction maps the upper or lower byte of the program word to D<7:0> of the data address, in the TBLRDL instruction. The data is always '0' when the upper 'phantom' byte is selected (Byte Select = 1).

Similarly, two table instructions, TBLWTH and TBLWTL, are used to write individual bytes or words to a program space address. The details of their operation are explained in Section 5.0 "Flash Program Memory".

For all table operations, the area of program memory space to be accessed is determined by the Table Page register (TBLPAG). TBLPAG covers the entire program memory space of the device, including user application and configuration spaces. When TBLPAG<7> = 0, the table page is located in the user memory space. When TBLPAG<7> = 1, the page is located in configuration space.

### FIGURE 4-7: ACCESSING PROGRAM MEMORY WITH TABLE INSTRUCTIONS

| REGISTER 7              | -5: IFS0:                                                                                                                                                        | INTERRUPT                                                                                                                                   | FLAG STAT                                                                                                                                             | US REGISTE        | R U              |                 |        |

|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|------------------|-----------------|--------|

| U-0                     | R/W-0                                                                                                                                                            | R/W-0                                                                                                                                       | R/W-0                                                                                                                                                 | R/W-0             | R/W-0            | R/W-0           | R/W-0  |

| —                       | DMA1IF                                                                                                                                                           | AD1IF                                                                                                                                       | U1TXIF                                                                                                                                                | U1RXIF            | SPI1IF           | SPI1EIF         | T3IF   |

| pit 15                  |                                                                                                                                                                  |                                                                                                                                             |                                                                                                                                                       |                   |                  |                 | bit    |

| R/W-0                   | R/W-0                                                                                                                                                            | R/W-0                                                                                                                                       | R/W-0                                                                                                                                                 | R/W-0             | R/W-0            | R/W-0           | R/W-0  |

| T2IF                    | OC2IF                                                                                                                                                            | IC2IF                                                                                                                                       | DMA0IF                                                                                                                                                | T1IF              | OC1IF            | IC1IF           | INTOIF |

| bit 7                   | 00211                                                                                                                                                            | 10211                                                                                                                                       | Division                                                                                                                                              |                   | 00111            | 10111           | bit    |

| Legend:                 |                                                                                                                                                                  |                                                                                                                                             |                                                                                                                                                       |                   |                  |                 |        |

| R = Readable            | bit                                                                                                                                                              | W = Writable                                                                                                                                | bit                                                                                                                                                   | U = Unimplem      | nented bit, read | d as '0'        |        |

| -n = Value at P         |                                                                                                                                                                  | '1' = Bit is set                                                                                                                            |                                                                                                                                                       | '0' = Bit is clea |                  | x = Bit is unkn | own    |

|                         |                                                                                                                                                                  |                                                                                                                                             |                                                                                                                                                       |                   |                  |                 |        |

| bit 15                  | Unimplemer                                                                                                                                                       | nted: Read as '                                                                                                                             | 0'                                                                                                                                                    |                   |                  |                 |        |

| bit 14                  | DMA1IF: DM                                                                                                                                                       | 1A Channel 1 D                                                                                                                              | ata Transfer C                                                                                                                                        | omplete Interru   | upt Flag Status  | bit             |        |

|                         | 1 = Interrupt                                                                                                                                                    | request has oc<br>request has no                                                                                                            | curred                                                                                                                                                |                   |                  |                 |        |

| bit 13                  | AD1IF: ADC                                                                                                                                                       | 1 Conversion C                                                                                                                              | complete Interr                                                                                                                                       | upt Flag Status   | bit              |                 |        |

|                         |                                                                                                                                                                  | request has oc<br>request has no                                                                                                            |                                                                                                                                                       |                   |                  |                 |        |

| bit 12                  | •                                                                                                                                                                | RT1 Transmitte                                                                                                                              |                                                                                                                                                       | s Status hit      |                  |                 |        |

| 21C 12                  |                                                                                                                                                                  | request has oc                                                                                                                              |                                                                                                                                                       | g olalas bit      |                  |                 |        |

|                         |                                                                                                                                                                  | request has no                                                                                                                              |                                                                                                                                                       |                   |                  |                 |        |

| bit 11                  | U1RXIF: UA                                                                                                                                                       | RT1 Receiver I                                                                                                                              | nterrupt Flag S                                                                                                                                       | Status bit        |                  |                 |        |

|                         | •                                                                                                                                                                | request has oc                                                                                                                              |                                                                                                                                                       |                   |                  |                 |        |

|                         | -                                                                                                                                                                | request has no                                                                                                                              |                                                                                                                                                       |                   |                  |                 |        |

| oit 10                  |                                                                                                                                                                  | Event Interrup                                                                                                                              | •                                                                                                                                                     | bit               |                  |                 |        |

|                         |                                                                                                                                                                  | request has oc<br>request has no                                                                                                            |                                                                                                                                                       |                   |                  |                 |        |

| bit 9                   | -                                                                                                                                                                | 11 Error Interru                                                                                                                            |                                                                                                                                                       | bit               |                  |                 |        |

|                         |                                                                                                                                                                  | request has oc                                                                                                                              |                                                                                                                                                       |                   |                  |                 |        |

|                         | 0 = Interrupt                                                                                                                                                    | request has no                                                                                                                              | t occurred                                                                                                                                            |                   |                  |                 |        |

| bit 8                   |                                                                                                                                                                  | Interrupt Flag                                                                                                                              |                                                                                                                                                       |                   |                  |                 |        |

|                         |                                                                                                                                                                  | request has oc                                                                                                                              |                                                                                                                                                       |                   |                  |                 |        |

| hit 7                   |                                                                                                                                                                  | request has no                                                                                                                              |                                                                                                                                                       |                   |                  |                 |        |

| bit 7                   |                                                                                                                                                                  | Interrupt Flag                                                                                                                              | Status Dit                                                                                                                                            |                   |                  |                 |        |

|                         |                                                                                                                                                                  | rogulaet hae on                                                                                                                             |                                                                                                                                                       |                   |                  |                 |        |

|                         |                                                                                                                                                                  | request has oc<br>request has no                                                                                                            | curred                                                                                                                                                |                   |                  |                 |        |

| bit 6                   | 0 = Interrupt                                                                                                                                                    |                                                                                                                                             | curred<br>t occurred                                                                                                                                  | upt Flag Status   | bit              |                 |        |

| bit 6                   | 0 = Interrupt<br>OC2IF: Outp                                                                                                                                     | request has no                                                                                                                              | curred<br>t occurred<br>nannel 2 Interro                                                                                                              | upt Flag Status   | bit              |                 |        |

|                         | <ul> <li>0 = Interrupt</li> <li>OC2IF: Outp</li> <li>1 = Interrupt</li> <li>0 = Interrupt</li> </ul>                                                             | request has no<br>out Compare Ch<br>request has oc<br>request has no                                                                        | curred<br>t occurred<br>hannel 2 Interru<br>curred<br>t occurred                                                                                      |                   | bit              |                 |        |

|                         | 0 = Interrupt<br>OC2IF: Outp<br>1 = Interrupt<br>0 = Interrupt<br>IC2IF: Input                                                                                   | request has no<br>out Compare Ch<br>request has oc<br>request has no<br>Capture Chann                                                       | curred<br>t occurred<br>nannel 2 Interro<br>curred<br>t occurred<br>el 2 Interrupt F                                                                  |                   | bit              |                 |        |

|                         | <ul> <li>0 = Interrupt</li> <li>OC2IF: Outp</li> <li>1 = Interrupt</li> <li>0 = Interrupt</li> <li>IC2IF: Input</li> <li>1 = Interrupt</li> </ul>                | request has no<br>out Compare Ch<br>request has oc<br>request has no<br>Capture Chann<br>request has oc                                     | curred<br>t occurred<br>hannel 2 Intern<br>curred<br>t occurred<br>el 2 Interrupt F<br>curred                                                         |                   | bit              |                 |        |

| bit 5                   | 0 = Interrupt<br><b>OC2IF:</b> Outp<br>1 = Interrupt<br>0 = Interrupt<br><b>IC2IF:</b> Input 0<br>1 = Interrupt<br>0 = Interrupt                                 | request has no<br>out Compare Ch<br>request has oc<br>request has no<br>Capture Chann<br>request has oc<br>request has no                   | curred<br>t occurred<br>hannel 2 Intern<br>curred<br>t occurred<br>el 2 Interrupt F<br>curred<br>t occurred                                           | lag Status bit    |                  | bit             |        |

| bit 5                   | 0 = Interrupt<br>OC2IF: Outp<br>1 = Interrupt<br>0 = Interrupt<br>IC2IF: Input<br>1 = Interrupt<br>0 = Interrupt<br>DMA0IF: DM                                   | request has no<br>out Compare Ch<br>request has no<br>Capture Chann<br>request has no<br>request has no<br>IA Channel 0 D                   | curred<br>t occurred<br>hannel 2 Interru<br>curred<br>t occurred<br>el 2 Interrupt F<br>curred<br>t occurred<br>hata Transfer C                       | lag Status bit    |                  | bit             |        |

| bit 6<br>bit 5<br>bit 4 | 0 = Interrupt<br>OC2IF: Outp<br>1 = Interrupt<br>0 = Interrupt<br>IC2IF: Input<br>1 = Interrupt<br>0 = Interrupt<br>DMA0IF: DM<br>1 = Interrupt                  | request has no<br>out Compare Ch<br>request has oc<br>request has no<br>Capture Chann<br>request has oc<br>request has no                   | curred<br>t occurred<br>hannel 2 Interru<br>curred<br>t occurred<br>el 2 Interrupt F<br>curred<br>t occurred<br>hata Transfer C<br>curred             | lag Status bit    |                  | bit             |        |

| bit 5                   | 0 = Interrupt<br>OC2IF: Outp<br>1 = Interrupt<br>0 = Interrupt<br>IC2IF: Input<br>1 = Interrupt<br>0 = Interrupt<br>DMA0IF: DM<br>1 = Interrupt<br>0 = Interrupt | request has no<br>out Compare Ch<br>request has no<br>Capture Chann<br>request has no<br>request has no<br>IA Channel 0 D<br>request has no | curred<br>t occurred<br>hannel 2 Intern<br>curred<br>t occurred<br>el 2 Interrupt F<br>curred<br>t occurred<br>ata Transfer C<br>curred<br>t occurred | lag Status bit    |                  | bit             |        |

#### IEGA, INTERDURT EL AC STATUS DECISTER A

| REGISTER 7-12: | IEC2: INTERRUPT ENABLE CONTROL REGISTER 2 |

|----------------|-------------------------------------------|

|----------------|-------------------------------------------|

| U-0<br>— bit 7<br>Legend:<br>R = Readable bi<br>n = Value at PC<br>bit 15<br>bit 14 | DR<br>Unimplement<br>DMA4IE: DM/                                                                                                                                                                                    | '1' = Bit is set                      |                |                                     | R/W-0<br>C1RXIE <sup>(1)</sup> |                 | R/W-0<br>SPI2EIE<br>bit |

|-------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|----------------|-------------------------------------|--------------------------------|-----------------|-------------------------|

| —<br>bit 7<br>Legend:<br>R = Readable bi<br>n = Value at PC<br>bit 15<br>bit 14     | —<br>it<br>DR<br>Unimplement<br>DMA4IE: DM/                                                                                                                                                                         | —<br>W = Writable<br>'1' = Bit is set | DMA3IE         | C1IE <sup>(1)</sup><br>U = Unimpler | C1RXIE <sup>(1)</sup>          | SPI2IE          | R/W-0<br>SPI2EIE        |

| —<br>bit 7<br>Legend:<br>R = Readable bi<br>n = Value at PC<br>bit 15<br>bit 14     | —<br>it<br>DR<br>Unimplement<br>DMA4IE: DM/                                                                                                                                                                         | —<br>W = Writable<br>'1' = Bit is set | DMA3IE         | C1IE <sup>(1)</sup><br>U = Unimpler | C1RXIE <sup>(1)</sup>          | SPI2IE          | SPI2EIE                 |

| —<br>bit 7<br>Legend:<br>R = Readable bi<br>n = Value at PC<br>bit 15<br>bit 14     | U-0       U-0       R/W-0       R/W-0       R/W-0         —       —       DMA3IE       C1IE <sup>(1)</sup> C1RXIE <sup>(1)</sup> SPI2IE         bit       W = Writable bit       U = Unimplemented bit, read as '0' |                                       |                |                                     | SPI2EIE                        |                 |                         |

| bit 14                                                                              | DR<br>Unimplement<br>DMA4IE: DM/                                                                                                                                                                                    | '1' = Bit is set                      | bit            | U = Unimpler                        |                                |                 |                         |

| R = Readable bi<br>-n = Value at PC<br>bit 15<br>bit 14                             | DR<br>Unimplement<br>DMA4IE: DM/                                                                                                                                                                                    | '1' = Bit is set                      |                |                                     | nented bit, read               | 25 '0'          |                         |

| R = Readable bi<br>n = Value at PC<br>bit 15<br>bit 14                              | DR<br>Unimplement<br>DMA4IE: DM/                                                                                                                                                                                    | '1' = Bit is set                      |                |                                     | mented bit, read               | ae 'O'          |                         |

| bit 15<br>bit 14                                                                    | Unimplement<br>DMA4IE: DM/                                                                                                                                                                                          |                                       |                |                                     | ,                              | as u            |                         |

| bit 15<br>bit 14                                                                    | Unimplement<br>DMA4IE: DM/                                                                                                                                                                                          |                                       |                |                                     | ared                           | x = Bit is unkr | nown                    |

| pit 14                                                                              | DMA4IE: DMA                                                                                                                                                                                                         | ed: Read as '                         |                |                                     |                                |                 |                         |

|                                                                                     |                                                                                                                                                                                                                     |                                       | 0'             |                                     |                                |                 |                         |

|                                                                                     | 1 = Interrupt r                                                                                                                                                                                                     | A Channel 4 D                         | ata Transfer C | Complete Interr                     | upt Enable bit                 |                 |                         |

|                                                                                     | ⊥ – interrupt i                                                                                                                                                                                                     | equest enable                         | d              | -                                   | -                              |                 |                         |

|                                                                                     | 0 = Interrupt r                                                                                                                                                                                                     | equest not ena                        | abled          |                                     |                                |                 |                         |

| bit 13                                                                              | PMPIE: Parall                                                                                                                                                                                                       | el Master Port                        | Interrupt Ena  | ble bit                             |                                |                 |                         |

|                                                                                     |                                                                                                                                                                                                                     |                                       |                |                                     |                                |                 |                         |

|                                                                                     | •                                                                                                                                                                                                                   | •                                     |                |                                     |                                |                 |                         |

|                                                                                     | -                                                                                                                                                                                                                   |                                       |                |                                     |                                |                 |                         |

|                                                                                     |                                                                                                                                                                                                                     |                                       |                | complete Interr                     | upt Enable bit                 |                 |                         |

|                                                                                     |                                                                                                                                                                                                                     |                                       |                |                                     |                                |                 |                         |

|                                                                                     |                                                                                                                                                                                                                     | •                                     |                | )                                   |                                |                 |                         |

|                                                                                     |                                                                                                                                                                                                                     |                                       |                |                                     |                                |                 |                         |

|                                                                                     |                                                                                                                                                                                                                     |                                       |                |                                     |                                |                 |                         |

| bit 2                                                                               | C1RXIE: ECA                                                                                                                                                                                                         | N1 Receive D                          | ata Ready Inte | errupt Enable b                     | oit <sup>(1)</sup>             |                 |                         |

|                                                                                     | 1 = Interrupt r                                                                                                                                                                                                     | equest enable                         | d              |                                     |                                |                 |                         |

| 1                                                                                   | 0 = Interrupt r                                                                                                                                                                                                     | equest not ena                        | abled          |                                     |                                |                 |                         |

|                                                                                     |                                                                                                                                                                                                                     |                                       |                |                                     |                                |                 |                         |

|                                                                                     | •                                                                                                                                                                                                                   | •                                     |                |                                     |                                |                 |                         |

|                                                                                     | •                                                                                                                                                                                                                   | equest not ena                        |                |                                     |                                |                 |                         |

|                                                                                     |                                                                                                                                                                                                                     | 2 Error Interrup                      |                |                                     |                                |                 |                         |

|                                                                                     | •                                                                                                                                                                                                                   | equest enable<br>equest not ena       |                |                                     |                                |                 |                         |

Note 1: Interrupts disabled on devices without ECAN<sup>™</sup> modules.

| U-0           | R/W-1         | R/W-0                                  | R/W-0           | U-0              | R/W-1            | R/W-0           | R/W-0 |

|---------------|---------------|----------------------------------------|-----------------|------------------|------------------|-----------------|-------|

| _             |               | CRCIP<2:0>                             |                 | _                |                  | U2EIP<2:0>      |       |

| bit 15        |               |                                        |                 |                  |                  |                 | bit 8 |

|               |               |                                        |                 |                  |                  |                 |       |

| U-0           | R/W-1         | R/W-0                                  | R/W-0           | U-0              | U-0              | U-0             | U-0   |

|               |               | U1EIP<2:0>                             |                 |                  |                  |                 |       |

| bit 7         |               |                                        |                 |                  |                  |                 | bit   |

| Legend:       |               |                                        |                 |                  |                  |                 |       |

| R = Readabl   | e bit         | W = Writable                           | bit             | U = Unimple      | mented bit, read | d as '0'        |       |

| -n = Value at | POR           | '1' = Bit is set                       |                 | '0' = Bit is cle | eared            | x = Bit is unkr | nown  |

|               |               |                                        |                 |                  |                  |                 |       |

| bit 15        | -             | nted: Read as '                        |                 |                  |                  |                 |       |

| bit 14-12     |               | CRC Generate                           |                 |                  | ty bits          |                 |       |

|               | 111 = Interro | upt is priority 7 (                    | highest priorit | ty interrupt)    |                  |                 |       |

|               | •             |                                        |                 |                  |                  |                 |       |

|               | •             |                                        |                 |                  |                  |                 |       |

|               |               | upt is priority 1<br>upt source is dis | abled           |                  |                  |                 |       |

| bit 11        |               | nted: Read as '                        |                 |                  |                  |                 |       |

| bit 10-8      | -             | : UART2 Error I                        |                 | ity bite         |                  |                 |       |

| DIL 10-0      |               | upt is priority 7 (                    |                 | •                |                  |                 |       |

|               | •             |                                        | nightest phone  | ly interrupt)    |                  |                 |       |

|               | •             |                                        |                 |                  |                  |                 |       |

|               | •             |                                        |                 |                  |                  |                 |       |

|               |               | upt is priority 1<br>upt source is dis | abled           |                  |                  |                 |       |

| bit 7         |               | nted: Read as '                        |                 |                  |                  |                 |       |

| bit 6-4       | -             | UART1 Error I                          |                 | itv bits         |                  |                 |       |

|               |               | upt is priority 7 (                    | -               | -                |                  |                 |       |

|               | •             | · · · · · · · · · · · · · · ·          | 5               | - <b>J</b>       |                  |                 |       |

|               | •             |                                        |                 |                  |                  |                 |       |

|               |               |                                        |                 |                  |                  |                 |       |

|               | •             | upt is priority 1                      |                 |                  |                  |                 |       |

bit 3-0 Unimplemented: Read as '0'

# 9.1 CPU Clocking System

The PIC24HJ32GP302/304, PIC24HJ64GPX02/X04 and PIC24HJ128GPX02/X04 devices provide seven system clock options:

- Fast RC (FRC) Oscillator

- FRC Oscillator with Phase-Locked Loop (PLL)

- Primary (XT, HS or EC) Oscillator

- Primary Oscillator with PLL

- Secondary (LP) Oscillator

- · Low-Power RC (LPRC) Oscillator

- · FRC Oscillator with postscaler

#### 9.1.1 SYSTEM CLOCK SOURCES

The Fast RC (FRC) internal oscillator runs at a nominal frequency of 7.37 MHz. User software can tune the FRC frequency. User software can optionally specify a factor (ranging from 1:2 to 1:256) by which the FRC clock frequency is divided. This factor is selected using the FRCDIV<2:0> (CLKDIV<10:8>) bits.

The primary oscillator can use one of the following as its clock source:

- Crystal (XT): Crystals and ceramic resonators in the range of 3 MHz to 10 MHz. The crystal is connected to the OSC1 and OSC2 pins.

- High-Speed Crystal (HS): Crystals in the range of 10 MHz to 40 MHz. The crystal is connected to the OSC1 and OSC2 pins.

- External Clock (EC): External clock signal is directly applied to the OSC1 pin.

The secondary (LP) oscillator is designed for low power and uses a 32.768 kHz crystal or ceramic resonator. The LP oscillator uses the SOSCI and SOSCO pins.

The Low-Power RC (LPRC) internal oscillator runs at a nominal frequency of 32.768 kHz. It is also used as a reference clock by the Watchdog Timer (WDT) and Fail-Safe Clock Monitor (FSCM).

The clock signals generated by the FRC and primary oscillators can be optionally applied to an on-chip PLL to provide a wide range of output frequencies for device operation. PLL configuration is described in **Section 9.1.3 "PLL Configuration**".

The FRC frequency depends on the FRC accuracy (see Table 28-19) and the value of the FRC Oscillator Tuning register (see Register 9-4).

### 9.1.2 SYSTEM CLOCK SELECTION

The oscillator source used at a device Power-on Reset event is selected using Configuration bit settings. The oscillator Configuration bit settings are located in the Configuration registers in the program memory. (Refer to Section 25.1 "Configuration Bits" for further details.) The Initial Oscillator FNOSC<2:0> Selection Configuration bits, (FOSCSEL<2:0>), and the Primary Oscillator Mode Select Configuration bits, POSCMD<1:0> (FOSC<1:0>), select the oscillator source that is used at a Power-on Reset. The FRC primary oscillator is the default (unprogrammed) selection.

The Configuration bits allow users to choose among 12 different clock modes, shown in Table 9-1.

The output of the oscillator (or the output of the PLL if a PLL mode has been selected) Fosc is divided by 2 to generate the device instruction clock (FcY) and the peripheral clock time base (FP). FcY defines the operating speed of the device, and speeds up to 40 MHz are supported by the PIC24HJ32GP302/304, PIC24HJ64GPX02/X04 and PIC24HJ128GPX02/X04 architecture.

Instruction execution speed or device operating frequency, FCY, is given by:

### EQUATION 9-1: DEVICE OPERATING FREQUENCY

$$FCY = \frac{FOSC}{2}$$

| R/W-0         | R/W-0                                                                                                                | R/W-1                                                       | R/W-1                  | R/W-0                | R/W-0           | R/W-0             | R/W-0       |

|---------------|----------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|------------------------|----------------------|-----------------|-------------------|-------------|

| ROI           |                                                                                                                      | DOZE<2:0>                                                   |                        | DOZEN <sup>(1)</sup> |                 | FRCDIV<2:0>       |             |

| bit 15        |                                                                                                                      |                                                             |                        |                      |                 |                   | bit         |

|               |                                                                                                                      |                                                             |                        |                      |                 |                   |             |

| R/W-0         | R/W-1                                                                                                                | U-0                                                         | R/W-0                  | R/W-0                | R/W-0           | R/W-0             | R/W-0       |

|               | DST<1:0>                                                                                                             | —                                                           |                        |                      | PLLPRE<4:0      | >                 |             |

| bit 7         |                                                                                                                      |                                                             |                        |                      |                 |                   | bit         |

| Legend:       |                                                                                                                      | y = Value set f                                             | rom Configu            | ration bits on PC    | R               |                   |             |

| R = Readabl   | e bit                                                                                                                | W = Writable I                                              | oit                    | U = Unimplem         | ented bit, read | d as '0'          |             |

| -n = Value at | POR                                                                                                                  | '1' = Bit is set                                            |                        | '0' = Bit is clea    | red             | x = Bit is unkn   | own         |

| bit 15        | 1 = Interrup<br>0 = Interrup                                                                                         | er on Interrupt bi<br>ts clears the DO<br>ts have no effect | ZEN bit and on the DOZ | EN bit               | ock/peripheral  | clock ratio is se | et to 1:1   |

| bit 14-12     | 111 = Fcy/1<br>110 = Fcy/6<br>101 = Fcy/3<br>100 = Fcy/1<br>011 = Fcy/8<br>010 = Fcy/4<br>001 = Fcy/2<br>000 = Fcy/1 | 4<br>2<br>6<br>(default)                                    |                        | Select Dits          |                 |                   |             |

| bit 11        | 1 = The DO                                                                                                           | ZE Mode Enable<br>ZE<2:0> bits spe<br>or clock/periphe      | ecify the ratio        |                      | eripheral clock | s and the proces  | ssor clocks |

| bit 10-8      |                                                                                                                      | )>: Internal Fast                                           |                        |                      |                 |                   |             |

|               | 110 = FRC (<br>101 = FRC (<br>100 = FRC (<br>011 = FRC (<br>010 = FRC (<br>001 = FRC (                               | divide by 32<br>divide by 16<br>divide by 8<br>divide by 4  | ult)                   |                      |                 |                   |             |

| bit 7-6       | PLLPOST<7<br>11 = Output<br>10 = Reserv<br>01 = Output<br>00 = Output                                                | ed<br>⁄4 (default)                                          | Dutput Divide          | er Select bits (als  | o denoted as    | 'N2', PLL postso  | caler)      |

| bit 5         |                                                                                                                      | -<br>nted: Read as '0                                       | )'                     |                      |                 |                   |             |

| bit 4-0       | -                                                                                                                    | 0>: PLL Phase [                                             |                        | it Divider bits (al  | so denoted as   | 'N1', PLL presc   | aler)       |

|               | •                                                                                                                    | 1/0                                                         |                        |                      |                 |                   |             |

|               | 00001 = Inp                                                                                                          | ut/3                                                        |                        |                      |                 |                   |             |

# **Note 1:** This bit is cleared when the ROI bit is set and an interrupt occurs.

2: This register is reset only on a Power-on Reset (POR).

### 10.2.2 IDLE MODE

The following occur in Idle mode:

- The CPU stops executing instructions.

- The WDT is automatically cleared.

- The system clock source remains active. By default, all peripheral modules continue to operate normally from the system clock source, but can also be selectively disabled (see Section 10.4 "Peripheral Module Disable").

- If the WDT or FSCM is enabled, the LPRC also remains active.

The device wakes from Idle mode on any of these events:

- Any interrupt that is individually enabled

- Any device Reset

- A WDT time-out

On wake-up from Idle mode, the clock is reapplied to the CPU and instruction execution will begin (2 to 4 cycles later), starting with the instruction following the PWRSAV instruction, or the first instruction in the ISR.

### 10.2.3 INTERRUPTS COINCIDENT WITH POWER SAVE INSTRUCTIONS

Any interrupt that coincides with the execution of a PWRSAV instruction is held off until entry into Sleep or Idle mode has completed. The device then wakes up from Sleep or Idle mode.

### 10.3 Doze Mode

The preferred strategies for reducing power consumption are changing clock speed and invoking one of the power-saving modes. In some circumstances, this cannot be practical. For example, it may be necessary for an application to maintain uninterrupted synchronous communication, even while it is doing nothing else. Reducing system clock speed can introduce communication errors, while using a power-saving mode can stop communications completely.

Doze mode is a simple and effective alternative method to reduce power consumption while the device is still executing code. In this mode, the system clock continues to operate from the same source and at the same speed. Peripheral modules continue to be clocked at the same speed, while the CPU clock speed is reduced. Synchronization between the two clock domains is maintained, allowing the peripherals to access the SFRs while the CPU executes code at a slower rate. Doze mode is enabled by setting the DOZEN bit (CLKDIV<11>). The ratio between peripheral and core clock speed is determined by the DOZE<2:0> bits (CLKDIV<14:12>). There are eight possible configurations, from 1:1 to 1:128, with 1:1 being the default setting.

Programs can use Doze mode to selectively reduce power consumption in event-driven applications. This allows clock-sensitive functions, such as synchronous communications, to continue without interruption while the CPU idles, waiting for something to invoke an interrupt routine. An automatic return to full-speed CPU operation on interrupts can be enabled by setting the ROI bit (CLKDIV<15>). By default, interrupt events have no effect on Doze mode operation.

For example, suppose the device is operating at 20 MIPS and the ECAN module has been configured for 500 kbps based on this device operating speed. If the device is placed in Doze mode with a clock frequency ratio of 1:4, the ECAN module continues to communicate at the required bit rate of 500 kbps, but the CPU now starts executing instructions at a frequency of 5 MIPS.

# 10.4 Peripheral Module Disable

The Peripheral Module Disable (PMD) registers provide a method to disable a peripheral module by stopping all clock sources supplied to that module. When a peripheral is disabled using the appropriate PMD control bit, the peripheral is in a minimum power consumption state. The control and status registers associated with the peripheral are also disabled, so writes to those registers do not have effect and read values are invalid.

A peripheral module is enabled only if both the associated bit in the PMD register is cleared and the peripheral is supported by the specific PIC MCU variant. If the peripheral is present in the device, it is enabled in the PMD register by default.

**Note:** If a PMD bit is set, the corresponding module is disabled after a delay of one instruction cycle. Similarly, if a PMD bit is cleared, the corresponding module is enabled after a delay of one instruction cycle (assuming the module control registers are already configured to enable module operation).

#### 11.6.3 CONTROLLING CONFIGURATION CHANGES

Because peripheral remapping can be changed during run time, some restrictions on peripheral remapping are needed to prevent accidental configuration changes. PIC24H devices include three features to prevent alterations to the peripheral map:

- Control register lock sequence

- · Continuous state monitoring

- Configuration bit pin select lock

#### 11.6.3.1 Control Register Lock

Under normal operation, writes to the RPINRx and RPORx registers are not allowed. Attempted writes appear to execute normally, but the contents of the registers remain unchanged. To change these registers, they must be unlocked in hardware. The register lock is controlled by the IOLOCK bit (OSCCON<6>). Setting IOLOCK prevents writes to the control registers; clearing IOLOCK allows writes.

To set or clear IOLOCK, a specific command sequence must be executed:

- 1. Write 0x46 to OSCCON<7:0>.

- 2. Write 0x57 to OSCCON<7:0>.

- 3. Clear (or set) the IOLOCK bit as a single operation.

| Note: | MPLAB <sup>®</sup> C30 provides built-in C language functions for unlocking the OSCCON register: |

|-------|--------------------------------------------------------------------------------------------------|