Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 40 MIPs                                                                        |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                   |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                     |

| Number of I/O              | 35                                                                             |

| Program Memory Size        | 64KB (22K x 24)                                                                |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 8K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                      |

| Data Converters            | A/D 13x10b/12b                                                                 |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 44-VQFN Exposed Pad                                                            |

| Supplier Device Package    | 44-QFN (8x8)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24hj64gp504t-i-ml |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

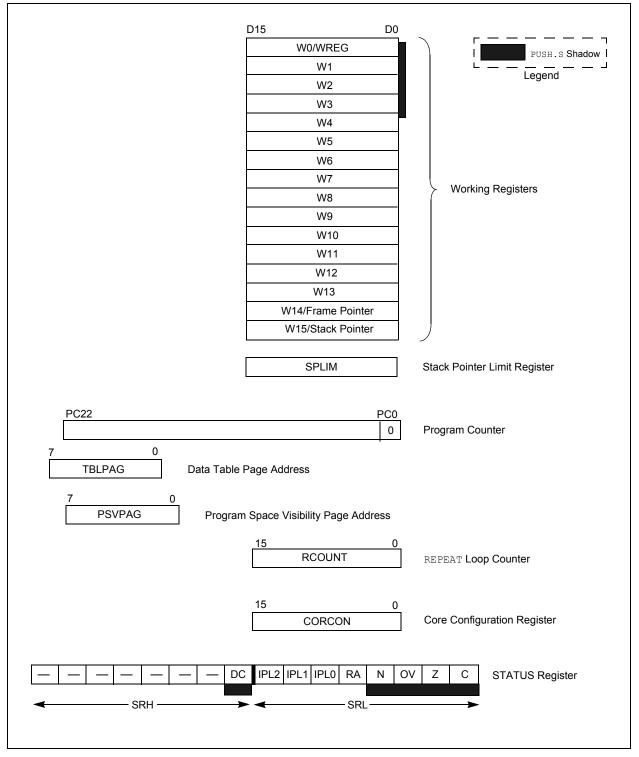

# FIGURE 3-2: PIC24HJ32GP302/304, PIC24HJ64GPX02/X04 AND PIC24HJ128GPX02/X04 PROGRAMMER'S MODEL

## 4.0 MEMORY ORGANIZATION

| Note: | This data sheet summarizes the features      |

|-------|----------------------------------------------|

|       | of the PIC24HJ32GP302/304,                   |

|       | PIC24HJ64GPX02/X04 and                       |

|       | PIC24HJ128GPX02/X04 families of              |

|       | devices. It is not intended to be a compre-  |

|       | hensive reference source. To complement      |

|       | the information in this data sheet, refer to |

|       | Section 4. "Program Memory"                  |

|       | (DS70203) of the "dsPIC33F/PIC24H            |

|       | Family Reference Manual", which is avail-    |

|       | able from the Microchip web site             |

|       | (www.microchip.com).                         |

The PIC24HJ32GP302/304, PIC24HJ64GPX02/X04 and PIC24HJ128GPX02/X04 architecture features separate program and data memory spaces and buses. This architecture also allows the direct access of program memory from the data space during code execution.

### 4.1 Program Address Space

The program address memory space of the PIC24HJ32GP302/304, PIC24HJ64GPX02/X04 and PIC24HJ128GPX02/X04 devices is 4M instructions. The space is addressable by a 24-bit value derived either from the 23-bit Program Counter (PC) during program execution, or from table operation or data space remapping as described in Section 4.6 "Interfacing Program and Data Memory Spaces".

User application access to the program memory space is restricted to the lower half of the address range (0x000000 to 0x7FFFFF). The exception is the use of TBLRD/TBLWT operations, which use TBLPAG<7> to permit access to the Configuration bits and Device ID sections of the configuration memory space.

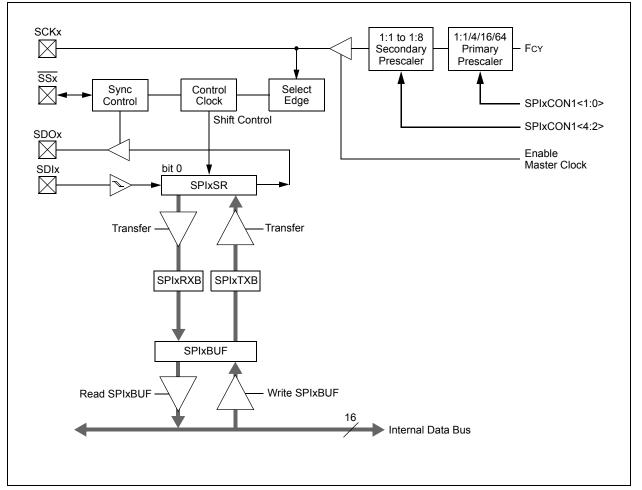

The memory map for the PIC24HJ32GP302/304, PIC24HJ64GPX02/X04 and PIC24HJ128GPX02/X04 devices is shown in Figure 4-1.

|      | PIC24HJ32GP302/304                                   | PIC24HJ64GPX02/X04                | PIC24HJ128GPX02/X04                                                                 |

|------|------------------------------------------------------|-----------------------------------|-------------------------------------------------------------------------------------|

| 4    | GOTO Instruction                                     | GOTO Instruction                  | GOTO Instruction 0x000000<br>Reset Address 0x000002                                 |

|      | Reset Address                                        | Reset Address                     | 0x000004                                                                            |

|      | Interrupt Vector Table                               | Interrupt Vector Table            | Interrupt Vector Table 0x0000FE                                                     |

|      | Reserved                                             | Reserved                          | <u>Reserved</u> 0x000100<br>0x000104                                                |

|      | Alternate Vector Table                               | Alternate Vector Table            | Alternate vector rable 0x0001FE                                                     |

| 2000 | User Program<br>Flash Memory<br>(11264 instructions) | User Program<br>Flash Memory      | 0x000200<br>0x0057FE<br>0x0057FE<br>0x005800                                        |

|      | Unimplemented                                        |                                   | User Program<br>Flash Memory<br>(44032 instructions)<br>                            |

|      | (Read '0's)                                          | Unimplemented                     | 0x0157FE                                                                            |

|      |                                                      | (Read '0's)                       | 0x015800                                                                            |

|      |                                                      |                                   | Unimplemented<br>(Read '0's)<br>0x7FFFE                                             |

|      | Reserved                                             | Reserved                          | 0x800000<br>Reserved                                                                |

|      | Device Configuration<br>Registers                    | Device Configuration<br>Registers | Device Configuration 0xF7FFE<br>Device Configuration 0xF80000<br>Registers 0xF80017 |

|      | Reserved                                             | Reserved                          | Care Contraction (0xF80017)<br>0xF80018<br>Reserved                                 |

| 0    |                                                      |                                   | DEVID (2)                                                                           |

|      | Reserved                                             | Reserved                          | 0xFF0002           Reserved           0xFFFFE                                       |

NVMCON: FLASH MEMORY CONTROL REGISTER

## 5.6 Flash Memory Control Registers

**REGISTER 5-1:**

| R/SO-0 <sup>(1)</sup> | R/W-0 <sup>(1)</sup>                                                                                                                     | R/W-0 <sup>(1)</sup>            |                |                      |                       |                      |                      |  |  |  |

|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|----------------|----------------------|-----------------------|----------------------|----------------------|--|--|--|

| WR                    | R/W-000                                                                                                                                  | WRERR                           | U-0            | U-0                  | U-0                   | U-0                  | U-0                  |  |  |  |

|                       | WREN                                                                                                                                     | WRERR                           | —              | _                    | —                     |                      |                      |  |  |  |

| bit 15                |                                                                                                                                          |                                 |                |                      |                       |                      | bit 8                |  |  |  |

| U-0                   | R/W-0 <sup>(1)</sup>                                                                                                                     | U-0                             | U-0            | R/W-0 <sup>(1)</sup> | R/W-0 <sup>(1)</sup>  | R/W-0 <sup>(1)</sup> | R/W-0 <sup>(1)</sup> |  |  |  |

| _                     | ERASE                                                                                                                                    |                                 | _              |                      | NVMOP                 | <3:0> <sup>(2)</sup> |                      |  |  |  |

| bit 7                 | ·                                                                                                                                        |                                 |                |                      |                       |                      | bit 0                |  |  |  |

| Legend:               |                                                                                                                                          | SO = Settal                     | ole only bit   |                      |                       |                      |                      |  |  |  |

| R = Readable          | bit                                                                                                                                      | W = Writabl                     | e bit          | U = Unimpler         | mented bit, read      | as '0'               |                      |  |  |  |

| -n = Value at F       | POR                                                                                                                                      | '1' = Bit is s                  | et             | '0' = Bit is cle     | ared                  | x = Bit is unkr      | nown                 |  |  |  |

| bit 15                | WR: Write Con                                                                                                                            | trol bit                        |                |                      |                       |                      |                      |  |  |  |

|                       | 1 = Initiates a                                                                                                                          | Flash memor                     | y program or   | erase operation      | on. The operatio      | on is self-timed     | and the bit is       |  |  |  |

|                       |                                                                                                                                          | hardware on                     |                |                      |                       |                      |                      |  |  |  |

|                       | 0 = Program of                                                                                                                           | •                               | tion is comple | ete and inactive     | 9                     |                      |                      |  |  |  |

| bit 14                | WREN: Write E                                                                                                                            |                                 |                |                      |                       |                      |                      |  |  |  |

|                       | 1 = Enable Fla                                                                                                                           |                                 |                |                      |                       |                      |                      |  |  |  |

| h:: 40                | 0 = Inhibit Flas                                                                                                                         |                                 | -              | IS                   |                       |                      |                      |  |  |  |

| bit 13                | <b>WRERR:</b> Write Sequence Error Flag bit<br>1 = An improper program or erase sequence attempt or termination has occurred (bit is set |                                 |                |                      |                       |                      |                      |  |  |  |

|                       |                                                                                                                                          | er program or<br>Illy on any se |                |                      | termination has       | occurred (bit i      | s set                |  |  |  |

|                       | 0 = The progra                                                                                                                           |                                 |                |                      | /                     |                      |                      |  |  |  |

| bit 12-7              | Unimplemente                                                                                                                             |                                 |                |                      |                       |                      |                      |  |  |  |

| bit 6                 |                                                                                                                                          |                                 |                |                      |                       |                      |                      |  |  |  |

| 2.00                  | <b>ERASE:</b> Erase/Program Enable bit<br>1 = Perform the erase operation specified by NVMOP<3:0> on the next WR command                 |                                 |                |                      |                       |                      |                      |  |  |  |

|                       |                                                                                                                                          |                                 |                |                      | ><3:0> on the network |                      |                      |  |  |  |

| bit 5-4               | Unimplemente                                                                                                                             | d: Read as '                    | )'             |                      |                       |                      |                      |  |  |  |

| bit 3-0               | NVMOP<3:0>:                                                                                                                              | NVM Operati                     | on Select bits | <sub>S</sub> (2)     |                       |                      |                      |  |  |  |

|                       | If ERASE = 1:                                                                                                                            |                                 |                |                      |                       |                      |                      |  |  |  |

|                       | 1111 <b>= Memor</b>                                                                                                                      | •                               | operation      |                      |                       |                      |                      |  |  |  |

|                       | 1110 = Reserv                                                                                                                            |                                 |                |                      |                       |                      |                      |  |  |  |

|                       | 1101 = Erase General Segment                                                                                                             |                                 |                |                      |                       |                      |                      |  |  |  |

|                       | 1100 = Erase Secure Segment<br>1011 = Reserved                                                                                           |                                 |                |                      |                       |                      |                      |  |  |  |

|                       | 0011 = Reserved                                                                                                                          |                                 |                |                      |                       |                      |                      |  |  |  |

|                       | 0010 = Memory page erase operation                                                                                                       |                                 |                |                      |                       |                      |                      |  |  |  |

|                       | 0001 = No operation                                                                                                                      |                                 |                |                      |                       |                      |                      |  |  |  |

|                       | 0000 <b>= Erase</b> a                                                                                                                    | a single Confi                  | guration regis | ster byte            |                       |                      |                      |  |  |  |

|                       | If ERASE = 0:                                                                                                                            |                                 |                |                      |                       |                      |                      |  |  |  |

|                       | 1111 <b>= No ope</b>                                                                                                                     |                                 |                |                      |                       |                      |                      |  |  |  |

|                       | 1110 = Reserved                                                                                                                          |                                 |                |                      |                       |                      |                      |  |  |  |

|                       | 1101 = No operation<br>1100 = No operation                                                                                               |                                 |                |                      |                       |                      |                      |  |  |  |

|                       | 1011 = Reserv                                                                                                                            |                                 |                |                      |                       |                      |                      |  |  |  |

|                       | 0011 = Memor                                                                                                                             | y word progra                   | m operation    |                      |                       |                      |                      |  |  |  |

|                       | 0010 = No ope                                                                                                                            | ration                          |                |                      |                       |                      |                      |  |  |  |

|                       | 0001 = Memory                                                                                                                            |                                 |                |                      |                       |                      |                      |  |  |  |

|                       | 0000 <b>= Progra</b> r                                                                                                                   | n a single Co                   | nfiguration re | gister byte          |                       |                      |                      |  |  |  |

| Note 1: The           | ese bits can only                                                                                                                        | be reset on a                   | POR.           |                      |                       |                      |                      |  |  |  |

| 2: All                | other combination                                                                                                                        | ns of NVMOF                     | <3:0> are un   | implemented          |                       |                      |                      |  |  |  |

2: All other combinations of NVMOP<3:0> are unimplemented.

## REGISTER 7-5: IFS0: INTERRUPT FLAG STATUS REGISTER 0 (CONTINUED)

| bit 2 | OC1IF: Output Compare Channel 1 Interrupt Flag Status bit                                           |

|-------|-----------------------------------------------------------------------------------------------------|

|       | <ul><li>1 = Interrupt request has occurred</li><li>0 = Interrupt request has not occurred</li></ul> |

| bit 1 | IC1IF: Input Capture Channel 1 Interrupt Flag Status bit                                            |

|       | 1 = Interrupt request has occurred                                                                  |

|       | 0 = Interrupt request has not occurred                                                              |

| bit 0 | <b>INTOIF:</b> External Interrupt 0 Flag Status bit                                                 |

|       | 1 = Interrupt request has occurred                                                                  |

|       | 0 = Interrupt request has not occurred                                                              |

| U-0          | R/W-1                                                      | R/W-0                                    | R/W-0         | U-0               | R/W-1            | R/W-0           | R/W-0 |  |  |  |  |  |

|--------------|------------------------------------------------------------|------------------------------------------|---------------|-------------------|------------------|-----------------|-------|--|--|--|--|--|

| _            |                                                            | U2TXIP<2:0>                              |               | —                 |                  | U2RXIP<2:0>     |       |  |  |  |  |  |

| bit 15       |                                                            |                                          |               |                   |                  |                 | bit 8 |  |  |  |  |  |

|              |                                                            |                                          |               |                   |                  |                 |       |  |  |  |  |  |

| U-0          | R/W-1                                                      | R/W-0                                    | R/W-0         | U-0               | R/W-1            | R/W-0           | R/W-0 |  |  |  |  |  |

| —            |                                                            | INT2IP<2:0>                              |               |                   |                  | T5IP<2:0>       |       |  |  |  |  |  |

| bit 7        |                                                            |                                          |               |                   |                  |                 | bit ( |  |  |  |  |  |

| Legend:      |                                                            |                                          |               |                   |                  |                 |       |  |  |  |  |  |

| R = Readab   | le bit                                                     | W = Writable                             | bit           | U = Unimple       | emented bit, rea | ad as '0'       |       |  |  |  |  |  |

| -n = Value a | t POR                                                      | '1' = Bit is set                         |               | '0' = Bit is cl   | eared            | x = Bit is unkr | nown  |  |  |  |  |  |

| bit 15       | Unimpleme                                                  | ented: Read as '                         | 0'            |                   |                  |                 |       |  |  |  |  |  |

| bit 14-12    | -                                                          | 0>: UART2 Trans                          |               | upt Prioritv bits |                  |                 |       |  |  |  |  |  |

|              |                                                            | rupt is priority 7 (                     |               |                   |                  |                 |       |  |  |  |  |  |

|              | •                                                          |                                          |               |                   |                  |                 |       |  |  |  |  |  |

|              | •                                                          |                                          |               |                   |                  |                 |       |  |  |  |  |  |

|              | 001 = Interrupt is priority 1                              |                                          |               |                   |                  |                 |       |  |  |  |  |  |

|              | 000 = Interr                                               | upt source is dis                        | abled         |                   |                  |                 |       |  |  |  |  |  |

| bit 11       | Unimpleme                                                  | ented: Read as '                         | 0'            |                   |                  |                 |       |  |  |  |  |  |

| bit 10-8     | U2RXIP<2:0>: UART2 Receiver Interrupt Priority bits        |                                          |               |                   |                  |                 |       |  |  |  |  |  |

|              | 111 = Interrupt is priority 7 (highest priority interrupt) |                                          |               |                   |                  |                 |       |  |  |  |  |  |

|              | •                                                          | •                                        |               |                   |                  |                 |       |  |  |  |  |  |

|              | •                                                          |                                          |               |                   |                  |                 |       |  |  |  |  |  |

|              | 001 = Interrupt is priority 1                              |                                          |               |                   |                  |                 |       |  |  |  |  |  |

|              | 000 = Interr                                               | 000 = Interrupt source is disabled       |               |                   |                  |                 |       |  |  |  |  |  |

| bit 7        | Unimpleme                                                  | ented: Read as '                         | 0'            |                   |                  |                 |       |  |  |  |  |  |

| bit 6-4      |                                                            | >: External Inter                        |               |                   |                  |                 |       |  |  |  |  |  |

|              | 111 = Interrupt is priority 7 (highest priority interrupt) |                                          |               |                   |                  |                 |       |  |  |  |  |  |

|              | •                                                          |                                          |               |                   |                  |                 |       |  |  |  |  |  |

|              | •                                                          |                                          |               |                   |                  |                 |       |  |  |  |  |  |

|              |                                                            | rupt is priority 1<br>rupt source is dis | abled         |                   |                  |                 |       |  |  |  |  |  |

| bit 3        | Unimpleme                                                  | ented: Read as '                         | 0'            |                   |                  |                 |       |  |  |  |  |  |

| bit 2-0      | T5IP<2:0>:                                                 | Timer5 Interrupt                         | Priority bits |                   |                  |                 |       |  |  |  |  |  |

|              | 111 = Interr<br>•                                          | rupt is priority 7 (                     | highest prior | ity interrupt)    |                  |                 |       |  |  |  |  |  |

|              | •                                                          |                                          |               |                   |                  |                 |       |  |  |  |  |  |

|              | •                                                          | and the method of the state              |               |                   |                  |                 |       |  |  |  |  |  |

|              |                                                            | rupt is priority 1                       |               |                   |                  |                 |       |  |  |  |  |  |

000 = Interrupt source is disabled

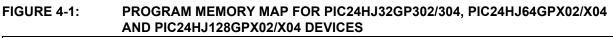

### 9.1.3 PLL CONFIGURATION

The primary oscillator and internal FRC oscillator can optionally use an on-chip PLL to obtain higher speeds of operation. The PLL provides significant flexibility in selecting the device operating speed. A block diagram of the PLL is shown in Figure 9-2.

The output of the primary oscillator or FRC, denoted as 'FIN', is divided down by a prescale factor (N1) of 2, 3, ... or 33 before being provided to the PLL's Voltage Controlled Oscillator (VCO). The input to the VCO must be selected in the range of 0.8 MHz to 8 MHz. The prescale factor 'N1' is selected using the PLLPRE<4:0> bits (CLKDIV<4:0>).

The PLL Feedback Divisor, selected using the PLLDIV<8:0> bits (PLLFBD<8:0>), provides a factor 'M', by which the input to the VCO is multiplied. This factor must be selected such that the resulting VCO output frequency is in the range of 100 MHz to 200 MHz.

The VCO output is further divided by a postscale factor 'N2'. This factor is selected using the PLLPOST<1:0> bits (CLKDIV<7:6>). 'N2' can be either 2, 4 or 8, and must be selected such that the PLL output frequency (Fosc) is in the range of 12.5 MHz to 80 MHz, which generates device operating speeds of 6.25-40 MIPS. For a primary oscillator or FRC oscillator, output 'FIN', the PLL output 'FOSC' is given by:

#### EQUATION 9-2: Fosc CALCULATION

$$FOSC = FIN \bullet \left(\frac{M}{N1 \bullet N2}\right)$$

For example, suppose a 10 MHz crystal is being used with the selected oscillator mode of XT with PLL.

- If PLLPRE<4:0> = 0, then N1 = 2. This yields a VCO input of 10/2 = 5 MHz, which is within the acceptable range of 0.8-8 MHz.

- If PLLDIV<8:0> = 0x1E, then M = 32. This yields a VCO output of 5 x 32 = 160 MHz, which is within the 100-200 MHz ranged needed.

- If PLLPOST<1:0> = 0, then N2 = 2. This provides a Fosc of 160/2 = 80 MHz. The resultant device operating speed is 80/2 = 40 MIPS.

#### EQUATION 9-3: XT WITH PLL MODE EXAMPLE

$$F_{CY} = \frac{F_{OSC}}{2} = \frac{1}{2} \left( \frac{10000000 \bullet 32}{2 \bullet 2} \right) = 40 MIPS$$

# FIGURE 9-2: PIC24HJ32GP302/304, PIC24HJ64GPX02/X04 AND PIC24HJ128GPX02/X04 PLL BLOCK DIAGRAM

| Input Name              | Function Name | Register | Configuration<br>Bits |

|-------------------------|---------------|----------|-----------------------|

| External Interrupt 1    | INT1          | RPINR0   | INT1R<4:0>            |

| External Interrupt 2    | INT2          | RPINR1   | INT2R<4:0>            |

| Timer2 External Clock   | T2CK          | RPINR3   | T2CKR<4:0>            |

| Timer3 External Clock   | T3CK          | RPINR3   | T3CKR<4:0>            |

| Timer4 External Clock   | T4CK          | RPINR4   | T4CKR<4:0>            |

| Timer5 External Clock   | T5CK          | RPINR4   | T5CKR<4:0>            |

| Input Capture 1         | IC1           | RPINR7   | IC1R<4:0>             |

| Input Capture 2         | IC2           | RPINR7   | IC2R<4:0>             |

| Input Capture 7         | IC7           | RPINR10  | IC7R<4:0>             |

| Input Capture 8         | IC8           | RPINR10  | IC8R<4:0>             |

| Output Compare Fault A  | OCFA          | RPINR11  | OCFAR<4:0>            |

| UART1 Receive           | U1RX          | RPINR18  | U1RXR<4:0>            |

| UART1 Clear To Send     | U1CTS         | RPINR18  | U1CTSR<4:0>           |

| UART2 Receive           | U2RX          | RPINR19  | U2RXR<4:0>            |

| UART2 Clear To Send     | U2CTS         | RPINR19  | U2CTSR<4:0>           |

| SPI1 Data Input         | SDI1          | RPINR20  | SDI1R<4:0>            |

| SPI1 Clock Input        | SCK1          | RPINR20  | SCK1R<4:0>            |

| SPI1 Slave Select Input | SS1           | RPINR21  | SS1R<4:0>             |

| SPI2 Data Input         | SDI2          | RPINR22  | SDI2R<4:0>            |

| SPI2 Clock Input        | SCK2          | RPINR22  | SCK2R<4:0>            |

| SPI2 Slave Select Input | SS2           | RPINR23  | SS2R<4:0>             |

| ECAN1 Receive           | CIRX          | RPINR26  | CIRXR<4:0>            |

# TABLE 11-1: SELECTABLE INPUT SOURCES (MAPS INPUT TO FUNCTION)<sup>(1)</sup>

**Note 1:** Unless otherwise noted, all inputs use Schmitt input buffers.

### REGISTER 11-7: RPINR11: PERIPHERAL PIN SELECT INPUT REGISTER 11

| U-0             | U-0 | U-0              | U-0   | U-0                                | U-0                             | U-0   | U-0   |

|-----------------|-----|------------------|-------|------------------------------------|---------------------------------|-------|-------|

| _               |     | -                | _     | —                                  | —                               | —     | —     |

| bit 15          |     |                  |       |                                    |                                 |       | bit 8 |

|                 |     |                  |       |                                    |                                 |       |       |

| U-0             | U-0 | U-0              | R/W-1 | R/W-1                              | R/W-1                           | R/W-1 | R/W-1 |

| _               | _   | _                |       |                                    | OCFAR<4:0>                      |       |       |

| bit 7           |     |                  |       |                                    |                                 |       | bit 0 |

|                 |     |                  |       |                                    |                                 |       |       |

| Legend:         |     |                  |       |                                    |                                 |       |       |

| R = Readable b  | oit | W = Writable bit |       | U = Unimplemented bit, read as '0' |                                 |       |       |

| -n = Value at P | OR  | '1' = Bit is set |       | '0' = Bit is cle                   | t is cleared x = Bit is unknown |       |       |

| •               |     |                  |       |                                    |                                 |       |       |

bit 15-5 Unimplemented: Read as '0'

| bit 4-0             | <b>OCFAR&lt;4:0&gt;:</b> Assign Output Compare A (OCFA) to the corresponding RPn pin |

|---------------------|--------------------------------------------------------------------------------------|

| DIL <del>4</del> -0 | OCIAN 4.0/. Assign Output Compare A (OCIA) to the corresponding IV in pin            |

11111 = Input tied to Vss 11001 = Input tied to RP25

.

• 00001 = Input tied to RP1 00000 = Input tied to RP0

#### REGISTER 11-11: RPINR21: PERIPHERAL PIN SELECT INPUT REGISTER 21

| bit 7  | -   | ÷   |       |       |           |       | bit C |

|--------|-----|-----|-------|-------|-----------|-------|-------|

|        |     |     |       |       | SS1R<4:0> |       |       |

| U-0    | U-0 | U-0 | R/W-1 | R/W-1 | R/W-1     | R/W-1 | R/W-1 |

| bit 15 |     |     |       |       |           |       | bit 8 |

| _      | —   | —   | _     | —     | _         | —     | —     |

| U-0    | U-0 | U-0 | U-0   | U-0   | U-0       | U-0   | U-0   |

bit 15-5 Unimplemented: Read as '0'

bit 4-0

SS1R<4:0>: Assign SPI1 Slave Select Input (SS1) to the corresponding RPn pin 11111 = Input tied to Vss 11001 = Input tied to RP25

00001 = Input tied to RP1 00000 = Input tied to RP0

## 15.3 Output Compare Control Registers

## **REGISTER 15-1:** OCxCON: OUTPUT COMPAREX CONTROL REGISTER (x = 1, 2, 3 OR 4)

| U-0                                  | U-0                                                                                                                                 | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | U-0                                                                                                                      | U-0                                                            | U-0                   | U-0             | U-0   |  |  |

|--------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|-----------------------|-----------------|-------|--|--|

|                                      | —                                                                                                                                   | OCSIDL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | _                                                                                                                        | —                                                              |                       | —               | —     |  |  |

| bit 15                               |                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                          |                                                                |                       |                 | bit 8 |  |  |

|                                      |                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                          |                                                                |                       |                 |       |  |  |

| U-0                                  | U-0                                                                                                                                 | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | R-0 HC                                                                                                                   | R/W-0                                                          | R/W-0                 | R/W-0           | R/W-0 |  |  |

|                                      | —                                                                                                                                   | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | OCFLT                                                                                                                    | OCTSEL                                                         |                       | OCM<2:0>        | 1:10  |  |  |

| bit 7                                |                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                          |                                                                |                       |                 | bit 0 |  |  |

| Legend: HC = Cleared in Hardware     |                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | HS = Set in H                                                                                                            | Hardware                                                       |                       |                 |       |  |  |

| R = Readab                           | ole bit                                                                                                                             | W = Writable bi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | t                                                                                                                        | U = Unimple                                                    | mented bit, rea       | d as '0'        |       |  |  |

| -n = Value a                         | it POR                                                                                                                              | '1' = Bit is set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                          | '0' = Bit is cle                                               | eared                 | x = Bit is unki | nown  |  |  |

| bit 13<br>bit 12-5<br>bit 4<br>bit 3 | 1 = Output Co<br>0 = Output Co<br>Unimplemen<br>OCFLT: PWM<br>1 = PWM Fau<br>0 = No PWM<br>(This bit is on<br>OCTSEL: Ou            | Unimplemented: Read as '0'<br>OCSIDL: Stop Output Compare in Idle Mode Control bit<br>1 = Output Compare x halts in CPU Idle mode<br>0 = Output Compare x continues to operate in CPU Idle mode<br>Unimplemented: Read as '0'<br>OCFLT: PWM Fault Condition Status bit<br>1 = PWM Fault condition has occurred (cleared in hardware only)<br>0 = No PWM Fault condition has occurred<br>(This bit is only used when OCM<2:0> = 111)<br>OCTSEL: Output Compare Timer Select bit<br>1 = Timer3 is the clock source for Compare x |                                                                                                                          |                                                                |                       |                 |       |  |  |

| bit 2-0                              | OCM<2:0>:0<br>111 = PWM n<br>110 = PWM n<br>101 = Initializ<br>100 = Initializ<br>011 = Compa<br>010 = Initializ<br>001 = Initializ | Output Compare<br>mode on OCx, F<br>mode on OCx, F<br>ze OCx pin low, g<br>are event toggles<br>ze OCx pin high,<br>ze OCx pin low, g<br>t compare chann                                                                                                                                                                                                                                                                                                                                                                       | Mode Select b<br>ault pin enable<br>ault pin disable<br>generate contir<br>generate single<br>s OCx pin<br>compare event | oits<br>ed<br>huous output p<br>output pulse<br>t forces OCx p | on OCx pin<br>bin low | bin             |       |  |  |

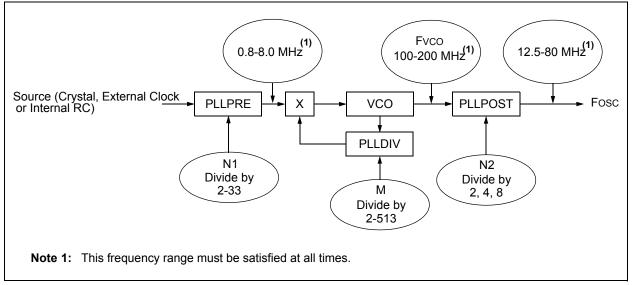

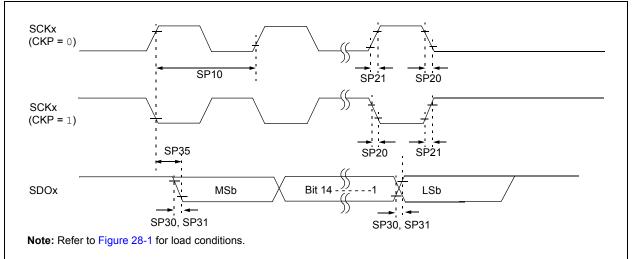

## 16.0 SERIAL PERIPHERAL INTERFACE (SPI)

- Note 1: This data sheet summarizes the features PIC24HJ32GP302/304, of the PIC24HJ64GPX02/X04 and PIC24HJ128GPX02/X04 families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 18. "Serial Peripheral Interface (SPI)" (DS70206) of the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Serial Peripheral Interface (SPI) module is a synchronous serial interface useful for communicating with other peripheral or microcontroller devices. These peripheral devices can be serial EEPROMs, shift registers, display drivers, analog-to-digital converters, etc. The SPI module is compatible with Motorola<sup>®</sup> SPI and SIOP.

Each SPI module consists of a 16-bit shift register, SPIxSR (where x = 1 or 2), used for shifting data in and out, and a buffer register, SPIxBUF. A control register, SPIxCON, configures the module. Additionally, a status register, SPIxSTAT, indicates status conditions.

The serial interface consists of 4 pins:

- · SDIx (serial data input)

- SDOx (serial data output)

- <u>SCKx</u> (shift clock input or output)

- SSx (active-low slave select)

In Master mode operation, SCK is a clock output. In Slave mode, it is a clock input.

#### FIGURE 16-1: SPI MODULE BLOCK DIAGRAM

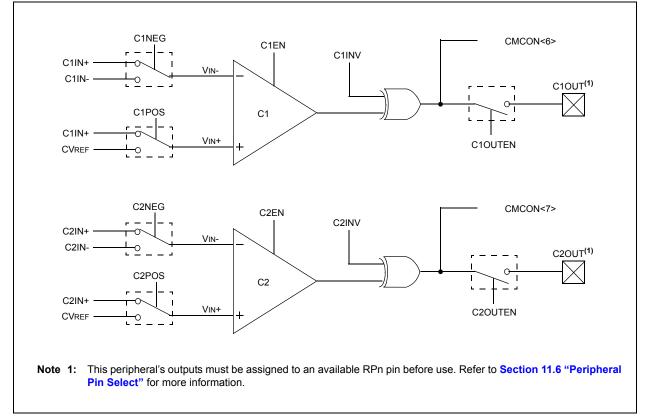

## 21.0 COMPARATOR MODULE

- **Note 1:** This data sheet summarizes the features the PIC24HJ32GP302/304. of PIC24HJ64GPX02/X04 and PIC24HJ128GPX02/X04 families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 34. "Comparator" (DS70212) of the "dsPIC33F/ PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Comparator module provides a set of dual input comparators. The inputs to the comparator can be configured to use any one of the four pin inputs (C1IN+, C1IN-, C2IN+ and C2IN-) as well as the Comparator Voltage Reference Input (CVREF).

Note: This peripheral contains output functions that may need to be configured by the peripheral pin select feature. For more information, see Section 11.6 "Peripheral Pin Select".

#### FIGURE 21-1: COMPARATOR I/O OPERATING MODES

## 21.2 Comparator Control Register

| R/W-0           | U-0                                                                                                                                  | R/W-0                               | R/W-0  | R/W-0            | R/W-0           | R/W-0                  | R/W-0                 |  |  |  |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|--------|------------------|-----------------|------------------------|-----------------------|--|--|--|

| CMIDL           | _                                                                                                                                    | C2EVT                               | C1EVT  | C2EN             | C1EN            | C2OUTEN <sup>(1)</sup> | C1OUTEN <sup>(2</sup> |  |  |  |

| bit 15          |                                                                                                                                      | •                                   |        |                  |                 |                        | bit 8                 |  |  |  |

|                 |                                                                                                                                      |                                     |        |                  |                 |                        |                       |  |  |  |

| R-0             | R-0                                                                                                                                  | R/W-0                               | R/W-0  | R/W-0            | R/W-0           | R/W-0                  | R/W-0                 |  |  |  |

| C2OUT           | C1OUT                                                                                                                                | C2INV                               | C1INV  | C2NEG            | C2POS           | C1NEG                  | C1POS                 |  |  |  |

| bit 7           |                                                                                                                                      |                                     |        |                  |                 |                        | bit (                 |  |  |  |

| Legend:         |                                                                                                                                      |                                     |        |                  |                 |                        |                       |  |  |  |

| R = Readable I  | oit                                                                                                                                  | W = Writable                        | bit    | U = Unimpler     | mented bit, rea | ad as '0'              |                       |  |  |  |

| -n = Value at P | OR                                                                                                                                   | '1' = Bit is set                    |        | '0' = Bit is cle |                 | x = Bit is unkn        | iown                  |  |  |  |

|                 |                                                                                                                                      |                                     |        |                  |                 |                        |                       |  |  |  |

| bit 15          | CMIDL: Stop                                                                                                                          |                                     |        |                  |                 |                        |                       |  |  |  |

|                 |                                                                                                                                      |                                     |        |                  | nerate interrup | ots. Module is stil    | ll enabled            |  |  |  |

| <b>L:1</b> 4 4  |                                                                                                                                      | normal modul                        | -      | Idle mode        |                 |                        |                       |  |  |  |

| bit 14          | -                                                                                                                                    | ted: Read as '                      |        |                  |                 |                        |                       |  |  |  |

| bit 13          | <b>C2EVT:</b> Comparator 2 Event<br>1 = Comparator output changed states                                                             |                                     |        |                  |                 |                        |                       |  |  |  |

|                 |                                                                                                                                      | tor output did                      |        | ates             |                 |                        |                       |  |  |  |

| bit 12          | <b>C1EVT:</b> Comparator 1 Event                                                                                                     |                                     |        |                  |                 |                        |                       |  |  |  |

|                 |                                                                                                                                      | tor output chai<br>tor output did i |        | ates             |                 |                        |                       |  |  |  |

| bit 11          | C2EN: Compa                                                                                                                          | arator 2 Enable                     | 9      |                  |                 |                        |                       |  |  |  |

|                 | 1 = Compara<br>0 = Compara                                                                                                           | tor is enabled<br>tor is disabled   |        |                  |                 |                        |                       |  |  |  |

| bit 10          | C1EN: Compa                                                                                                                          | arator 1 Enable                     | Э      |                  |                 |                        |                       |  |  |  |

|                 | 1 = Comparator is enabled                                                                                                            |                                     |        |                  |                 |                        |                       |  |  |  |

|                 | 0 = Comparator is disabled                                                                                                           |                                     |        |                  |                 |                        |                       |  |  |  |

| bit 9           |                                                                                                                                      | omparator 2 C                       | -      |                  |                 |                        |                       |  |  |  |

|                 | <ul> <li>1 = Comparator output is driven on the output pad</li> <li>0 = Comparator output is not driven on the output pad</li> </ul> |                                     |        |                  |                 |                        |                       |  |  |  |

| bit 8           |                                                                                                                                      |                                     |        |                  |                 |                        |                       |  |  |  |

| Sit 0           | <b>C1OUTEN:</b> Comparator 1 Output Enable <sup>(2)</sup><br>1 = Comparator output is driven on the output pad                       |                                     |        |                  |                 |                        |                       |  |  |  |

|                 |                                                                                                                                      | tor output is no                    |        |                  |                 |                        |                       |  |  |  |

| bit 7           | C2OUT: Com                                                                                                                           | parator 2 Outp                      | ut bit |                  |                 |                        |                       |  |  |  |

|                 | When C2INV = 0:                                                                                                                      |                                     |        |                  |                 |                        |                       |  |  |  |

|                 | 1 = C2 VIN+2<br>0 = C2 VIN+2                                                                                                         |                                     |        |                  |                 |                        |                       |  |  |  |

|                 | When C2INV                                                                                                                           |                                     |        |                  |                 |                        |                       |  |  |  |

|                 |                                                                                                                                      | 001/00                              |        |                  |                 |                        |                       |  |  |  |

|                 | 0 = C2 VIN+ 2<br>1 = C2 VIN+ 2                                                                                                       |                                     |        |                  |                 |                        |                       |  |  |  |

### REGISTER 21-1: CMCON: COMPARATOR CONTROL REGISTER

- Section 11.6 "Peripheral Pin Select" for more information.

If C10UTEN = 1, the C10UT peripheral output must be configured to an available RPX pin. See

- 2: If C1OUTEN = 1, the C1OUT peripheral output must be configured to an available RPx pin. See Section 11.6 "Peripheral Pin Select" for more information.

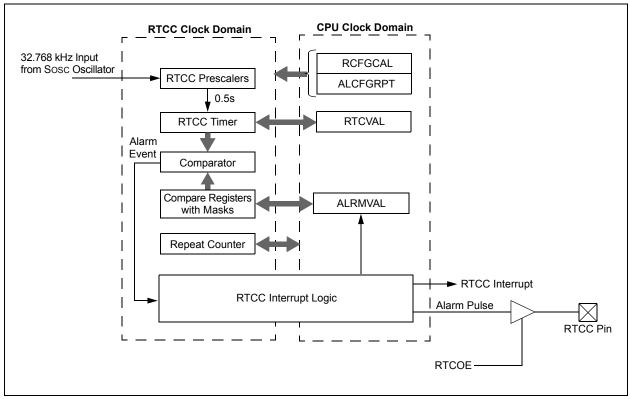

## 22.0 REAL-TIME CLOCK AND CALENDAR (RTCC)

- Note 1: This data sheet summarizes the features PIC24HJ32GP302/304, of the PIC24HJ64GPX02/X04 and PIC24HJ128GPX02/X04 families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 37. "Real-Time Clock and Calendar (RTCC)" (DS70301) of the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

This chapter discusses the Real-Time Clock and Calendar (RTCC) module, available on PIC24HJ32GP302/304, PIC24HJ64GPX02/X04 and PIC24HJ128GPX02/X04 devices, and its operation.

Some of the key features of this module are:

- Time: hours, minutes and seconds

- 24-hour format (military time)

- · Calendar: weekday, date, month and year

- Alarm configurable

- Year range: 2000 to 2099

- · Leap year correction

- BCD format for compact firmware

- Optimized for low-power operation

- · User calibration with auto-adjust

- Calibration range: ±2.64 seconds error per month

- Requirements: External 32.768 kHz clock crystal

- Alarm pulse or seconds clock output on RTCC pin

The RTCC module is intended for applications where accurate time must be maintained for extended periods of time with minimum to no intervention from the CPU. The RTCC module is optimized for low-power usage to provide extended battery lifetime while keeping track of time.

The RTCC module is a 100-year clock and calendar with automatic leap year detection. The range of the clock is from 00:00:00 (midnight) on January 1, 2000 to 23:59:59 on December 31, 2099.

The hours are available in 24-hour (military time) format. The clock provides a granularity of one second with half-second visibility to the user.

## FIGURE 22-1: RTCC BLOCK DIAGRAM

© 2007-2012 Microchip Technology Inc.

| AC CHARAC            | CTERISTICS                               |                                             | Standard Operating Conditions: 3.0V to 3.6V         (unless otherwise stated)         Operating temperature       -40°C ≤TA ≤+85°C for Industri         -40°C ≤TA ≤+125°C for Extended |     |     |     |

|----------------------|------------------------------------------|---------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|

| Maximum<br>Data Rate | Master<br>Transmit Only<br>(Half-Duplex) | Master<br>Transmit/Receive<br>(Full-Duplex) | Slave<br>Transmit/Receive<br>(Full-Duplex)                                                                                                                                             | CKE | СКР | SMP |

| 15 MHz               | Table 28-29                              | —                                           | _                                                                                                                                                                                      | 0,1 | 0,1 | 0,1 |

| 9 MHz                | —                                        | Table 28-30                                 | —                                                                                                                                                                                      | 1   | 0,1 | 1   |

| 9 MHz                | —                                        | Table 28-31                                 | —                                                                                                                                                                                      | 0   | 0,1 | 1   |

| 15 MHz               | _                                        | _                                           | Table 28-32                                                                                                                                                                            | 1   | 0   | 0   |

| 11 MHz               | _                                        | —                                           | Table 28-33                                                                                                                                                                            | 1   | 1   | 0   |

| 15 MHz               | _                                        | —                                           | Table 28-34                                                                                                                                                                            | 0   | 1   | 0   |

| 11 MHz               | _                                        | —                                           | Table 28-35                                                                                                                                                                            | 0   | 0   | 0   |

#### TABLE 28-28: SPIx MAXIMUM DATA/CLOCK RATE SUMMARY

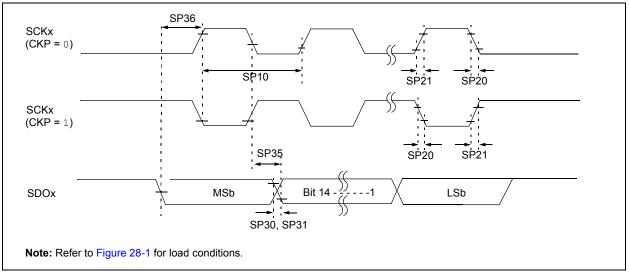

# FIGURE 28-9: SPIX MASTER MODE (HALF-DUPLEX, TRANSMIT ONLY CKE = 0) TIMING CHARACTERISTICS

# FIGURE 28-10: SPIX MASTER MODE (HALF-DUPLEX, TRANSMIT ONLY CKE = 1) TIMING CHARACTERISTICS

#### TABLE 28-45: COMPARATOR MODULE SPECIFICATIONS

| DC CHA       |        | STICS                                      | Standard Operating Conditions: 3.0V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industri $-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended |     |           | 85°C for Industrial |            |

|--------------|--------|--------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----------|---------------------|------------|

| Param<br>No. | Symbol | Characteristic                             | Min.                                                                                                                                                                                               | Тур | Max.      | Units               | Conditions |

| D300         | VIOFF  | Input Offset Voltage <sup>(1)</sup>        | —                                                                                                                                                                                                  | ±10 | _         | mV                  | —          |

| D301         | VICM   | Input Common Mode Voltage <sup>(1)</sup>   | 0                                                                                                                                                                                                  | —   | AVDD-1.5V | V                   | —          |

| D302         | CMRR   | Common Mode Rejection Ratio <sup>(1)</sup> | -54                                                                                                                                                                                                | —   | —         | dB                  | —          |

Note 1: Parameters are characterized but not tested.

#### TABLE 28-46: COMPARATOR REFERENCE VOLTAGE SETTLING TIME SPECIFICATIONS

| AC CHA       | RACTERIS | TICS                         | Standard Operating Conditions: 3.0V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industri $-40^{\circ}C \le TA \le +125^{\circ}C$ for External |     |      | 85°C for Industrial |            |

|--------------|----------|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|---------------------|------------|

| Param<br>No. | Symbol   | Characteristic               | Min.                                                                                                                                                                                               | Тур | Max. | Units               | Conditions |

| VR310        | TSET     | Settling Time <sup>(1)</sup> | —                                                                                                                                                                                                  | —   | 10   | μs                  |            |

**Note 1:** Setting time measured while CVRR = 1 and CVR3:CVR0 bits transition from '0000' to '1111'.

#### TABLE 28-47: COMPARATOR REFERENCE VOLTAGE SPECIFICATIONS

| DC CHAI      | RACTERIS | Standard Operating Conditions: 3.0V to<br>(unless otherwise stated)<br>Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}$<br>$-40^{\circ}C \le TA \le +12^{\circ}$ |                                |    |           |     |   |

|--------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|----|-----------|-----|---|

| Param<br>No. | Symbol   | Characteristic                                                                                                                                                              | Min. Typ Max. Units Conditions |    |           |     |   |

| VRD310       | CVRES    | Resolution                                                                                                                                                                  | CVRSRC/24                      |    | CVRSRC/32 | LSb | _ |

| VRD311       | CVRAA    | Absolute Accuracy                                                                                                                                                           | —                              |    | 0.5       | LSb | — |

| VRD312       | CVRur    | Unit Resistor Value (R)                                                                                                                                                     | _                              | 2k | _         | Ω   | _ |

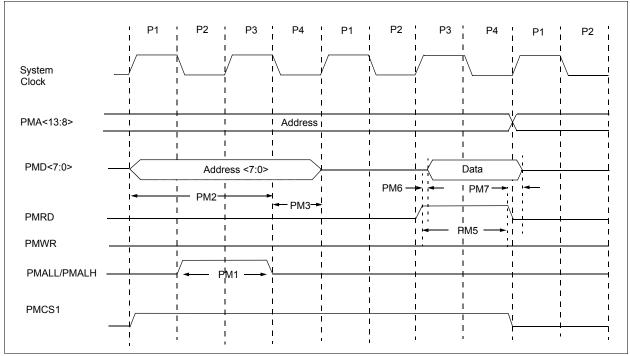

#### FIGURE 28-26: PARALLEL MASTER PORT READ TIMING DIAGRAM

#### TABLE 28-49: PARALLEL MASTER PORT READ TIMING REQUIREMENTS

| AC CHARACTERISTICS |                                                                | Standard Operating Co<br>(unless otherwise stat<br>Operating temperature |          | ,    |       |            |

|--------------------|----------------------------------------------------------------|--------------------------------------------------------------------------|----------|------|-------|------------|

| Param<br>No.       | Characteristic                                                 | Min.                                                                     | Тур      | Max. | Units | Conditions |

| PM1                | PMALL/PMALH Pulse Width                                        | —                                                                        | 0.5 TCY  | _    | ns    | —          |

| PM2                | Address Out Valid to PMALL/PMALH Invalid (address setup time)  | —                                                                        | 0.75 TCY | —    | ns    | —          |